# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 8K x 8                                                                  |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 14x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151ccu6   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   | 3.16                | Timers                                                                                                                    | and watchdogs                                                                                                                                                                                                                                                                                                                            | 28                                                                                                              |

|---|---------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|   |                     | 3.16.1                                                                                                                    | General-purpose timers (TIM2, TIM3, TIM4, TIM5, TIM9, TIM10 and TIM11)                                                                                                                                                                                                                                                                   | . 28                                                                                                            |

|   |                     | 3.16.2                                                                                                                    | Basic timers (TIM6 and TIM7)                                                                                                                                                                                                                                                                                                             |                                                                                                                 |

|   |                     | 3.16.3                                                                                                                    | SysTick timer                                                                                                                                                                                                                                                                                                                            | . 29                                                                                                            |

|   |                     | 3.16.4                                                                                                                    | Independent watchdog (IWDG)                                                                                                                                                                                                                                                                                                              | . 29                                                                                                            |

|   |                     | 3.16.5                                                                                                                    | Window watchdog (WWDG)                                                                                                                                                                                                                                                                                                                   | . 29                                                                                                            |

|   | 3.17                | Commu                                                                                                                     | inication interfaces                                                                                                                                                                                                                                                                                                                     | 29                                                                                                              |

|   |                     | 3.17.1                                                                                                                    | I <sup>2</sup> C bus                                                                                                                                                                                                                                                                                                                     | . 29                                                                                                            |

|   |                     | 3.17.2                                                                                                                    | Universal synchronous/asynchronous receiver transmitter (USART) .                                                                                                                                                                                                                                                                        | . 30                                                                                                            |

|   |                     | 3.17.3                                                                                                                    | Serial peripheral interface (SPI)                                                                                                                                                                                                                                                                                                        | . 30                                                                                                            |

|   |                     | 3.17.4                                                                                                                    | Inter-integrated sound (I2S)                                                                                                                                                                                                                                                                                                             | . 30                                                                                                            |

|   |                     | 3.17.5                                                                                                                    | Universal serial bus (USB)                                                                                                                                                                                                                                                                                                               | . 30                                                                                                            |

|   | 3.18                | CRC (c                                                                                                                    | yclic redundancy check) calculation unit                                                                                                                                                                                                                                                                                                 | 30                                                                                                              |

|   | 3.19                | Develo                                                                                                                    | pment support                                                                                                                                                                                                                                                                                                                            | 31                                                                                                              |

|   |                     | 3.19.1                                                                                                                    | Serial wire JTAG debug port (SWJ-DP)                                                                                                                                                                                                                                                                                                     | . 31                                                                                                            |

|   |                     | 3.19.2                                                                                                                    | Embedded Trace Macrocell™                                                                                                                                                                                                                                                                                                                | . 31                                                                                                            |

| 4 | Pin d               | escripti                                                                                                                  | ons                                                                                                                                                                                                                                                                                                                                      | 32                                                                                                              |

| _ |                     |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |

| E |                     |                                                                                                                           | -                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |

| 5 | Mem                 | ory map                                                                                                                   | oping                                                                                                                                                                                                                                                                                                                                    | 51                                                                                                              |

| 6 |                     |                                                                                                                           | oping                                                                                                                                                                                                                                                                                                                                    |                                                                                                                 |

|   |                     | rical ch                                                                                                                  |                                                                                                                                                                                                                                                                                                                                          | 52                                                                                                              |

|   | Elect               | rical ch                                                                                                                  | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>52                                                                                                 |

|   | Elect               | rical ch<br>Parame                                                                                                        | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>52<br>. 52                                                                                         |

|   | Elect               | rical ch<br>Parame<br>6.1.1                                                                                               | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>52<br>. 52<br>. 52                                                                                 |

|   | Elect               | <b>rical ch</b><br>Parame<br>6.1.1<br>6.1.2                                                                               | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>52<br>52<br>52<br>52<br>52                                                                         |

|   | Elect               | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3                                                                             | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>52<br>52<br>52<br>52<br>52<br>52                                                                   |

|   | Elect               | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                                                    | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>. 52<br>. 52<br>. 52<br>. 52<br>. 52<br>. 52                                                       |

|   | Elect               | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                                           | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>53                                                       |

|   | Elect               | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6                                                  | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>53                                           |

|   | Elect               | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8                                | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>53<br>54                                     |

|   | Elect<br>6.1        | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut                     | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>53<br>54<br>55                                     |

|   | <b>Elect</b><br>6.1 | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut                     | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>53<br>54<br>55<br>56                               |

|   | <b>Elect</b><br>6.1 | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut<br>Operati          | aracteristics         eter conditions         Minimum and maximum values         Typical values         Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme         Current consumption measurement         re maximum ratings         ng conditions | <b>52</b><br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>54<br>54<br>55<br>56<br>56                   |

|   | <b>Elect</b><br>6.1 | rical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut<br>Operati<br>6.3.1 | aracteristics                                                                                                                                                                                                                                                                                                                            | <b>52</b><br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>53<br>54<br>55<br>55<br>56<br>56<br>56<br>57 |

• **Stop** mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and HSE crystal oscillators are disabled. The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB wakeup.

• **Standby** mode with RTC

Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI RC and HSE crystal oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

• Standby mode without RTC

Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

|                                                           | Functionalities depending on the operating power supply range |                |                                   |                            |  |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------|----------------|-----------------------------------|----------------------------|--|--|--|

| Operating power supply range                              | DAC and ADC operation                                         | USB            | Dynamic voltage<br>scaling range  | I/O operation              |  |  |  |

| V <sub>DD</sub> = V <sub>DDA</sub> = 1.65 to 1.71 V       | Not functional                                                | Not functional | Range 2 or<br>Range 3             | Degraded speed performance |  |  |  |

| $V_{DD} = V_{DDA} = 1.71 \text{ to } 1.8 \text{ V}^{(1)}$ | Not functional                                                | Not functional | Range 1, Range 2<br>or Range 3    | Degraded speed performance |  |  |  |

| $V_{DD}=V_{DDA}= 1.8 \text{ to } 2.0 \text{ V}^{(1)}$     | Conversion time up<br>to 500 Ksps                             | Not functional | Range 1, Range 2<br>or<br>Range 3 | Degraded speed performance |  |  |  |

#### Table 3. Functionalities depending on the operating power supply range

power ramp-up should guarantee that 1.65 V is reached on  $V_{\text{DD}}$  at least 1 ms after it exits the POR area.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

# 3.3.3 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32K osc, RCC\_CSR).

# 3.3.4 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using USART1, USART2 or USB. See Application note "STM32 microcontroller system memory boot mode" (AN2606) for details.

# 3.17.2 Universal synchronous/asynchronous receiver transmitter (USART)

The three USART interfaces are able to communicate at speeds of up to 4 Mbit/s. They support IrDA SIR ENDEC and have LIN Master/Slave capability. The three USARTs provide hardware management of the CTS and RTS signals and are ISO 7816 compliant.

All USART interfaces can be served by the DMA controller.

# 3.17.3 Serial peripheral interface (SPI)

Up to three SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The SPIs can be served by the DMA controller.

# 3.17.4 Inter-integrated sound (I<sup>2</sup>S)

Two standard I2S interfaces (multiplexed with SPI2 and SPI3) are available. They can operate in master or slave mode, and can be configured to operate with a 16-/32-bit resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I2S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

The I2Ss can be served by the DMA controller.

# 3.17.5 Universal serial bus (USB)

The STM32L151xC and STM32L152xC devices embed a USB device peripheral compatible with the USB full-speed 12 Mbit/s. The USB interface implements a full-speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and supports suspend/resume. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

# 3.18 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

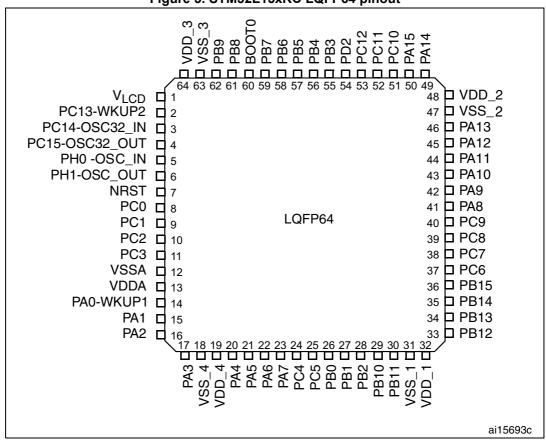

Figure 5. STM32L15xRC LQFP64 pinout

1. This figure shows the package top view.

| Table 9. STM32L151xC and STM32L152xC pin definitions (continued)         Pins       Pin functions |         |        |         |                    |                                  |                         | •               |                                                     |                                          |                                               |

|---------------------------------------------------------------------------------------------------|---------|--------|---------|--------------------|----------------------------------|-------------------------|-----------------|-----------------------------------------------------|------------------------------------------|-----------------------------------------------|

|                                                                                                   | F       | rins   |         |                    |                                  |                         |                 |                                                     | Pin fun                                  | ctions                                        |

| UFBGA100                                                                                          | LQFP100 | LQFP64 | WLCSP63 | LQFP48 or UFQFPN48 | Pin name                         | Pin type <sup>(1)</sup> | I / O Structure | Main<br>function <sup>(2)</sup><br>(after<br>reset) | Alternate functions                      | Additional functions                          |

| C1                                                                                                | 7       | 2      | D5      | 2                  | PC13-<br>WKUP2                   | I/O                     | FT              | PC13                                                | -                                        | WKUP2/<br>RTC_TAMP1/<br>RTC_TS/RTC_OUT        |

| D1                                                                                                | 8       | 3      | D7      | 3                  | PC14-<br>OSC32_IN <sup>(4)</sup> | I/O                     | тс              | PC14                                                | -                                        | OSC32_IN                                      |

| E1                                                                                                | 9       | 4      | D6      | 4                  | PC15-<br>OSC32_OUT               | I/O                     | тс              | PC15                                                | -                                        | OSC32_OUT                                     |

| F2                                                                                                | 10      | -      | -       | -                  | V <sub>SS_5</sub>                | S                       | -               | V <sub>SS_5</sub>                                   | -                                        | -                                             |

| G2                                                                                                | 11      | -      | -       | -                  | $V_{DD_5}$                       | S                       | -               | V <sub>DD_5</sub>                                   | -                                        | -                                             |

| F1                                                                                                | 12      | 5      | F6      | 5                  | PH0-<br>OSC_IN <sup>(5)</sup>    | I/O                     | тс              | PH0                                                 | -                                        | OSC_IN                                        |

| G1                                                                                                | 13      | 6      | F7      | 6                  | PH1-<br>OSC_OUT <sup>(5)</sup>   | I/O                     | тс              | PH1                                                 | -                                        | OSC_OUT                                       |

| H2                                                                                                | 14      | 7      | E7      | 7                  | NRST                             | I/O                     | RST             | NRST                                                | -                                        | -                                             |

| H1                                                                                                | 15      | 8      | E6      | -                  | PC0                              | I/O                     | FT              | PC0                                                 | LCD_SEG18                                | ADC_IN10/<br>COMP1_INP                        |

| J2                                                                                                | 16      | 9      | E5      | -                  | PC1                              | I/O                     | FT              | PC1                                                 | LCD_SEG19                                | ADC_IN11/<br>COMP1_INP                        |

| J3                                                                                                | 17      | 10     | G7      | -                  | PC2                              | I/O                     | FT              | PC2                                                 | LCD_SEG20                                | ADC_IN12/<br>COMP1_INP                        |

| K2                                                                                                | 18      | 11     | G6      | -                  | PC3                              | I/O                     | тс              | PC3                                                 | LCD_SEG21                                | ADC_IN13/<br>COMP1_INP                        |

| J1                                                                                                | 19      | 12     | F5      | 8                  | V <sub>SSA</sub>                 | S                       | -               | V <sub>SSA</sub>                                    | -                                        | -                                             |

| K1                                                                                                | 20      | -      | -       | -                  | V <sub>REF-</sub>                | S                       | -               | V <sub>REF-</sub>                                   | -                                        | -                                             |

| L1                                                                                                | 21      | -      | -       | -                  | V <sub>REF+</sub>                | S                       | -               | V <sub>REF+</sub>                                   | -                                        | -                                             |

| M1                                                                                                | 22      | 13     | H7      | 9                  | V <sub>DDA</sub>                 | S                       | -               | V <sub>DDA</sub>                                    | -                                        | -                                             |

| L2                                                                                                | 23      | 14     | E4      | 10                 | PA0-WKUP1                        | I/O                     | FT              | PA0                                                 | TIM2_CH1_ETR/<br>TIM5_CH1/<br>USART2_CTS | WKUP1/<br>RTC_TAMP2/<br>ADC_IN0/<br>COMP1_INP |

# Table 9. STM32L151xC and STM32L152xC pin definitions (continued)

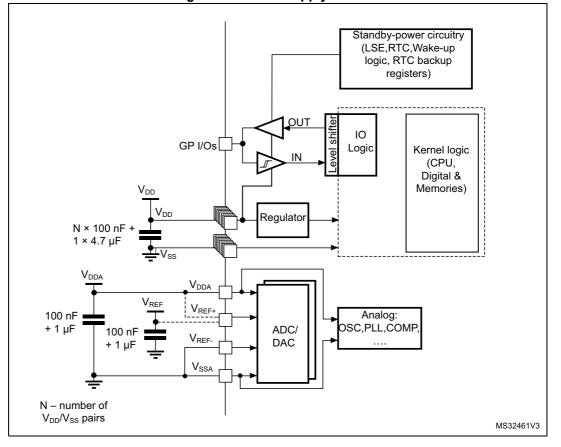

# 6.1.6 Power supply scheme

Figure 12. Power supply scheme

5. To guarantee less than 1% VREF\_OUT deviation.

# 6.3.4 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code. The current consumption is measured as described in *Figure 14: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to the Dhrystone 2.1 code, unless otherwise specified. The current consumption values are derived from tests performed under ambient temperature  $T_A = 25$  °C and  $V_{DD}$  supply voltage conditions summarized in *Table 14: General operating conditions*, unless otherwise specified.

The MCU is placed under the following conditions:

- All I/O pins are configured in analog input mode

- All peripherals are disabled except when explicitly mentioned.

- The Flash memory access time, 64-bit access and prefetch is adjusted depending on f<sub>HCLK</sub> frequency and voltage range to provide the best CPU performance.

- When the peripherals are enabled  $f_{APB1} = f_{APB2} = f_{AHB}$ .

- When PLL is ON, the PLL inputs are equal to HSI = 16 MHz (if internal clock is used) or HSE = 16 MHz (if HSE bypass mode is used).

- The HSE user clock applied to OSCI\_IN input follows the characteristic specified in *Table 27: High-speed external user clock characteristics*.

- For maximum current consumption  $V_{DD} = V_{DDA} = 3.6$  V is applied to all supply pins.

- For typical current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.0 V is applied to all supply pins if not specified otherwise.

| Symbol                                  | Parameter                                                 | Condit                                                                               | tions                                                       | Тур   | Max <sup>(1)</sup> | Unit |

|-----------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------|-------|--------------------|------|

|                                         |                                                           |                                                                                      | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V | 0.905 | -                  |      |

|                                         |                                                           | RTC clocked by LSI (no                                                               | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                     | 1.15  | 1.9                |      |

|                                         |                                                           | independent watchdog)                                                                | T <sub>A</sub> = 55 °C                                      | 1.5   | 2.2                |      |

|                                         |                                                           |                                                                                      | T <sub>A</sub> = 85 °C                                      | 1.75  | 4                  |      |

| I <sub>DD</sub>                         | Supply current in                                         |                                                                                      | T <sub>A</sub> = 105 °C                                     | 2.1   | 8.3 <sup>(2)</sup> |      |

| (Standby<br>with RTC)                   | Standby mode with RTC enabled                             |                                                                                      | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V | 0.98  | -                  |      |

|                                         |                                                           | RTC clocked by LSE<br>external quartz (no<br>independent<br>watchdog) <sup>(3)</sup> | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                     | 1.3   | -                  | μA   |

|                                         |                                                           |                                                                                      | T <sub>A</sub> = 55 °C                                      | 1.7   | -                  |      |

|                                         |                                                           |                                                                                      | T <sub>A</sub> = 85 °C                                      | 2.05  | -                  |      |

|                                         |                                                           |                                                                                      | T <sub>A</sub> = 105 °C                                     | 2.45  | -                  |      |

|                                         |                                                           | Independent watchdog and LSI enabled                                                 | $T_A = -40 \ ^\circ C \text{ to } 25 \ ^\circ C$            | 1     | 1.7                |      |

| I <sub>DD</sub>                         | Supply current in                                         |                                                                                      | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                     | 0.29  | 0.6                |      |

| (Standby)                               | Standby mode (RTC disabled)                               | Independent watchdog                                                                 | T <sub>A</sub> = 55 °C                                      | 0.345 | 0.9                |      |

|                                         |                                                           | and LSI OFF                                                                          | T <sub>A</sub> = 85 °C                                      | 0.575 | 2.75               |      |

|                                         |                                                           |                                                                                      | T <sub>A</sub> = 105 °C                                     | 1.45  | 7 <sup>(2)</sup>   |      |

| I <sub>DD</sub><br>(WU from<br>Standby) | Supply current during<br>wakeup time from<br>Standby mode | -                                                                                    | T <sub>A</sub> = -40 °C to 25 °C                            | 1     | -                  | mA   |

| Table 24. Typical and maximum current co | onsumptions in Standby mode |

|------------------------------------------|-----------------------------|

|------------------------------------------|-----------------------------|

1. Guaranteed by characterization results, unless otherwise specified.

2. Guaranteed by test in production.

3. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8pF loading capacitors.

# **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in the following table. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

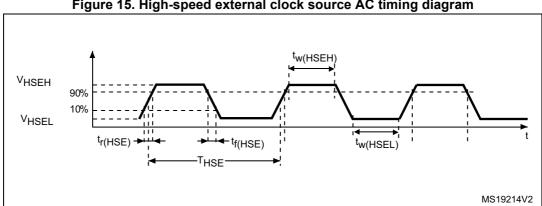

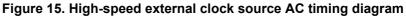

#### 6.3.6 **External clock source characteristics**

# High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.The external clock signal has to respect the I/O characteristics in Section 6.3.12. However, the recommended clock input waveform is shown in Figure 15.

| Symbol                                       | Parameter                           | Conditions                  | Min             | Тур | Max                | Unit |

|----------------------------------------------|-------------------------------------|-----------------------------|-----------------|-----|--------------------|------|

| f                                            | User external clock source          | CSS is on or<br>PLL is used | 1               | 8   | 32                 | MHz  |

| f <sub>HSE_ext</sub>                         | frequency                           | CSS is off, PLL<br>not used | 0               | 8   | 32                 | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage |                             | $0.7V_{DD}$     | -   | V <sub>DD</sub>    | v    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage  |                             | V <sub>SS</sub> | -   | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time             | -                           | 12              | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time            |                             | -               | -   | 20                 | 113  |

| C <sub>in(HSE)</sub>                         | OSC_IN input capacitance            |                             | -               | 2.6 | -                  | pF   |

| Table 27. High-speed external user clock characteristics <sup>(1)</sup> | Table 27 | . Hiah-speed | external u | user clock | characteristics <sup>(1)</sup> |

|-------------------------------------------------------------------------|----------|--------------|------------|------------|--------------------------------|

|-------------------------------------------------------------------------|----------|--------------|------------|------------|--------------------------------|

1. Guaranteed by design.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

|                  |                                                                         |                                    |                             | Max vs.                     | frequenc                     | y range                      |      |

|------------------|-------------------------------------------------------------------------|------------------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------|

| Symbol           | Parameter                                                               | Conditions                         | Monitored<br>frequency band | 4 MHz<br>voltage<br>range 3 | 16 MHz<br>voltage<br>range 2 | 32 MHz<br>voltage<br>range 1 | Unit |

|                  | $V_{DD} = 3.3 V,$<br>$T_A = 25 °C,$<br>SEMI Peak level   QEP100 package | 0.1 to 30 MHz                      | 3                           | -6                          | -5                           |                              |      |

| 6                |                                                                         |                                    | 30 to 130 MHz               | 18                          | 4                            | -7                           | dBµV |

| S <sub>EMI</sub> | reak level                                                              | LQFP100 package compliant with IEC | 130 MHz to 1GHz             | 15                          | 5                            | -7                           |      |

|                  |                                                                         |                                    | SAE EMI Level               | 2.5                         | 2                            | 1                            | -    |

Table 39. EMI characteristics

# 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

## Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114, ANSI/ESD STM5.3.1. standard.

| Symbol                | Ratings                                                     | Conditions                                                   | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|--------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic<br>discharge voltage<br>(human body model)    | $T_A = +25 \text{ °C}$ , conforming<br>to JESD22-A114        | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic<br>discharge voltage<br>(charge device model) | $T_A = +25 \text{ °C}$ , conforming<br>to ANSI/ESD STM5.3.1. | C4    | 500                             | V    |

Table 40. ESD absolute maximum ratings

1. Guaranteed by characterization results.

# **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA with the non-standard V<sub>OL</sub>/V<sub>OH</sub> specifications given in *Table 44*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD(Σ)</sub> (see *Table 12*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS(Σ)</sub> (see *Table 12*).

# **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 44* are derived from tests performed under the conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                | Conditions                                                 | Min                   | Max  | Unit |

|-----------------------------------|------------------------------------------|------------------------------------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)(2)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(2)(3)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V                            | V <sub>DD</sub> -0.4  | -    |      |

| V <sub>OL</sub> <sup>(3)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 4 mA                                     | -                     | 0.45 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 1.65 V < V <sub>DD</sub> < 3.6 V                           | V <sub>DD</sub> -0.45 | -    | v    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 20 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | -                     | 1.3  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V                            | V <sub>DD</sub> -1.3  | -    |      |

Table 44. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. Guaranteed by test in production.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 12 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Guaranteed by characterization results.

# 6.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 56* are guaranteed by design.

| Symbol           | Parameter              |                        | Conditions                     |                                                                   | Min   | Max   | Unit |     |

|------------------|------------------------|------------------------|--------------------------------|-------------------------------------------------------------------|-------|-------|------|-----|

|                  |                        |                        |                                | V <sub>REF+</sub> = V <sub>DDA</sub>                              |       | 16    |      |     |

|                  |                        |                        | 2.4 V ≤V <sub>DDA</sub> ≤3.6 V | V <sub>REF+</sub> < V <sub>DDA</sub><br>V <sub>REF+</sub> > 2.4 V |       | 8     |      |     |

| f <sub>ADC</sub> | ADC clock<br>frequency | Voltage<br>range 1 & 2 |                                | V <sub>REF+</sub> < V <sub>DDA</sub><br>V <sub>REF+</sub> ≤2.4 V  | 0.480 | 0.480 | 4    | MHz |

|                  |                        |                        | 1.8 V ≤V <sub>DDA</sub> ≤2.4 V | V <sub>REF+</sub> = V <sub>DDA</sub>                              |       | 8     |      |     |

|                  |                        |                        | 1.0 V ≤V <sub>DDA</sub> ≤2.4 V | V <sub>REF+</sub> < V <sub>DDA</sub>                              |       | 4     |      |     |

|                  |                        |                        | Voltage range 3                |                                                                   |       | 4     |      |     |

| Table 55. ADC clock frequence | :v |

|-------------------------------|----|

|-------------------------------|----|

## Table 56. ADC characteristics

|                                  |                                           |                      |                    |                  | 1                 |        |  |

|----------------------------------|-------------------------------------------|----------------------|--------------------|------------------|-------------------|--------|--|

| Symbol                           | Parameter                                 | Conditions           | Min                | Тур              | Max               | Unit   |  |

| $V_{DDA}$                        | Power supply                              | -                    | - 1.8 - 3.6        |                  |                   |        |  |

| V <sub>REF+</sub>                | Positive reference voltage                | -                    | 1.8 <sup>(1)</sup> | -                | V <sub>DDA</sub>  | V      |  |

| V <sub>REF-</sub>                | Negative reference voltage                | -                    | -                  | V <sub>SSA</sub> | -                 |        |  |

| I <sub>VDDA</sub>                | Current on the V <sub>DDA</sub> input pin | -                    | -                  | 1000 1450        |                   |        |  |

| I <sub>VREF</sub> <sup>(2)</sup> | Current on the V <sub>REF</sub> input pin | Peak                 | -                  | 400              | 700               | μA     |  |

|                                  |                                           | Average              | -                  | 400              | 450               |        |  |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup>   | -                    | 0 <sup>(4)</sup>   | -                | V <sub>REF+</sub> | V      |  |

| f <sub>S</sub>                   | 12-bit sampling rate                      | Direct channels      | -                  | -                | 1                 | Mana   |  |

|                                  |                                           | Multiplexed channels | -                  | -                | 0.76              | Msps   |  |

|                                  | 10-bit sampling rate                      | Direct channels      | -                  | -                | 1.07              | Mana   |  |

|                                  |                                           | Multiplexed channels | -                  | -                | 0.8               | Msps   |  |

|                                  | 0 hit compliant acts                      | Direct channels      | -                  | -                | 1.23              | Mana   |  |

|                                  | 8-bit sampling rate                       | Multiplexed channels | -                  | -                | 0.89              | Msps   |  |

|                                  | 6 bit compling rate                       | Direct channels      | -                  | -                | 1.45              | D.4 mm |  |

|                                  | 6-bit sampling rate                       | Multiplexed channels | -                  | -                | 1                 | - Msps |  |

| Symbol                          | Parameter                                          | Conditions                                             | Min                       | Тур                | Max     | Unit               |

|---------------------------------|----------------------------------------------------|--------------------------------------------------------|---------------------------|--------------------|---------|--------------------|

| t <sub>S</sub> <sup>(5)</sup>   | Sampling time                                      | Direct channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V      | 0.25                      | -                  | -       | μs                 |

|                                 |                                                    | Multiplexed channels<br>2.4 V ⊴V <sub>DDA</sub> ≤3.6 V | 0.56                      | -                  | -       |                    |

|                                 |                                                    | Direct channels<br>1.8 V ⊴V <sub>DDA</sub> ⊴2.4 V      | 0.56                      | -                  | -       |                    |

|                                 |                                                    | Multiplexed channels<br>1.8 V ⊴V <sub>DDA</sub> ⊴2.4 V | 1                         | -                  | -       |                    |

|                                 |                                                    | -                                                      | 4                         | -                  | 384     | 1/f <sub>ADC</sub> |

|                                 | Total conversion time<br>(including sampling time) | f <sub>ADC</sub> = 16 MHz                              | 1                         | -                  | 24.75   | μs                 |

| t <sub>CONV</sub>               |                                                    | -                                                      | 4 to 384 (s<br>(successiv | 1/f <sub>ADC</sub> |         |                    |

| C                               | Internal sample and hold capacitor                 | Direct channels                                        | -                         | - 16               | -       | pF                 |

| C <sub>ADC</sub>                |                                                    | Multiplexed channels                                   | -                         |                    | -       |                    |

| £                               | External trigger frequency<br>Regular sequencer    | 12-bit conversions                                     | -                         | -                  | Tconv+1 | 1/f <sub>ADC</sub> |

| f <sub>TRIG</sub>               |                                                    | 6/8/10-bit conversions                                 | -                         | -                  | Tconv   | 1/f <sub>ADC</sub> |

| £                               | External trigger frequency<br>Injected sequencer   | 12-bit conversions                                     | -                         | -                  | Tconv+2 | 1/f <sub>ADC</sub> |

| f <sub>TRIG</sub>               |                                                    | 6/8/10-bit conversions                                 | -                         | -                  | Tconv+1 | 1/f <sub>ADC</sub> |

| R <sub>AIN</sub> <sup>(6)</sup> | Signal source impedance                            |                                                        | -                         | -                  | 50      | kΩ                 |

| t <sub>lat</sub>                | Injection trigger conversion<br>latency            | f <sub>ADC</sub> = 16 MHz                              | 219                       | -                  | 281     | ns                 |

|                                 |                                                    | -                                                      | 3.5                       | -                  | 4.5     | 1/f <sub>ADC</sub> |

| +                               | Regular trigger conversion                         | f <sub>ADC</sub> = 16 MHz                              | 156                       | -                  | 219     | ns                 |

| t <sub>latr</sub>               | latency                                            | -                                                      | 2.5                       | -                  | 3.5     | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub>               | Power-up time                                      | -                                                      | -                         | -                  | 3.5     | μs                 |

# Table 56. ADC characteristics (continued)

1. The Vref+ input can be grounded if neither the ADC nor the DAC are used (this allows to shut down an external voltage reference).

2. The current consumption through VREF is composed of two parameters:

- one constant (max 300 µA)

- one variable (max 400  $\mu A$ ), only during sampling time + 2 first conversion pulses

So, peak consumption is 300+400 = 700  $\mu A$  and average consumption is 300 + [(4 sampling + 2) /16] x 400 = 450  $\mu A$  at 1Msps

V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 4: Pin descriptions for further details.

4.  $V_{SSA}$  or  $V_{REF-}$  must be tied to ground.

5. Minimum sampling time is reached for an external input impedance limited to a value as defined in *Table 58: Maximum source impedance RAIN max*.

6. External impedance has another high value limitation when using short sampling time as defined in *Table 58: Maximum source impedance RAIN max*.

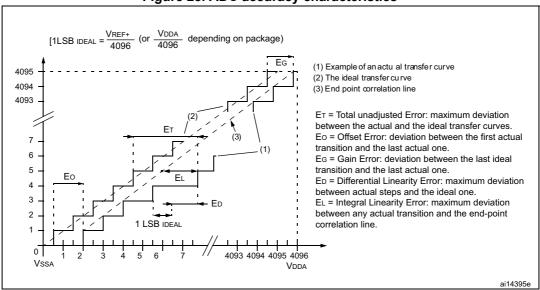

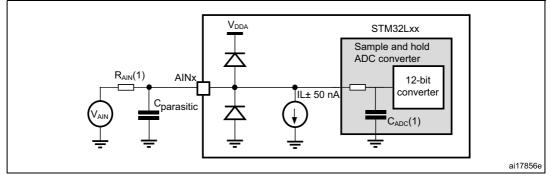

#### Figure 28. ADC accuracy characteristics

- 1. Refer to Table 58: Maximum source impedance RAIN max for the value of  $R_{AIN}$  and Table 56: ADC characteristics for the value of  $C_{ADC}$ .

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

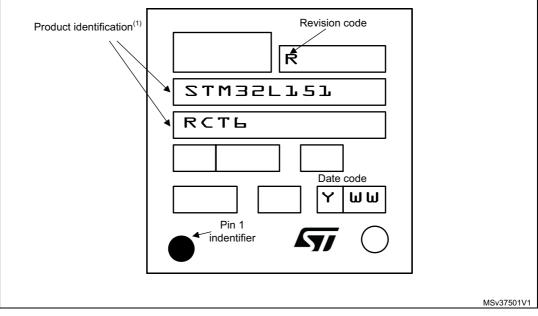

# Marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

# Figure 37. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity

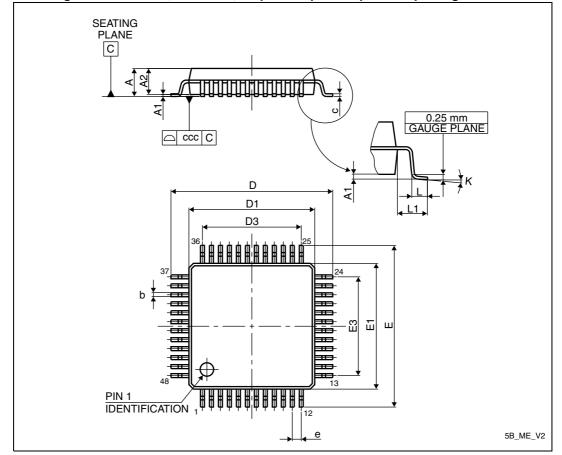

# 7.3 LQFP48, 7 x 7 mm, 48-pin low-profile quad flat package information

Figure 38. LQFP48, 7 x 7 mm, 48-pin low-profile quad flat package outline

1. Drawing is not to scale.

DocID022799 Rev 12

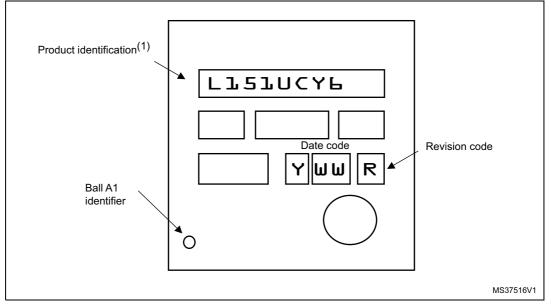

# Marking of engineering samples

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity

# 9 Revision History

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 21-Feb-2012 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |