Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 8K x 8                                                                  |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 21x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 63-UFBGA, WLCSP                                                         |

| Supplier Device Package    | 63-WLCSP (3.23x4.16)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151ucy7tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 46. | UFBGA100, 7 x 7 mm, 0.5 mm pitch, package top view example    | 124 |

|------------|---------------------------------------------------------------|-----|

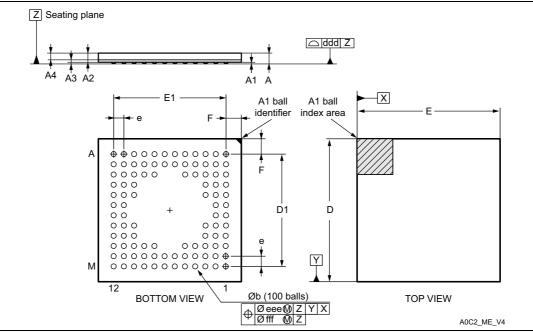

| Figure 47. | WLCSP63, 0.400 mm pitch wafer level chip size package outline | 125 |

| Figure 48. | WLCSP63 device marking example                                | 127 |

| Figure 49. | Thermal resistance suffix 6                                   | 129 |

| Figure 50. | Thermal resistance suffix 7                                   | 129 |

# 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of cores and features. From proprietary 8bit to up to Cortex-M3, including the Cortex-M0+, the STM32Lx series are the best choice to answer the user needs, in terms of ultra-low-power features. The STM32 ultra-low-power series are the best fit, for instance, for gas/water meter, keyboard/mouse or fitness and healthcare, wearable applications. Several built-in features like LCD drivers, dual-bank memory, Low-power run mode, op-amp, AES 128-bit, DAC, USB crystal-less and many others will clearly allow to build very cost-optimized applications by reducing BOM.

Note: STMicroelectronics as a reliable and long-term manufacturer ensures as much as possible the pin-to-pin compatibility between any STM8Lxxxxx and STM32Lxxxxx devices and between any of the STM32Lx and STM32Fx series. Thanks to this unprecedented scalability, the old applications can be upgraded to respond to the latest market features and efficiency demand.

#### 2.2.1 Performance

All the families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM Cortex-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-low-power performance to range from 5 up to 33.3 DMIPs.

#### 2.2.2 Shared peripherals

STM8L15xxx, STM32L15xxx and STM32L162xx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC, DAC and comparators

- Digital peripherals: RTC and some communication interfaces

#### 2.2.3 Common system strategy.

To offer flexibility and optimize performance, the STM8L15xxx, STM32L15xxx and STM32L162xx family uses a common architecture:

- Same power supply range from 1.65 V to 3.6 V

- Architecture optimized to reach ultra-low consumption both in low-power modes and Run mode

- Fast startup strategy from low-power modes

- Flexible system clock

- Ultrasafe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector

#### 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 15 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 2 to 512 Kbytes

# 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **System clock source**: three different clock sources can be used to drive the master clock SYSCLK:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz).

When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- **Auxiliary clock source**: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- **RTC and LCD clock sources:** the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- **Clock-out capability (MCO: microcontroller clock output):** it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

# 3.7 Memories

The STM32L151xC and STM32L152xC devices have the following features:

- 32 Kbytes of embedded RAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 256 Kbytes of embedded Flash program memory

- 8 Kbytes of data EEPROM

- Options bytes

The options bytes are used to write-protect or read-out protect the memory (with 4 Kbytes granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (ARM Cortex-M3 JTAG and serial wire) and boot in RAM selection disabled (JTAG fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature.

The user area of the Flash memory can be protected against Dbus read access by PCROP feature (see RM0038 for details).

# 3.8 DMA (direct memory access)

The flexible 12-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI,  $I^2C$ , USART, general-purpose timers, DAC and ADC.

# 3.12 Operational amplifier

The STM32L151xC and STM32L152xC devices embed two operational amplifiers with external or internal follower routing capability (or even amplifier and filter capability with external components). When one operational amplifier is selected, one external ADC channel is used to enable output measurement.

The operational amplifiers feature:

- Low input bias current

- Low offset voltage

- Low-power mode

- Rail-to-rail input

# 3.13 Ultra-low-power comparators and reference voltage

The STM32L151xC and STM32L152xC devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with fixed threshold

- One comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or a sub-multiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

# 3.14 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM3 and TIM4 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1 and COMP2 and the internal reference voltage  $V_{\text{REFINT}}$ .

# 3.15 Touch sensing

The STM32L151xC and STM32L152xC devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 23 capacitive sensing channels distributed over 10 analog I/O groups. Both software and timer capacitive sensing acquisition modes are supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic...). The capacitive variation

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### TIM10, TIM11 and TIM9

TIM10 and TIM11 are based on a 16-bit auto-reload upcounter. TIM9 is based on a 16-bit auto-reload up/down counter. They include a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers.

They can also be used as simple time bases and be clocked by the LSE clock source (32.768 kHz) to provide time bases independent from the main CPU clock.

#### 3.16.2 Basic timers (TIM6 and TIM7)

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

#### 3.16.3 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit downcounter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches 0.

#### 3.16.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

#### 3.16.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

# 3.17 Communication interfaces

#### 3.17.1 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support dual slave addressing (7-bit only) and both 7- and 10-bit addressing in master mode. A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SM Bus 2.0/PM Bus.

DocID022799 Rev 12

#### 3.17.2 Universal synchronous/asynchronous receiver transmitter (USART)

The three USART interfaces are able to communicate at speeds of up to 4 Mbit/s. They support IrDA SIR ENDEC and have LIN Master/Slave capability. The three USARTs provide hardware management of the CTS and RTS signals and are ISO 7816 compliant.

All USART interfaces can be served by the DMA controller.

#### 3.17.3 Serial peripheral interface (SPI)

Up to three SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The SPIs can be served by the DMA controller.

### 3.17.4 Inter-integrated sound (I<sup>2</sup>S)

Two standard I2S interfaces (multiplexed with SPI2 and SPI3) are available. They can operate in master or slave mode, and can be configured to operate with a 16-/32-bit resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I2S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

The I2Ss can be served by the DMA controller.

#### 3.17.5 Universal serial bus (USB)

The STM32L151xC and STM32L152xC devices embed a USB device peripheral compatible with the USB full-speed 12 Mbit/s. The USB interface implements a full-speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and supports suspend/resume. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

# 3.18 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

STM32L151xC STM32L152xC

| Pin          |

|--------------|

| descriptions |

|               |         | Digital alternate function number |          |                |        |                      |       |            |        |          |           |

|---------------|---------|-----------------------------------|----------|----------------|--------|----------------------|-------|------------|--------|----------|-----------|

| Port          | AFIO0   | AFIO1                             | AFIO2    | AFIO3          | AFIO4  | AFIO5                | AFIO6 | AFIO7      | AFIO11 | AFIO14   | AFIO15    |

| name          |         |                                   |          |                | Alte   | ernate func          | tion  | 11         |        |          |           |

|               | SYSTEM  | TIM2                              | TIM3/4/5 | TIM9/<br>10/11 | I2C1/2 | SPI1/2               | SPI3  | USART1/2/3 | LCD    | CPRI     | SYSTEM    |

| PD3           | -       | -                                 | -        | -              | -      | SPI2_MISO            | -     | USART2_CTS | -      | TIMx_IC4 | EVENT OUT |

| PD4           | -       | -                                 | -        | -              | -      | SPI2_MOSI<br>I2S2_SD | -     | USART2_RTS | -      | TIMx_IC1 | EVENT OUT |

| PD5           | -       | -                                 | -        | -              | -      |                      | -     | USART2_TX  | -      | TIMx_IC2 | EVENT OU  |

| PD6           | -       | -                                 | -        |                | -      | -                    | -     | USART2_RX  | -      | TIMx_IC3 | EVENT OUT |

| PD7           | -       | -                                 | -        | TIM9_CH2       | -      | -                    | -     | USART2_CK  | -      | TIMx_IC4 | EVENT OU  |

| PD8           | -       | -                                 | -        | -              | -      | -                    | -     | USART3_TX  | SEG28  | TIMx_IC1 | EVENT OUT |

| PD9           | -       | -                                 | -        | -              | -      | -                    | -     | USART3_RX  | SEG29  | TIMx_IC2 | EVENT OUT |

| PD10          | -       | -                                 | -        | -              | -      | -                    | -     | USART3_CK  | SEG30  | TIMx_IC3 | EVENT OUT |

| PD11          | -       | -                                 | -        | -              | -      | -                    | -     | USART3_CTS | SEG31  | TIMx_IC4 | EVENT OUT |

| PD12          | -       | -                                 | TIM4_CH1 | -              | -      | -                    | -     | USART3_RTS | SEG32  | TIMx_IC1 | EVENT OU  |

| PD13          | -       | -                                 | TIM4_CH2 | -              | -      | -                    | -     | -          | SEG33  | TIMx_IC2 | EVENT OUT |

| PD14          | -       | -                                 | TIM4_CH3 | -              | -      | -                    | -     | -          | SEG34  | TIMx_IC3 | EVENT OUT |

| PD15          | -       | -                                 | TIM4_CH4 | -              | -      | -                    | -     | -          | SEG35  | TIMx_IC4 | EVENT OU  |

| PE0           | -       | -                                 | TIM4_ETR | TIM10_CH1      | -      | -                    | -     | -          | SEG36  | TIMx_IC1 | EVENT OUT |

| PE1           | -       | -                                 | -        | TIM11_CH1      | -      | -                    | -     | -          | SEG37  | TIMx_IC2 | EVENT OUT |

| PE2           | TRACECK | -                                 | TIM3_ETR | -              |        |                      |       | -          | SEG 38 | TIMx_IC3 | EVENT OUT |

| PE3           | TRACED0 | -                                 | TIM3_CH1 | -              | -      | -                    | -     | -          | SEG 39 | TIMx_IC4 | EVENT OUT |

| PE4           | TRACED1 | -                                 | TIM3_CH2 | -              | -      | -                    | -     | -          | -      | TIMx_IC1 | EVENT OUT |

| PE5           | TRACED2 | -                                 | -        | TIM9_CH1       | -      | -                    | -     | -          | -      | TIMx_IC2 | EVENT OUT |

| PE6-<br>WKUP3 | TRACED3 | -                                 | -        | TIM9_CH2       | -      | -                    | -     | -          | -      | TIMx_IC3 | EVENT OU  |

| PE7           | -       | -                                 | -        | -              | -      | -                    | -     | -          | -      | TIMx_IC4 | EVENT OU  |

#### . 4 : . . . 4 . . 40 A 14 ..... E. :..

DocID022799 Rev 12

49/136

577

| r       |                                          | <b>U</b> (                               |                         |     |      |

|---------|------------------------------------------|------------------------------------------|-------------------------|-----|------|

| Symbol  | Parameter                                | Conditions                               | Min                     | Мах | Unit |

| Тл      | Ambient temperature for 6 suffix version | Maximum power dissipation <sup>(5)</sup> | -40                     | 85  | °C   |

| TA      | Ambient temperature for 7 suffix version | Maximum power dissipation                | ver dissipation -40 105 |     | C    |

| т.      | Junction temperature range               | 6 suffix version                         | -40                     | 105 | °C   |

| TJ Junc |                                          | 7 suffix version                         | -40                     | 110 |      |

#### Table 14. General operating conditions (continued)

1. When the ADC is used, refer to Table 56: ADC characteristics.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and up to 140 mV in operation.

3. To sustain a voltage higher than VDD+0.3V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 73: Thermal characteristics on page 128).

In low-power dissipation state, T<sub>A</sub> can be extended to -40°C to 105°C temperature range as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see *Table 73: Thermal characteristics on page 128*).

#### 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the conditions summarized in *Table 14*.

| Symbol                               | Parameter Conditions           |                                                     | Min  | Тур  | Max  | Unit  |  |

|--------------------------------------|--------------------------------|-----------------------------------------------------|------|------|------|-------|--|

|                                      | V <sub>DD</sub> rise time rate | BOR detector enabled                                | 0    | -    | ∞    |       |  |

| t <sub>VDD</sub> <sup>(1)</sup>      |                                | BOR detector disabled                               | 0    | -    | 1000 | μs/V  |  |

| VDD**                                | V foll time rate               | BOR detector enabled                                | 20   | -    | ∞    | μ5/ ν |  |

|                                      | V <sub>DD</sub> fall time rate | BOR detector disabled                               | 0    | -    | 1000 |       |  |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> | Reset temporization            | V <sub>DD</sub> rising, BOR enabled                 | -    | 2    | 3.3  | ms    |  |

| 'RSTTEMPO` '                         | Reset temporization            | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6  | 1115  |  |

| N .                                  | Power on/power down reset      | Falling edge                                        | 1    | 1.5  | 1.65 |       |  |

| V <sub>POR/PDR</sub>                 | threshold                      | Rising edge                                         | 1.3  | 1.5  | 1.65 |       |  |

| N                                    | Brown-out reset threshold 0    | Falling edge                                        | 1.67 | 1.7  | 1.74 |       |  |

| V <sub>BOR0</sub>                    |                                | Rising edge                                         | 1.69 | 1.76 | 1.8  | v     |  |

| N .                                  | Brown-out reset threshold 1    | Falling edge                                        | 1.87 | 1.93 | 1.97 | v     |  |

| V <sub>BOR1</sub>                    |                                | Rising edge                                         | 1.96 | 2.03 | 2.07 |       |  |

| N .                                  | Brown-out reset threshold 2    | Falling edge                                        | 2.22 | 2.30 | 2.35 |       |  |

| V <sub>BOR2</sub>                    |                                | Rising edge                                         | 2.31 | 2.41 | 2.44 |       |  |

#### Table 15. Embedded reset and power control block characteristics

| Symbol            | Parameter                     | Conditions                                   | Min  | Тур  | Max  | Unit |

|-------------------|-------------------------------|----------------------------------------------|------|------|------|------|

| M                 | Drown out react threshold 2   | Falling edge                                 | 2.45 | 2.55 | 2.6  |      |

| V <sub>BOR3</sub> | Brown-out reset threshold 3   | Rising edge                                  | 2.54 | 2.66 | 2.7  |      |

| M                 | Brown-out reset threshold 4   | Falling edge                                 | 2.68 | 2.8  | 2.85 |      |

| V <sub>BOR4</sub> | BIOWN-OULTESEL INTESHOLU 4    | Rising edge                                  | 2.78 | 2.9  | 2.95 |      |

| V                 | Programmable voltage detector | Falling edge                                 | 1.8  | 1.85 | 1.88 |      |

| V <sub>PVD0</sub> | threshold 0                   | Rising edge                                  | 1.88 | 1.94 | 1.99 |      |

| V                 | PVD threshold 1               | Falling edge                                 | 1.98 | 2.04 | 2.09 |      |

| V <sub>PVD1</sub> |                               | Rising edge                                  | 2.08 | 2.14 | 2.18 |      |

| V                 | DVD threaded 2                | Falling edge                                 | 2.20 | 2.24 | 2.28 | v    |

| V <sub>PVD2</sub> | PVD threshold 2               | Rising edge                                  | 2.28 | 2.34 | 2.38 | V    |

| M                 | DVD threshold 2               | Falling edge                                 | 2.39 | 2.44 | 2.48 |      |

| V <sub>PVD3</sub> | PVD threshold 3               | Rising edge                                  | 2.47 | 2.54 | 2.58 |      |

| M                 | PVD threshold 4               | Falling edge                                 | 2.57 | 2.64 | 2.69 |      |

| V <sub>PVD4</sub> |                               | Rising edge                                  | 2.68 | 2.74 | 2.79 |      |

| M                 | PVD threshold 5               | Falling edge                                 | 2.77 | 2.83 | 2.88 |      |

| V <sub>PVD5</sub> | PVD threshold 5               | Rising edge                                  | 2.87 | 2.94 | 2.99 |      |

| V                 | DVD threshold 6               | Falling edge                                 | 2.97 | 3.05 | 3.09 |      |

| V <sub>PVD6</sub> | PVD threshold 6               | Rising edge                                  | 3.08 | 3.15 | 3.20 |      |

|                   |                               | BOR0 threshold                               | -    | 40   | -    |      |

| V <sub>hyst</sub> | Hysteresis voltage            | All BOR and PVD<br>thresholds excepting BOR0 | -    | 100  | -    | mV   |

Table 15. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

| Symbol                          | Parameter                                          | Conditions                                 |                                                 |                                          |     | Max <sup>(1)</sup> | Unit |

|---------------------------------|----------------------------------------------------|--------------------------------------------|-------------------------------------------------|------------------------------------------|-----|--------------------|------|

|                                 |                                                    |                                            |                                                 | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$  | 8.6 | 12                 |      |

|                                 |                                                    |                                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | T <sub>A</sub> = 85 °C                   | 19  | 25                 |      |

|                                 |                                                    | All<br>peripherals                         |                                                 | T <sub>A</sub> = 105 °C                  | 35  | 47                 |      |

|                                 |                                                    | OFF, code                                  |                                                 | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 14  | 16                 |      |

|                                 |                                                    | executed from RAM,                         | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | T <sub>A</sub> = 85 °C                   | 24  | 29                 |      |

|                                 |                                                    | Flash<br>switched                          |                                                 | T <sub>A</sub> = 105 °C                  | 40  | 51                 |      |

|                                 |                                                    | OFF, V <sub>DD</sub>                       |                                                 | $T_A = -40 \degree C$ to 25 $\degree C$  | 26  | 29                 |      |

|                                 |                                                    | from 1.65 V<br>to 3.6 V                    | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                   | 28  | 31                 |      |

|                                 | Quanha                                             | Supply                                     | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                   | 36  | 42                 | μA   |

| I <sub>DD (LP</sub>             | current in                                         |                                            |                                                 | T <sub>A</sub> = 105 °C                  | 52  | 64                 |      |

| Run)                            | Low-power                                          | /-power<br>mode                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | $T_A = -40 \degree C$ to 25 $\degree C$  | 20  | 24                 |      |

|                                 | run mode                                           |                                            |                                                 | T <sub>A</sub> = 85 °C                   | 32  | 37                 |      |

|                                 |                                                    |                                            |                                                 | T <sub>A</sub> = 105 °C                  | 49  | 61                 |      |

|                                 |                                                    | peripherals                                | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$  | 26  | 30                 |      |

|                                 |                                                    | OFF, code<br>executed                      |                                                 | T <sub>A</sub> = 85 °C                   | 38  | 44                 |      |

|                                 |                                                    | from Flash,                                |                                                 | T <sub>A</sub> = 105 °C                  | 55  | 67                 |      |

|                                 |                                                    | V <sub>DD</sub> from<br>1.65 V to          |                                                 | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$  | 41  | 46                 |      |

|                                 |                                                    | 3.6 V                                      | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                   | 44  | 50                 |      |

|                                 |                                                    |                                            | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                   | 56  | 87                 |      |

|                                 |                                                    |                                            |                                                 | T <sub>A</sub> = 105 °C                  | 73  | 110                |      |

| I <sub>DD</sub> max<br>(LP Run) | Max allowed<br>current in<br>Low-power<br>run mode | V <sub>DD</sub> from<br>1.65 V to<br>3.6 V | -                                               | -                                        | -   | 200                |      |

Table 21. Current consumption in Low-power run mode

1. Guaranteed by characterization results, unless otherwise specified.

| Symbol                            | Parameter                                               | Conditions                                   |                                                                |                                         |     | Max <sup>(1)</sup> | Unit |

|-----------------------------------|---------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------|-----------------------------------------|-----|--------------------|------|

|                                   |                                                         |                                              | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz<br>Flash OFF   | T <sub>A</sub> = -40 °C to 25 °C        | 4.4 | -                  |      |

|                                   |                                                         |                                              | MSI clock, 65 kHz                                              | $T_A$ = -40 °C to 25 °C                 | 14  | 16                 |      |

|                                   |                                                         |                                              | f <sub>HCLK</sub> = 32 kHz                                     | T <sub>A</sub> = 85 °C                  | 19  | 23                 |      |

|                                   |                                                         |                                              | Flash ON                                                       | T <sub>A</sub> = 105 °C                 | 27  | 33                 |      |

|                                   |                                                         | All peripherals<br>OFF, V <sub>DD</sub> from | MSI clock, 65 kHz                                              | $T_A$ = -40 °C to 25 °C                 | 15  | 17                 |      |

|                                   |                                                         | 1.65 V to 3.6 V                              | f <sub>HCLK</sub> = 65 kHz,                                    | T <sub>A</sub> = 85 °C                  | 20  | 23                 |      |

|                                   |                                                         |                                              | Flash ON                                                       | T <sub>A</sub> = 105 °C                 | 28  | 33                 |      |

|                                   |                                                         |                                              |                                                                | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 17  | 19                 |      |

|                                   | Supply<br>current in<br>Low-power<br>sleep mode         |                                              | MSI clock, 131 kHz<br>f <sub>HCLK</sub> = 131 kHz,<br>Flash ON | T <sub>A</sub> = 55 °C                  | 18  | 21                 | μΑ   |

| I <sub>DD</sub>                   |                                                         |                                              |                                                                | T <sub>A</sub> = 85 °C                  | 22  | 25                 |      |

| (LP Sleep)                        |                                                         |                                              |                                                                | T <sub>A</sub> = 105 °C                 | 30  | 35                 |      |

|                                   |                                                         |                                              | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz                | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 14  | 16                 |      |

|                                   |                                                         |                                              |                                                                | T <sub>A</sub> = 85 °C                  | 19  | 22                 |      |

|                                   |                                                         |                                              |                                                                | T <sub>A</sub> = 105 °C                 | 27  | 32                 |      |

|                                   |                                                         | TIM9 and                                     | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz                | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 15  | 17                 |      |

|                                   |                                                         | USART1                                       |                                                                | T <sub>A</sub> = 85 °C                  | 20  | 23                 |      |

|                                   |                                                         | enabled, Flash<br>ON, V <sub>DD</sub> from   |                                                                | T <sub>A</sub> = 105 °C                 | 28  | 33                 |      |

|                                   |                                                         | 1.65 V to 3.6 V                              |                                                                | $T_A$ = -40 °C to 25 °C                 | 17  | 19                 |      |

|                                   |                                                         |                                              | MSI clock, 131 kHz                                             | T <sub>A</sub> = 55 °C                  | 18  | 21                 |      |

|                                   |                                                         |                                              | f <sub>HCLK</sub> = 131 kHz                                    | T <sub>A</sub> = 85 °C                  | 22  | 25                 |      |

|                                   |                                                         |                                              |                                                                | T <sub>A</sub> = 105 °C                 | 30  | 36                 |      |

| I <sub>DD</sub> max<br>(LP Sleep) | Max<br>allowed<br>current in<br>Low-power<br>sleep mode | V <sub>DD</sub> from 1.65 V<br>to 3.6 V      | -                                                              | _                                       | -   | 200                |      |

| Table 22. Current consum | ntion in Low | nower sleen | mode |

|--------------------------|--------------|-------------|------|

| Table 22. Current Consum | puon in Low  | hower sleep | moue |

1. Guaranteed by characterization results, unless otherwise specified.

|            |        | Typical o                                                    | consumption,                                                 | V <sub>DD</sub> = 3.0 V, T                                   | <sub>A</sub> = 25 °C          |                      |

|------------|--------|--------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-------------------------------|----------------------|

| Peripheral |        | Range 1,<br>V <sub>CORE</sub> =<br>1.8 V<br>VOS[1:0] =<br>01 | Range 2,<br>V <sub>CORE</sub> =<br>1.5 V<br>VOS[1:0] =<br>10 | Range 3,<br>V <sub>CORE</sub> =<br>1.2 V<br>VOS[1:0] =<br>11 | Low-power<br>sleep and<br>run | Unit                 |

|            | TIM2   | 11.2                                                         | 8.9                                                          | 7.0                                                          | 8.9                           |                      |

|            | TIM3   | 11.2                                                         | 9.0                                                          | 7.1                                                          | 9.0                           |                      |

|            | TIM4   | 12.9                                                         | 10.4                                                         | 8.2                                                          | 10.4                          |                      |

|            | TIM5   | 14.4                                                         | 11.5                                                         | 9.0                                                          | 11.5                          |                      |

|            | TIM6   | 4.0                                                          | 3.1                                                          | 2.4                                                          | 3.1                           |                      |

|            | TIM7   | 3.8                                                          | 3.0                                                          | 2.3                                                          | 3.0                           |                      |

|            | LCD    | 5.8                                                          | 4.6                                                          | 3.6                                                          | 4.6                           |                      |

|            | WWDG   | 2.9                                                          | 2.3                                                          | 1.8                                                          | 2.3                           |                      |

| APB1       | SPI2   | 6.5                                                          | 5.2                                                          | 4.1                                                          | 5.2                           | µA/MHz               |

| AFDI       | SPI3   | 5.9                                                          | 4.6                                                          | 3.6                                                          | 4.6                           | (f <sub>HCLK</sub> ) |

|            | USART2 | 8.8                                                          | 7.0                                                          | 5.5                                                          | 7.0                           |                      |

|            | USART3 | 8.4                                                          | 6.8                                                          | 5.3                                                          | 6.8                           |                      |

|            | I2C1   | 7.3                                                          | 5.8                                                          | 4.6                                                          | 5.8                           |                      |

|            | I2C2   | 7.9                                                          | 6.3                                                          | 5.0                                                          | 6.3                           |                      |

|            | USB    | 13.3                                                         | 10.6                                                         | 8.3                                                          | 10.6                          |                      |

|            | PWR    | 2.8                                                          | 2.2                                                          | 1.8                                                          | 2.2                           |                      |

|            | DAC    | 6.1                                                          | 4.9                                                          | 3.9                                                          | 4.9                           |                      |

|            | COMP   | 4.8                                                          | 3.8                                                          | 3.0                                                          | 3.8                           |                      |

Table 25. Peripheral current consumption<sup>(1)</sup>

### 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 38*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                                                                                               | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2                                                                                                           | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.3 \text{ V}, \text{LQFP100},  \text{T}_{\text{A}} = +25 \\ \ ^{\circ}\text{C}, \\ \ \text{f}_{\text{HCLK}} = 32 \text{ MHz} \\ \text{conforms to IEC 61000-4-4} \end{array}$ | 4A              |

| Table | 38. | EMS | characteristics    |

|-------|-----|-----|--------------------|

| 10010 | ••• |     | 01101 00101 101100 |

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

### 6.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 46*)

Unless otherwise specified, the parameters given in *Table 46* are derived from tests performed under the conditions summarized in *Table 14*.

| Symbol                                | Parameter                                          | Conditions                                                   | Min                       | Тур                               | Max                 | Unit |

|---------------------------------------|----------------------------------------------------|--------------------------------------------------------------|---------------------------|-----------------------------------|---------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST input low level voltage                       | -                                                            | -                         | -                                 | 0.3 V <sub>DD</sub> |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST input high<br>level voltage                   | -                                                            | 0.39V <sub>DD</sub> +0.59 | -                                 | -                   | V    |

| V <sub>OL(NRST)</sub> <sup>(1)</sup>  | NRST output low                                    | I <sub>OL</sub> = 2 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V    | -                         | -                                 | 0.4                 | v    |

|                                       | level voltage                                      | I <sub>OL</sub> = 1.5 mA<br>1.65 V < V <sub>DD</sub> < 2.7 V | -                         | -                                 | 0.4                 |      |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage hysteresis            | -                                                            | -                         | 10%V <sub>DD</sub> <sup>(2)</sup> | -                   | mV   |

| R <sub>PU</sub>                       | Weak pull-up<br>equivalent resistor <sup>(3)</sup> | $V_{IN} = V_{SS}$                                            | 30                        | 45                                | 60                  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST input filtered pulse                          | -                                                            | -                         | -                                 | 50                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(3)</sup>  | NRST input not<br>filtered pulse                   | -                                                            | 350                       | -                                 | -                   | ns   |

Table 46. NRST pin characteristics

1. Guaranteed by design.

2. With a minimum of 200 mV.

3. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is around 10%.

# 6.3.16 Communications interfaces

# I<sup>2</sup>C interface characteristics

The device I<sup>2</sup>C interface meets the requirements of the standard I<sup>2</sup>C communication protocol with the following restrictions: SDA and SCL are not "true" open-drain I/O pins. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 48*. Refer also to *Section 6.3.13: I/O port characteristics* for more details on the input/output ction characteristics (SDA and SCL).

| Symbol                                     | Parameter                                                            |     | rd mode<br>(1)(2)   | Fast mode | Unit               |    |

|--------------------------------------------|----------------------------------------------------------------------|-----|---------------------|-----------|--------------------|----|

|                                            |                                                                      | Min | Max                 | Min       | Мах                |    |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                                   | 4.7 | -                   | 1.3       | -                  |    |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                                  | 4.0 | -                   | 0.6       | -                  | μs |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                       | 250 | -                   | 100       | -                  |    |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                                   | -   | 3450 <sup>(3)</sup> | -         | 900 <sup>(3)</sup> |    |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                                | -   | 1000                | -         | 300                | ns |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                                | -   | 300                 | -         | 300                |    |

| t <sub>h(STA)</sub>                        | Start condition hold time                                            | 4.0 | -                   | 0.6       | -                  |    |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time                                  | 4.7 | -                   | 0.6       | -                  | μs |

| t <sub>su(STO)</sub>                       | Stop condition setup time                                            | 4.0 | -                   | 0.6       | -                  | μs |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free)                              | 4.7 | -                   | 1.3       | -                  | μs |

| Cb                                         | Capacitive load for each bus line                                    | -   | 400                 | -         | 400                | pF |

| t <sub>SP</sub>                            | Pulse width of spikes that<br>are suppressed by the<br>analog filter | 0   | 50 <sup>(4)</sup>   | 0         | 50 <sup>(4)</sup>  | ns |

| Table 4 | 48. | l <sup>2</sup> C | chara | cteristics |

|---------|-----|------------------|-------|------------|

|---------|-----|------------------|-------|------------|

1. Guaranteed by design.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I<sup>2</sup>C fast mode clock.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

4. The minimum width of the spikes filtered by the analog filter is above  $t_{SP(max)}$ .

# 6.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 56* are guaranteed by design.

| Symbol                                    | Parameter | Conditions                     |                                                                   |                                      |    | Max | Unit |

|-------------------------------------------|-----------|--------------------------------|-------------------------------------------------------------------|--------------------------------------|----|-----|------|

| f <sub>ADC</sub> ADC clock r<br>frequency | Tange Taz | 2.4 V ≤V <sub>DDA</sub> ≤3.6 V | V <sub>REF+</sub> = V <sub>DDA</sub>                              |                                      | 16 |     |      |

|                                           |           |                                | V <sub>REF+</sub> < V <sub>DDA</sub><br>V <sub>REF+</sub> > 2.4 V | 0.480                                | 8  |     |      |

|                                           |           |                                | V <sub>REF+</sub> < V <sub>DDA</sub><br>V <sub>REF+</sub> ≤2.4 V  |                                      | 4  | MHz |      |

|                                           |           | 1.8 V ≤V <sub>DDA</sub> ≤2.4 V | V <sub>REF+</sub> = V <sub>DDA</sub>                              |                                      | 8  |     |      |

|                                           |           |                                | 1.0 V ≤V <sub>DDA</sub> ≤2.4 V                                    | V <sub>REF+</sub> < V <sub>DDA</sub> |    | 4   | ]    |

|                                           |           |                                | Voltage range 3                                                   |                                      |    | 4   |      |

| Table 55. ADC clock frequence | :v |

|-------------------------------|----|

|-------------------------------|----|

#### Table 56. ADC characteristics

| Symbol                           | Parameter                                 | Conditions           | Min                | Тур              | Max                                                       | Unit   |  |  |  |

|----------------------------------|-------------------------------------------|----------------------|--------------------|------------------|-----------------------------------------------------------|--------|--|--|--|

| $V_{DDA}$                        | Power supply                              | -                    | 1.8                | -                | 3.6                                                       |        |  |  |  |

| V <sub>REF+</sub>                | Positive reference voltage                | -                    | 1.8 <sup>(1)</sup> | -                | V <sub>DDA</sub>                                          | V      |  |  |  |

| V <sub>REF-</sub>                | Negative reference voltage                | -                    | -                  | V <sub>SSA</sub> | -<br>1450<br>700<br>450<br>V <sub>REF+</sub><br>1<br>0.76 |        |  |  |  |

| I <sub>VDDA</sub>                | Current on the V <sub>DDA</sub> input pin | -                    | -                  | 1000             | 1450                                                      |        |  |  |  |

| I <sub>VREF</sub> <sup>(2)</sup> | Current on the V input nin                | Peak                 | -                  | 400              | 700                                                       | μA     |  |  |  |

|                                  | Current on the V <sub>REF</sub> input pin | Average              | -                  | 400              | 450                                                       |        |  |  |  |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup>   | -                    | 0 <sup>(4)</sup>   | -                | V <sub>REF+</sub>                                         | V      |  |  |  |

|                                  | 12 hit compling rate                      | Direct channels      | -                  | -                | 1                                                         | Mana   |  |  |  |

|                                  | 12-bit sampling rate                      | Multiplexed channels | -                  | -                | 0.76                                                      | - Msps |  |  |  |

|                                  | 10 hit compling rate                      | Direct channels      | -                  | -                | 1.07                                                      | Msps   |  |  |  |

| £                                | 10-bit sampling rate                      | Multiplexed channels | -                  | -                | 0.8                                                       |        |  |  |  |

| f <sub>S</sub>                   | 0 hit compliant rate                      | Direct channels      | -                  | -                | 1.23                                                      | - Msps |  |  |  |

|                                  | 8-bit sampling rate                       | Multiplexed channels | -                  | -                | 0.89                                                      |        |  |  |  |

|                                  | 6 bit compling rate                       | Direct channels      | -                  | -                | 1.45                                                      | Mana   |  |  |  |

|                                  | 6-bit sampling rate                       | Multiplexed channels | -                  | -                | 1                                                         | - Msps |  |  |  |

| 0h.e.l |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol | Min   | Тур Мах     |       | Min                   | Тур    | Max    |  |

| А      | -     | -           | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170 | 0.220       | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -     | 5.500       | -     | -                     | 0.2165 | -      |  |

| E      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| E3     | -     | 5.500       | -     | -                     | 0.2165 | -      |  |

| е      | -     | 0.500       | -     | -                     | 0.0197 | -      |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -     | 1.000       | -     | -                     | 0.0394 | -      |  |

| k      | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |  |

| CCC    | -     | -           | 0.080 | -                     | -      | 0.0031 |  |

Table 68. LQFP48, 7 x 7 mm, 48-pin low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

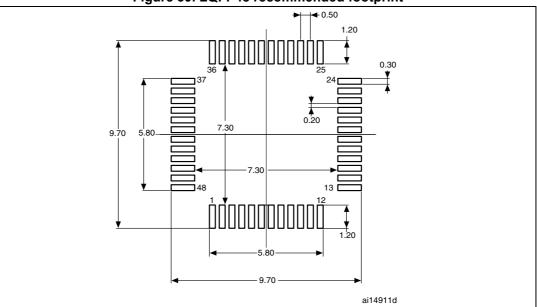

#### Figure 39. LQFP48 recommended footprint

1. Dimensions are in millimeters.

# 7.5 UFBGA100, 7 x 7 mm, 100-ball ultra thin, fine pitch ball grid array package information

Figure 44. UFBGA100, 7 x 7 mm, 0.5 mm pitch package outline

1. Drawing is not to scale.

| Table 70. UFBGA 100, 7 X 7 mm, 0.5 mm pitch package mechanical data |             |       |       |                       |        |        |  |  |  |

|---------------------------------------------------------------------|-------------|-------|-------|-----------------------|--------|--------|--|--|--|

| Symbol                                                              | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |  |  |

|                                                                     | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |  |  |  |

| А                                                                   | 0.460       | 0.530 | 0.600 | 0.0181                | 0.0209 | 0.0236 |  |  |  |

| A1                                                                  | 0.050       | 0.080 | 0.110 | 0.0020                | 0.0031 | 0.0043 |  |  |  |

| A2                                                                  | 0.400       | 0.450 | 0.500 | 0.0157                | 0.0177 | 0.0197 |  |  |  |

| A3                                                                  | 0.080       | 0.130 | 0.180 | 0.0031                | 0.0051 | 0.0071 |  |  |  |

| A4                                                                  | 0.270       | 0.320 | 0.370 | 0.0106                | 0.0126 | 0.0146 |  |  |  |

| b                                                                   | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |  |  |  |

| D                                                                   | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |  |  |

| D1                                                                  | 5.450       | 5.500 | 5.550 | 0.2146                | 0.2165 | 0.2185 |  |  |  |

| E                                                                   | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |  |  |

| E1                                                                  | 5.450       | 5.500 | 5.550 | 0.2146                | 0.2165 | 0.2185 |  |  |  |

| е                                                                   | -           | 0.500 | -     | -                     | 0.0197 | -      |  |  |  |

| F                                                                   | 0.700       | 0.750 | 0.800 | 0.0276                | 0.0295 | 0.0315 |  |  |  |

| ddd                                                                 | -           | -     | 0.100 | -                     | -      | 0.0039 |  |  |  |

#### Table 70. UFBGA100, 7 x 7 mm, 0.5 mm pitch package mechanical data

DocID022799 Rev 12

# 8 Part numbering

#### Table 74. STM32L151xC and STM32L152xC ordering information scheme

| Example:                                            | STM32   | L 151 R C | Т | 6 | D | TR |

|-----------------------------------------------------|---------|-----------|---|---|---|----|

| Device family                                       |         |           |   |   |   |    |

| STM32 = ARM-based 32-bit microcontroller            |         |           |   |   |   |    |

|                                                     |         |           |   |   |   |    |

| Product type                                        |         |           |   |   |   |    |

| L = Low-power                                       |         |           |   |   |   |    |

| Device subfamily                                    |         |           |   |   |   |    |

| 151: Devices without LCD                            |         |           |   |   |   |    |

| 152: Devices with LCD                               |         |           |   |   |   |    |

| Pin count                                           |         |           |   |   |   |    |

| C = 48 pins                                         |         |           |   |   |   |    |

| U = 63 pins                                         |         |           |   |   |   |    |

| R = 64 pins                                         |         |           |   |   |   |    |

| V = 100 pins                                        |         |           |   |   |   |    |

| Flash memory size                                   |         |           |   |   |   |    |

| C = 256 Kbytes of Flash memory                      |         |           |   |   |   |    |

| Package                                             |         |           |   |   |   |    |

| H = BGA                                             |         |           |   |   |   |    |

| T = LQFP                                            |         |           |   |   |   |    |

| Y = WLCSP                                           |         |           |   |   |   |    |

| U = UFQFPN                                          |         |           |   |   |   |    |

| Temperature range                                   |         |           |   |   |   |    |

| 6 = Industrial temperature range, –40 to 85 °C      |         |           |   |   |   |    |

| 7 = Industrial temperature range, –40 to 105 °C     |         |           |   |   |   |    |

| Options                                             |         |           |   |   |   |    |

| No character = $V_{DD}$ range: 1.8 to 3.6 V and BOR | enabled |           |   |   |   |    |

| D = $V_{DD}$ range: 1.65 to 3.6 V and BOR disat     | bled    |           |   |   |   |    |

| Packing                                             |         |           |   |   |   |    |

TR = tape and reel No character = tray or tube

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact the nearest ST sales office.