Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 83                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 8K x 8                                                                  |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 25x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-UFBGA                                                               |

| Supplier Device Package    | 100-UFBGA (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151vch6   |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32L151xC and STM32L152xC ultra-low-power ARM<sup>®</sup> Cortex<sup>®</sup>-M3 based microcontroller product line with a Flash memory of 256 Kbytes.

The ultra-low-power STM32L151xC and STM32L152xC family includes devices in 6 different package types: from 48 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L151xC and STM32L152xC microcontroller family suitable for a wide range of applications:

- Medical and handheld equipment

- Application control and user interface

- PC peripherals, gaming, GPS and sport equipment

- Alarm systems, wired and wireless sensors, video intercom

- Utility metering

This STM32L151xC and STM32L152xC datasheet should be read in conjunction with the STM32L1xxxx reference manual (RM0038). The application note "Getting started with STM32L1xxxx hardware development" (AN3216) gives a hardware implementation overview. Both documents are available from the STMicroelectronics website *www.st.com*.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core please refer to the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 technical reference manual, available from the www.arm.com website. *Figure 1* shows the general block diagram of the device family.

• **Stop** mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and HSE crystal oscillators are disabled. The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB wakeup.

• **Standby** mode with RTC

Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI RC and HSE crystal oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

• Standby mode without RTC

Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

|                                                           | Functionalities depending on the operating power supply range |                |                                   |                            |  |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------|----------------|-----------------------------------|----------------------------|--|--|--|

| Operating power supply range                              | DAC and ADC<br>operation USB                                  |                | Dynamic voltage<br>scaling range  | I/O operation              |  |  |  |

| V <sub>DD</sub> = V <sub>DDA</sub> = 1.65 to 1.71 V       | Not functional                                                | Not functional | Range 2 or<br>Range 3             | Degraded speed performance |  |  |  |

| $V_{DD} = V_{DDA} = 1.71 \text{ to } 1.8 \text{ V}^{(1)}$ | Not functional                                                | Not functional | Range 1, Range 2<br>or Range 3    | Degraded speed performance |  |  |  |

| $V_{DD}=V_{DDA}= 1.8 \text{ to } 2.0 \text{ V}^{(1)}$     | Conversion time up<br>to 500 Ksps                             | Not functional | Range 1, Range 2<br>or<br>Range 3 | Degraded speed performance |  |  |  |

#### Table 3. Functionalities depending on the operating power supply range

|                                   | Functionaliti                     | Functionalities depending on the operating power supply range |                                  |                      |  |  |  |  |  |

|-----------------------------------|-----------------------------------|---------------------------------------------------------------|----------------------------------|----------------------|--|--|--|--|--|

| Operating power supply range      | DAC and ADC operation             | USB                                                           | Dynamic voltage<br>scaling range | I/O operation        |  |  |  |  |  |

| $V_{DD} = V_{DDA} = 2.0$ to 2.4 V | Conversion time up<br>to 500 Ksps | Functional <sup>(2)</sup>                                     | Range 1, Range 2<br>or Range 3   | Full speed operation |  |  |  |  |  |

| $V_{DD} = V_{DDA} = 2.4$ to 3.6 V | Conversion time up<br>to 1 Msps   | Functional <sup>(2)</sup>                                     | Range 1, Range 2<br>or Range 3   | Full speed operation |  |  |  |  |  |

#### Table 3. Functionalities depending on the operating power supply range (continued)

CPU frequency changes from initial to final must respect "F<sub>CPU</sub> initial < 4\*F<sub>CPU</sub> final" to limit V<sub>CORE</sub> drop due to current consumption peak when frequency increases. It must also respect 5 μs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, the user can switch from 4.2 MHz to 16 MHz, wait 5 μs, then switch from 16 MHz to 32 MHz.

2. Should be USB compliant from I/O voltage standpoint, the minimum  $\rm V_{DD}$  is 3.0 V.

#### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                                | Dynamic voltage scaling range |

|----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)   | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)     | Range 2                       |

| 2.1MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

|                                                    |                             | standby)                     | Low-            | ,<br>Low- |                                              | Stop                                           | 5                    | Standby                                        |

|----------------------------------------------------|-----------------------------|------------------------------|-----------------|-----------|----------------------------------------------|------------------------------------------------|----------------------|------------------------------------------------|

| lps                                                | Run/Active                  | Sleep                        | power power Wal |           | Wakeup<br>capability                         |                                                | Wakeup<br>capability |                                                |

| ADC                                                | Y                           | Y                            |                 |           |                                              |                                                |                      |                                                |

| DAC                                                | Y                           | Y                            | Y               | Y         | Y                                            |                                                |                      |                                                |

| Tempsensor                                         | Y                           | Y                            | Y               | Y         | Y                                            |                                                |                      |                                                |

| OP amp                                             | Y                           | Y                            | Y               | Y         | Y                                            |                                                |                      |                                                |

| Comparators                                        | Y                           | Y                            | Y               | Y         | Y                                            | Y                                              |                      |                                                |

| 16-bit and 32-bit<br>Timers                        | Y                           | Y                            | Y               | Y         |                                              |                                                |                      |                                                |

| IWDG                                               | Y                           | Y                            | Y               | Y         | Y                                            | Y                                              | Y                    | Y                                              |

| WWDG                                               | Y                           | Y                            | Y               | Y         |                                              |                                                |                      |                                                |

| Touch sensing                                      | Y                           | Y                            |                 |           |                                              |                                                |                      |                                                |

| Systic Timer                                       | Y                           | Y                            | Y               | Y         |                                              |                                                |                      |                                                |

| GPIOs                                              | Y                           | Y                            | Y               | Y         | Y                                            | Y                                              |                      | 3 pins                                         |

| Wakeup time to<br>Run mode                         | 0 µs                        | 0.4 µs                       | 3 µs            | 46 µs     |                                              | < 8 µs                                         |                      | 58 µs                                          |

|                                                    |                             |                              |                 |           | (1                                           | 0.43 µA<br>no RTC)<br><sub>DD</sub> =1.8V      | (                    | 0.29 µA<br>no RTC)<br>′ <sub>DD</sub> =1.8V    |

| Consumption $V_{} = 1.8 \text{ to } 3.6 \text{ V}$ | Down to 185<br>µA/MHz (from | Down to 34.5<br>µA/MHz (from | Down to         | Down to   | (v                                           | 1.15 μΑ<br>(with RTC)<br>V <sub>DD</sub> =1.8V |                      | 0.9 μA<br>vith RTC)<br>/ <sub>DD</sub> =1.8V   |

| V <sub>DD</sub> =1.8 to 3.6 V<br>(Typ)             | Flash)                      | Flash)                       | 8.6 µA          | 4.4 µA    | 0.44 µA<br>(no RTC)<br>V <sub>DD</sub> =3.0V |                                                | (                    | 0.29 µA<br>no RTC)<br>′ <sub>DD</sub> =3.0V    |

|                                                    |                             |                              |                 |           |                                              | 1.4 μΑ<br>/ith RTC)<br>/ <sub>DD</sub> =3.0V   | (v                   | 1.15 μA<br>(with RTC)<br>V <sub>DD</sub> =3.0V |

## Table 5. Functionalities depending on the working mode (from Run/active down to<br/>standby) (continued)

1. The startup on communication line wakes the CPU which was made possible by an EXTI, this induces a delay before entering run mode.

## 3.2 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with MPU

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor is the industry leading processor for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The memory protection unit (MPU) improves system reliability by defining the memory attributes (such as read/write access permissions) for different memory regions. It provides up to eight different regions and an optional predefined background region.

Owing to its embedded ARM core, the STM32L151xC and STM32L152xC devices are compatible with all ARM tools and software.

#### Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L151xC and STM32L152xC devices embed a nested vectored interrupt controller able to handle up to 53 maskable interrupt channels (not including the 16 interrupt lines of ARM<sup>®</sup> Cortex<sup>®</sup>-M3) and 16 priority levels.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving*, higher-priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

#### 3.3 **Reset and supply management**

#### 3.3.1 Power supply schemes

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 1.8 V when the ADC is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

#### 3.3.2 **Power supply supervisor**

The device has an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

The device exists in two versions:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the V<sub>DD</sub> threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the V<sub>DD</sub> min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the

power ramp-up should guarantee that 1.65 V is reached on  $V_{\text{DD}}$  at least 1 ms after it exits the POR area.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

#### 3.3.3 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32K osc, RCC\_CSR).

#### 3.3.4 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using USART1, USART2 or USB. See Application note "STM32 microcontroller system memory boot mode" (AN2606) for details.

introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. The capacitive sensing acquisition only requires few external components to operate. This acquisition is managed directly by the GPIOs, timers and analog I/O groups (see Section 3.14: System configuration controller and routing interface).

Reliable touch sensing functionality can be quickly and easily implemented using the free STM32L1xx STMTouch touch sensing firmware library.

### 3.16 Timers and watchdogs

The ultra-low-power STM32L151xC and STM32L152xC devices include seven generalpurpose timers, two basic timers, and two watchdog timers.

Table 7 compares the features of the general-purpose and basic timers.

| Timer                  | Counter resolution | Counter type Prescaler factor request |                                    | Counter type Prescaler factor request |   | Complementary<br>outputs |  |  |  |  |

|------------------------|--------------------|---------------------------------------|------------------------------------|---------------------------------------|---|--------------------------|--|--|--|--|

| TIM2,<br>TIM3,<br>TIM4 | 16-bit             | Up, down,<br>up/down                  | Any integer between<br>1 and 65536 | Yes                                   | 4 | No                       |  |  |  |  |

| TIM5                   | 32-bit             | Up, down,<br>up/down                  | Any integer between<br>1 and 65536 | Yes                                   | 4 | No                       |  |  |  |  |

| TIM9                   | 16-bit             | Up, down,<br>up/down                  | Any integer between<br>1 and 65536 | No                                    | 2 | No                       |  |  |  |  |

| TIM10,<br>TIM11        | 16-bit             | Up                                    | Any integer between<br>1 and 65536 | No                                    | 1 | No                       |  |  |  |  |

| TIM6,<br>TIM7          | 16-bit             | Up                                    | Any integer between<br>1 and 65536 | Yes                                   | 0 | No                       |  |  |  |  |

Table 7. Timer feature comparison

# 3.16.1 General-purpose timers (TIM2, TIM3, TIM4, TIM5, TIM9, TIM10 and TIM11)

There are seven synchronizable general-purpose timers embedded in the STM32L151xC and STM32L152xC devices (see *Table 7* for differences).

#### TIM2, TIM3, TIM4, TIM5

TIM2, TIM3, TIM4 are based on 16-bit auto-reload up/down counter. TIM5 is based on a 32bit auto-reload up/down counter. They include a 16-bit prescaler. They feature four independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures/output compares/PWMs on the largest packages.

TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together or with the TIM10, TIM11 and TIM9 general-purpose timers via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

|          | Table 9. STM32L151xC and STM32L152xC pin definitions (continued)         Pins       Pin functions |        |         |                    |                                  |                         |                 |                                                     | •                                        |                                               |  |  |

|----------|---------------------------------------------------------------------------------------------------|--------|---------|--------------------|----------------------------------|-------------------------|-----------------|-----------------------------------------------------|------------------------------------------|-----------------------------------------------|--|--|

|          | F                                                                                                 | rins   |         |                    |                                  |                         |                 |                                                     |                                          |                                               |  |  |

| UFBGA100 | LQFP100                                                                                           | LQFP64 | WLCSP63 | LQFP48 or UFQFPN48 | Pin name                         | Pin type <sup>(1)</sup> | I / O Structure | Main<br>function <sup>(2)</sup><br>(after<br>reset) | Alternate functions                      | Additional functions                          |  |  |

| C1       | 7                                                                                                 | 2      | D5      | 2                  | PC13-<br>WKUP2                   | I/O                     | FT              | PC13                                                | -                                        | WKUP2/<br>RTC_TAMP1/<br>RTC_TS/RTC_OUT        |  |  |

| D1       | 8                                                                                                 | 3      | D7      | 3                  | PC14-<br>OSC32_IN <sup>(4)</sup> | I/O                     | тс              | PC14                                                | -                                        | OSC32_IN                                      |  |  |

| E1       | 9                                                                                                 | 4      | D6      | 4                  | PC15-<br>OSC32_OUT               | I/O                     | тс              | PC15                                                | -                                        | OSC32_OUT                                     |  |  |

| F2       | 10                                                                                                | -      | -       | -                  | V <sub>SS_5</sub>                | S                       | -               | V <sub>SS_5</sub>                                   | -                                        | -                                             |  |  |

| G2       | 11                                                                                                | -      | -       | -                  | $V_{DD_5}$                       | S                       | -               | V <sub>DD_5</sub>                                   | -                                        | -                                             |  |  |

| F1       | 12                                                                                                | 5      | F6      | 5                  | PH0-<br>OSC_IN <sup>(5)</sup>    | I/O                     | тс              | PH0                                                 | -                                        | OSC_IN                                        |  |  |

| G1       | 13                                                                                                | 6      | F7      | 6                  | PH1-<br>OSC_OUT <sup>(5)</sup>   | I/O                     | тс              | PH1                                                 | -                                        | OSC_OUT                                       |  |  |

| H2       | 14                                                                                                | 7      | E7      | 7                  | NRST                             | I/O                     | RST             | NRST                                                | -                                        | -                                             |  |  |

| H1       | 15                                                                                                | 8      | E6      | -                  | PC0                              | I/O                     | FT              | PC0                                                 | LCD_SEG18                                | ADC_IN10/<br>COMP1_INP                        |  |  |

| J2       | 16                                                                                                | 9      | E5      | -                  | PC1                              | I/O                     | FT              | PC1                                                 | LCD_SEG19                                | ADC_IN11/<br>COMP1_INP                        |  |  |

| J3       | 17                                                                                                | 10     | G7      | -                  | PC2                              | I/O                     | FT              | PC2                                                 | LCD_SEG20                                | ADC_IN12/<br>COMP1_INP                        |  |  |

| K2       | 18                                                                                                | 11     | G6      | -                  | PC3                              | I/O                     | тс              | PC3                                                 | LCD_SEG21                                | ADC_IN13/<br>COMP1_INP                        |  |  |

| J1       | 19                                                                                                | 12     | F5      | 8                  | V <sub>SSA</sub>                 | S                       | -               | V <sub>SSA</sub>                                    | -                                        | -                                             |  |  |

| K1       | 20                                                                                                | -      | -       | -                  | V <sub>REF-</sub>                | S                       | -               | V <sub>REF-</sub>                                   | -                                        | -                                             |  |  |

| L1       | 21                                                                                                | -      | -       | -                  | V <sub>REF+</sub>                | S                       | -               | V <sub>REF+</sub>                                   | -                                        | -                                             |  |  |

| M1       | 22                                                                                                | 13     | H7      | 9                  | V <sub>DDA</sub>                 | S                       | -               | V <sub>DDA</sub>                                    | -                                        | -                                             |  |  |

| L2       | 23                                                                                                | 14     | E4      | 10                 | PA0-WKUP1                        | I/O                     | FT              | PA0                                                 | TIM2_CH1_ETR/<br>TIM5_CH1/<br>USART2_CTS | WKUP1/<br>RTC_TAMP2/<br>ADC_IN0/<br>COMP1_INP |  |  |

#### Table 9. STM32L151xC and STM32L152xC pin definitions (continued)

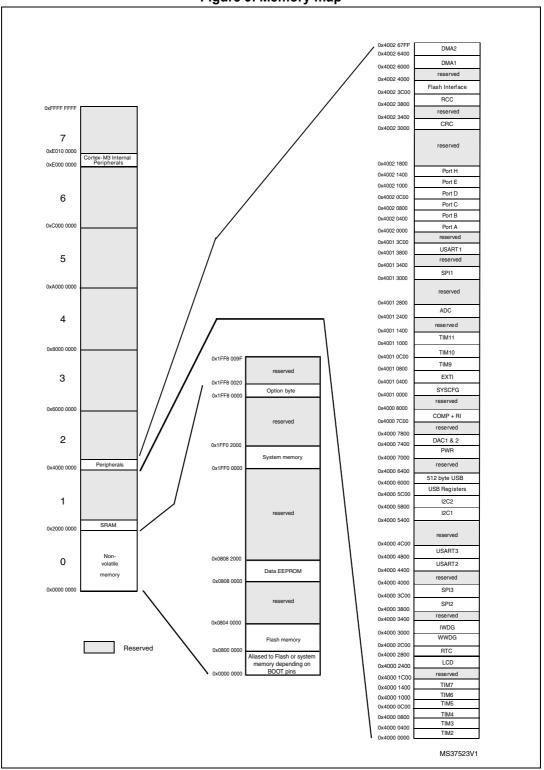

## 5 Memory mapping

Figure 9. Memory map

| Symbol | Parameter                                | Conditions                               | Min | Мах | Unit |  |  |  |  |

|--------|------------------------------------------|------------------------------------------|-----|-----|------|--|--|--|--|

| Тл     | Ambient temperature for 6 suffix version | Maximum power dissipation <sup>(5)</sup> | -40 | 85  | °C   |  |  |  |  |

| ΤΑ     | Ambient temperature for 7 suffix version | Maximum power dissipation                | -40 | 105 | C    |  |  |  |  |

| TJ     | Junction temperature range               | 6 suffix version                         | -40 | 105 | °C   |  |  |  |  |

|        |                                          | 7 suffix version                         | -40 | 110 |      |  |  |  |  |

#### Table 14. General operating conditions (continued)

1. When the ADC is used, refer to Table 56: ADC characteristics.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and up to 140 mV in operation.

3. To sustain a voltage higher than VDD+0.3V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 73: Thermal characteristics on page 128).

In low-power dissipation state, T<sub>A</sub> can be extended to -40°C to 105°C temperature range as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see *Table 73: Thermal characteristics on page 128*).

#### 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the conditions summarized in *Table 14*.

| Symbol                               | Parameter                      | Conditions                                          | Min  | Тур  | Max  | Unit  |

|--------------------------------------|--------------------------------|-----------------------------------------------------|------|------|------|-------|

|                                      | V <sub>DD</sub> rise time rate | BOR detector enabled                                | 0    | -    | ∞    |       |

| t <sub>VDD</sub> <sup>(1)</sup>      |                                | BOR detector disabled                               | 0    | -    | 1000 | μs/V  |

| VDD**                                | V foll time rate               | BOR detector enabled                                | 20   | -    | ∞    | μ5/ ν |

|                                      | V <sub>DD</sub> fall time rate | BOR detector disabled                               | 0    | -    | 1000 |       |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> | Reset temporization            | V <sub>DD</sub> rising, BOR enabled                 | -    | 2    | 3.3  | ms    |

| 'RSTTEMPO` '                         | Reset temporization            | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6  | 1115  |

| N .                                  | Power on/power down reset      | Falling edge                                        | 1    | 1.5  | 1.65 |       |

| V <sub>POR/PDR</sub>                 | threshold                      | Rising edge                                         | 1.3  | 1.5  | 1.65 |       |

| N                                    | Brown-out reset threshold 0    | Falling edge                                        | 1.67 | 1.7  | 1.74 |       |

| V <sub>BOR0</sub>                    |                                | Rising edge                                         | 1.69 | 1.76 | 1.8  | v     |

| N .                                  | Brown-out reset threshold 1    | Falling edge                                        | 1.87 | 1.93 | 1.97 | v     |

| V <sub>BOR1</sub>                    | Brown-out reset threshold 1    | Rising edge                                         | 1.96 | 2.03 | 2.07 |       |

| N .                                  | Brown-out reset threshold 2    | Falling edge                                        | 2.22 | 2.30 | 2.35 |       |

| V <sub>BOR2</sub>                    |                                | Rising edge                                         | 2.31 | 2.41 | 2.44 |       |

#### Table 15. Embedded reset and power control block characteristics

| Symbol          | Parameter               | Conc                                                                  | f <sub>HCLK</sub>                                  | Тур     | Max <sup>(1)</sup> | Unit |    |

|-----------------|-------------------------|-----------------------------------------------------------------------|----------------------------------------------------|---------|--------------------|------|----|

| I <sub>DD</sub> |                         |                                                                       |                                                    | 1 MHz   | 215                | 400  |    |

|                 |                         |                                                                       | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 2 MHz   | 400                | 600  | μA |

|                 |                         |                                                                       |                                                    | 4 MHz   | 725                | 960  |    |

|                 |                         | $f_{HSE} = f_{HCLK}$ up to 16                                         |                                                    | 4 MHz   | 0.915              | 1.1  |    |

|                 |                         | MHz included, f <sub>HSE</sub> =<br>f <sub>HCLK</sub> /2 above 16 MHz | Range 2, V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 8 MHz   | 1.75               | 2.1  |    |

|                 | Cumple                  | (PLL ON) <sup>(2)</sup><br>urrent in<br>un mode,<br>ode<br>xecuted    |                                                    | 16 MHz  | 3.4                | 3.9  |    |

|                 | current in<br>Run mode, |                                                                       | Range 1, V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 8 MHz   | 2.1                | 2.8  |    |

| (Run<br>from    |                         |                                                                       |                                                    | 16 MHz  | 4.2                | 4.9  | mA |

| Flash)          | executed                |                                                                       |                                                    | 32 MHz  | 8.25               | 9.4  |    |

|                 | from Flash              |                                                                       | Range 2, V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz  | 3.5                | 4    |    |

|                 |                         |                                                                       | Range 1, V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz  | 8.2                | 9.6  |    |

|                 |                         | MSI clock, 65 kHz                                                     |                                                    | 65 kHz  | 40.5               | 110  |    |

|                 |                         | MSI clock, 524 kHz                                                    | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 524 kHz | 125                | 190  | μA |

|                 |                         | MSI clock, 4.2 MHz                                                    |                                                    | 4.2 MHz | 775                | 900  |    |

#### Table 18. Current consumption in Run mode, code with data processing running from Flash

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

#### 6.3.7 Internal clock source characteristics

The parameters given in *Table 31* are derived from tests performed under the conditions summarized in *Table 14*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                                         | Conditions                                                           | Min               | Тур  | Max              | Unit |

|-------------------------------------|---------------------------------------------------|----------------------------------------------------------------------|-------------------|------|------------------|------|

| f <sub>HSI</sub>                    | Frequency                                         | V <sub>DD</sub> = 3.0 V                                              | -                 | 16   | -                | MHz  |

| TRIM <sup>(1)(2)</sup>              | HSI user-trimmed                                  | Trimming code is not a multiple of 16                                | -                 | ±0.4 | 0.7              | %    |

| TRIM                                | resolution                                        | Trimming code is a multiple of 16                                    | -                 | -    | ±1.5             | %    |

|                                     |                                                   | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                     | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |

|                                     | Accuracy of the factory-calibrated HSI oscillator | $V_{DDA}$ = 3.0 V, $T_{A}$ = 0 to 55 °C                              | -1.5              | -    | 1.5              | %    |

|                                     |                                                   | $V_{DDA}$ = 3.0 V, $T_{A}$ = -10 to 70 °C                            | -2                | -    | 2                | %    |

| ACC <sub>HSI</sub> <sup>(2)</sup>   |                                                   | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = -10 to 85 °C              | -2.5              | -    | 2                | %    |

|                                     |                                                   | $V_{DDA}$ = 3.0 V, $T_{A}$ = -10 to 105 °C                           | -4                | -    | 2                | %    |

|                                     |                                                   | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = -40 to 105 °C | -4                | -    | 3                | %    |

| t <sub>SU(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>startup time                    | _                                                                    | -                 | 3.7  | 6                | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>power consumption               | -                                                                    | -                 | 100  | 140              | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

#### Low-speed internal (LSI) RC oscillator

#### Table 32. LSI oscillator characteristics

| Symbol                              | Parameter                                                                | Min | Тур | Мах | Unit |

|-------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                                            | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift $0^{\circ}C \leq T_{A} \leq 105^{\circ}C$ | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                              | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                                         | -   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

#### **SPI characteristics**

Unless otherwise specified, the parameters given in the following table are derived from tests performed under the conditions summarized in *Table 14*.

Refer to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                        | Conditions                 | Min                   | Max <sup>(2)</sup>    | Unit |  |

|----------------------------------------------------------------------------|----------------------------------|----------------------------|-----------------------|-----------------------|------|--|

| -                                                                          |                                  | Master mode                | -                     | 16                    |      |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency              | Slave mode                 | -                     | 16                    | MHz  |  |

|                                                                            |                                  | Slave transmitter          | -                     | 12 <sup>(3)</sup>     |      |  |

| $t_{r(SCK)}^{(2)}_{t_{f(SCK)}^{(2)}}$                                      | SPI clock rise and fall time     | Capacitive load: C = 30 pF | -                     | 6                     | ns   |  |

| DuCy(SCK)                                                                  | SPI slave input clock duty cycle | Slave mode                 | 30                    | 70                    | %    |  |

| t <sub>su(NSS)</sub>                                                       | NSS setup time                   | Slave mode                 | 4t <sub>HCLK</sub>    | -                     |      |  |

| t <sub>h(NSS)</sub>                                                        | NSS hold time                    | Slave mode                 | 2t <sub>HCLK</sub>    | -                     |      |  |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time            | Master mode                | t <sub>SCK</sub> /2-5 | t <sub>SCK</sub> /2+3 |      |  |

| t <sub>su(MI)</sub> <sup>(2)</sup>                                         | Data input actur time            | Master mode                | 5                     | -                     |      |  |

| t <sub>su(SI)</sub> <sup>(2)</sup>                                         | Data input setup time            | Slave mode                 | 6                     | -                     |      |  |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                          | Deta input hold time             | Master mode                | 5                     | -                     | ns   |  |

| t <sub>h(SI)</sub> <sup>(2)</sup>                                          | Data input hold time             | Slave mode                 | 5                     | -                     |      |  |

| t <sub>a(SO)</sub> <sup>(4)</sup>                                          | Data output access time          | Slave mode                 | 0                     | 3t <sub>HCLK</sub>    |      |  |

| t <sub>v(SO)</sub> (2)                                                     | Data output valid time           | Slave mode                 | -                     | 33                    |      |  |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time           | Master mode                | -                     | 6.5                   |      |  |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Slave mode                 | 17                    | -                     |      |  |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Master mode                | 0.5                   | -                     |      |  |

Table 50. SPI characteristics<sup>(1)</sup>

1. The characteristics above are given for voltage range 1.

2. Guaranteed by characterization results.

3. The maximum SPI clock frequency in slave transmitter mode is given for an SPI slave input clock duty cycle (DuCy(SCK)) ranging between 40 to 60%.

4. Min time is for the minimum time to drive the output and max time is for the maximum time to validate the data.

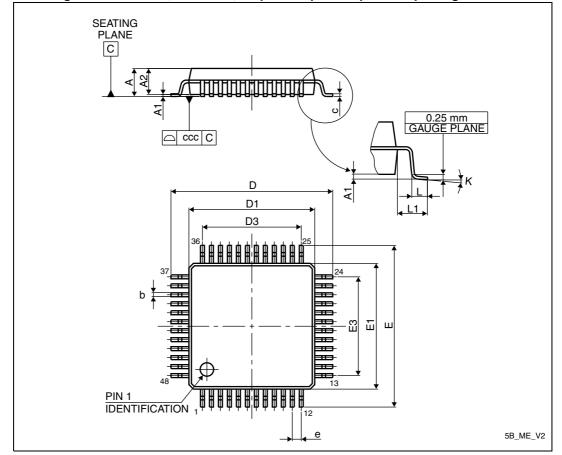

# 7.3 LQFP48, 7 x 7 mm, 48-pin low-profile quad flat package information

Figure 38. LQFP48, 7 x 7 mm, 48-pin low-profile quad flat package outline

1. Drawing is not to scale.

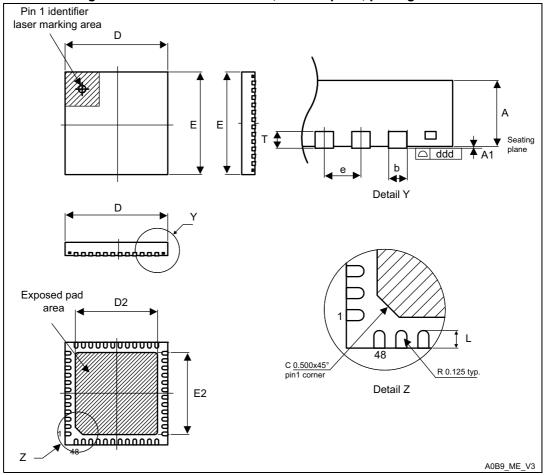

### 7.4 UFQFPN48 7 x 7 mm, 0.5 mm pitch, package information

Figure 41. UFQFPN48 7 x 7 mm, 0.5 mm pitch, package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

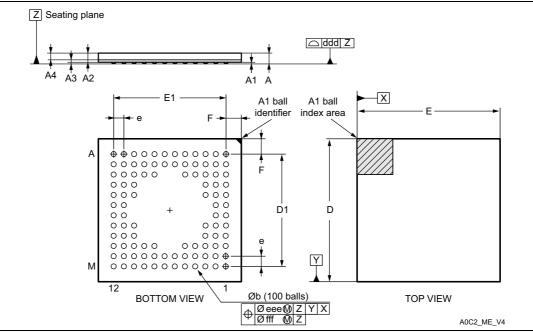

# 7.5 UFBGA100, 7 x 7 mm, 100-ball ultra thin, fine pitch ball grid array package information

Figure 44. UFBGA100, 7 x 7 mm, 0.5 mm pitch package outline

1. Drawing is not to scale.

| Table 70. UFBGA100, 7 X 7 mm, 0.5 mm pitch package mechanical data |             |       |       |                       |        |        |  |

|--------------------------------------------------------------------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol                                                             | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|                                                                    | Min         | Тур   | Max   | Min                   | Тур    | Мах    |  |

| А                                                                  | 0.460       | 0.530 | 0.600 | 0.0181                | 0.0209 | 0.0236 |  |

| A1                                                                 | 0.050       | 0.080 | 0.110 | 0.0020                | 0.0031 | 0.0043 |  |

| A2                                                                 | 0.400       | 0.450 | 0.500 | 0.0157                | 0.0177 | 0.0197 |  |

| A3                                                                 | 0.080       | 0.130 | 0.180 | 0.0031                | 0.0051 | 0.0071 |  |

| A4                                                                 | 0.270       | 0.320 | 0.370 | 0.0106                | 0.0126 | 0.0146 |  |

| b                                                                  | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |  |

| D                                                                  | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |

| D1                                                                 | 5.450       | 5.500 | 5.550 | 0.2146                | 0.2165 | 0.2185 |  |

| Е                                                                  | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |

| E1                                                                 | 5.450       | 5.500 | 5.550 | 0.2146                | 0.2165 | 0.2185 |  |

| е                                                                  | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| F                                                                  | 0.700       | 0.750 | 0.800 | 0.0276                | 0.0295 | 0.0315 |  |

| ddd                                                                | -           | -     | 0.100 | -                     | -      | 0.0039 |  |

#### Table 70. UFBGA100, 7 x 7 mm, 0.5 mm pitch package mechanical data

| Symbol | millimeters |     |       | inches <sup>(1)</sup> |     |        |

|--------|-------------|-----|-------|-----------------------|-----|--------|

|        | Min         | Тур | Мах   | Min                   | Тур | Мах    |

| eee    | -           | -   | 0.150 | -                     | -   | 0.0059 |

| fff    | -           | -   | 0.050 | -                     | -   | 0.0020 |

#### Table 70. UFBGA100, 7 x 7 mm, 0.5 mm pitch package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

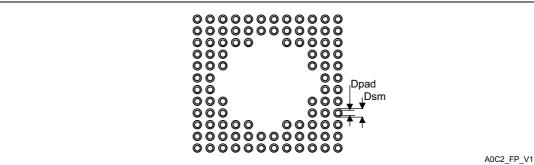

#### Figure 45. UFBGA100, 7 x 7 mm, 0.5 mm pitch, package recommended footprint

#### Table 71. UFBGA100, 7 x 7 mm, 0.50 mm pitch, recommended PCB design rules

| Dimension         | Recommended values                                               |  |  |

|-------------------|------------------------------------------------------------------|--|--|

| Pitch             | 0.5                                                              |  |  |

| Dpad              | 0.280 mm                                                         |  |  |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |  |  |

| Stencil opening   | 0.280 mm                                                         |  |  |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |  |  |

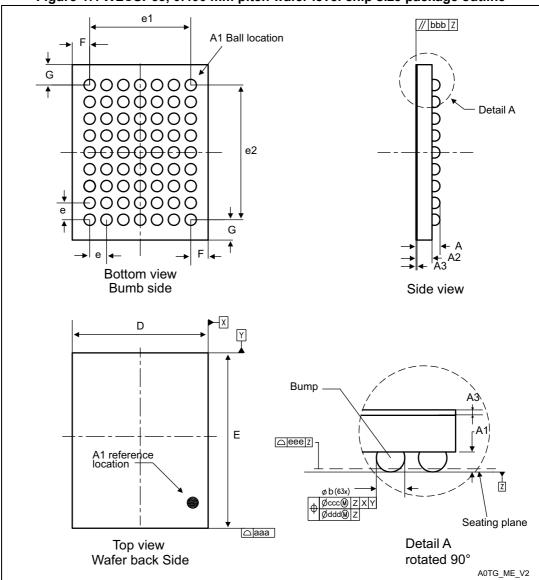

# 7.6 WLCSP63, 0.400 mm pitch wafer level chip size package information

Figure 47. WLCSP63, 0.400 mm pitch wafer level chip size package outline

1. Drawing is not to scale.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01-Feb-2013 | 3        | Removed AHB1/AHB2 and corrected typo on APB1/APB2 in: <i>Figure 1:</i><br><i>Ultra-low-power STM32L162xC block diagram-low-power</i><br><i>STM32L162xC block diagram</i><br>Updated "OP amp" line in <i>Table 4: Functionalities depending on the</i><br><i>working mode (from Run/active down to standby)</i><br>Added IWDG and WWDG rows in <i>Table 4: Functionalities depending</i><br><i>on the working mode (from Run/active down to standby)</i><br>Updated address range in <i>Table 7: Internal voltage reference</i><br><i>measured values</i><br>The comment "HSE = 16 MHz(2) (PLL ON for fHCLK above 16 MHz)"<br>replaced by "fHSE = fHCLK up to 16 MHz included, fHSE = fHCLK/2<br>above 16 MHz (PLL ON)(2)" in table <i>Table 27: Current consumption in</i><br><i>Sleep mode</i><br>replaced pin names D7,C7,C6,C8,B8,A8 respectively by<br>D11,D10,C12,B12,A12,A11 in column UFBGA100 of <i>Table 9:</i><br><i>STM32L15xxC pin definitions</i> Added more alternate functions<br>supported on pin K3 and M4 for UFBGA100 package in <i>Table 9:</i><br><i>STM32L15xxC pin definitions</i><br>Added part number STM32L151CC in <i>Table 1: Device summary</i><br>Updated Stop mode current to 1.5 µA in <i>Ultra-low-power platform</i><br>Updated entire <i>Section 7: Package information</i> |

| 02-Sep-2013 | 4        | Removed UFBGA132 and LQFP144 packages<br>Removed first sentence in Section : I2C interface characteristics<br>Added Section Table 5.: $V_{LCD}$ rail decoupling<br>Added VRAIL functions in Table 9: STM32L15xxC pin definitions<br>Updated PH0-OSC_IN and PH1-OSC_OUT type in Table 9:<br>STM32L15xxC pin definitions.<br>Added Table 6.1.7: Optional LCD power supply scheme.<br>Updated consumption data in Table 6.3.4: Supply current<br>characteristics<br>Updated Table 7: Pin loading conditions<br>Updated Table 7: Pin loading conditions<br>Updated Table 8: Pin input voltage Updated Table 15: Typical<br>application with a 32.768 kHz crystal<br>Updated Table 25: Recommended NRST pin protection<br>Table 26: $I^2$ C bus AC waveforms and measurement circuitUpdated<br>Table 35: Typical connection diagram using the ADC and<br>definition of symbol "RAIN" in Table 77: ADC characteristics<br>Updated Table 49: Thermal resistance suffix 6.<br>Added D2 and E2 in Table 69: UFQFPN48 – ultra thin fine pitch quad<br>flat pack no-lead 7 × 7 mm, 0.5 mm pitch package mechanical data<br>Fixed columns inversion in Table 67: LQFP64, 10 × 10 mm 64-pin low-<br>profile quad flat package mechanical data                                                                               |

| Date        | Revision | 75. Document revision history (continued)<br>Changes                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2410        |          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |          | Updated Section 3.15: Touch sensing.<br>Added V <sub>DD</sub> = 1.71 to 1.8 V operating power supply range in Table 4:<br>Functionalities depending on the working mode (from Run/active down<br>to standby)<br>Renamed "I/O Level" to "I/O structure" in Table 9: STM32L15xxC pin<br>definitions, added the I/O structure for PC14, PC15, PC3, PH0, PH1,<br>PA3, PA4, PA5, PB0, PE7, PE8, PE9, PE10, NRST and BOOT0<br>Updated Table 10: Voltage characteristics added row |

|             |          | Updated <i>Table 11: Current characteristics</i> replaced with the one inside STM32L15xxBxxA datasheet.                                                                                                                                                                                                                                                                                                                                                                     |

|             |          | Updated <i>Table 13: General operating conditions</i> , footnote and added row.                                                                                                                                                                                                                                                                                                                                                                                             |

|             |          | Updated Table 15: Embedded internal reference voltage calibration values and moved inside Section 6.3.3: Embedded internal reference voltage                                                                                                                                                                                                                                                                                                                                |

|             |          | Updated Section 6.3.4: Supply current characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             |          | Updated Table 19: Current consumption in Run mode, code with data processing running from Flash.                                                                                                                                                                                                                                                                                                                                                                            |

|             |          | Updated Table 22: Current consumption in Run mode, code with data processing running from RAM.                                                                                                                                                                                                                                                                                                                                                                              |

|             |          | Created Section 6.3.5: Wakeup time from low-power mode                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             |          | Updated Table 38: High-speed external user clock characteristics.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12-Nov-2013 | 5        | Moved Figure 12: High-speed external clock source AC timing diagram after Table 38: High-speed external user clock characteristics.                                                                                                                                                                                                                                                                                                                                         |

|             |          | Updated Table 40: HSE oscillator characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |          | Updated Section 6.3.12: Electrical sensitivity characteristics (title).                                                                                                                                                                                                                                                                                                                                                                                                     |

|             |          | Updated Section 6.3.13: I/O current injection characteristics.                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |          | Updated <i>Table 61: I/O current injection susceptibility</i> and added footnote.                                                                                                                                                                                                                                                                                                                                                                                           |

|             |          | Updated Table 63: I/O static characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |          | Updated Section 6.3.15: NRST pin characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |          | Updated <i>Table 77: ADC characteristics</i> .<br>Added footnote <sup>(5)</sup> and <sup>(6)</sup> in <i>Table 77: ADC characteristics</i>                                                                                                                                                                                                                                                                                                                                  |

|             |          | Updated THD values and added 4 more rows ENOB, SINAD, SNR,<br>THD in <i>Table 78: ADC accuracy</i>                                                                                                                                                                                                                                                                                                                                                                          |

|             |          | Updated "SDA data hold time" and "SDA and SCL rise time" values<br>and added "Pulse width of spikes that are suppressed by the analog<br>filter" row in <i>Table 68: I<sup>2</sup>C characteristics</i>                                                                                                                                                                                                                                                                     |

|             |          | Updated direct channels VDDA range in <i>Table 79:</i> $R_{AIN}$ max for $f_{ADC} = 16 MHz$                                                                                                                                                                                                                                                                                                                                                                                 |

|             |          | Moved Table 82: Temperature sensor calibration values and moved inside Section 6.3.23: Temperature sensor characteristics                                                                                                                                                                                                                                                                                                                                                   |

|             |          | Updated I <sub>DD</sub> (WU from Standby) unit in <i>Table 31: Typical and maximum current consumptions in Standby mode</i> .                                                                                                                                                                                                                                                                                                                                               |

|             |          | Updated Table 67: LQFP64, 10 x 10 mm 64-pin low-profile quad flat package mechanical data                                                                                                                                                                                                                                                                                                                                                                                   |

|             |          | Updated Chapter 8: Part numbering (title).                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 75. Document revision I | history ( | (continued) |

|-------------------------------|-----------|-------------|

|-------------------------------|-----------|-------------|