Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 51                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 8K x 8                                                                       |

| RAM Size                   | 32K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 21x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LQFP                                                                      |

| Supplier Device Package    | 64-LQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152rct6        |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

7

| 4/136 |      |                  | DocID022799 Rev 12                                          | 57  |

|-------|------|------------------|-------------------------------------------------------------|-----|

| 9     | Revi | sion His         | story                                                       | 131 |

| 8     | Part | number           | ring                                                        | 130 |

|       |      | 7.7.1            | Reference document                                          | 129 |

|       | 7.7  |                  | al characteristics                                          |     |

|       | 7.6  | informa          | P63, 0.400 mm pitch wafer level chip size package ation     |     |

|       |      | array p          | ackage information                                          | 122 |

|       | 7.5  |                  | A100, 7 x 7 mm, 100-ball ultra thin, fine pitch ball grid   |     |

|       | 7.4  | UFQFF            | PN48 7 x 7 mm, 0.5 mm pitch, package information            | -   |

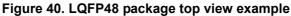

|       | 7.3  | LQFP4<br>informa | 8, 7 x 7 mm, 48-pin low-profile quad flat package ation     | 116 |

|       | 7.2  |                  | 64, 10 x 10 mm, 64-pin low-profile quad flat package ation  |     |

|       | 7.1  |                  | 00, 14 x 14 mm, 100-pin low-profile quad flat package ation | 110 |

| 7     | Pack | age info         | ormation                                                    | 110 |

|       |      | 6.3.22           |                                                             | 109 |

|       |      | 6.3.21           | Comparator                                                  |     |

|       |      | 6.3.20           | Temperature sensor characteristics                          |     |

|       |      | 6.3.19           | Operational amplifier characteristics                       |     |

|       |      | 6.3.18           | DAC electrical specifications                               | 103 |

|       |      | 6.3.17           | 12-bit ADC characteristics                                  | 98  |

|       |      | 6.3.16           | Communications interfaces                                   | 90  |

|       |      | 6.3.15           | TIM timer characteristics                                   |     |

|       |      | 6.3.14           | NRST pin characteristics                                    |     |

|       |      | 6.3.13           | I/O port characteristics                                    |     |

|       |      | 6.3.12           | I/O current injection characteristics                       |     |

|       |      | 6.3.11           | Electrical sensitivity characteristics                      |     |

|       |      | 6.3.10           | EMC characteristics                                         |     |

|       |      | 6.3.9            | Memory characteristics                                      |     |

|       |      | 6.3.8            | PLL characteristics                                         |     |

|       |      | 6.3.7            | Internal clock source characteristics                       |     |

|       |      | 6.3.6            | External clock source characteristics                       |     |

|       |      | 6.3.5            | Wakeup time from low-power mode                             |     |

|       |      | 6.3.4            | Supply current characteristics                              | 60  |

| Figure 46. | UFBGA100, 7 x 7 mm, 0.5 mm pitch, package top view example    | 124 |

|------------|---------------------------------------------------------------|-----|

| Figure 47. | WLCSP63, 0.400 mm pitch wafer level chip size package outline | 125 |

| Figure 48. | WLCSP63 device marking example                                | 127 |

| Figure 49. | Thermal resistance suffix 6                                   | 129 |

| Figure 50. | Thermal resistance suffix 7                                   | 129 |

## 3.12 Operational amplifier

The STM32L151xC and STM32L152xC devices embed two operational amplifiers with external or internal follower routing capability (or even amplifier and filter capability with external components). When one operational amplifier is selected, one external ADC channel is used to enable output measurement.

The operational amplifiers feature:

- Low input bias current

- Low offset voltage

- Low-power mode

- Rail-to-rail input

## 3.13 Ultra-low-power comparators and reference voltage

The STM32L151xC and STM32L152xC devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with fixed threshold

- One comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or a sub-multiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

## 3.14 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM3 and TIM4 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1 and COMP2 and the internal reference voltage  $V_{\text{REFINT}}$ .

## 3.15 Touch sensing

The STM32L151xC and STM32L152xC devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 23 capacitive sensing channels distributed over 10 analog I/O groups. Both software and timer capacitive sensing acquisition modes are supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic...). The capacitive variation

introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. The capacitive sensing acquisition only requires few external components to operate. This acquisition is managed directly by the GPIOs, timers and analog I/O groups (see Section 3.14: System configuration controller and routing interface).

Reliable touch sensing functionality can be quickly and easily implemented using the free STM32L1xx STMTouch touch sensing firmware library.

## 3.16 Timers and watchdogs

The ultra-low-power STM32L151xC and STM32L152xC devices include seven generalpurpose timers, two basic timers, and two watchdog timers.

Table 7 compares the features of the general-purpose and basic timers.

| Timer                  | Counter resolution | Counter type         | Prescaler factor                   | DMA<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |  |  |  |

|------------------------|--------------------|----------------------|------------------------------------|------------------------------|-----------------------------|--------------------------|--|--|--|

| TIM2,<br>TIM3,<br>TIM4 | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | Yes                          | 4                           | No                       |  |  |  |

| TIM5                   | 32-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | Yes                          | 4                           | No                       |  |  |  |

| TIM9                   | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | No                           | 2                           | No                       |  |  |  |

| TIM10,<br>TIM11        | 16-bit             | Up                   | Any integer between<br>1 and 65536 | No                           | 1                           | No                       |  |  |  |

| TIM6,<br>TIM7          | 16-bit             | Up                   | Any integer between<br>1 and 65536 | Yes                          | 0                           | No                       |  |  |  |

Table 7. Timer feature comparison

## 3.16.1 General-purpose timers (TIM2, TIM3, TIM4, TIM5, TIM9, TIM10 and TIM11)

There are seven synchronizable general-purpose timers embedded in the STM32L151xC and STM32L152xC devices (see *Table 7* for differences).

#### TIM2, TIM3, TIM4, TIM5

TIM2, TIM3, TIM4 are based on 16-bit auto-reload up/down counter. TIM5 is based on a 32bit auto-reload up/down counter. They include a 16-bit prescaler. They feature four independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures/output compares/PWMs on the largest packages.

TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together or with the TIM10, TIM11 and TIM9 general-purpose timers via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

DocID022799 Rev 12

|          | Р       | ins    | 140     |                    |                   |                         |                 |                                                     | 2 pin definitions (cont<br>Pin fund           | •                                  |

|----------|---------|--------|---------|--------------------|-------------------|-------------------------|-----------------|-----------------------------------------------------|-----------------------------------------------|------------------------------------|

|          | •       |        |         |                    |                   |                         |                 |                                                     |                                               |                                    |

| UFBGA100 | LQFP100 | LQFP64 | WLCSP63 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I / O Structure | Main<br>function <sup>(2)</sup><br>(after<br>reset) | Alternate functions                           | Additional functions               |

| M6       | 36      | 27     | H3      | 19                 | PB1               | I/O                     | FT              | PB1                                                 | TIM3_CH4/LCD_SEG6                             | ADC_IN9/<br>COMP1_INP/<br>VREF_OUT |

| L6       | 37      | 28     | G3      | 20                 | PB2               | I/O                     | FT              | PB2<br>/BOOT1                                       | BOOT1                                         | VLCDRAIL1/<br>ADCIN0b              |

| M7       | 38      | -      | -       | -                  | PE7               | I/O                     | тс              | PE7                                                 | -                                             | ADC_IN22/<br>COMP1_INP             |

| L7       | 39      | -      | -       | I                  | PE8               | I/O                     | тс              | PE8                                                 | -                                             | ADC_IN23/<br>COMP1_INP             |

| M8       | 40      | -      | -       | I                  | PE9               | I                       | тс              | PE9                                                 | TIM2_CH1_ETR/<br>TIM5_ETR                     | ADC_IN24/<br>COMP1_INP             |

| L8       | 41      | -      | -       | -                  | PE10              | I/O                     | тс              | PE10                                                | TIM2_CH2                                      | ADC_IN25/<br>COMP1_INP             |

| M9       | 42      | -      | -       | -                  | PE11              | I/O                     | FT              | PE11                                                | TIM2_CH3                                      | VLCDRAIL2                          |

| L9       | 43      | -      | -       | -                  | PE12              | I/O                     | FT              | PE12                                                | TIM2_CH4/SPI1_NSS                             | VLCDRAIL3                          |

| M10      | 44      | -      | -       | -                  | PE13              | I/O                     | FT              | PE13                                                | SPI1_SCK                                      | -                                  |

| M11      | 45      | -      | -       | 1                  | PE14              | I/O                     | FT              | PE14                                                | SPI1_MISO                                     | -                                  |

| M12      | 46      | -      | -       | -                  | PE15              | I/O                     | FT              | PE15                                                | SPI1_MOSI                                     | -                                  |

| L10      | 47      | 29     | J2      | 21                 | PB10              | I/O                     | FT              | PB10                                                | TIM2_CH3/I2C2_SCL/<br>USART3_TX/<br>LCD_SEG10 | -                                  |

| L11      | 48      | 30     | H2      | 22                 | PB11              | I/O                     | FT              | PB11                                                | TIM2_CH4/I2C2_SDA/<br>USART3_RX/<br>LCD_SEG11 | -                                  |

| -        | -       | -      | H5      | -                  | V <sub>SS</sub>   | S                       | I               | V <sub>SS</sub>                                     | -                                             | -                                  |

| F12      | 49      | 31     | J1      | 23                 | V <sub>SS_1</sub> | S                       | -               | V <sub>SS_1</sub>                                   | -                                             | -                                  |

| G12      | 50      | 32     | H1      | 24                 | $V_{DD_1}$        | S                       | -               | V <sub>DD_1</sub>                                   | -                                             | -                                  |

#### Table 9. STM32L151xC and STM32L152xC pin definitions (continued)

| r      |                                          | <b>U</b> (                               |     |     |      |

|--------|------------------------------------------|------------------------------------------|-----|-----|------|

| Symbol | Parameter                                | Conditions                               | Min | Мах | Unit |

| Тл     | Ambient temperature for 6 suffix version | Maximum power dissipation <sup>(5)</sup> | -40 | 85  | °C   |

| TA     | Ambient temperature for 7 suffix version | Maximum power dissipation                | -40 | 105 |      |

| TJ     | Junction temperature range               | 6 suffix version                         | -40 | 105 | °C   |

| IJ     |                                          | 7 suffix version                         | -40 | 110 |      |

#### Table 14. General operating conditions (continued)

1. When the ADC is used, refer to Table 56: ADC characteristics.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and up to 140 mV in operation.

3. To sustain a voltage higher than VDD+0.3V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 73: Thermal characteristics on page 128).

In low-power dissipation state, T<sub>A</sub> can be extended to -40°C to 105°C temperature range as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see *Table 73: Thermal characteristics on page 128*).

#### 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the conditions summarized in *Table 14*.

| Symbol                               | Parameter                      | Conditions                                          | Min  | Тур  | Max  | Unit  |  |

|--------------------------------------|--------------------------------|-----------------------------------------------------|------|------|------|-------|--|

|                                      | V <sub>DD</sub> rise time rate | BOR detector enabled                                | 0    | -    | ∞    |       |  |

| t <sub>VDD</sub> <sup>(1)</sup>      |                                | BOR detector disabled                               | 0    | -    | 1000 | μs/V  |  |

| VDD**                                | V foll time rate               | BOR detector enabled                                | 20   | -    | ∞    | μ5/ ν |  |

|                                      | V <sub>DD</sub> fall time rate | BOR detector disabled                               | 0    | -    | 1000 |       |  |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> | Reset temporization            | V <sub>DD</sub> rising, BOR enabled                 | -    | 2    | 3.3  | me    |  |

| 'RSTTEMPO` '                         |                                | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6  | ms    |  |

| N .                                  | Power on/power down reset      | Falling edge                                        | 1    | 1.5  | 1.65 |       |  |

| V <sub>POR/PDR</sub>                 | threshold                      | Rising edge                                         | 1.3  | 1.5  | 1.65 |       |  |

| N                                    | Brown-out reset threshold 0    | Falling edge                                        | 1.67 | 1.7  | 1.74 |       |  |

| V <sub>BOR0</sub>                    |                                | Rising edge                                         | 1.69 | 1.76 | 1.8  | v     |  |

| M                                    | Brown-out reset threshold 1    | Falling edge                                        | 1.87 | 1.93 | 1.97 | v     |  |

| V <sub>BOR1</sub>                    |                                | Rising edge                                         | 1.96 | 2.03 | 2.07 |       |  |

| N .                                  | Brown-out reset threshold 2    | Falling edge                                        | 2.22 | 2.30 | 2.35 |       |  |

| V <sub>BOR2</sub>                    |                                | Rising edge                                         | 2.31 | 2.41 | 2.44 |       |  |

#### Table 15. Embedded reset and power control block characteristics

## 6.3.3 Embedded internal reference voltage

The parameters given in *Table 17* are based on characterization results, unless otherwise specified.

| Table 10. Ellibeuue    | a internal reference voltage                                                        |                           |

|------------------------|-------------------------------------------------------------------------------------|---------------------------|

| Calibration value name | Description                                                                         | Memory address            |

| VREFINT_CAL            | Raw data acquired at<br>temperature of 30 °C ±5 °C<br>V <sub>DDA</sub> = 3 V ±10 mV | 0x1FF8 00F8 - 0x1FF8 00F9 |

#### Table 16. Embedded internal reference voltage calibration values

| Symbol                                  | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                               | Conditions                                                                              | Min   | Тур   | Max   | Unit               |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------------------|

| V <sub>REFINT out</sub> <sup>(1)</sup>  | Internal reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                              | – 40 °C < T <sub>J</sub> < +110 °C                                                      | 1.202 | 1.224 | 1.242 | V                  |

| I <sub>REFINT</sub>                     | Internal reference current consumption                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                       | -     | 1.4   | 2.3   | μΑ                 |

| T <sub>VREFINT</sub>                    | Internal reference startup time                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                       | -     | 2     | 3     | ms                 |

| V <sub>VREF_MEAS</sub>                  | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during<br>V <sub>REFINT</sub> factory measure                                                                                                                                                                                                                                                                                                                                                            | -                                                                                       | 2.99  | 3     | 3.01  | V                  |

| A <sub>VREF_MEAS</sub>                  | Accuracy of factory-measured V <sub>REF</sub> value <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                      | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV                 |

| T <sub>Coeff</sub> <sup>(3)</sup>       | Temperature coefficient                                                                                                                                                                                                                                                                                                                                                                                                                                 | –40 °C < T <sub>J</sub> < +110 °C                                                       | -     | 25    | 100   | ppm/°<br>C         |

| A <sub>Coeff</sub> <sup>(3)</sup>       | Long-term stability                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm                |

| V <sub>DDCoeff</sub> <sup>(3)</sup>     | Voltage coefficient                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V              |

| T <sub>S_vrefint</sub> <sup>(3)</sup>   | ADC sampling time when reading the internal reference voltage                                                                                                                                                                                                                                                                                                                                                                                           | -                                                                                       | 4     | -     | -     | μs                 |

| T <sub>ADC_BUF</sub> <sup>(3) (4)</sup> | Startup time of reference voltage buffer for ADC                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                       | -     | -     | 10    | μs                 |

| I <sub>BUF_ADC</sub> <sup>(3)</sup>     | Consumption of reference voltage buffer for ADC                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                       | -     | 13.5  | 25    | μA                 |

| I <sub>VREF_OUT</sub> <sup>(3)</sup>    | VREF_OUT output current <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                       | -     | -     | 1     | μA                 |

| C <sub>VREF_OUT</sub> <sup>(3)</sup>    | VREF_OUT output load                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                       | -     | -     | 50    | pF                 |

| I <sub>LPBUF</sub> <sup>(3)</sup>       | Consumption of reference voltage<br>buffer for VREF_OUT and COMP                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                       | -     | 730   | 1200  | nA                 |

| V <sub>REFINT_DIV1</sub> <sup>(3)</sup> | 1/4 reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                                       | 24    | 25    | 26    | %                  |

| V <sub>REFINT_DIV2</sub> <sup>(3)</sup> | 1/2 reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                                       | 49    | 50    | 51    | V <sub>REFIN</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(3)</sup> | ACoeffLong-term stabilityVDDCoeffVoltage coefficientTS_vrefintADC sampling time when reading<br>the internal reference voltageADC_BUFStartup time of reference voltage<br>buffer for ADCBUF_ADCConsumption of reference voltage<br>buffer for ADCVREF_OUTVREF_OUT output current (5)VREF_OUTVREF_OUT output loadI_LPBUFConsumption of reference voltage<br>buffer for VREF_OUT and COMPREFINT_DIV11/4 reference voltageREFINT_DIV21/2 reference voltage | -                                                                                       | 74    | 75    | 76    | Т                  |

#### Table 17. Embedded internal reference voltage

1. Guaranteed by test in production.

2. The internal  $V_{REF}$  value is individually measured in production and stored in dedicated EEPROM bytes.

3. Guaranteed by characterization results.

4. Shortest sampling time can be determined in the application by multiple iterations.

DocID022799 Rev 12

| Symbol                                                 | Parameter                   | Conc                                                      | litions                                               | f <sub>HCLK</sub> | Тур   | Max <sup>(1)</sup> | Unit |

|--------------------------------------------------------|-----------------------------|-----------------------------------------------------------|-------------------------------------------------------|-------------------|-------|--------------------|------|

|                                                        |                             |                                                           | Range 3,                                              | 1 MHz             | 185   | 240                |      |

|                                                        |                             |                                                           | V <sub>CORE</sub> =1.2 V VOS[1:0]                     | 2 MHz             | 345   | 410                | μA   |

|                                                        |                             | f <sub>HSE</sub> = f <sub>HCLK</sub>                      | = 11                                                  | 4 MHz             | 645   | 880 <sup>(3)</sup> |      |

|                                                        |                             | up to 16 MHz,                                             | Range 2,                                              | 4 MHz             | 0.755 | 1.4                |      |

|                                                        |                             | included<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above | V <sub>CORE</sub> =1.5 V VOS[1:0]                     | 8 MHz             | 1.5   | 2.1                |      |

|                                                        |                             | 16 MHz                                                    | = 10                                                  | 16 MHz            | 3     | 3.5                |      |

|                                                        | Supply surrent in           | (PLL ON) <sup>(2)</sup>                                   | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 8 MHz             | 1.8   | 2.8                |      |

| Supply current i<br>I <sub>DD</sub> (Run Run mode, cod | Run mode, code              |                                                           |                                                       | 16 MHz            | 3.6   | 4.1                |      |

| from<br>RAM)                                           | executed from<br>RAM, Flash |                                                           |                                                       | 32 MHz            | 7.15  | 8.3                | mA   |

|                                                        | switched off                | HSI clock source (16                                      | Range 2,<br>V <sub>CORE</sub> =1.5 V VOS[1:0]<br>= 10 | 16 MHz            | 2.95  | 3.5                |      |

|                                                        |                             | MHz)                                                      | Range 1,<br>V <sub>CORE</sub> =1.8 V VOS[1:0]<br>= 01 | 32 MHz            | 7.15  | 8.4                |      |

|                                                        | MSI clock, 65 kHz           | Range 3,                                                  | 65 kHz                                                | 38.5              | 85    |                    |      |

|                                                        |                             | MSI clock, 524 kHz                                        | V <sub>CORE</sub> =1.2 V VOS[1:0]                     | 524 kHz           | 110   | 160                | μA   |

|                                                        |                             | MSI clock, 4.2 MHz                                        | = 11                                                  | 4.2 MHz           | 690   | 810                |      |

#### Table 19. Current consumption in Run mode, code with data processing running from RAM

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

3. Guaranteed by test in production.

| Symbol                          | Parameter                                          |                                            | Conditions                                      |                                          |     |     | Unit |

|---------------------------------|----------------------------------------------------|--------------------------------------------|-------------------------------------------------|------------------------------------------|-----|-----|------|

|                                 |                                                    |                                            |                                                 | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$  | 8.6 | 12  |      |

|                                 |                                                    |                                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | T <sub>A</sub> = 85 °C                   | 19  | 25  |      |

|                                 |                                                    | All<br>peripherals                         |                                                 | T <sub>A</sub> = 105 °C                  | 35  | 47  |      |

|                                 |                                                    | OFF, code                                  |                                                 | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 14  | 16  |      |

|                                 |                                                    | executed<br>from RAM,                      | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | T <sub>A</sub> = 85 °C                   | 24  | 29  |      |

|                                 |                                                    | Flash<br>switched                          |                                                 | T <sub>A</sub> = 105 °C                  | 40  | 51  |      |

|                                 |                                                    | OFF, V <sub>DD</sub>                       |                                                 | $T_A = -40 \degree C$ to 25 $\degree C$  | 26  | 29  |      |

|                                 |                                                    | from 1.65 V<br>to 3.6 V                    | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                   | 28  | 31  |      |

|                                 | Supply<br>current in<br>Low-power<br>run mode      | 10 0.0 V                                   | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                   | 36  | 42  | μA   |

| I <sub>DD (LP</sub>             |                                                    |                                            |                                                 | T <sub>A</sub> = 105 °C                  | 52  | 64  |      |

| Run)                            |                                                    | All                                        | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | $T_A = -40 \degree C$ to 25 $\degree C$  | 20  | 24  |      |

|                                 | run mode                                           |                                            |                                                 | T <sub>A</sub> = 85 °C                   | 32  | 37  |      |

|                                 |                                                    |                                            |                                                 | T <sub>A</sub> = 105 °C                  | 49  | 61  |      |

|                                 |                                                    | peripherals                                | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$  | 26  | 30  |      |

|                                 |                                                    | OFF, code<br>executed                      |                                                 | T <sub>A</sub> = 85 °C                   | 38  | 44  |      |

|                                 |                                                    | from Flash,                                |                                                 | T <sub>A</sub> = 105 °C                  | 55  | 67  |      |

|                                 |                                                    | V <sub>DD</sub> from<br>1.65 V to          |                                                 | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$  | 41  | 46  |      |

|                                 |                                                    | 3.6 V                                      | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                   | 44  | 50  |      |

|                                 |                                                    |                                            | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                   | 56  | 87  |      |

|                                 |                                                    |                                            |                                                 | T <sub>A</sub> = 105 °C                  | 73  | 110 |      |

| I <sub>DD</sub> max<br>(LP Run) | Max allowed<br>current in<br>Low-power<br>run mode | V <sub>DD</sub> from<br>1.65 V to<br>3.6 V | -                                               | -                                        | -   | 200 |      |

Table 21. Current consumption in Low-power run mode

1. Guaranteed by characterization results, unless otherwise specified.

| Symbol                 | Parameter                           | Conditions                                                                        |                                       | Тур   | Max <sup>(1)</sup> | Unit |

|------------------------|-------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------|-------|--------------------|------|

|                        |                                     | Regulator in LP mode, HSI and<br>HSE OFF, independent<br>watchdog and LSI enabled | $T_A = -40^{\circ}C$ to $25^{\circ}C$ | 1.8   | 2.2                |      |

| I <sub>DD</sub> (Stop) | Supply current in<br>Stop mode (RTC |                                                                                   | $T_A = -40^{\circ}C$ to $25^{\circ}C$ | 0.435 | 1                  | μA   |

| .00(                   | disabled)                           | Regulator in LP mode, LSI, HSI<br>and HSE OFF (no independent<br>watchdog)        | T <sub>A</sub> = 55°C                 | 0.99  | 3                  | P    |

|                        |                                     |                                                                                   | T <sub>A</sub> = 85°C                 | 2.4   | 9                  |      |

|                        |                                     |                                                                                   | T <sub>A</sub> = 105°C                | 5.5   | 22 <sup>(5)</sup>  |      |

| I <sub>DD</sub>        | Supply current during               | MSI = 4.2 MHz                                                                     |                                       | 2     | -                  |      |

| (WU from<br>Stop)      | wakeup from Stop                    | MSI = 1.05 MHz                                                                    | $T_A = -40^{\circ}C$ to $25^{\circ}C$ | 1.45  | -                  | mA   |

|                        | mode                                | MSI = 65 kHz <sup>(6)</sup>                                                       |                                       | 1.45  | -                  |      |

| Table 23. Typical and maximum of | current consumptions ir | Stop mode | (continued) |

|----------------------------------|-------------------------|-----------|-------------|

|----------------------------------|-------------------------|-----------|-------------|

1. Guaranteed by characterization results, unless otherwise specified.

2. LCD enabled with external VLCD, static duty, division ratio = 256, all pixels active, no LCD connected.

3. LCD enabled with external VLCD, 1/8 duty, 1/3 bias, division ratio = 64, all pixels active, no LCD connected.

4. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

5. Guaranteed by test in production.

When MSI = 64 kHz, the RMS current is measured over the first 15 µs following the wakeup event. For the remaining part

of the wakeup period, the current corresponds the Run mode current.

| Symbol                                | Parameter Conditi                  |                                                                                                                                                                                                                                                                                                                                                                                             | Тур   | Max | Unit |  |

|---------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|--|

|                                       |                                    | MSI range 0                                                                                                                                                                                                                                                                                                                                                                                 | -     | 40  |      |  |

|                                       |                                    | MSI range 0         -         40           MSI range 1         -         20           MSI range 2         -         10           MSI range 3         -         4           MSI range 4         -         2.5           MSI range 5         -         2           MSI range 6,<br>Voltage range 1<br>and 2         -         2           MSI range 3,<br>Voltage range 3         -         3 |       |     |      |  |

|                                       |                                    | MSI range 2                                                                                                                                                                                                                                                                                                                                                                                 | -     | 10  |      |  |

|                                       |                                    | MSI range 3 - 4                                                                                                                                                                                                                                                                                                                                                                             |       |     |      |  |

| t <sub>stab(MSI)</sub> <sup>(2)</sup> | MSI oscillator stabilization time  | MSI range 4                                                                                                                                                                                                                                                                                                                                                                                 | -     | 2.5 | μs   |  |

|                                       |                                    | MSI range 5                                                                                                                                                                                                                                                                                                                                                                                 | -     | 2   |      |  |

|                                       |                                    | Voltage range 1                                                                                                                                                                                                                                                                                                                                                                             | 1 - 2 |     |      |  |

|                                       |                                    |                                                                                                                                                                                                                                                                                                                                                                                             | -     | - 3 |      |  |

| f <sub>OVER(MSI)</sub>                | MSI oscillator frequency overshoot | Any range to<br>range 5                                                                                                                                                                                                                                                                                                                                                                     | -     | - 4 |      |  |

|                                       |                                    | Any range to<br>range 6                                                                                                                                                                                                                                                                                                                                                                     | -     | 6   | MHz  |  |

Table 33. MSI oscillator characteristics (continued)

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results.

## 6.3.13 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 49* are derived from tests performed under the conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol                                  | Parameter                                                                         | Parameter Conditions Min                                                                  |                                           | Тур                                | Мах                                   | Unit |

|-----------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------|---------------------------------------|------|

| V <sub>IL</sub> Input low level voltage |                                                                                   | TC and FT I/O                                                                             | -                                         | -                                  | 0.3 V <sub>DD</sub> <sup>(1)(2)</sup> |      |

|                                         |                                                                                   | BOOT0                                                                                     | -                                         | -                                  | 0.14 V <sub>DD</sub> <sup>(2)</sup>   |      |

|                                         |                                                                                   | TC I/O                                                                                    | 0.45 V <sub>DD</sub> +0.38 <sup>(2)</sup> | -                                  | -                                     |      |

| $V_{\text{IH}}$                         | Input high level voltage                                                          | FT I/O                                                                                    | 0.39 V <sub>DD</sub> +0.59 <sup>(2)</sup> | -                                  | -                                     | V    |

|                                         |                                                                                   | BOOT0                                                                                     | 0.15 V <sub>DD</sub> +0.56 <sup>(2)</sup> | -                                  | -                                     |      |

| V                                       | I/O Schmitt trigger voltage                                                       | TC and FT I/O                                                                             | -                                         | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                     |      |

| V <sub>hys</sub>                        | hysteresis <sup>(2)</sup>                                                         | BOOT0                                                                                     | -                                         | 0.01                               | -                                     |      |

|                                         | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with LCD                | -                                                                                         | -                                         | ±50                                |                                       |      |

|                                         | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches | -                                                                                         | -                                         | ±50                                |                                       |      |

| l <sub>lkg</sub>                        | Input leakage current <sup>(4)</sup>                                              | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches and LCD | -                                         | -                                  | ±50                                   | nA   |

|                                         |                                                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with USB                        | -                                         | -                                  | ±250                                  |      |

|                                         |                                                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>TC and FT I/Os                       | -                                         | -                                  | ±50                                   |      |

|                                         | FT I/O<br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤5V                                    | -                                                                                         | -                                         | ±10                                | μA                                    |      |

| R <sub>PU</sub>                         | Weak pull-up equivalent resistor <sup>(5)(1)</sup>                                | $V_{IN} = V_{SS}$                                                                         | 30                                        | 45                                 | 60                                    | kΩ   |

| R <sub>PD</sub>                         | Weak pull-down equivalent resistor <sup>(5)</sup>                                 | $V_{IN} = V_{DD}$                                                                         | 30                                        | 45                                 | 60                                    | kΩ   |

| C <sub>IO</sub>                         | I/O pin capacitance                                                               | -                                                                                         | -                                         | 5                                  | -                                     | pF   |

| Table 43. | I/O static | characteristics |

|-----------|------------|-----------------|

|           |            | onuluotonotioo  |

1. Guaranteed by test in production

2. Guaranteed by design.

3. With a minimum of 200 mV.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

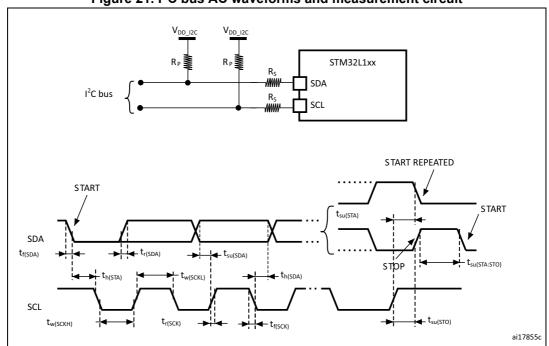

Figure 21. I<sup>2</sup>C bus AC waveforms and measurement circuit

- 1.  $R_S$  = series protection resistor.

- 2. R<sub>P</sub> = external pull-up resistor.

- 3.  $V_{DD\_12C}$  is the I2C bus power supply.

- 4. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

| f (kHz)                | I2C_CCR value           |  |

|------------------------|-------------------------|--|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |  |

| 400                    | 0x801B                  |  |

| 300                    | 0x8024                  |  |

| 200                    | 0x8035                  |  |

| 100                    | 0x00A0                  |  |

| 50                     | 0x0140                  |  |

| 20                     | 0x0320                  |  |

## Table 49. SCL frequency ( $f_{PCLK1}$ = 32 MHz, $V_{DD} = V_{DD_{12C}} = 3.3 V$ )<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed.

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed is ±2%. These variations depend on the accuracy of the external components used to design the application.

#### **SPI characteristics**

Unless otherwise specified, the parameters given in the following table are derived from tests performed under the conditions summarized in *Table 14*.

Refer to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | ol Parameter Conditions          |                            | Min                   | Max <sup>(2)</sup>    | Unit |  |

|----------------------------------------------------------------------------|----------------------------------|----------------------------|-----------------------|-----------------------|------|--|

| -                                                                          |                                  | Master mode                | -                     | 16                    |      |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency              | Slave mode                 | -                     | 16                    | MHz  |  |

|                                                                            |                                  | Slave transmitter          | -                     | 12 <sup>(3)</sup>     |      |  |

| $t_{r(SCK)}^{(2)}_{t_{f(SCK)}^{(2)}}$                                      | SPI clock rise and fall time     | Capacitive load: C = 30 pF | -                     | 6                     | ns   |  |

| DuCy(SCK)                                                                  | SPI slave input clock duty cycle | Slave mode                 | 30                    | 70                    | %    |  |

| t <sub>su(NSS)</sub>                                                       | NSS setup time                   | Slave mode                 | 4t <sub>HCLK</sub>    | -                     |      |  |

| t <sub>h(NSS)</sub>                                                        | NSS hold time                    | Slave mode                 | 2t <sub>HCLK</sub>    | -                     |      |  |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time            | Master mode                | t <sub>SCK</sub> /2-5 | t <sub>SCK</sub> /2+3 |      |  |

| t <sub>su(MI)</sub> <sup>(2)</sup>                                         | Data input actus time            | Master mode                | 5                     | -                     |      |  |

| t <sub>su(SI)</sub> <sup>(2)</sup>                                         | Data input setup time            | Slave mode                 | 6                     | -                     |      |  |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                          | Deta input hold time             | Master mode                | 5                     | -                     | ns   |  |

| t <sub>h(SI)</sub> <sup>(2)</sup>                                          | Data input hold time             | Slave mode                 | 5                     | -                     |      |  |

| t <sub>a(SO)</sub> <sup>(4)</sup>                                          | Data output access time          | Slave mode                 | 0                     | 3t <sub>HCLK</sub>    |      |  |

| t <sub>v(SO)</sub> (2)                                                     | Data output valid time           | Slave mode                 | -                     | 33                    |      |  |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time           | Master mode                | -                     | 6.5                   |      |  |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Slave mode                 | 17                    | -                     |      |  |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Master mode                | 0.5                   | -                     |      |  |

Table 50. SPI characteristics<sup>(1)</sup>

1. The characteristics above are given for voltage range 1.

2. Guaranteed by characterization results.

3. The maximum SPI clock frequency in slave transmitter mode is given for an SPI slave input clock duty cycle (DuCy(SCK)) ranging between 40 to 60%.

4. Min time is for the minimum time to drive the output and max time is for the maximum time to validate the data.

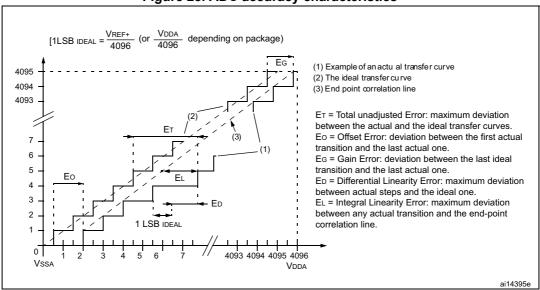

#### Figure 28. ADC accuracy characteristics

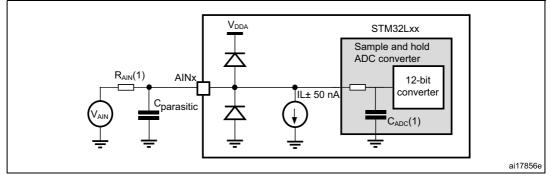

- 1. Refer to Table 58: Maximum source impedance RAIN max for the value of  $R_{AIN}$  and Table 56: ADC characteristics for the value of  $C_{ADC}$ .

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

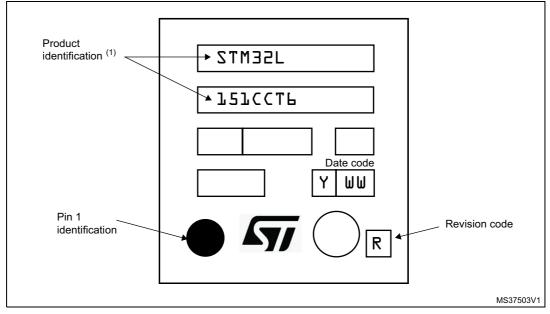

#### Marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity

## 7.4 UFQFPN48 7 x 7 mm, 0.5 mm pitch, package information

Figure 41. UFQFPN48 7 x 7 mm, 0.5 mm pitch, package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| А      | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |

| D      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| E      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| D2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| E2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| Т      | -           | 0.152 | -     | -                     | 0.0060 | -      |

| b      | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |

## Table 69. UFQFPN48 – ultra thin fine pitch quad flat pack no-lead 7 × 7 mm,0.5 mm pitch package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

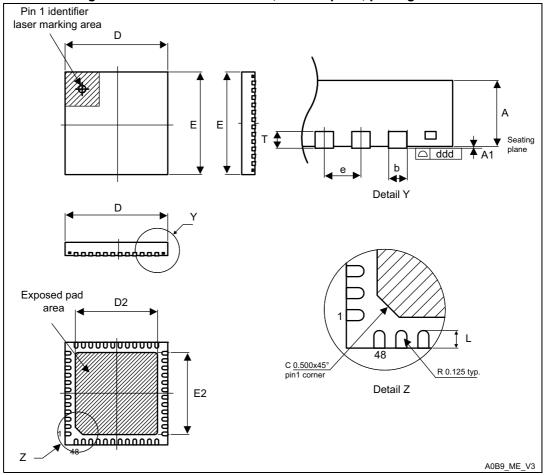

#### Figure 42. UFQFPN48 recommended footprint

1. Dimensions are in millimeters.

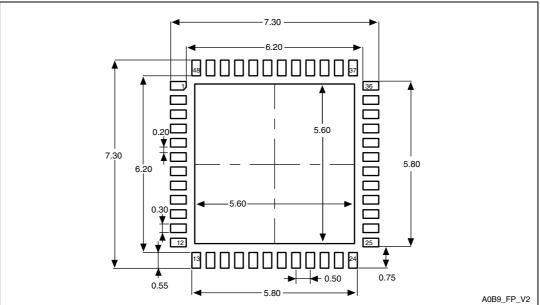

# 7.6 WLCSP63, 0.400 mm pitch wafer level chip size package information

Figure 47. WLCSP63, 0.400 mm pitch wafer level chip size package outline

1. Drawing is not to scale.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID022799 Rev 12