# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 83                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 8K x 8                                                                       |

| RAM Size                   | 32K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 25x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

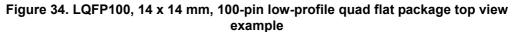

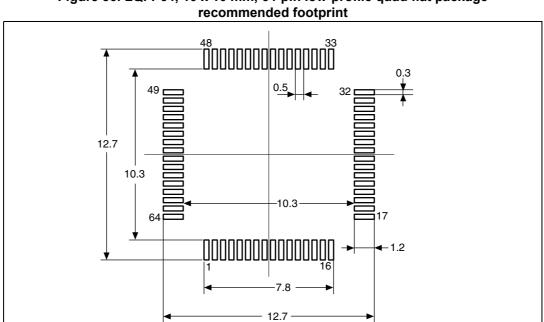

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152vct6        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• **Stop** mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and HSE crystal oscillators are disabled. The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB wakeup.

• **Standby** mode with RTC

Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI RC and HSE crystal oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

• Standby mode without RTC

Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

|                                                                                      | Functionalities depending on the operating power supply range |                |                                   |                            |  |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------|-----------------------------------|----------------------------|--|--|

| Operating power supply range                                                         | DAC and ADC operation                                         | USB            | Dynamic voltage<br>scaling range  | I/O operation              |  |  |

| V <sub>DD</sub> = V <sub>DDA</sub> = 1.65 to 1.71 V                                  | Not functional                                                | Not functional | Range 2 or<br>Range 3             | Degraded speed performance |  |  |

| $V_{DD} = V_{DDA} = 1.71 \text{ to } 1.8 \text{ V}^{(1)}$                            | Not functional                                                | Not functional | Range 1, Range 2<br>or Range 3    | Degraded speed performance |  |  |

| $V_{DD}=V_{DDA}= 1.8 \text{ to } 2.0 \text{ V}^{(1)}$ Conversion time up to 500 Ksps |                                                               | Not functional | Range 1, Range 2<br>or<br>Range 3 | Degraded speed performance |  |  |

#### Table 3. Functionalities depending on the operating power supply range

power ramp-up should guarantee that 1.65 V is reached on  $V_{\text{DD}}$  at least 1 ms after it exits the POR area.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

#### 3.3.3 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32K osc, RCC\_CSR).

#### 3.3.4 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using USART1, USART2 or USB. See Application note "STM32 microcontroller system memory boot mode" (AN2606) for details.

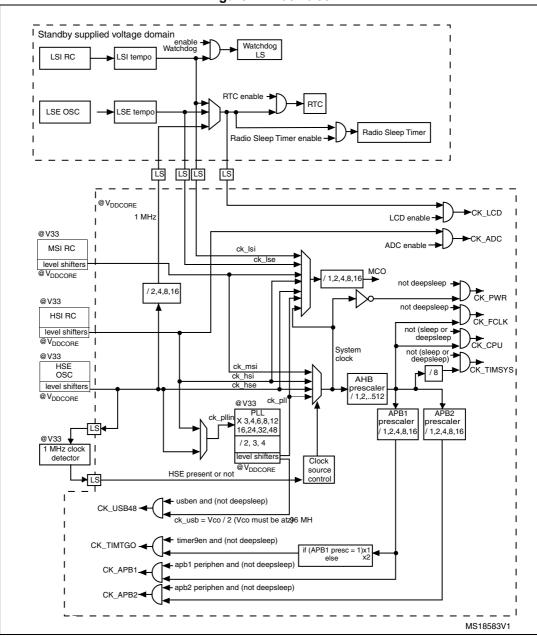

Figure 2. Clock tree

### 3.9 LCD (liquid crystal display)

The LCD drives up to 8 common terminals and 44 segment terminals to drive up to 320 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

- V<sub>LCD</sub> rail decoupling capability

|                       |                      | LOD                  | 1 0                  |       |      |

|-----------------------|----------------------|----------------------|----------------------|-------|------|

|                       |                      | Bias                 | В                    | in    |      |

|                       | 1/2                  | 1/3                  | 1/4                  | - Pin |      |

| V <sub>LCDRAIL1</sub> | 1/2 V <sub>LCD</sub> | 2/3 V <sub>LCD</sub> | 1/2 V <sub>LCD</sub> | PB2   |      |

| V <sub>LCDRAIL2</sub> | N/A                  | 1/3 V <sub>LCD</sub> | 1/4 V <sub>LCD</sub> | PB12  | PE11 |

| V <sub>LCDRAIL3</sub> | N/A                  | N/A                  | 3/4 V <sub>LCD</sub> | PB0   | PE12 |

#### Table 6. V<sub>LCD</sub> rail decoupling

### 3.10 ADC (analog-to-digital converter)

A 12-bit analog-to-digital converters is embedded into STM32L151xC and STM32L152xC devices with up to 25 external channels, performing conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs with up to 24 external channels in a group.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers. An injection mode allows high priority conversions to be done by interrupting a scan mode which runs in as a background task.

The ADC includes a specific low-power mode. The converter is able to operate at maximum speed even if the CPU is operating at a very low frequency and has an auto-shutdown function. The ADC's runtime and analog front-end current consumption are thus minimized whatever the MCU operating mode.

### 3.12 Operational amplifier

The STM32L151xC and STM32L152xC devices embed two operational amplifiers with external or internal follower routing capability (or even amplifier and filter capability with external components). When one operational amplifier is selected, one external ADC channel is used to enable output measurement.

The operational amplifiers feature:

- Low input bias current

- Low offset voltage

- Low-power mode

- Rail-to-rail input

### 3.13 Ultra-low-power comparators and reference voltage

The STM32L151xC and STM32L152xC devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with fixed threshold

- One comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or a sub-multiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

### 3.14 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM3 and TIM4 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1 and COMP2 and the internal reference voltage  $V_{\text{REFINT}}$ .

### 3.15 Touch sensing

The STM32L151xC and STM32L152xC devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 23 capacitive sensing channels distributed over 10 analog I/O groups. Both software and timer capacitive sensing acquisition modes are supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic...). The capacitive variation

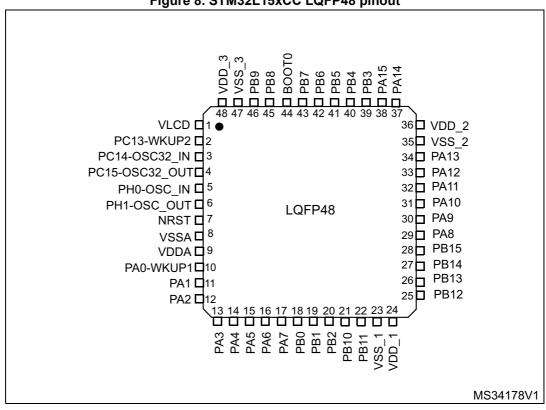

Figure 8. STM32L15xCC LQFP48 pinout

1. This figure shows the package top view.

| Table 9. STM32L151xC and STM32L152xC Pins |         |        |         |                    |                   |                         |                 |                                                     |                                                                         |                      |  |  |

|-------------------------------------------|---------|--------|---------|--------------------|-------------------|-------------------------|-----------------|-----------------------------------------------------|-------------------------------------------------------------------------|----------------------|--|--|

|                                           | P       | rins   |         |                    |                   |                         |                 |                                                     | Pin functions                                                           |                      |  |  |

| UFBGA100                                  | LQFP100 | rgfp64 | MLCSP63 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I / O Structure | Main<br>function <sup>(2)</sup><br>(after<br>reset) | Alternate functions                                                     | Additional functions |  |  |

| E11                                       | 64      | 38     | E1      | -                  | PC7               | I/O                     | FT              | PC7                                                 | TIM3_CH2/I2S3_MCK/<br>LCD_SEG25                                         | -                    |  |  |

| E10                                       | 65      | 39     | D1      | -                  | PC8               | I/O                     | FT              | PC8                                                 | TIM3_CH3/LCD_SEG26                                                      | -                    |  |  |

| D12                                       | 66      | 40     | E2      | -                  | PC9               | I/O                     | FT              | PC9                                                 | TIM3_CH4/LCD_SEG27                                                      | -                    |  |  |

| D11                                       | 67      | 41     | E3      | 29                 | PA8               | I/O                     | FT              | PA8                                                 | USART1_CK/MCO/<br>LCD_COM0                                              | -                    |  |  |

| D10                                       | 68      | 42     | C1      | 30                 | PA9               | I/O                     | FT              | PA9                                                 | USART1_TX/<br>LCD_COM1                                                  | -                    |  |  |

| C12                                       | 69      | 43     | D2      | 31                 | PA10              | I/O                     | FT              | PA10                                                | USART1_RX/<br>LCD_COM2                                                  | -                    |  |  |

| B12                                       | 70      | 44     | B1      | 32                 | PA11              | I/O                     | FT              | PA11                                                | USART1_CTS/<br>SPI1_MISO                                                | USB_DM               |  |  |

| A12                                       | 71      | 45     | D3      | 33                 | PA12              | I/O                     | FT              | PA12                                                | USART1_RTS/<br>SPI1_MOSI                                                | USB_DP               |  |  |

| A11                                       | 72      | 46     | C2      | 34                 | PA13              | I/O                     | FT              | JTMS-<br>SWDIO                                      | JTMS-SWDIO                                                              | -                    |  |  |

| C11                                       | 73      | -      | -       | -                  | PH2               | I/O                     | FT              | PH2                                                 | -                                                                       | -                    |  |  |

| F11                                       | 74      | 47     | A1      | 35                 | V <sub>SS_2</sub> | S                       | -               | V <sub>SS_2</sub>                                   | -                                                                       | -                    |  |  |

| G11                                       | 75      | 48     | B2      | 36                 | V <sub>DD_2</sub> | S                       | -               | V <sub>DD_2</sub>                                   | -                                                                       | -                    |  |  |

| A10                                       | 76      | 49     | C3      | 37                 | PA14              | I/O                     | FT              | JTCK-<br>SWCLK                                      | JTCK-SWCLK                                                              | -                    |  |  |

| A9                                        | 77      | 50     | A2      | 38                 | PA15              | I/O                     | FT              | JTDI                                                | TIM2_CH1_ETR/<br>SPI1_NSS/<br>SPI3_NSS/I2S3_WS/<br>LCD_SEG17/JTDI       | -                    |  |  |

| B11                                       | 78      | 51     | В3      | -                  | PC10              | I/O                     | FT              | PC10                                                | SPI3_SCK/I2S3_CK/<br>USART3_TX/<br>LCD_SEG28/<br>LCD_SEG40/<br>LCD_COM4 | _                    |  |  |

#### Table 9. STM32L151xC and STM32L152xC pin definitions (continued)

STM32L151xC STM32L152xC

| Pin          |

|--------------|

| descriptions |

|               | Digital alternate function number |                    |          |                |        |                      |       |            |        |          |           |  |  |

|---------------|-----------------------------------|--------------------|----------|----------------|--------|----------------------|-------|------------|--------|----------|-----------|--|--|

| Port          | AFIO0                             | AFIO1              | AFIO2    | AFIO3          | AFIO4  | AFIO5                | AFIO6 | AFIO7      | AFIO11 | AFIO14   | AFIO15    |  |  |

| name          |                                   | Alternate function |          |                |        |                      |       |            |        |          |           |  |  |

|               | SYSTEM                            | TIM2               | TIM3/4/5 | TIM9/<br>10/11 | I2C1/2 | SPI1/2               | SPI3  | USART1/2/3 | LCD    | CPRI     | SYSTEM    |  |  |

| PD3           | -                                 | -                  | -        | -              | -      | SPI2_MISO            | -     | USART2_CTS | -      | TIMx_IC4 | EVENT OUT |  |  |

| PD4           | -                                 | -                  | -        | -              | -      | SPI2_MOSI<br>I2S2_SD | -     | USART2_RTS | -      | TIMx_IC1 | EVENT OUT |  |  |

| PD5           | -                                 | -                  | -        | -              | -      |                      | -     | USART2_TX  | -      | TIMx_IC2 | EVENT OU  |  |  |

| PD6           | -                                 | -                  | -        |                | -      | -                    | -     | USART2_RX  | -      | TIMx_IC3 | EVENT OUT |  |  |

| PD7           | -                                 | -                  | -        | TIM9_CH2       | -      | -                    | -     | USART2_CK  | -      | TIMx_IC4 | EVENT OU  |  |  |

| PD8           | -                                 | -                  | -        | -              | -      | -                    | -     | USART3_TX  | SEG28  | TIMx_IC1 | EVENT OUT |  |  |

| PD9           | -                                 | -                  | -        | -              | -      | -                    | -     | USART3_RX  | SEG29  | TIMx_IC2 | EVENT OUT |  |  |

| PD10          | -                                 | -                  | -        | -              | -      | -                    | -     | USART3_CK  | SEG30  | TIMx_IC3 | EVENT OUT |  |  |

| PD11          | -                                 | -                  | -        | -              | -      | -                    | -     | USART3_CTS | SEG31  | TIMx_IC4 | EVENT OUT |  |  |

| PD12          | -                                 | -                  | TIM4_CH1 | -              | -      | -                    | -     | USART3_RTS | SEG32  | TIMx_IC1 | EVENT OU  |  |  |

| PD13          | -                                 | -                  | TIM4_CH2 | -              | -      | -                    | -     | -          | SEG33  | TIMx_IC2 | EVENT OUT |  |  |

| PD14          | -                                 | -                  | TIM4_CH3 | -              | -      | -                    | -     | -          | SEG34  | TIMx_IC3 | EVENT OUT |  |  |

| PD15          | -                                 | -                  | TIM4_CH4 | -              | -      | -                    | -     | -          | SEG35  | TIMx_IC4 | EVENT OU  |  |  |

| PE0           | -                                 | -                  | TIM4_ETR | TIM10_CH1      | -      | -                    | -     | -          | SEG36  | TIMx_IC1 | EVENT OUT |  |  |

| PE1           | -                                 | -                  | -        | TIM11_CH1      | -      | -                    | -     | -          | SEG37  | TIMx_IC2 | EVENT OUT |  |  |

| PE2           | TRACECK                           | -                  | TIM3_ETR | -              |        |                      |       | -          | SEG 38 | TIMx_IC3 | EVENT OUT |  |  |

| PE3           | TRACED0                           | -                  | TIM3_CH1 | -              | -      | -                    | -     | -          | SEG 39 | TIMx_IC4 | EVENT OUT |  |  |

| PE4           | TRACED1                           | -                  | TIM3_CH2 | -              | -      | -                    | -     | -          | -      | TIMx_IC1 | EVENT OUT |  |  |

| PE5           | TRACED2                           | -                  | -        | TIM9_CH1       | -      | -                    | -     | -          | -      | TIMx_IC2 | EVENT OUT |  |  |

| PE6-<br>WKUP3 | TRACED3                           | -                  | -        | TIM9_CH2       | -      | -                    | -     | -          | -      | TIMx_IC3 | EVENT OU  |  |  |

| PE7           | -                                 | -                  | -        | -              | -      | -                    | -     | -          | -      | TIMx_IC4 | EVENT OU  |  |  |

#### . 4 : . . . 4 . . 40 A 14 ..... E. :..

DocID022799 Rev 12

49/136

577

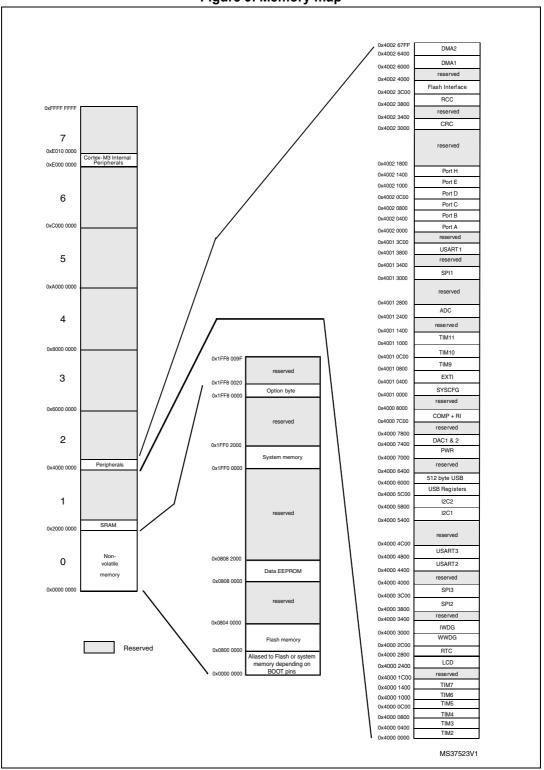

### 5 Memory mapping

Figure 9. Memory map

5. To guarantee less than 1% VREF\_OUT deviation.

#### 6.3.4 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code. The current consumption is measured as described in *Figure 14: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to the Dhrystone 2.1 code, unless otherwise specified. The current consumption values are derived from tests performed under ambient temperature  $T_A = 25$  °C and  $V_{DD}$  supply voltage conditions summarized in *Table 14: General operating conditions*, unless otherwise specified.

The MCU is placed under the following conditions:

- All I/O pins are configured in analog input mode

- All peripherals are disabled except when explicitly mentioned.

- The Flash memory access time, 64-bit access and prefetch is adjusted depending on f<sub>HCLK</sub> frequency and voltage range to provide the best CPU performance.

- When the peripherals are enabled  $f_{APB1} = f_{APB2} = f_{AHB}$ .

- When PLL is ON, the PLL inputs are equal to HSI = 16 MHz (if internal clock is used) or HSE = 16 MHz (if HSE bypass mode is used).

- The HSE user clock applied to OSCI\_IN input follows the characteristic specified in *Table 27: High-speed external user clock characteristics*.

- For maximum current consumption  $V_{DD} = V_{DDA} = 3.6$  V is applied to all supply pins.

- For typical current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.0 V is applied to all supply pins if not specified otherwise.

| Symbol                            | Parameter                                               |                                              | Conditions                                                     |                                         | Тур | Max <sup>(1)</sup> | Unit |

|-----------------------------------|---------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------|-----------------------------------------|-----|--------------------|------|

|                                   |                                                         |                                              | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz<br>Flash OFF   | T <sub>A</sub> = -40 °C to 25 °C        | 4.4 | -                  |      |

|                                   |                                                         |                                              | MSI clock, 65 kHz                                              | $T_A$ = -40 °C to 25 °C                 | 14  | 16                 |      |

|                                   |                                                         |                                              | f <sub>HCLK</sub> = 32 kHz                                     | T <sub>A</sub> = 85 °C                  | 19  | 23                 |      |

|                                   |                                                         |                                              | Flash ON                                                       | T <sub>A</sub> = 105 °C                 | 27  | 33                 |      |

|                                   |                                                         | All peripherals<br>OFF, V <sub>DD</sub> from | MSI clock, 65 kHz                                              | $T_A$ = -40 °C to 25 °C                 | 15  | 17                 |      |

|                                   |                                                         | 1.65 V to 3.6 V                              | f <sub>HCLK</sub> = 65 kHz,                                    | T <sub>A</sub> = 85 °C                  | 20  | 23                 |      |

|                                   |                                                         |                                              | Flash ON                                                       | T <sub>A</sub> = 105 °C                 | 28  | 33                 |      |

|                                   |                                                         |                                              |                                                                | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 17  | 19                 |      |

|                                   | Supply                                                  |                                              | MSI clock, 131 kHz<br>f <sub>HCLK</sub> = 131 kHz,<br>Flash ON | T <sub>A</sub> = 55 °C                  | 18  | 21                 | μΑ   |

| I <sub>DD</sub>                   | current in                                              |                                              |                                                                | T <sub>A</sub> = 85 °C                  | 22  | 25                 |      |

| (LP Sleep)                        | Low-power sleep mode                                    |                                              |                                                                | T <sub>A</sub> = 105 °C                 | 30  | 35                 |      |

|                                   |                                                         | TIM9 and                                     |                                                                | $T_A$ = -40 °C to 25 °C                 | 14  | 16                 |      |

|                                   |                                                         |                                              | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz                | T <sub>A</sub> = 85 °C                  | 19  | 22                 |      |

|                                   |                                                         |                                              |                                                                | T <sub>A</sub> = 105 °C                 | 27  | 32                 |      |

|                                   |                                                         |                                              |                                                                | $T_A$ = -40 °C to 25 °C                 | 15  | 17                 |      |

|                                   |                                                         | USART1                                       | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz                | T <sub>A</sub> = 85 °C                  | 20  | 23                 |      |

|                                   |                                                         | enabled, Flash<br>ON, V <sub>DD</sub> from   |                                                                | T <sub>A</sub> = 105 °C                 | 28  | 33                 |      |

|                                   |                                                         | 1.65 V to 3.6 V                              |                                                                | $T_A$ = -40 °C to 25 °C                 | 17  | 19                 |      |

|                                   |                                                         |                                              | MSI clock, 131 kHz                                             | T <sub>A</sub> = 55 °C                  | 18  | 21                 | -    |

|                                   |                                                         |                                              | f <sub>HCLK</sub> = 131 kHz                                    | T <sub>A</sub> = 85 °C                  | 22  | 25                 |      |

|                                   |                                                         |                                              |                                                                | T <sub>A</sub> = 105 °C                 | 30  | 36                 |      |

| I <sub>DD</sub> max<br>(LP Sleep) | Max<br>allowed<br>current in<br>Low-power<br>sleep mode | V <sub>DD</sub> from 1.65 V<br>to 3.6 V      | -                                                              | _                                       | -   | 200                |      |

| Table 22. Current consum | ntion in Low | nower sleen | mode |

|--------------------------|--------------|-------------|------|

| Table 22. Current Consum | puon in Low  | hower sleep | moue |

1. Guaranteed by characterization results, unless otherwise specified.

| Symbol                             | Parameter                            | С                                        | onditions                                    |                                                                 | Тур  | Max <sup>(1)</sup> | Unit |

|------------------------------------|--------------------------------------|------------------------------------------|----------------------------------------------|-----------------------------------------------------------------|------|--------------------|------|

|                                    |                                      |                                          |                                              | T <sub>A</sub> = -40°C to 25°C<br>V <sub>DD</sub> = 1.8 V       | 1.15 | -                  |      |

|                                    |                                      |                                          | LCD                                          | $T_A = -40^{\circ}C$ to $25^{\circ}C$                           | 1.4  | -                  |      |

|                                    |                                      |                                          | OFF                                          | T <sub>A</sub> = 55°C                                           | 2    | -                  |      |

|                                    |                                      |                                          |                                              | T <sub>A</sub> = 85°C                                           | 3.4  | 10                 |      |

|                                    |                                      | RTC clocked by LSI or LSE external clock |                                              | T <sub>A</sub> = 105°C                                          | 6.35 | 23                 |      |

|                                    |                                      | (32.768kHz),                             | LCD                                          | $T_A = -40^{\circ}C$ to $25^{\circ}C$                           | 1.55 | 6                  |      |

|                                    |                                      | regulator in LP mode,<br>HSI and HSE OFF | ON                                           | T <sub>A</sub> = 55°C                                           | 2.15 | 7                  |      |

|                                    |                                      | (no independent                          | (static<br>duty) <sup>(2)</sup>              | T <sub>A</sub> = 85°C                                           | 3.55 | 12                 |      |

|                                    |                                      | watchdog)                                | uuty).                                       | T <sub>A</sub> = 105°C                                          | 6.3  | 27                 |      |

|                                    |                                      |                                          |                                              | $T_A = -40^{\circ}C$ to $25^{\circ}C$                           | 3.9  | 10                 |      |

|                                    |                                      |                                          | LCD<br>ON (1/8<br>duty) <sup>(3)</sup>       | T <sub>A</sub> = 55°C                                           | 4.65 | 11                 | -    |

|                                    | Supply surrent in                    |                                          |                                              | T <sub>A</sub> = 85°C                                           | 6.25 | 16                 |      |

|                                    |                                      |                                          |                                              | T <sub>A</sub> = 105°C                                          | 9.1  | 44                 |      |

|                                    |                                      | RTC clocked by LSE                       | LCD<br>OFF                                   | $T_A = -40^{\circ}C$ to $25^{\circ}C$                           | 1.5  | -                  |      |

| I <sub>DD</sub> (Stop<br>with RTC) | Supply current in Stop mode with RTC |                                          |                                              | $T_A = 55^{\circ}C$                                             | 2.15 | -                  | μΑ   |

| with IXIC)                         | enabled                              |                                          |                                              | T <sub>A</sub> = 85°C                                           | 3.7  | -                  |      |

|                                    |                                      |                                          |                                              | T <sub>A</sub> = 105°C                                          | 6.75 | -                  |      |

|                                    |                                      |                                          | LCD<br>ON<br>(static<br>duty) <sup>(2)</sup> | $T_A = -40^{\circ}C$ to $25^{\circ}C$                           | 1.6  | -                  |      |

|                                    |                                      |                                          |                                              | T <sub>A</sub> = 55°C                                           | 2.3  | -                  |      |

|                                    |                                      |                                          |                                              | T <sub>A</sub> = 85°C                                           | 3.8  | -                  |      |

|                                    |                                      | external quartz<br>(32.768kHz),          |                                              | T <sub>A</sub> = 105°C                                          | 6.85 | -                  |      |

|                                    |                                      | regulator in LP mode,                    |                                              | $T_A = -40^{\circ}C$ to $25^{\circ}C$                           | 4    | -                  |      |

|                                    |                                      | HSI and HSE OFF<br>(no independent       | LCD<br>ON (1/8                               | T <sub>A</sub> = 55°C                                           | 4.85 | -                  |      |

|                                    |                                      | watchdog <sup>(4)</sup>                  | duty) <sup>(3)</sup>                         | T <sub>A</sub> = 85°C                                           | 6.5  | -                  |      |

|                                    |                                      |                                          |                                              | T <sub>A</sub> = 105°C                                          | 9.1  | -                  | 1    |

|                                    |                                      |                                          |                                              | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 1.8V$ | 1.2  | -                  |      |

|                                    |                                      |                                          | LCD<br>OFF                                   | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 3.0V$ | 1.5  | -                  |      |

|                                    |                                      |                                          |                                              | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 3.6V$ | 1.75 | -                  |      |

### 6.3.8 PLL characteristics

The parameters given in *Table 34* are derived from tests performed under the conditions summarized in *Table 14*.

| Symbol                                                       | Parameter                                               |     | Unit |                    |      |

|--------------------------------------------------------------|---------------------------------------------------------|-----|------|--------------------|------|

| Symbol                                                       | Parameter                                               | Min | Тур  | Max <sup>(1)</sup> | Unit |

| f                                                            | PLL input clock <sup>(2)</sup>                          | 2   | -    | 24                 | MHz  |

| f <sub>PLL_IN</sub>                                          | PLL input clock duty cycle                              | 45  | -    | 55                 | %    |

| f <sub>PLL_OUT</sub>                                         | PLL output clock                                        | 2   | -    | 32                 | MHz  |

| t <sub>LOCK</sub>                                            | PLL lock time<br>PLL input = 16 MHz<br>PLL VCO = 96 MHz | -   | 115  | 160                | μs   |

| Jitter                                                       | Cycle-to-cycle jitter                                   | -   | -    | ±600               | ps   |

| I <sub>DDA</sub> (PLL)                                       | Current consumption on V <sub>DDA</sub>                 | -   | 220  | 450                |      |

| I <sub>DD</sub> (PLL) Current consumption on V <sub>DD</sub> |                                                         | -   | 120  | 150                | μA   |

| Table 34. | PLL | characteristics |

|-----------|-----|-----------------|

|           |     |                 |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

#### 6.3.9 Memory characteristics

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

#### **RAM** memory

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

#### **SPI characteristics**

Unless otherwise specified, the parameters given in the following table are derived from tests performed under the conditions summarized in *Table 14*.

Refer to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter Conditions             |                            | Min                   | Max <sup>(2)</sup>    | Unit |

|----------------------------------------------------------------------------|----------------------------------|----------------------------|-----------------------|-----------------------|------|

| -                                                                          |                                  | Master mode                | -                     | 16                    |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency              | Slave mode                 | -                     | 16                    | MHz  |

|                                                                            |                                  | Slave transmitter          | -                     | 12 <sup>(3)</sup>     |      |

| $t_{r(SCK)}^{(2)}_{t_{f(SCK)}^{(2)}}$                                      | SPI clock rise and fall time     | Capacitive load: C = 30 pF | -                     | 6                     | ns   |

| DuCy(SCK)                                                                  | SPI slave input clock duty cycle | Slave mode                 | 30                    | 70                    | %    |

| t <sub>su(NSS)</sub>                                                       | NSS setup time                   | Slave mode                 | 4t <sub>HCLK</sub>    | -                     |      |

| t <sub>h(NSS)</sub>                                                        | NSS hold time                    | Slave mode                 | 2t <sub>HCLK</sub>    | -                     |      |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time            | Master mode                | t <sub>SCK</sub> /2-5 | t <sub>SCK</sub> /2+3 |      |

| t <sub>su(MI)</sub> <sup>(2)</sup>                                         | Data input actur time            | Master mode                | 5                     | -                     |      |

| t <sub>su(SI)</sub> <sup>(2)</sup>                                         | Data input setup time            | Slave mode                 | 6                     | -                     |      |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                          | Deta input hold time             | Master mode                | 5                     | -                     | ns   |

| t <sub>h(SI)</sub> <sup>(2)</sup>                                          | Data input hold time             | Slave mode                 | 5                     | -                     |      |

| t <sub>a(SO)</sub> <sup>(4)</sup>                                          | Data output access time          | Slave mode                 | 0                     | 3t <sub>HCLK</sub>    |      |

| t <sub>v(SO)</sub> (2)                                                     | Data output valid time           | Slave mode                 | -                     | 33                    |      |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time           | Master mode                | -                     | 6.5                   |      |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Slave mode                 | 17                    | -                     |      |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Master mode                | 0.5                   | -                     |      |

Table 50. SPI characteristics<sup>(1)</sup>

1. The characteristics above are given for voltage range 1.

2. Guaranteed by characterization results.

3. The maximum SPI clock frequency in slave transmitter mode is given for an SPI slave input clock duty cycle (DuCy(SCK)) ranging between 40 to 60%.

4. Min time is for the minimum time to drive the output and max time is for the maximum time to validate the data.

#### **USB** characteristics

The USB interface is USB-IF certified (full speed).

| Table 51. USB startup time          |                              |     |      |  |

|-------------------------------------|------------------------------|-----|------|--|

| Symbol                              | Parameter                    | Мах | Unit |  |

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |  |

1. Guaranteed by design.

| Table 52. US | SB DC electrica | I characteristics |

|--------------|-----------------|-------------------|

|              |                 |                   |

| Symbol                         | Parameter                                                                           | Conditions                                                 | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

|--------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------|---------------------|------|

| Input leve                     | ls                                                                                  |                                                            |                     |                     |      |

| V <sub>DD</sub>                | USB operating voltage                                                               | -                                                          | 3.0                 | 3.6                 | V    |

| V <sub>DI</sub> <sup>(2)</sup> | Differential input sensitivity                                                      | I(USB_DP, USB_DM)                                          | 0.2                 | -                   |      |

| V <sub>CM</sub> <sup>(2)</sup> | Differential common mode range                                                      | Includes V <sub>DI</sub> range                             | 0.8                 | 2.5                 | V    |

| V <sub>SE</sub> <sup>(2)</sup> | Single ended receiver threshold -                                                   |                                                            | 1.3                 | 2.0                 |      |

| Output levels                  |                                                                                     |                                                            |                     |                     |      |

| V <sub>OL</sub> <sup>(3)</sup> | Static output level low                                                             | ${\sf R}_{\sf L}$ of 1.5 k $\Omega$ to 3.6 ${\sf V}^{(4)}$ | -                   | 0.3                 | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Static output level high $R_{L}$ of 15 k $\Omega$ to V <sub>SS</sub> <sup>(4)</sup> |                                                            | 2.8                 | 3.6                 | V    |

1. All the voltages are measured from the local ground potential.

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

4. R<sub>L</sub> is the load connected on the USB drivers.

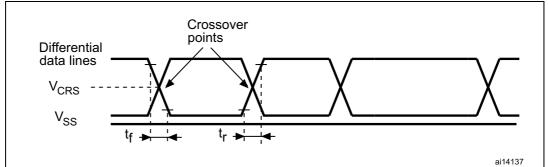

Table 53. USB: full speed electrical characteristics

|                | Driver characteristics <sup>(1)</sup> |                        |     |     |      |  |

|----------------|---------------------------------------|------------------------|-----|-----|------|--|

| Symbol         | Parameter                             | Conditions             | Min | Max | Unit |  |

| t <sub>r</sub> | Rise time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF | 4   | 20  | ns   |  |

| t <sub>f</sub> | Fall Time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF | 4   | 20  | ns   |  |

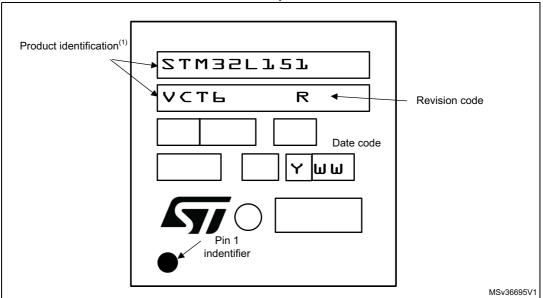

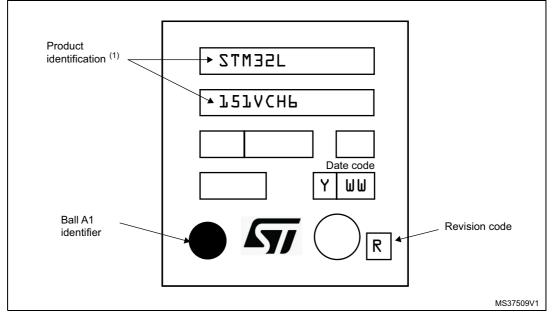

#### Marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity

| Table 67. LQFP64, 10 x 10 mm 64-pin low-profile quad flat package mechanical data |

|-----------------------------------------------------------------------------------|

| (continued)                                                                       |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Max    |  |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |  |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |  |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 36. LQFP64, 10 x 10 mm, 64-pin low-profile quad flat package

1. Dimensions are in millimeters.

ai14909c

### 7.4 UFQFPN48 7 x 7 mm, 0.5 mm pitch, package information

Figure 41. UFQFPN48 7 x 7 mm, 0.5 mm pitch, package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

#### Marking of engineering samples

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity

## 9 Revision History

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Feb-2012 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12-Oct-2012 | 2        | Added WLCSP63 package.<br>Updated <i>Figure 1: Ultra-low-power STM32L162xC block diagram.</i><br>Changed maximum number of touch sensing channels to 34, and<br>updated <i>Table 2: Ultralow power STM32L15xxC device features and</i><br><i>peripheral counts.</i><br>Added <i>Table 4: Functionalities depending on the working mode (from</i><br><i>Run/active down to standby)</i> , and <i>Table 3: ange depending on</i><br><i>dynamic voltage scaling.</i><br>Updated <i>Section 3.10: ADC (analog-to-digital converter)</i> to add<br><i>Section 3.10.1: Temperature sensor</i> and <i>Section 3.10.2: Internal</i><br><i>voltage reference (VREFINT).</i><br>Updated <i>Figure 3: STM32L162VC LQFP100 pinout.</i><br><i>Table 10: STM32L15xxC pin definitions:</i> updated name of reference<br>manual in footnote 5.<br>Changed I2C1_SMBAI into I2C1_SMBA in <i>Table 10: STM32L15xxC</i><br><i>pin definitions.</i><br>Modified PB10/11/12 for AFIO4 alternate function, and replaced LBAR<br>by NADV for AFIO12 in <i>Table 10: Alternate function input/output.</i><br>Removed caution note below <i>Figure 8: Power supply scheme.</i><br>Added <i>Note 2</i> in <i>Table 15: Embedded reset and power control block</i><br><i>characteristics.</i><br>Updated <i>Table 22: Typical and maximum current consumptions in Stop</i><br><i>mode</i> and added <i>Note 6.</i> Updated <i>Table 23: Typical and maximum</i><br><i>current consumptions in Standby mode.</i> Updated t <sub>WUSTOP</sub> in <i>Table : .</i><br>Updated <i>Table 26: Peripheral current consumption.</i><br>Updated <i>Table 60: SPI characteristics,</i> added <i>Note 1</i> and <i>Note 3</i> , and<br>applied <i>Note 2</i> to t <sub>r(SCK)</sub> , t <sub>R(SCK)</sub> , t <sub>w(SCKL)</sub> , t <sub>su(MI)</sub> , t <sub>su(SI)</sub> , t <sub>h(MI)</sub> ,<br>and t <sub>h(SI)</sub> .<br>Added <i>Table 61: I2S characteristics, Figure 29: I2S slave timing</i><br><i>diagram (Philips protocol)(1)</i> and <i>Figure 30: I2S master timing diagram</i><br><i>(Philips protocol)(1).</i><br>Updated <i>Table 72: Temperature sensor characteristics.</i><br>Added <i>Figure 40: Thermal resistance.</i> |

#### Table 75. Document revision history