Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

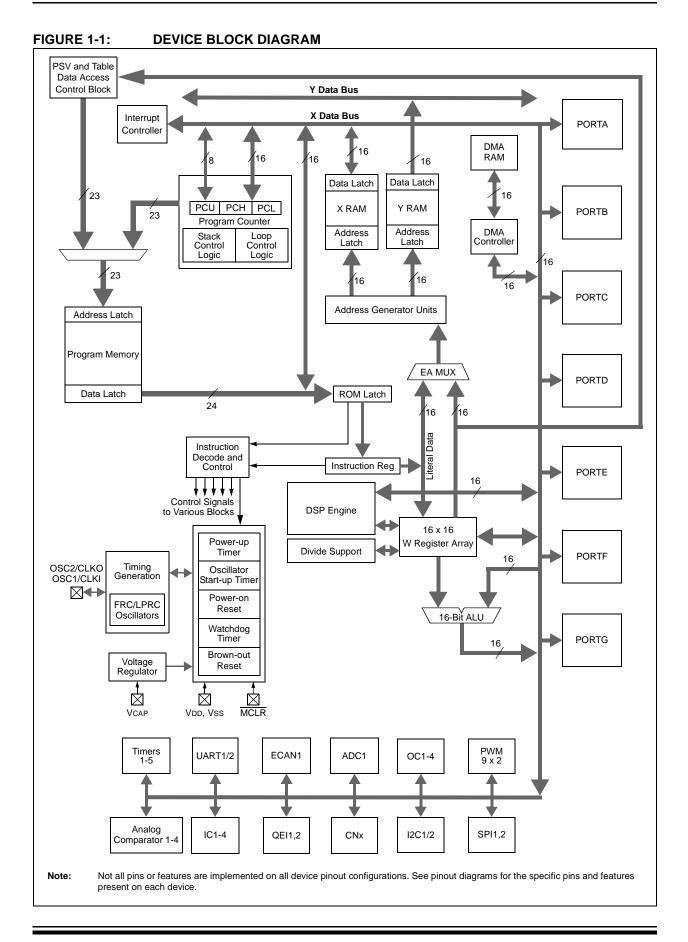

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$= K \in$

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 50 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                        |

| Number of I/O              | 58                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 4K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9×9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs406-50i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| File    | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13   | Bit 12  | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4         | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All    |

|---------|-------------|---------|---------|----------|---------|---------|----------|----------|----------|----------|----------|----------|---------------|---------|----------|----------|----------|--------|

| Name    |             |         |         |          |         |         |          |          |          |          |          |          |               |         |          |          |          | Resets |

| INTCON1 | 0080        | NSTDIS  | OVAERR  | OVBERR   | COVAERR | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  | DMACERR  | MATHERR       | ADDRERR | STKERR   | OSCFAIL  |          | 0000   |

| INTCON2 | 0082        | ALTIVT  | DISI    | —        | —       | —       | —        | —        | —        | —        | —        | —        | INT4EP        | INT3EP  | INT2EP   | INT1EP   | INT0EP   | 0000   |

| IFS0    | 0084        | —       | DMA1IF  | ADIF     | U1TXIF  | U1RXIF  | SPI1IF   | SPI1EIF  | T3IF     | T2IF     | OC2IF    | IC2IF    | DMA0IF        | T1IF    | OC1IF    | IC1IF    | INTOIF   | 0000   |

| IFS1    | 0086        | U2TXIF  | U2RXIF  | INT2IF   | T5IF    | T4IF    | OC4IF    | OC3IF    | DMA2IF   | —        | -        | —        | INT1IF        | CNIF    | AC1IF    | MI2C1IF  | SI2C1IF  | 0000   |

| IFS2    | 0088        | —       | _       | -        | _       | _       | _        | —        | —        | —        | IC4IF    | IC3IF    | DMA3IF        | C1IF    | C1RXIF   | SPI2IF   | SPI2EIF  | 0000   |

| IFS3    | 008A        | —       | —       | -        | —       | —       | QEI1IF   | PSEMIF   | —        | —        | INT4IF   | INT3IF   | -             | —       | MI2C2IF  | SI2C2IF  | —        | 0000   |

| IFS4    | 008C        | —       | —       | —        | —       | QEI2IF  | —        | PSESMIF  |          | —        | C1TXIF   | —        | —             | —       | U2EIF    | U1EIF    | —        | 0000   |

| IFS5    | 008E        | PWM2IF  | PWM1IF  | ADCP12IF | _       | —       | _        | _        | —        | —        | _        | —        | _             | —       | _        | ADCP8IF  | —        | 0000   |

| IFS6    | 0090        | ADCP1IF | ADCP0IF |          | —       | —       | _        | AC4IF    | AC3IF    | AC2IF    |          | PWM8IF   | PWM7IF        | PWM6IF  | PWM5IF   | PWM4IF   | PWM3IF   | 0000   |

| IFS7    | 0092        | —       | —       | -        | —       | —       | -        | _        | —        | —        | -        | ADCP7IF  | ADCP6IF       | ADCP5IF | ADCP4IF  | ADCP3IF  | ADCP2IF  | 0000   |

| IEC0    | 0094        | _       | DMA1IE  | ADIE     | U1TXIE  | U1RXIE  | SPI1IE   | SPI1EIE  | T3IE     | T2IE     | OC2IE    | IC2IE    | DMA0IE        | T1IE    | OC1IE    | IC1IE    | INTOLE   | 0000   |

| IEC1    | 0096        | U2TXIE  | U2RXIE  | INT2IE   | T5IE    | T4IE    | OC4IE    | OC3IE    | DMA2IE   | _        | —        | _        | INT1IE        | CNIE    | AC1IE    | MI2C1IE  | SI2C1IE  | 0000   |

| IEC2    | 0098        | -       |         | _        | -       | -       | _        | _        | _        | _        | IC4IE    | IC3IE    | <b>DMA3IE</b> | C1IE    | C1RXIE   | SPI2IE   | SPI2EIE  | 0000   |

| IEC3    | 009A        | —       | _       | -        | _       | _       | QEI1IE   | PSEMIE   | _        | —        | INT4IE   | INT3IE   | _             | _       | MI2C2IE  | SI2C2IE  | _        | 0000   |

| IEC4    | 009C        | _       | _       | _        | _       | QEI2IE  | _        | PSESMIE  | _        | _        | C1TXIE   | _        | _             | _       | U2EIE    | U1EIE    | _        | 0000   |

| IEC5    | 009E        | PWM2IE  | PWM1IE  | ADCP12IE | _       | _       | -        | _        | _        | _        |          | _        |               | _       | -        | ADCP8IE  |          | 0000   |

| IEC6    | 00A0        | ADCP1IE | ADCP0IE | _        | —       | _       | _        | AC4IE    | AC3IE    | AC2IE    | -        | PWM8IE   | PWM7IE        | PWM6IE  | PWM5IE   | PWM4IE   | PWM3IE   | 0000   |

| IEC7    | 00A2        | _       | _       | _        | _       | _       | _        | _        | _        | _        | _        | ADCP7IE  | ADCP6IE       | ADCP5IE | ADCP4IE  | ADCP3IE  | ADCP2IE  | 0000   |

| IPC0    | 00A4        | _       | T1IP2   | T1IP1    | T1IP0   | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2   | IC1IP1   | IC1IP0        | _       | INT0IP2  | INT0IP1  | INT0IP0  | 4444   |

| IPC1    | 00A6        | _       | T2IP2   | T2IP1    | T2IP0   | _       | OC2IP2   | OC2IP1   | OC2IP0   | _        | IC2IP2   | IC2IP1   | IC2IP0        | _       | DMA0IP2  | DMA0IP1  | DMA0IP0  | 4444   |

| IPC2    | 00A8        | _       | U1RXIP2 | U1RXIP1  | U1RXIP0 | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0      | _       | T3IP2    | T3IP1    | T3IP0    | 4444   |

| IPC3    | 00AA        | _       | _       |          | —       | _       | DMA1IP2  | DMA1IP1  | DMA1IP0  | _        | ADIP2    | ADIP1    | ADIP0         | —       | U1TXIP2  | U1TXIP1  | U1TXIP0  | 4444   |

| IPC4    | 00AC        | _       | CNIP2   | CNIP1    | CNIP0   | _       | AC1IP2   | AC1IP1   | AC1IP0   | _        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0      | —       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 | 4444   |

| IPC5    | 00AE        | _       | _       |          | —       | _       |          | -        | —        | _        |          | —        |               | _       | INT1IP2  | INT1IP1  | INT1IP0  | 0004   |

| IPC6    | 00B0        | _       | T4IP2   | T4IP1    | T4IP0   | _       | OC4IP2   | OC4IP1   | OC4IP0   | _        | OC3IP2   | OC3IP1   | OC3IP0        | —       | DMA2IP2  | DMA2IP1  | DMA2IP0  | 4444   |

| IPC7    | 00B2        | _       | U2TXIP2 | U2TXIP1  | U2TXIP0 | _       | U2RXIP2  | U2RXIP1  | U2RXIP0  | _        | INT2IP2  | INT2IP1  | INT2IP0       | _       | T5IP2    | T5IP1    | T5IP0    | 4444   |

| IPC8    | 00B4        | _       | C1IP2   | C1IP1    | C1IP0   | _       | C1RXIP2  | C1RXIP1  | C1RXIP0  | _        | SPI2IP2  | SPI2IP1  | SPI2IP0       | _       | SPI2EIP2 | SPI2EIP1 | SPI2EIP0 | 4444   |

| IPC9    | 00B6        | _       | _       | _        | _       | _       | IC4IP2   | IC4IP1   | IC4IP0   | _        | IC3IP2   | IC3IP1   | IC3IP0        | _       | DMA3IP2  | DMA3IP1  | DMA3IP0  | 0444   |

| IPC12   | 00BC        | _       | _       | _        | _       | _       | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 | _        | SI2C2IP2 | SI2C2IP1 | SI2C2IP0      | _       | _        | _        | —        | 0440   |

| IPC13   | 00BE        | _       | _       | _        | _       | _       | INT4IP2  | INT4IP1  | INT4IP0  | _        | INT3IP2  | INT3IP1  | INT3IP0       | _       | _        | _        | _        | 0440   |

| IPC14   | 00C0        | _       | _       | _        | _       | _       | QEI1IP2  | QEI1IP0  | QEI1IP0  | _        | PSEMIP2  | PSEMIP1  | PSEMIP0       | _       | _        | _        | _        | 0440   |

| IPC16   | 00C4        | _       | _       | _        | _       | _       | U2EIP2   | U2EIP1   | U2EIP0   | _        | U1EIP2   | U1EIP1   | U1EIP0        | _       | _        | _        | _        | 0440   |

| IPC17   | 00C6        | _       | _       | _        | _       | _       | C1TXIP2  | C1TXIP1  | C1TXIP0  | _        | _        | _        | _             | _       | _        | _        | _        | 0400   |

| IPC18   | 00C8        |         | QEI2IP2 | QEI2IP1  | QEI2IP0 |         | _        |          | _        | _        | PSESMIP2 | PSESMIP1 | PSESMIP0      |         |          |          |          | 4040   |

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ64GS608 DEVICES

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 8000h and higher maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

# Note: PSV access is temporarily disabled during Table Reads/Writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data, to execute in a single cycle.

#### When CORCON < 2 > = 1 and EA < 15 > = 1: **Program Space** Data Space **PSVPAG** 15 0 0x000000 0x0000 02 Data EA<14:0> 0x010000 0x018000 The data in the page designated by PSVPAG is mapped into the upper half of the data memory 0x8000 space... **PSV** Area ...while the lower 15 bits of the EA specify an exact address within 0xFFFF the PSV area. This corresponds exactly to the same lower 15 bits of the actual program space address. 0x800000

### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

#### 6.9 Using the RCON Status Bits

The user application can read the Reset Control (RCON) register after any device Reset to determine the cause of the Reset.

| Note: | The status bits in the RCON register      |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | should be cleared after they are read so  |  |  |  |  |  |  |  |  |  |

|       | that the next RCON register value after a |  |  |  |  |  |  |  |  |  |

|       | device Reset will be meaningful.          |  |  |  |  |  |  |  |  |  |

#### TABLE 6-3: RESET FLAG BIT OPERATION

Flag Bit **Cleared by:** Set by: TRAPR (RCON<15>) Trap Conflict Event POR, BOR IOPWR (RCON<14>) Illegal Opcode or Uninitialized W register POR, BOR Access or Security Reset MCLR Reset POR EXTR (RCON<7>) SWR (RCON<6>) **RESET** Instruction POR, BOR WDTO (RCON<4>) WDT Time-out PWRSAV Instruction, CLRWDT Instruction, POR, BOR SLEEP (RCON<3>) POR, BOR PWRSAV #SLEEP Instruction IDLE (RCON<2>) **PWRSAV #IDLE Instruction** POR, BOR BOR (RCON<1>) POR, BOR \_\_\_\_ **POR** (RCON<0>) POR \_\_\_\_

Note: All Reset flag bits can be set or cleared by user software.

Table 6-3 provides a summary of the Reset flag bit operation.

| U-0                          | U-0                                                                                                              | U-0                                                                                                    | U-0              | U-0                             | U-0                   | U-0             | U-0     |  |  |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------|---------------------------------|-----------------------|-----------------|---------|--|--|--|--|--|

| _                            | —                                                                                                                |                                                                                                        | —                | —                               | —                     | _               | —       |  |  |  |  |  |

| bit 15                       |                                                                                                                  |                                                                                                        |                  |                                 |                       |                 | bit 8   |  |  |  |  |  |

| U-0                          | R/W-0                                                                                                            | R/W-0                                                                                                  | R/W-0            | R/W-0                           | R/W-0                 | R/W-0           | R/W-0   |  |  |  |  |  |

|                              | IC4IF                                                                                                            | IC3IF                                                                                                  | DMA3IF           | C1IF <sup>(1)</sup>             | C1RXIF <sup>(1)</sup> | SPI2IF          | SPI2EIF |  |  |  |  |  |

| bit 7                        |                                                                                                                  | 10011                                                                                                  | Divition         | 0111                            | Onota                 | 01 1211         | bit (   |  |  |  |  |  |

|                              |                                                                                                                  |                                                                                                        |                  |                                 |                       |                 | _       |  |  |  |  |  |

| <b>Legend:</b><br>R = Readab | le hit                                                                                                           | W = Writable                                                                                           | bit              | II – I Inimpler                 | mented bit, read      | as '0'          |         |  |  |  |  |  |

| -n = Value a                 |                                                                                                                  | 1' = Bit is se                                                                                         |                  | $0^{\circ} = \text{Bit is cle}$ |                       | x = Bit is unki | าดพท    |  |  |  |  |  |

|                              |                                                                                                                  |                                                                                                        | -                |                                 |                       |                 |         |  |  |  |  |  |

| bit 15-7                     | Unimplement                                                                                                      | ted: Read as                                                                                           | ʻ0'              |                                 |                       |                 |         |  |  |  |  |  |

| bit 6                        | IC4IF: Input Capture Channel 4 Interrupt Flag Status bit                                                         |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |  |

|                              | 1 = Interrupt r                                                                                                  | 1 = Interrupt request has occurred                                                                     |                  |                                 |                       |                 |         |  |  |  |  |  |

|                              | 0 = Interrupt r                                                                                                  | equest has no                                                                                          | ot occurred      |                                 |                       |                 |         |  |  |  |  |  |

| bit 5                        | IC3IF: Input Capture Channel 3 Interrupt Flag Status bit                                                         |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |  |

|                              | •                                                                                                                | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                  |                                 |                       |                 |         |  |  |  |  |  |

| bit 4                        | 0 = Interrupt request has not occurred<br>DMA3IF: DMA Channel 3 Data Transfer Complete Interrupt Flag Status bit |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |  |

| DIL 4                        | 1 = Interrupt request has occurred                                                                               |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |  |

|                              | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>           |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |  |

| bit 3                        | C1IF: ECAN1 Event Interrupt Flag Status bit <sup>(1)</sup>                                                       |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |  |

|                              | 1 = Interrupt r                                                                                                  | 1 = Interrupt request has occurred                                                                     |                  |                                 |                       |                 |         |  |  |  |  |  |

|                              | 0 = Interrupt request has not occurred                                                                           |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |  |

| bit 2                        |                                                                                                                  | C1RXIF: ECAN1 External Event Interrupt Flag Status bit <sup>(1)</sup>                                  |                  |                                 |                       |                 |         |  |  |  |  |  |

|                              | 1 = Interrupt r<br>0 = Interrupt r                                                                               |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |  |

| bit 1                        | -                                                                                                                | -                                                                                                      | ot Flag Status b | vit                             |                       |                 |         |  |  |  |  |  |

|                              | 1 = Interrupt r                                                                                                  | •                                                                                                      | •                | Л                               |                       |                 |         |  |  |  |  |  |

|                              | 0 = Interrupt r                                                                                                  |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |  |

| bit 0                        | SPI2EIF: SPI2                                                                                                    | 2 Error Interru                                                                                        | pt Flag Status   | bit                             |                       |                 |         |  |  |  |  |  |

|                              | 1 = Interrupt r                                                                                                  |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |  |

|                              | 0 – Interrupt r                                                                                                  | equest has no                                                                                          | t occurred       |                                 |                       |                 |         |  |  |  |  |  |

#### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

**Note 1:** Interrupts are disabled on devices without ECAN<sup>™</sup> modules.

| U-0                                                                        | R/W-1                                                   | R/W-0              | R/W-0            | U-0         | R/W-1             | R/W-0    | R/W-0   |  |  |  |  |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------|--------------------|------------------|-------------|-------------------|----------|---------|--|--|--|--|--|--|

| _                                                                          | AC2IP2                                                  | AC2IP1             | AC2IP0           | _           | PWM9IP2           | PWM9IP1  | PWM9IP0 |  |  |  |  |  |  |

| bit 15                                                                     |                                                         |                    |                  |             |                   |          | bit     |  |  |  |  |  |  |

|                                                                            |                                                         |                    |                  |             |                   |          |         |  |  |  |  |  |  |

| U-0                                                                        | R/W-1                                                   | R/W-0              | R/W-0            | U-0         | R/W-1             | R/W-0    | R/W-0   |  |  |  |  |  |  |

| —                                                                          | PWM8IP2                                                 | PWM8IP1            | PWM8IP0          | —           | PWM7IP2           | PWM7IP1  | PWM7IP0 |  |  |  |  |  |  |

| bit 7                                                                      |                                                         |                    |                  |             |                   |          | bit     |  |  |  |  |  |  |

| Legend:                                                                    |                                                         |                    |                  |             |                   |          |         |  |  |  |  |  |  |

| R = Readab                                                                 | le bit                                                  | W = Writable       | bit              | U = Unimple | emented bit, read | 1 as '0' |         |  |  |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                         |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            |                                                         |                    |                  |             |                   |          |         |  |  |  |  |  |  |

| bit 15                                                                     | Unimplemen                                              | ted: Read as '     | 0'               |             |                   |          |         |  |  |  |  |  |  |

| bit 14-12                                                                  | AC2IP<2:0>: Analog Comparator 2 Interrupt Priority bits |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | 111 = Interrupt is Priority 7 (highest priority)        |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | •                                                       |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | •                                                       |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | 001 = Interru                                           | pt is Priority 1   |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | 000 = Interrupt source is disabled                      |                    |                  |             |                   |          |         |  |  |  |  |  |  |

| bit 11                                                                     | Unimplemen                                              | ted: Read as '     | 0'               |             |                   |          |         |  |  |  |  |  |  |

| bit 10-8                                                                   | PWM9IP<2:0>: PWM9 Interrupt Priority bits               |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | 111 = Interrupt is Priority 7 (highest priority)        |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | •                                                       |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | •                                                       |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | 001 = Interrupt is Priority 1                           |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | 000 = Interrupt source is disabled                      |                    |                  |             |                   |          |         |  |  |  |  |  |  |

| bit 7                                                                      | Unimplemen                                              | ted: Read as '     | 0'               |             |                   |          |         |  |  |  |  |  |  |

| bit 6-4                                                                    | PWM8IP<2:0                                              | >: PWM8 Inter      | rupt Priority b  | its         |                   |          |         |  |  |  |  |  |  |

|                                                                            | 111 = Interru                                           | pt is Priority 7 ( | (highest priorit | y)          |                   |          |         |  |  |  |  |  |  |

|                                                                            | •                                                       |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | •                                                       |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | 001 = Interru                                           | pt is Priority 1   |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | 000 = Interru                                           | pt source is dis   | abled            |             |                   |          |         |  |  |  |  |  |  |

| bit 3                                                                      | Unimplemen                                              | ted: Read as '     | 0'               |             |                   |          |         |  |  |  |  |  |  |

| bit 2-0                                                                    | PWM7IP<2:0                                              | >: PWM7 Inter      | rupt Priority b  | its         |                   |          |         |  |  |  |  |  |  |

|                                                                            | 111 = Interru                                           | pt is Priority 7 ( | (highest priorit | y)          |                   |          |         |  |  |  |  |  |  |

|                                                                            | •                                                       |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | •                                                       |                    |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            | 001 = Interru                                           | pt is Priority 1   |                  |             |                   |          |         |  |  |  |  |  |  |

|                                                                            |                                                         |                    |                  |             |                   |          |         |  |  |  |  |  |  |

### REGISTER 7-41: IPC25: INTERRUPT PRIORITY CONTROL REGISTER 25

| 11.0         |                                                      | 11.0                                                                                                                                                                                                       | 11.0            | 11.0                               | 11.0   | 11.0            | 11.0   |  |  |  |  |

|--------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------|--------|-----------------|--------|--|--|--|--|

| U-0          | U-0                                                  | U-0                                                                                                                                                                                                        | U-0             | U-0                                | U-0    | U-0             | U-0    |  |  |  |  |

| _            | —                                                    |                                                                                                                                                                                                            |                 | —                                  | —      | —               | —      |  |  |  |  |

| bit 15       |                                                      |                                                                                                                                                                                                            |                 |                                    |        |                 | bit    |  |  |  |  |

|              |                                                      |                                                                                                                                                                                                            |                 |                                    |        |                 |        |  |  |  |  |

| U-0          | R/W-1                                                | R/W-0                                                                                                                                                                                                      | R/W-0           | U-0                                | R/W-1  | R/W-0           | R/W-0  |  |  |  |  |

| —            | AC4IP2                                               | AC4IP1                                                                                                                                                                                                     | AC4IP0          | —                                  | AC3IP2 | AC3IP1          | AC3IP0 |  |  |  |  |

| bit 7        |                                                      |                                                                                                                                                                                                            |                 |                                    |        |                 | bit    |  |  |  |  |

|              |                                                      |                                                                                                                                                                                                            |                 |                                    |        |                 |        |  |  |  |  |

| Legend:      |                                                      |                                                                                                                                                                                                            |                 |                                    |        |                 |        |  |  |  |  |

| R = Readat   |                                                      | W = Writable                                                                                                                                                                                               |                 | U = Unimplemented bit, read as '0' |        |                 |        |  |  |  |  |

| -n = Value a | at POR                                               | '1' = Bit is set                                                                                                                                                                                           |                 | '0' = Bit is cle                   | ared   | x = Bit is unkr | nown   |  |  |  |  |

| bit 6-4      | 111 = Interru<br>•<br>001 = Interru<br>000 = Interru | Unimplemented: Read as '0'<br>AC4IP<2:0>: Analog Comparator 4 Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority)<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |                 |                                    |        |                 |        |  |  |  |  |

| bit 3        | -                                                    | ted: Read as '                                                                                                                                                                                             |                 |                                    |        |                 |        |  |  |  |  |

|              | AC3IP<2:0>:                                          | Analog Compa                                                                                                                                                                                               |                 |                                    |        |                 |        |  |  |  |  |

| bit 2-0      | 111 = Interrupt is Priority 7 (highest priority)     |                                                                                                                                                                                                            |                 |                                    |        |                 |        |  |  |  |  |

| bit 2-0      | 111 = Interru                                        | pt is Priority 7 (                                                                                                                                                                                         | nignest priorit | y)                                 |        |                 |        |  |  |  |  |

| bit 2-0      | 111 = Interru<br>•                                   | pt is Priority 7 (                                                                                                                                                                                         | nignest priorit | <b>y</b> )                         |        |                 |        |  |  |  |  |

| bit 2-0      | 111 = Interru<br>•                                   | pt is Priority 7 (                                                                                                                                                                                         | nignest priorit | <i>y</i> /                         |        |                 |        |  |  |  |  |

| bit 2-0      | •<br>•                                               | pt is Priority 7 (<br>pt is Priority 1                                                                                                                                                                     | nignest priorit | <i>y</i> /                         |        |                 |        |  |  |  |  |

#### REGISTER 7-42: IPC26: INTERRUPT PRIORITY CONTROL REGISTER 26

| U-0          | R/W-1                                                                                                                          | R/W-0                                     | R/W-0             | U-0             | R/W-1             | R/W-0             | R/W-0             |  |  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------|-----------------|-------------------|-------------------|-------------------|--|--|--|--|--|--|--|

| _            | ADCP5IP2                                                                                                                       | ADCP5IP1                                  | ADCP5IP0          | _               | ADCP4IP2          | ADCP4IP1          | ADCP4IP0          |  |  |  |  |  |  |  |

| oit 15       |                                                                                                                                |                                           |                   |                 |                   |                   | bit 8             |  |  |  |  |  |  |  |

|              |                                                                                                                                | DAVO                                      | DAMO              |                 | D 44/4            | DAMA              | DAMO              |  |  |  |  |  |  |  |

| U-0          | R/W-1<br>ADCP3IP2                                                                                                              | R/W-0<br>ADCP3IP1                         | R/W-0<br>ADCP3IP0 | U-0             | R/W-1<br>ADCP2IP2 | R/W-0<br>ADCP2IP1 | R/W-0<br>ADCP2IP0 |  |  |  |  |  |  |  |

| <br>bit 7    | ADCF3IF2                                                                                                                       | ADCESIEL                                  | ADCF3IFU          | _               | ADGFZIFZ          | ADGFZIFT          | bit (             |  |  |  |  |  |  |  |

|              |                                                                                                                                |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| Legend:      |                                                                                                                                |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                         | W = Writable                              | bit               | U = Unimple     | emented bit, read | 1 as '0'          |                   |  |  |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                          | '1' = Bit is set                          |                   | '0' = Bit is cl | eared             | x = Bit is unkr   | nown              |  |  |  |  |  |  |  |

|              |                                                                                                                                |                                           | _                 |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 15       | Unimplemented: Read as '0'                                                                                                     |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 14-12    | ADCP5IP<2:0>: ADC Pair 5 Conversion Done Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              |                                                                                                                                |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                                                                              |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •<br>001 – Interrur                                                                                                            | •<br>001 = Interrupt is Priority 1        |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | 000 = Interrupt source is disabled                                                                                             |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 11       | Unimplemen                                                                                                                     | ted: Read as '                            | 0'                |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 10-8     | ADCP4IP<2:0>: ADC Pair 4 Conversion Done Interrupt Priority bits                                                               |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                     |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                                                                              |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                                                                              |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                                                                                                  |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                                                                              | ot source is dis                          |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 7        | -                                                                                                                              | ted: Read as '                            |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 6-4      | ADCP3IP<2:0>: ADC Pair 3 Conversion Done Interrupt Priority bits                                                               |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                     |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                                                                              |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                                                                              | •                                         |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | 001 = Interrup                                                                                                                 | •                                         | ablad             |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 3        | -                                                                                                                              | ot source is dis<br><b>ted:</b> Read as ' |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 2-0      | -                                                                                                                              | D>: ADC Pair 2                            |                   | one Interrunt   | Priority bits     |                   |                   |  |  |  |  |  |  |  |

| 5h 2-0       |                                                                                                                                | ot is Priority 7 (                        |                   | =               | IT HOILY DIS      |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                                                                              |                                           |                   | ,               |                   |                   |                   |  |  |  |  |  |  |  |

|              |                                                                                                                                |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                                                                              |                                           |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •<br>•<br>001 = Interrup                                                                                                       | nt is Priority 1                          |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

### REGISTER 7-44: IPC28: INTERRUPT PRIORITY CONTROL REGISTER 28

| U-0                             | U-0                                                                                   | U-0                                                                                                                                                                                                                                             | U-0      | U-0              | U-0              | U-0                | U-0      |  |  |  |  |

|---------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|------------------|--------------------|----------|--|--|--|--|

| —                               | —                                                                                     | —                                                                                                                                                                                                                                               | —        | —                | —                | —                  | —        |  |  |  |  |

| bit 15                          |                                                                                       |                                                                                                                                                                                                                                                 |          |                  |                  |                    | bit 8    |  |  |  |  |

|                                 |                                                                                       |                                                                                                                                                                                                                                                 |          |                  |                  |                    |          |  |  |  |  |

| U-0                             | R/W-1                                                                                 | R/W-0                                                                                                                                                                                                                                           | R/W-0    | U-0              | R/W-1            | R/W-0              | R/W-0    |  |  |  |  |

| —                               | ADCP7IP2                                                                              | ADCP7IP1                                                                                                                                                                                                                                        | ADCP7IP0 |                  | ADCP6IP2         | ADCP6IP1           | ADCP6IP0 |  |  |  |  |

| bit 7                           |                                                                                       |                                                                                                                                                                                                                                                 |          |                  |                  |                    | bit 0    |  |  |  |  |

|                                 |                                                                                       |                                                                                                                                                                                                                                                 |          |                  |                  |                    |          |  |  |  |  |

| Legend:                         |                                                                                       |                                                                                                                                                                                                                                                 |          |                  |                  |                    |          |  |  |  |  |

| R = Readable bit W = Writable b |                                                                                       |                                                                                                                                                                                                                                                 | bit      | U = Unimplei     | mented bit, read | as '0'             |          |  |  |  |  |

| -n = Value at                   | POR                                                                                   | '1' = Bit is set                                                                                                                                                                                                                                |          | '0' = Bit is cle | eared            | x = Bit is unknown |          |  |  |  |  |

| bit 15-7<br>bit 6-4<br>bit 3    | ADCP7IP<2:0<br>111 = Interrup<br>•<br>•<br>•<br>•<br>001 = Interrup<br>000 = Interrup | Unimplemented: Read as '0'<br>ADCP7IP<2:0>: ADC Pair 7 Conversion Done Interrupt 1 Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                 |          |                  |                  |                    |          |  |  |  |  |

| bit 2-0                         | 111 = Interru<br>•<br>•                                                               | 000 = Interrupt source is disabled<br>Unimplemented: Read as '0'<br>ADCP6IP<2:0>: ADC Pair 6 Conversion Done Interrupt 1 Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)<br>•<br>•<br>001 = Interrupt is Priority 1 |          |                  |                  |                    |          |  |  |  |  |

#### REGISTER 7-45: IPC29: INTERRUPT PRIORITY CONTROL REGISTER 29

### 10.5 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

**Note:** If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

### REGISTER 16-21: FCLCONx: PWM FAULT CURRENT-LIMIT CONTROL x REGISTER (CONTINUED)

| bit 9   |            | <b>CLPOL:</b> Current-Limit Polarity for PWM Generator # bit <sup>(1)</sup>                                    |

|---------|------------|----------------------------------------------------------------------------------------------------------------|

|         |            | 1 = The selected current-limit source is active-low                                                            |

|         |            | 0 = The selected current-limit source is active-high                                                           |

| bit 8   |            | <b>CLMOD:</b> Current-Limit Mode Enable for PWM Generator # bit                                                |

|         |            | 1 = Current-Limit mode is enabled                                                                              |

|         |            | 0 = Current-Limit mode is disabled                                                                             |

| bit 7-3 | 5          | <b>FLTSRC&lt;4:0&gt;:</b> Fault Control Signal Source Select for PWM Generator # bits <sup>(2,3)</sup>         |

|         |            | 11111 = Reserved                                                                                               |

|         |            | 11110 = Fault 23<br>11101 = Fault 22                                                                           |

|         |            | 11101 = Fault 22<br>11100 = Fault 21                                                                           |

|         |            | 11001 = Fault 20                                                                                               |

|         |            | 11010 <b>= Fault 19</b>                                                                                        |

|         |            | 11001 <b>= Fault 18</b>                                                                                        |

|         |            | 11000 <b>= Fault 17</b>                                                                                        |

|         |            | 10111 = Fault 16                                                                                               |

|         |            | 10110 = Fault 15                                                                                               |

|         |            | 10101 = Fault 14<br>10100 = Fault 13                                                                           |

|         |            | 10100 = Fault 13<br>10011 = Fault 12                                                                           |

|         |            | 10011 = Fault 12<br>10010 = Fault 11                                                                           |

|         |            | 10001 = Fault 10                                                                                               |

|         |            | 10000 <b>= Fault 9</b>                                                                                         |

|         |            | 01111 <b>= Fault 8</b>                                                                                         |

|         |            | 01110 = Fault 7                                                                                                |

|         |            | 01101 = Fault 6                                                                                                |

|         |            | 01100 = Fault 5<br>01011 = Fault 4                                                                             |

|         |            | 01011 = Fault 4<br>01010 = Fault 3                                                                             |

|         |            | 01001 = Fault 2                                                                                                |

|         |            | 01000 = Fault 1                                                                                                |

|         |            | 00111 = Reserved                                                                                               |

|         |            | 00110 = Reserved                                                                                               |

|         |            | 00101 = Reserved                                                                                               |

|         |            | 00100 = Reserved                                                                                               |

|         |            | 00011 = Analog Comparator 4                                                                                    |

|         |            | 00010 = Analog Comparator 3<br>00001 = Analog Comparator 2                                                     |

|         |            | 00000 = Analog Comparator 1                                                                                    |

| bit 2   |            | <b>FLTPOL:</b> Fault Polarity for PWM Generator # bit <sup>(1)</sup>                                           |

| 5112    |            | 1 = The selected Fault source is active-low                                                                    |

|         |            | 0 = The selected Fault source is active-high                                                                   |

| bit 1-0 |            | <b>FLTMOD&lt;1:0&gt;:</b> Fault Mode for PWM Generator # bits                                                  |

|         |            | 11 = Fault input is disabled                                                                                   |

|         |            | 10 = Reserved                                                                                                  |

|         |            | 01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)                               |

|         |            | 00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)                   |

| Noto    | 4.         | These bits should be changed only when PTEN (PTCON<15>) = $0$ .                                                |

|         |            | When Independent Fault mode is enabled (IFLTMOD = 1) and Fault 1 is used for Current-Limit mode                |

|         | <b>č</b> . | (CLSRC<4:0> = $b0000$ ), the Fault Control Source Select bits (FLTSRC<4:0>) should be set to an unused         |

|         |            | Fault source to prevent Fault 1 from disabling both the PWMxL and PWMxH outputs.                               |

| :       | 3:         | When Independent Fault mode is enabled (IFLTMOD = 1) and Fault 1 is used for Fault mode                        |

|         |            | (FLTSRC<4:0> = $b0000$ ), the Current-Limit Control Source Select bits (CLSRC<4:0>) should be set to an unused |

|         |            | current-limit source to prevent the current-limit source from disabling both the PWMxH and PWMxL outputs.      |

| R/W-0         | R/W-0       | R/W-0                               | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|-------------|-------------------------------------|------------------|------------------|------------------|-----------------|--------|

| F11BP3        | F11BP2      | F11BP1                              | F11BP0           | F10BP3           | F10BP2           | F10BP1          | F10BP0 |

| bit 15        |             |                                     |                  |                  |                  |                 | bit 8  |

|               |             |                                     |                  |                  |                  |                 |        |

| R/W-0         | R/W-0       | R/W-0                               | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| F9BP3         | F9BP2       | F9BP1                               | F9BP0            | F8BP3            | F8BP2            | F8BP1           | F8BP0  |

| bit 7         |             |                                     |                  |                  |                  |                 | bit 0  |

|               |             |                                     |                  |                  |                  |                 |        |

| Legend:       |             |                                     |                  |                  |                  |                 |        |

| R = Readable  | e bit       | W = Writable                        | bit              | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at | POR         | '1' = Bit is set                    |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15 10     | E44BD (2:0) |                                     | ok for Filtor 11 | hita             |                  |                 |        |

| bit 15-12     |             | : RX Buffer Mas<br>hits received in |                  |                  |                  |                 |        |

|               |             | hits received in                    |                  |                  |                  |                 |        |

|               | •           |                                     | Danor            |                  |                  |                 |        |

|               | •           |                                     |                  |                  |                  |                 |        |

|               | •           |                                     |                  |                  |                  |                 |        |

|               | 0001        | hits received in                    |                  |                  |                  |                 |        |

|               |             | hits received ir                    |                  |                  |                  |                 |        |

| bit 11-8      | F10BP<3:0>  | : RX Buffer Ma                      | sk for Filter 10 | ) bits (same va  | lues as bits<15  | :12>)           |        |

| bit 7-4       | F9BP<3:0>:  | RX Buffer Masl                      | k for Filter 9 b | its (same value  | es as bits<15:12 | 2>)             |        |

|               |             |                                     |                  |                  |                  |                 |        |

### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

bit 3-0 **F8BP<3:0>:** RX Buffer Mask for Filter 8 bits (same values as bits<15:12>)

| R/W-0         | R/W-0                                                                                     | R/W-0            | R/W-0                              | R/W-0                            | R/W-0           | R/W-0           | R/W-0    |  |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------|------------------|------------------------------------|----------------------------------|-----------------|-----------------|----------|--|--|--|--|--|--|

| IRQEN3        | PEND3                                                                                     | SWTRG3           | TRGSRC34                           | TRGSRC33                         | TRGSRC32        | TRGSRC31        | TRGSRC30 |  |  |  |  |  |  |

| bit 15        |                                                                                           |                  |                                    |                                  |                 |                 | bit 8    |  |  |  |  |  |  |

|               |                                                                                           |                  |                                    |                                  |                 |                 |          |  |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                     | R/W-0            | R/W-0                              | R/W-0                            | R/W-0           | R/W-0           | R/W-0    |  |  |  |  |  |  |

| IRQEN2        | PEND2                                                                                     | SWTRG2           | TRGSRC24                           | TRGSRC23                         | TRGSRC22        | TRGSRC21        | TRGSRC20 |  |  |  |  |  |  |

| bit 7         |                                                                                           |                  |                                    |                                  |                 |                 | bit 0    |  |  |  |  |  |  |

|               |                                                                                           |                  |                                    |                                  |                 |                 |          |  |  |  |  |  |  |