Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                      |

| Number of I/O              | 58                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

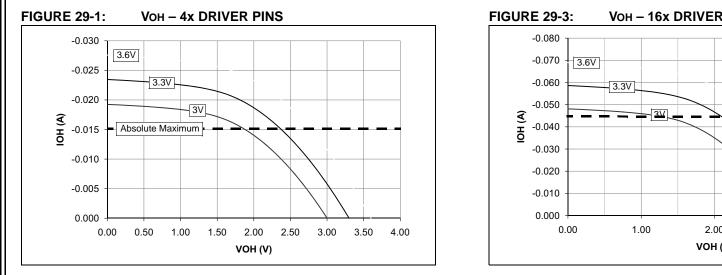

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs406-e-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-18: HIGH-SPEED PWM GENERATOR 2 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14            | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7    | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|---------|-------------------|---------|---------|-----------|-----------|-----------|-----------|----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON2      | 0440        | FLTSTAT | CLSTAT            | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS      | DTC1     | DTC0    | DTCP     |          | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON2       | 0442        | PENH    | PENL              | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL    | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON2      | 0444        | IFLTMOD | CLSRC4            | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD     | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC2         | 0446        |         |                   |         |         |           |           |           | PDC2      | 2<15:0>  |         |          |          |          |          |          |          | 0000          |

| PHASE2       | 0448        |         | PHASE2<15:0> 00   |         |         |           |           |           |           |          |         |          | 0000     |          |          |          |          |               |

| DTR2         | 044A        | _       | — — DTR2<13:0> 0  |         |         |           |           |           |           |          |         | 0000     |          |          |          |          |          |               |

| ALTDTR2      | 044C        | _       | — — ALTDTR2<13:0> |         |         |           |           |           |           |          | 0000    |          |          |          |          |          |          |               |

| SDC2         | 044E        |         |                   |         |         |           |           |           | SDC2      | 2<15:0>  |         |          |          |          |          |          |          | 0000          |

| SPHASE2      | 0450        |         |                   |         |         |           |           |           | SPHAS     | E2<15:0> |         |          |          |          |          |          |          | 0000          |

| TRIG2        | 0452        |         |                   |         |         |           |           | TRGCMP<12 | 2:0>      |          |         |          |          |          | _        | _        | —        | 0000          |

| TRGCON2      | 0454        | TRGDIV3 | TRGDIV2           | TRGDIV1 | TRGDIV0 | _         | _         | —         | _         | DTM      | _       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG2       | 0456        |         |                   |         |         |           |           | STRGCMP<1 | 2:0>      |          |         |          |          |          | _        | _        | —        | 0000          |

| PWMCAP2      | 0458        |         |                   |         |         |           |           | PWMCAP<1  | 2:0>      |          |         |          |          |          | _        | _        | —        | 0000          |

| LEBCON2      | 045A        | PHR     | PHF               | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | _         | _         | _        | _       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY2      | 045C        | _       | _                 | _       | —       | •         |           |           | L         | EB<8:0>  | •       |          |          | -        |          |          |          | 0000          |

| AUXCON2      | 045E        | HRPDIS  | HRDDIS            | _       | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 | _        | —       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER 7    | 7-6: IFS1: I    | NTERRUPT                          | FLAG STAT       |                  | ER 1            |                 |         |

|---------------|-----------------|-----------------------------------|-----------------|------------------|-----------------|-----------------|---------|

| R/W-0         | R/W-0           | R/W-0                             | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0   |

| U2TXIF        | U2RXIF          | INT2IF                            | T5IF            | T4IF             | OC4IF           | OC3IF           | DMA2IF  |

| bit 15        |                 |                                   |                 |                  |                 |                 | bit 8   |

| U-0           | U-0             | U-0                               | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0   |

| _             | _               | _                                 | INT1IF          | CNIF             | AC1IF           | MI2C1IF         | SI2C1IF |

| bit 7         |                 |                                   |                 |                  |                 |                 | bit (   |

| Legend:       |                 |                                   |                 |                  |                 |                 |         |

| R = Readable  | e bit           | W = Writable                      | bit             | U = Unimpler     | mented bit, rea | d as '0'        |         |

| -n = Value at | POR             | '1' = Bit is set                  | t               | '0' = Bit is cle | ared            | x = Bit is unkr | iown    |

| bit 12        | U2TXIF: UAR     | RT2 Transmitte                    | r Interrupt Fla | g Status bit     |                 |                 |         |

|               | 1 = Interrupt r | request has oc                    | curred          | -                |                 |                 |         |

|               | •               | request has no                    |                 |                  |                 |                 |         |

| bit 11        |                 | RT2 Receiver I                    |                 | Status bit       |                 |                 |         |

|               |                 | request has oc                    |                 |                  |                 |                 |         |

| bit 13        | -               | request has no                    |                 | :.               |                 |                 |         |

| DIL 13        |                 | nal Interrupt 2<br>request has oc | 0               | п                |                 |                 |         |

|               | •               | request has no                    |                 |                  |                 |                 |         |

| bit 12        | -               | Interrupt Flag                    |                 |                  |                 |                 |         |

|               | 1 = Interrupt r | request has oc<br>request has no  | curred          |                  |                 |                 |         |

| bit 11        | -               | Interrupt Flag                    |                 |                  |                 |                 |         |

|               |                 | request has oc                    |                 |                  |                 |                 |         |

|               |                 | request has no                    |                 |                  |                 |                 |         |

| bit 10        | OC4IF: Outpu    | ut Compare Ch                     | nannel 4 Interr | upt Flag Status  | s bit           |                 |         |

|               | •               | request has oc<br>request has no  |                 |                  |                 |                 |         |

| bit 9         | -               | -                                 |                 | upt Flag Status  | bit             |                 |         |

|               | -               | request has oc                    |                 | optillag etailet | 2               |                 |         |

|               | •               | equest has no                     |                 |                  |                 |                 |         |

| bit 8         | DMA2IF: DM      | A Channel 2 D                     | ata Transfer (  | Complete Interr  | upt Flag Status | s bit           |         |

|               |                 | request has oc<br>request has no  |                 |                  |                 |                 |         |

| bit 7-5       | Unimplemen      | ted: Read as '                    | 0'              |                  |                 |                 |         |

| bit 4         | INT1IF: Exter   | nal Interrupt 1                   | Flag Status b   | it               |                 |                 |         |

|               |                 | request has oc<br>request has no  |                 |                  |                 |                 |         |

| bit 3         | -               | -                                 |                 | Flag Status bit  |                 |                 |         |

|               | 1 = Interrupt r | request has oc<br>request has no  | curred          | -                |                 |                 |         |

| bit 2         | •               | g Comparator                      |                 | ag Status bit    |                 |                 |         |

| -             |                 | request has oc                    | -               | J                |                 |                 |         |

|               | 0 = Interrupt r | -                                 |                 |                  |                 |                 |         |

# REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

|                    | -1: DMAX                                                    |                                      |                                                                 |                                    |                 |                  |            |

|--------------------|-------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------|------------------------------------|-----------------|------------------|------------|

| R/W-0              | R/W-0                                                       | R/W-0                                | R/W-0                                                           | R/W-0                              | U-0             | U-0              | U-0        |

| CHEN               | SIZE                                                        | DIR                                  | HALF                                                            | NULLW                              | —               | —                | —          |

| bit 15             |                                                             |                                      |                                                                 | •                                  |                 |                  | bit 8      |

|                    |                                                             |                                      |                                                                 |                                    |                 |                  |            |

| U-0                | U-0                                                         | R/W-0                                | R/W-0                                                           | U-0                                | U-0             | R/W-0            | R/W-0      |

|                    |                                                             | AMODE1                               | AMODE0                                                          | —                                  | —               | MODE1            | MODE0      |

| bit 7              |                                                             |                                      |                                                                 |                                    |                 |                  | bit C      |

| Legend:            |                                                             |                                      |                                                                 |                                    |                 |                  |            |

| R = Readable       | bit                                                         | W = Writable                         | hit                                                             | U = Unimpler                       | nented bit, rea | d as '0'         |            |

| -n = Value at F    |                                                             | '1' = Bit is set                     |                                                                 | '0' = Bit is cle                   |                 | x = Bit is unkn  | own        |

|                    | ÖN                                                          | 1 – Dit 13 36t                       |                                                                 |                                    | aleu            |                  | lowin      |

| bit 15             | CHEN: DMA                                                   | Channel Enabl                        | e bit                                                           |                                    |                 |                  |            |

|                    | 1 = Channel i                                               | s enabled                            |                                                                 |                                    |                 |                  |            |

|                    | 0 = Channel i                                               | s disabled                           |                                                                 |                                    |                 |                  |            |

| bit 14             | SIZE: Data Tr                                               | ansfer Size bit                      |                                                                 |                                    |                 |                  |            |

|                    | 1 = Byte<br>0 = Word                                        |                                      |                                                                 |                                    |                 |                  |            |

| bit 13             | DIR: Transfer                                               | Direction bit (s                     | source/destina                                                  | tion bus select                    | t)              |                  |            |

|                    |                                                             | m DMA RAM a<br>m peripheral a        | •                                                               |                                    |                 |                  |            |

| bit 12             |                                                             | Block Transfer                       |                                                                 |                                    |                 |                  |            |

| 5.1.12             | 1 = Initiates b                                             | lock transfer co<br>lock transfer co | omplete interru                                                 | upt when half c                    | of the data has |                  |            |

| bit 11             |                                                             | Data Periphera                       | -                                                               | -                                  |                 |                  |            |

|                    |                                                             | write to periphe                     |                                                                 |                                    | write (DIR bit  | must also be cle | ar)        |

| bit 10-6           | -                                                           | ted: Read as '                       | 0'                                                              |                                    |                 |                  |            |

| bit 5-4            | -                                                           | -: DMA Chann                         |                                                                 | lode Select bit                    | S               |                  |            |

|                    | 11 = Reserve                                                |                                      | 5                                                               |                                    |                 |                  |            |

|                    |                                                             | al Indirect Add                      |                                                                 |                                    |                 |                  |            |

|                    | -                                                           | Indirect withou<br>Indirect with F   |                                                                 |                                    |                 |                  |            |

|                    | -                                                           |                                      |                                                                 | mode                               |                 |                  |            |

| hit 3-2            | Unimplemen                                                  | ted: Read as '                       |                                                                 |                                    |                 |                  |            |

| bit 3-2<br>bit 1-0 | Unimplemen                                                  |                                      |                                                                 | de Select hits                     |                 |                  |            |

| bit 3-2<br>bit 1-0 | MODE<1:0>:                                                  | DMA Channel                          | Operating Mo                                                    |                                    | k transfer from | n/to each DMA R  | AM buffer) |

|                    | <b>MODE&lt;1:0&gt;:</b><br>11 = One-Sho                     | DMA Channel                          | Operating Mo<br>nodes are ena                                   | abled (one bloc                    | k transfer from | n/to each DMA R  | AM buffer) |

|                    | MODE<1:0>:<br>11 = One-Sho<br>10 = Continuo<br>01 = One-Sho | DMA Channel<br>ot, Ping-Pong r       | Operating Mo<br>nodes are ena<br>modes are en<br>nodes are disa | abled (one bloc<br>nabled<br>abled | k transfer from | n/to each DMA R  | AM buffer) |

# REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

| U-0                               | U-0          | U-0                                 | U-0            | U-0                  | R/W-0            | U-0                | U-0   |

|-----------------------------------|--------------|-------------------------------------|----------------|----------------------|------------------|--------------------|-------|

| —                                 | —            | —                                   | —              | —                    | CMPMD            | —                  | —     |

| bit 15                            |              |                                     |                |                      |                  |                    | bit 8 |

|                                   |              |                                     |                |                      |                  |                    |       |

| U-0                               | U-0          | R/W-0                               | U-0            | U-0                  | U-0              | R/W-0              | U-0   |

| —                                 | —            | QEI2MD                              |                | —                    | —                | I2C2MD             | —     |

| bit 7                             |              |                                     |                |                      |                  |                    | bit 0 |

|                                   |              |                                     |                |                      |                  |                    |       |

| Legend:                           |              |                                     |                |                      |                  |                    |       |

| R = Readable bit W = Writable bit |              |                                     |                | U = Unimplen         | nented bit, read | d as '0'           |       |

| -n = Value a                      | t POR        | '1' = Bit is set                    |                | '0' = Bit is cleared |                  | x = Bit is unknown |       |

|                                   |              |                                     |                |                      |                  |                    |       |

| bit 15-11                         | Unimplemen   | ted: Read as '                      | כ'             |                      |                  |                    |       |

| bit 10                            | CMPMD: Ana   | alog Comparato                      | or Module Disa | ble bit              |                  |                    |       |

|                                   |              | omparator mode                      |                |                      |                  |                    |       |

| bit 9-6                           | Unimplemen   | ted: Read as '                      | )'             |                      |                  |                    |       |

| bit 5                             | QEI2MD: QE   | I2 Module Disa                      | ble bit        |                      |                  |                    |       |

|                                   |              | dule is disabled<br>dule is enabled |                |                      |                  |                    |       |

| bit 4-2                           | Unimplemen   | ted: Read as '                      | )'             |                      |                  |                    |       |

| bit 1                             | -            | 2 Module Disab                      |                |                      |                  |                    |       |

|                                   | 1 = I2C2 mod | lule is disabled                    |                |                      |                  |                    |       |

|                                   | 0 = I2C2 mod | lule is enabled                     |                |                      |                  |                    |       |

| bit 0                             | Unimplemen   | ted: Read as '                      | )'             |                      |                  |                    |       |

|                                   |              |                                     |                |                      |                  |                    |       |

### REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

#### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0        | U-0                                                                     | U-0                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| —          | —                                                                       | —                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            |                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| U-0        | U-0                                                                     | U-0                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| —          | —                                                                       | _                                                                                                                                                                  | REFOMD                                                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ·          | •                                                                       |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| e bit      | W = Writable I                                                          | oit                                                                                                                                                                | U = Unimplem                                                                                                                                                                                                                                                                                                                                                                       | nented bit, read                                                                                                                                                                                                                                                                                                            | l as '0'                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| POR        | '1' = Bit is set                                                        |                                                                                                                                                                    | 0' = Bit is cleared $x = Bit is unl$                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            | nown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            |                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Unimplemen | ted: Read as 'o                                                         | )'                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| REFOMD: Re | eference Clock                                                          | Generator Mod                                                                                                                                                      | dule Disable bit                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |