Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                      |

| Number of I/O              | 58                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs406-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

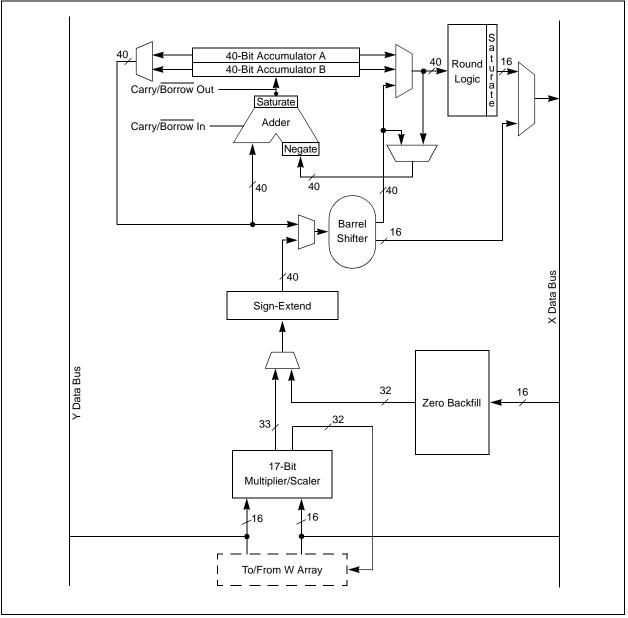

#### FIGURE 3-3: DSP ENGINE BLOCK DIAGRAM

| TABLE 4-34: | HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ32GS606 AND dsPIC33FJ64GS606 DEVICES |  |

|-------------|--------------------------------------------------------------------------------------|--|

|-------------|--------------------------------------------------------------------------------------|--|

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                 | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6  | Bit 5   | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     | All<br>Resets |

|--------------|-------------|--------|------------------------|--------|----------|----------|----------|----------|----------|-------------|--------|---------|-----------|-----------|-----------|-----------|-----------|---------------|

| ADCON        | 0300        | ADON   | -                      | ADSIDL | SLOWCLK  | —        | GSWTRG   | _        | FORM     | EIE         | ORDER  | SEQSAMP | ASYNCSAMP | —         | ADCS2     | ADCS1     | ADCS0     | 0003          |

| ADPCFG       | 0302        |        |                        |        |          |          |          |          | PC       | CFG<15:0>   |        |         |           |           |           |           |           | 0000          |

| ADSTAT       | 0306        | —      | _                      | _      | P12RDY   | —        | _        |          | _        | P7RDY       | P6RDY  | P5RDY   | P4RDY     | P3RDY     | P2RDY     | P1RDY     | PORDY     | 0000          |

| ADBASE       | 0308        |        |                        |        |          |          |          |          | ADBASE<1 | 15:1>       |        |         |           |           |           |           | -         | 0000          |

| ADCPC0       | 030A        | IRQEN1 | PEND1                  | SWTRG1 | TRGSRC14 | TRGSRC13 | TRGSRC12 | TRGSRC11 | TRGSRC10 | IRQEN0      | PEND0  | SWTRG0  | TRGSRC04  | TRGSRC03  | TRGSRC02  | TRGSRC01  | TRGSRC00  | 0000          |

| ADCPC1       | 030C        | IRQEN3 | PEND3                  | SWTRG3 | TRGSRC34 | TRGSRC33 | TRGSRC32 | TRGSRC31 | TRGSRC30 | IRQEN2      | PEND2  | SWTRG2  | TRGSRC24  | TRGSRC23  | TRGSRC22  | TRGSRC21  | TRGSRC20  | 0000          |

| ADCPC2       | 030E        | IRQEN5 | PEND5                  | SWTRG5 | TRGSRC54 | TRGSRC53 | TRGSRC52 | TRGSRC51 | TRGSRC50 | IRQEN4      | PEND4  | SWTRG4  | TRGSRC44  | TRGSRC43  | TRGSRC42  | TRGSRC41  | TRGSRC40  | 0000          |

| ADCPC3       | 0310        | IRQEN7 | PEND7                  | SWTRG7 | TRGSRC74 | TRGSRC73 | TRGSRC72 | TRGSRC71 | TRGSRC70 | IRQEN6      | PEND6  | SWTRG6  | TRGSRC64  | TRGSRC63  | TRGSRC62  | TRGSRC61  | TRGSRC640 | 0000          |

| ADCPC6       | 0316        | _      | —                      | -      | —        | —        | —        | -        | _        | IRQEN12     | PEND12 | SWTRG12 | TRGSRC124 | TRGSRC123 | TRGSRC122 | TRGSRC121 | TRGSRC120 | 0000          |

| ADCBUF0      | 0340        |        |                        |        |          |          |          |          |          |             |        |         | xxxx      |           |           |           |           |               |

| ADCBUF1      | 0342        |        | ADC Data Buffer 1 xxxx |        |          |          |          |          |          |             |        |         | xxxx      |           |           |           |           |               |

| ADCBUF2      | 0344        |        | ADC Data Buffer 2 xxxx |        |          |          |          |          |          |             |        |         | xxxx      |           |           |           |           |               |

| ADCBUF3      | 0346        |        | ADC Data Buffer 3 xxxx |        |          |          |          |          |          |             |        |         | XXXX      |           |           |           |           |               |

| ADCBUF4      | 0348        |        |                        |        |          |          |          |          | ADC      | Data Buffe  | r 4    |         |           |           |           |           |           | XXXX          |

| ADCBUF5      | 034A        |        |                        |        |          |          |          |          | ADC      | Data Buffe  | r 5    |         |           |           |           |           |           | XXXX          |

| ADCBUF6      | 034C        |        |                        |        |          |          |          |          | ADC      | Data Buffe  | r 6    |         |           |           |           |           |           | XXXX          |

| ADCBUF7      | 034E        |        |                        |        |          |          |          |          | ADC      | Data Buffe  | r 7    |         |           |           |           |           |           | XXXX          |

| ADCBUF8      | 0350        |        |                        |        |          |          |          |          | ADC      | Data Buffe  | r 8    |         |           |           |           |           |           | xxxx          |

| ADCBUF9      | 0352        |        |                        |        |          |          |          |          | ADC      | Data Buffe  | r 9    |         |           |           |           |           |           | xxxx          |

| ADCBUF10     | 0354        |        |                        |        |          |          |          |          | ADC      | Data Buffer | 10     |         |           |           |           |           |           | xxxx          |

| ADCBUF11     | 0356        |        |                        |        |          |          |          |          | ADC      | Data Buffer | 11     |         |           |           |           |           |           | xxxx          |

| ADCBUF12     | 0358        |        |                        |        |          |          |          |          | ADC      | Data Buffer | 12     |         |           |           |           |           |           | xxxx          |

| ADCBUF13     | 035A        |        |                        |        |          |          |          |          | ADC      | Data Buffer | 13     |         |           |           |           |           |           | xxxx          |

| ADCBUF14     | 035C        |        |                        |        |          |          |          |          | -        | Data Buffer |        |         |           |           |           |           |           | xxxx          |

| ADCBUF15     | 035E        |        |                        |        |          |          |          |          | ADC      | Data Buffer | 15     |         |           |           |           |           |           | xxxx          |

| ADCBUF24     | 0370        |        |                        |        |          |          |          |          | ADC      | Data Buffer | 24     |         |           |           |           |           |           | xxxx          |

| ADCBUF25     | 0372        |        |                        |        |          |          |          |          | ADC      | Data Buffer | 25     |         |           |           |           |           |           | XXXX          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

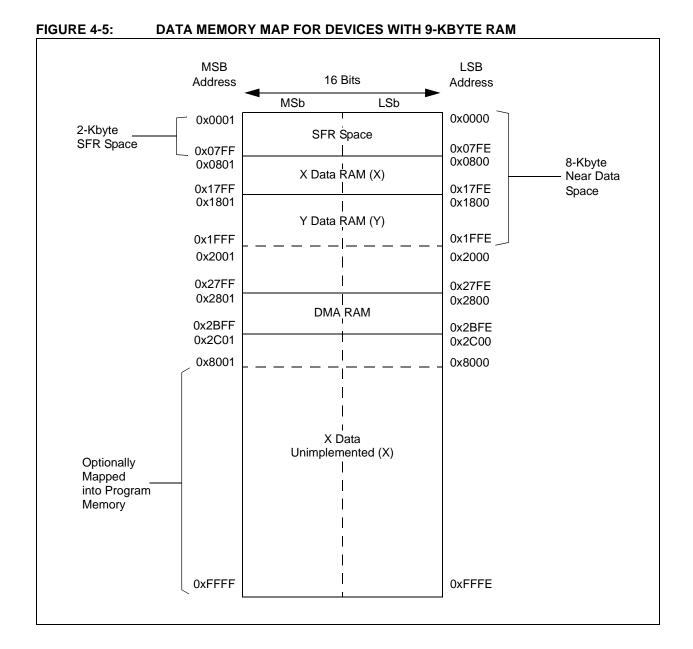

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 8000h and higher maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

# Note: PSV access is temporarily disabled during Table Reads/Writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data, to execute in a single cycle.

#### When CORCON < 2 > = 1 and EA < 15 > = 1: **Program Space** Data Space **PSVPAG** 15 0 0x000000 0x0000 02 Data EA<14:0> 0x010000 0x018000 The data in the page designated by PSVPAG is mapped into the upper half of the data memory 0x8000 space... **PSV** Area ...while the lower 15 bits of the EA specify an exact address within 0xFFFF the PSV area. This corresponds exactly to the same lower 15 bits of the actual program space address. 0x800000

#### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                                                                                     | R/W-0 <sup>(1)</sup>                                                                      | U-0             | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

| WR                    | WREN                                                                                                     | WRERR                                                                                     | —               | _                     | —                     | —                     | —                     |  |  |  |  |

| bit 15                |                                                                                                          | 1                                                                                         |                 | I.                    |                       |                       | bit 8                 |  |  |  |  |

|                       |                                                                                                          |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

| U-0                   | R/W-0 <sup>(1)</sup>                                                                                     | U-0                                                                                       | U-0             | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  |  |  |  |  |

| _                     | ERASE                                                                                                    |                                                                                           | —               | NVMOP3 <sup>(2)</sup> | NVMOP2 <sup>(2)</sup> | NVMOP1 <sup>(2)</sup> | NVMOP0 <sup>(2)</sup> |  |  |  |  |

| bit 7                 |                                                                                                          |                                                                                           |                 |                       |                       | •                     | bit 0                 |  |  |  |  |

|                       |                                                                                                          |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

| Legend:               |                                                                                                          | SO = Settal                                                                               | ole Only bit    |                       |                       |                       |                       |  |  |  |  |

| R = Readable          | bit                                                                                                      | W = Writabl                                                                               | e bit           | U = Unimpler          | mented bit, read      | l as '0'              |                       |  |  |  |  |

| -n = Value at F       | POR                                                                                                      | '1' = Bit is s                                                                            | et              | '0' = Bit is cle      | ared                  | x = Bit is unkr       | nown                  |  |  |  |  |

|                       |                                                                                                          |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

| bit 15                | WR: Write Con                                                                                            | trol bit <sup>(1)</sup>                                                                   |                 |                       |                       |                       |                       |  |  |  |  |

|                       | 1 = Initiates a                                                                                          |                                                                                           |                 |                       | on; the operation     | on is self-timed      | and the bit is        |  |  |  |  |

|                       | cleared by<br>0 = Program of                                                                             | hardware one                                                                              |                 |                       | 2                     |                       |                       |  |  |  |  |

| bit 14                | WREN: Write E                                                                                            | -                                                                                         |                 |                       | 5                     |                       |                       |  |  |  |  |

| DIL 14                | 1 = Enables Flash program/erase operations                                                               |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

|                       | 0 = Inhibits Fla                                                                                         |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

| bit 13                | WRERR: Write                                                                                             |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

|                       |                                                                                                          | 1 = An improper program or erase sequence attempt or termination has occurred (bit is set |                 |                       |                       |                       |                       |  |  |  |  |

|                       | automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

|                       |                                                                                                          |                                                                                           |                 | pleted normally       | /                     |                       |                       |  |  |  |  |

| bit 12-7              | Unimplemente                                                                                             |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

| bit 6                 | ERASE: Erase                                                                                             | •                                                                                         |                 |                       |                       |                       |                       |  |  |  |  |

|                       | 1 = Performs tl<br>0 = Performs tl                                                                       |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

| bit 5-4               | Unimplemente                                                                                             |                                                                                           |                 |                       |                       | on the next w         | i communa             |  |  |  |  |

| bit 3-0               | NVMOP<3:0>:                                                                                              |                                                                                           |                 | s(1,2)                |                       |                       |                       |  |  |  |  |

|                       | If ERASE = 1:                                                                                            |                                                                                           |                 | ,<br>,                |                       |                       |                       |  |  |  |  |

|                       | II ERASE = 1:<br>1111 = Memory bulk erase operation                                                      |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

|                       | 1101 = Erases General Segment (GS)                                                                       |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

|                       | 0011 = No operation<br>0010 = Memory page erase operation                                                |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

|                       | 0001 = No ope                                                                                            |                                                                                           | operation       |                       |                       |                       |                       |  |  |  |  |

|                       | 0000 = Erases                                                                                            |                                                                                           | figuration regi | ister byte            |                       |                       |                       |  |  |  |  |

|                       | If ERASE = 0:                                                                                            |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

|                       | 1111 = No ope                                                                                            |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

|                       | 1101 = No ope<br>0011 = Memory                                                                           |                                                                                           | m operation     |                       |                       |                       |                       |  |  |  |  |

|                       | 0010 = No ope                                                                                            |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

|                       | 0001 = Memor                                                                                             | y row progran                                                                             |                 |                       |                       |                       |                       |  |  |  |  |

|                       | 0000 = Program                                                                                           | ms a single C                                                                             | onfiguration r  | egister byte          |                       |                       |                       |  |  |  |  |

| Note 1: The           | ese bits can only                                                                                        | be reset on a                                                                             | Power-on Re     | eset.                 |                       |                       |                       |  |  |  |  |

|                       | -                                                                                                        |                                                                                           |                 |                       |                       |                       |                       |  |  |  |  |

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

2: All other combinations of NVMOP<3:0> are unimplemented.

#### REGISTER 7-14: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

- bit 1 MI2C1IE: I2C1 Master Events Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

| U-0          | R/W-1         | R/W-0                                                                          | R/W-0           | U-0               | R/W-1              | R/W-0          | R/W-0   |  |  |  |  |  |  |

|--------------|---------------|--------------------------------------------------------------------------------|-----------------|-------------------|--------------------|----------------|---------|--|--|--|--|--|--|

| _            | T2IP2         | T2IP1                                                                          | T2IP0           |                   | OC2IP2             | OC2IP1         | OC2IP0  |  |  |  |  |  |  |

| bit 15       | ·             |                                                                                |                 |                   |                    |                | bit     |  |  |  |  |  |  |

| U-0          | R/W-1         | R/W-0                                                                          | R/W-0           | U-0               | R/W-1              | ΡΛΛΙΟ          | R/W-0   |  |  |  |  |  |  |

|              | IC2IP2        | IC2IP1                                                                         | IC2IP0          |                   | DMA0IP2            |                | DMA0IP0 |  |  |  |  |  |  |

| bit 7        | 102112        | 102.11                                                                         | 10211 0         |                   | Dim ton 2          |                | bit     |  |  |  |  |  |  |

| Legend:      |               |                                                                                |                 |                   |                    |                |         |  |  |  |  |  |  |

| R = Readab   | le bit        | W = Writable                                                                   | bit             | U = Unimple       | mented bit, read   | l as '0'       |         |  |  |  |  |  |  |

| -n = Value a |               | '1' = Bit is set                                                               |                 | ʻ0' = Bit is cl   |                    |                | nown    |  |  |  |  |  |  |

| bit 15       | Unimplement   | nted: Read as '                                                                | 0'              |                   |                    |                |         |  |  |  |  |  |  |

| bit 14-12    | -             | Timer2 Interrupt                                                               |                 |                   |                    |                |         |  |  |  |  |  |  |

|              |               | upt is Priority 7                                                              | ,               | ty interrupt)     |                    |                |         |  |  |  |  |  |  |

|              | •             |                                                                                |                 |                   |                    |                |         |  |  |  |  |  |  |

|              | •             | •                                                                              |                 |                   |                    |                |         |  |  |  |  |  |  |

|              | 001 = Interru | pt is Priority 1                                                               |                 |                   |                    |                |         |  |  |  |  |  |  |

|              | 000 = Interru | ipt source is dis                                                              | sabled          |                   |                    |                |         |  |  |  |  |  |  |

| bit 11       | Unimplemer    | nted: Read as '                                                                | 0'              |                   |                    |                |         |  |  |  |  |  |  |

| bit 10-8     |               | <b>OC2IP&lt;2:0&gt;:</b> Output Compare Channel 2 Interrupt Priority bits      |                 |                   |                    |                |         |  |  |  |  |  |  |

|              | 111 = Interru | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul> |                 |                   |                    |                |         |  |  |  |  |  |  |

|              | •             |                                                                                |                 |                   |                    |                |         |  |  |  |  |  |  |

|              | •             |                                                                                |                 |                   |                    |                |         |  |  |  |  |  |  |

|              |               | ipt is Priority 1<br>ipt source is dis                                         | sabled          |                   |                    |                |         |  |  |  |  |  |  |

| bit 7        |               | nted: Read as '                                                                |                 |                   |                    |                |         |  |  |  |  |  |  |

| bit 6-4      | -             | Input Capture                                                                  |                 | errupt Priority I | oits               |                |         |  |  |  |  |  |  |

|              | 111 = Interru | pt is Priority 7                                                               | (highest priori | ty interrupt)     |                    | P2 DMA0IP1 DMA |         |  |  |  |  |  |  |

|              | •             |                                                                                |                 |                   |                    |                |         |  |  |  |  |  |  |

|              | •             |                                                                                |                 |                   |                    |                |         |  |  |  |  |  |  |

|              |               | upt is Priority 1<br>upt source is dis                                         | sabled          |                   |                    |                |         |  |  |  |  |  |  |

| bit 3        |               | nted: Read as '                                                                |                 |                   |                    |                |         |  |  |  |  |  |  |

| bit 2-0      | DMA0IP<2:0    | >: DMA Chanr                                                                   | nel 0 Data Tra  | nsfer Complet     | e Interrupt Priori | ty bits        |         |  |  |  |  |  |  |

|              | 111 = Interru | pt is Priority 7                                                               | (highest priori | ty interrupt)     |                    | -              |         |  |  |  |  |  |  |

|              | •             |                                                                                |                 |                   |                    |                |         |  |  |  |  |  |  |

|              | •             |                                                                                |                 |                   |                    |                |         |  |  |  |  |  |  |

|              |               |                                                                                |                 |                   |                    |                |         |  |  |  |  |  |  |

|              |               | ipt is Priority 1<br>ipt source is dis                                         |                 |                   |                    |                |         |  |  |  |  |  |  |

#### REGISTER 7-22: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0          | R/W-1                                                                        | R/W-0                                                            | R/W-0             | U-0             | R/W-1             | R/W-0             | R/W-0             |  |  |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------|-----------------|-------------------|-------------------|-------------------|--|--|--|--|--|--|--|

| _            | ADCP5IP2                                                                     | ADCP5IP1                                                         | ADCP5IP0          | _               | ADCP4IP2          | ADCP4IP1          | ADCP4IP0          |  |  |  |  |  |  |  |

| oit 15       |                                                                              | •                                                                |                   |                 |                   |                   | bit 8             |  |  |  |  |  |  |  |

|              |                                                                              | DAVO                                                             | DAMO              |                 | D 44/4            | DAMA              | DAMO              |  |  |  |  |  |  |  |

| U-0          | R/W-1<br>ADCP3IP2                                                            | R/W-0<br>ADCP3IP1                                                | R/W-0<br>ADCP3IP0 | U-0             | R/W-1<br>ADCP2IP2 | R/W-0<br>ADCP2IP1 | R/W-0<br>ADCP2IP0 |  |  |  |  |  |  |  |

| <br>bit 7    | ADCF3IF2                                                                     | ADCESIEL                                                         | ADCF3IFU          | _               | ADGFZIFZ          | ADGFZIFT          | bit (             |  |  |  |  |  |  |  |

|              |                                                                              |                                                                  |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| Legend:      |                                                                              |                                                                  |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| R = Readab   | le bit                                                                       | W = Writable                                                     | bit               | U = Unimple     | emented bit, read | 1 as '0'          |                   |  |  |  |  |  |  |  |

| -n = Value a | t POR                                                                        | '1' = Bit is set                                                 |                   | '0' = Bit is cl | eared             | x = Bit is unkr   | nown              |  |  |  |  |  |  |  |

|              |                                                                              |                                                                  | _                 |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 15       | -                                                                            | ted: Read as '                                                   |                   |                 | Dui a vitu de ita |                   |                   |  |  |  |  |  |  |  |

| bit 14-12    |                                                                              | <b>0&gt;:</b> ADC Pair 5                                         |                   | =               | Phoney bits       |                   |                   |  |  |  |  |  |  |  |

|              | <ul><li>111 = Interrupt is Priority 7 (highest priority interrupt)</li></ul> |                                                                  |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                            |                                                                  |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •<br>001 – Interrur                                                          | •<br>001 = Interrupt is Priority 1                               |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              |                                                                              | ot source is dis                                                 | abled             |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 11       | Unimplemen                                                                   | ted: Read as '                                                   | 0'                |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 10-8     | ADCP4IP<2:0                                                                  | ADCP4IP<2:0>: ADC Pair 4 Conversion Done Interrupt Priority bits |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | 111 = Interrup                                                               | 111 = Interrupt is Priority 7 (highest priority interrupt)       |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                            |                                                                  |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                            |                                                                  |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | 001 = Interrup                                                               | 001 = Interrupt is Priority 1                                    |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                            | ot source is dis                                                 |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 7        | -                                                                            | ted: Read as '                                                   |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 6-4      |                                                                              | 0>: ADC Pair 3                                                   |                   | -               | Priority bits     |                   |                   |  |  |  |  |  |  |  |

|              | 111 = Interrup                                                               | ot is Priority 7 (                                               | highest priority  | y interrupt)    |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                            |                                                                  |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                            |                                                                  |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | 001 = Interrup                                                               | •                                                                | ablad             |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 3        | -                                                                            | ot source is dis<br><b>ted:</b> Read as '                        |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

| bit 2-0      | -                                                                            | D>: ADC Pair 2                                                   |                   | one Interrunt   | Priority bits     |                   |                   |  |  |  |  |  |  |  |

| 5h 2-0       |                                                                              | ot is Priority 7 (                                               |                   | =               | IT HOILY DIS      |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                            |                                                                  |                   | ,               |                   |                   |                   |  |  |  |  |  |  |  |

|              |                                                                              |                                                                  |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •                                                                            |                                                                  |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

|              | •<br>•<br>001 = Interrup                                                     | nt is Priority 1                                                 |                   |                 |                   |                   |                   |  |  |  |  |  |  |  |

#### REGISTER 7-44: IPC28: INTERRUPT PRIORITY CONTROL REGISTER 28

#### REGISTER 16-1: PTCON: PWM TIME BASE CONTROL REGISTER (CONTINUED)

bit 3-0 SEVTPS<3:0>: PWM Special Event Trigger Output Postscaler Select bits<sup>(1)</sup>

1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event

.

.

.

0001 = 1:2 Postscaler generates Special Event Trigger on every second compare match event 0000 = 1:1 Postscaler generates Special Event Trigger on every compare match event

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

| REGISTER 16-4: SEVTCMP: PWM SPECIAL EVENT COMPARE REGISTER |

|------------------------------------------------------------|

|------------------------------------------------------------|

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | SEVTO | CMP<12:5>         |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | U-0              | U-0             | U-0   |

|                 | 5     | SEVTCMP<4:0:     | >     |                   | —                | —               | —     |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplen      | nented bit, read | as '0'          |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkn | nown  |

bit 15-3 SEVTCMP<12:0>: Special Event Compare Count Value bits

bit 2-0 Unimplemented: Read as '0'

Note 1: One LSB = 1.04 ns (at fastest auxiliary clock rate); therefore, the minimum SEVTCMP resolution is 8.32 ns.

### REGISTER 16-14: PHASEx: PWM PRIMARY PHASE-SHIFT x REGISTER<sup>(1,2)</sup>

| R/W-0   | R/W-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0 | R/W-0   | R/W-0 |

|---------|-------|---------|---------|---------|-------|---------|-------|

|         |       | 11/00-0 | 11/00-0 | 10/00-0 |       | 10,44-0 |       |

|         |       |         | PHASE   | x<15:8> |       |         |       |

| bit 15  |       |         |         |         |       |         | bit 8 |

| R/W-0   | R/W-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0 | R/W-0   | R/W-0 |

|         |       |         | PHASE   | X<7:0>  |       |         |       |

| bit 7   |       |         |         |         |       |         | bit ( |

|         |       |         |         |         |       |         |       |

| Logondi |       |         |         |         |       |         |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 PHASEx<15:0>: PWM Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

- **Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<10:8> = 00, 01 or 10), PHASEx<15:0> = Phase-Shift Value for PWMxH and PWMxL outputs.

- True Independent Output mode (IOCONx<10:8> = 11), PHASEx<15:0> = Phase-Shift Value for PWMxH only.

- The PHASEx/SPHASEx registers provide the phase shift with respect to the master time base; therefore, the valid range is 0x0000 through period.

- **2:** If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<10:8> = 00, 01 or 10), PHASEx<15:0> = Independent Time Base Period Value for PWMxH and PWMxL.

- True Independent Output mode (IOCONx<10:8> = 11). PHASEx<15:0> = Independent Time Base Period Value for PWMxH only.

- When the PHASEx/SPHASEx registers provide the local period, the valid range is 0x0000 through 0xFFF8.

| R/W-0              | R/W-0                                                                                                                                                                                                                               | R/W-0                                     | R/W-0            | U-0              | U-0                | U-0              | U-0            |  |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------|------------------|--------------------|------------------|----------------|--|--|--|--|--|

| TRGDIV3            | TRGDIV2                                                                                                                                                                                                                             | TRGDIV1                                   | TRGDIV0          |                  | _                  |                  |                |  |  |  |  |  |

| bit 15             |                                                                                                                                                                                                                                     | 1                                         |                  |                  | L                  |                  | bit 8          |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

| R/W-0              | U-0                                                                                                                                                                                                                                 | R/W-0                                     | R/W-0            | R/W-0            | R/W-0              | R/W-0            | R/W-0          |  |  |  |  |  |

| DTM <sup>(1)</sup> | —                                                                                                                                                                                                                                   | TRGSTRT5                                  | TRGSTRT4         | TRGSTRT3         | TRGSTRT2           | TRGSTRT1         | TRGSTRT0       |  |  |  |  |  |

| bit 7              |                                                                                                                                                                                                                                     | 1                                         |                  |                  | L                  |                  | bit C          |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

| Legend:            |                                                                                                                                                                                                                                     |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

| R = Readable       | bit                                                                                                                                                                                                                                 | W = Writable                              | bit              | U = Unimpler     | mented bit, read   | l as '0'         |                |  |  |  |  |  |

| -n = Value at F    | POR                                                                                                                                                                                                                                 | '1' = Bit is set                          |                  | '0' = Bit is cle | ared               | x = Bit is unkr  | nown           |  |  |  |  |  |

| -                  |                                                                                                                                                                                                                                     |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

| bit 15-12          | TRGDIV<3:0                                                                                                                                                                                                                          | >: Trigger # Ou                           | utput Divider bi | its              |                    |                  |                |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     | er output for ev                          | •                |                  |                    |                  |                |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    | 1110 = Trigger output for every 15th trigger event<br>1101 = Trigger output for every 14th trigger event                                                                                                                            |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    | 1100 = Trigger output for every 13th trigger event                                                                                                                                                                                  |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    | 1011 = Trigger output for every 12th trigger event<br>1010 = Trigger output for every 11th trigger event                                                                                                                            |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     | •                                         |                  |                  |                    |                  |                |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     | er output for ev                          |                  |                  |                    |                  |                |  |  |  |  |  |

|                    | 1000 = Trigger output for every 9th trigger event<br>0111 = Trigger output for every 8th trigger event                                                                                                                              |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    | 0110 = Trigger output for every 7th trigger event                                                                                                                                                                                   |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    | 0101 = Trigger output for every 6th trigger event                                                                                                                                                                                   |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    | 0100 = Trigge                                                                                                                                                                                                                       | er output for ev                          | ery 5th trigger  | event            |                    |                  |                |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     | er output for ev                          |                  |                  |                    |                  |                |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     | er output for ev                          |                  |                  |                    |                  |                |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     | er output for ev                          |                  |                  |                    |                  |                |  |  |  |  |  |

| bit 11-8           |                                                                                                                                                                                                                                     | er output for ev<br><b>ted:</b> Read as ' |                  |                  |                    |                  |                |  |  |  |  |  |

| bit 7              | -                                                                                                                                                                                                                                   |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    | <b>DTM:</b> Dual Trigger Mode bit <sup>(1)</sup>                                                                                                                                                                                    |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    | <ul> <li>1 = Secondary trigger event is combined with the primary trigger event to create the PWM trigger</li> <li>0 = Secondary trigger event is not combined with the primary trigger event to create the PWM trigger;</li> </ul> |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     | rate PWM trigg                            |                  | -                | nary ingger eve    |                  |                |  |  |  |  |  |

| bit 6              | -                                                                                                                                                                                                                                   | ted: Read as '                            |                  |                  |                    |                  |                |  |  |  |  |  |

| bit 5-0            | -                                                                                                                                                                                                                                   | :0>: Trigger Po                           |                  | Enable Select    | bits               |                  |                |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     |                                           |                  |                  | rst trigger event  | t after the modu | ule is enabled |  |  |  |  |  |

|                    | •                                                                                                                                                                                                                                   | ····· <b>·</b>                            |                  |                  | 33-1-1-01          |                  |                |  |  |  |  |  |

|                    | •                                                                                                                                                                                                                                   |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    | •                                                                                                                                                                                                                                   |                                           |                  |                  |                    |                  |                |  |  |  |  |  |

|                    | 000010 - \//=                                                                                                                                                                                                                       | aits 2 PMM cvc                            | les hefore der   | erating the fire | st trigger event a | after the modul  | e is enabled   |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     |                                           |                  |                  | trigger event a    |                  |                |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     |                                           |                  |                  | st trigger event   |                  |                |  |  |  |  |  |

|                    |                                                                                                                                                                                                                                     | -                                         | Ū                | C                |                    |                  |                |  |  |  |  |  |

| Note 1. The        | e secondary PM                                                                                                                                                                                                                      | /M generator c                            | annot generat    | e PWM triage     | r interrupts       |                  |                |  |  |  |  |  |

#### REGISTER 16-18: TRGCONx: PWM TRIGGER CONTROL x REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | STRGC | MP<12:5>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | U-0             | U-0             | U-0   |

|                 |       | STRGCMP<4:0>     |       |                   | —               | —               | _     |

| bit 7           |       |                  |       | ·                 |                 |                 | bit 0 |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable bit |       | U = Unimplem      | ented bit, read | l as '0'        |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | red             | x = Bit is unkr | nown  |

### **REGISTER 16-22:** STRIGX: PWM SECONDARY TRIGGER x COMPARE VALUE REGISTER<sup>(1)</sup>

t 15-3 **STRGCMP<12:0>:** PWM Secondary Trigger Compare Value bits When the secondary PWM functions in a local time base, this register contains the compare values that can trigger the ADC module.

bit 2-0 Unimplemented: Read as '0'

**Note 1:** STRIGx cannot generate the PWM trigger interrupts.

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                   | R/W-0                                                      | U-0 | U-0          | U-0              | U-0      | U-0    |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----|--------------|------------------|----------|--------|--|--|

| SPIEN         | _                                                                                                                                                                                                                                                                                                                     | SPISIDL                                                    | _   | _            | _                |          |        |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                                       | I                                                          |     |              |                  |          | bit 8  |  |  |

|               |                                                                                                                                                                                                                                                                                                                       |                                                            |     |              |                  |          |        |  |  |

| U-0           | R/C-0                                                                                                                                                                                                                                                                                                                 | U-0                                                        | U-0 | U-0          | U-0              | R-0      | R-0    |  |  |

| —             | SPIROV                                                                                                                                                                                                                                                                                                                | —                                                          | —   | —            |                  | SPITBF   | SPIRBF |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                       |                                                            |     |              |                  |          | bit 0  |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                       | C = Clearable                                              | bit |              |                  |          |        |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                                 | W = Writable b                                             |     | U = Unimpler | mented bit, read | l as '0' |        |  |  |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                   | (1) = Bit is set $(0) = Bit is cleared x = Bit is unknown$ |     |              |                  |          |        |  |  |

|               | -                                                                                                                                                                                                                                                                                                                     |                                                            |     |              |                  |          | -      |  |  |

| bit 15        | SPIEN: SPIx Enable bit                                                                                                                                                                                                                                                                                                |                                                            |     |              |                  |          |        |  |  |