Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                      |

| Number of I/O              | 58                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs406-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70204) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies from device to device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can serve as a data, address or address offset register. The sixteenth Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

There are two classes of instruction in the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices are capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle.

As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 is shown in Figure 3-2.

## 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data space mapping feature lets any instruction access program space as if it were data space.

### 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits, right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal realtime performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain Working registers to each address space.

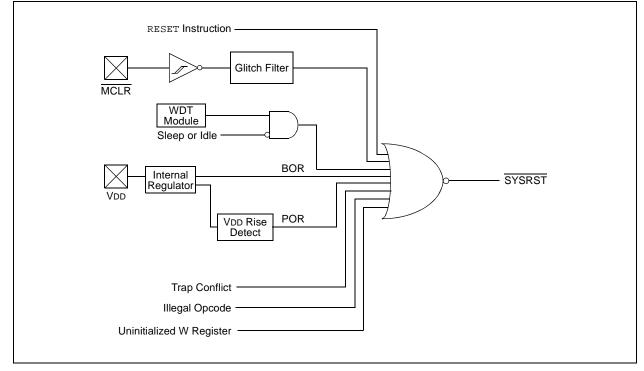

### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

- bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

## REGISTER 7-13: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | OC1IE: Output Compare Channel 1 Interrupt Enable bit |

|-------|------------------------------------------------------|

|       | 1 = Interrupt request is enabled                     |

|       | 0 = Interrupt request is not enabled                 |

| bit 1 | IC1IE: Input Capture Channel 1 Interrupt Enable bit  |

|       | 1 = Interrupt request is enabled                     |

|       | 0 = Interrupt request is not enabled                 |

| bit 0 | INTOIE: External Interrupt 0 Enable bit              |

|       | 1 = Interrupt request is enabled                     |

0 = Interrupt request is not enabled

© 2009-2014 Microchip Technology Inc.

| R/W-0           | R/W-0           | R/W-0            | U-0          | U-0                                | U-0      | U-0                | U-0   |  |  |

|-----------------|-----------------|------------------|--------------|------------------------------------|----------|--------------------|-------|--|--|

| PWM2IE          | PWM1IE          | ADCP12IE         | —            | —                                  | —        | —                  | _     |  |  |

| bit 15          |                 |                  |              |                                    |          |                    | bit 8 |  |  |

|                 |                 |                  |              |                                    |          |                    |       |  |  |

| U-0             | U-0             | U-0              | U-0          | U-0                                | U-0      | U-0                | U-0   |  |  |

|                 | —               | —                | —            | —                                  | _        | —                  | —     |  |  |

| bit 7           |                 |                  |              |                                    |          |                    | bit 0 |  |  |

| <b></b>         |                 |                  |              |                                    |          |                    |       |  |  |

| Legend:         |                 |                  |              |                                    |          |                    |       |  |  |

| R = Readable    | bit             | W = Writable I   | bit          | U = Unimplemented bit, read as '0' |          |                    |       |  |  |

| -n = Value at F | POR             | '1' = Bit is set |              | '0' = Bit is cle                   | eared    | x = Bit is unknown |       |  |  |

|                 |                 |                  |              |                                    |          |                    |       |  |  |

| bit 15          | PWM2IE: PW      | /M2 Interrupt Ei | nable bit    |                                    |          |                    |       |  |  |

|                 | •               | request is enab  |              |                                    |          |                    |       |  |  |

|                 | 0 = Interrupt i | request is not e | nabled       |                                    |          |                    |       |  |  |

| bit 14          | PWM1IE: PW      | /M1 Interrupt Ei | nable bit    |                                    |          |                    |       |  |  |

|                 | 1 = Interrupt i | request is enab  | led          |                                    |          |                    |       |  |  |

|                 | 0 = Interrupt i | request is not e | nabled       |                                    |          |                    |       |  |  |

| bit 13          | ADCP12IE: A     | DC Pair 12 Co    | nversion Don | e Interrupt Ena                    | able bit |                    |       |  |  |

|                 |                 | request is enab  |              |                                    |          |                    |       |  |  |

|                 | 0 = Interrupt i | request is not e | nabled       |                                    |          |                    |       |  |  |

| bit 12-0        | Unimplemen      | ted: Read as '0  | )'           |                                    |          |                    |       |  |  |

### REGISTER 7-18: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0           | R/W-1                            | R/W-0                                | R/W-0            | U-0            | R/W-1             | R/W-0           | R/W-0   |

|---------------|----------------------------------|--------------------------------------|------------------|----------------|-------------------|-----------------|---------|

|               | PWM6IP2                          | PWM6IP1                              | PWM6IP0          |                | PWM5IP2           | PWM5IP1         | PWM5IP0 |

| bit 15        |                                  |                                      | •                |                |                   |                 | bit     |

| U-0           | R/W-1                            | R/W-0                                | R/W-0            | U-0            | R/W-1             | R/W-0           | R/W-0   |

|               | PWM4IP2                          | PWM4IP1                              | PWM4IP0          | _              | PWM3IP2           | PWM3IP1         | PWM3IP0 |

| oit 7         |                                  |                                      |                  |                |                   |                 | bit     |

| Legend:       |                                  |                                      |                  |                |                   |                 |         |

| R = Readabl   | e bit                            | W = Writable                         | bit              | U = Unimple    | emented bit, read | l as '0'        |         |

| -n = Value at |                                  | '1' = Bit is set                     |                  | '0' = Bit is c |                   | x = Bit is unkr | nown    |

| bit 15        | Unimplemen                       | <b>ted:</b> Read as '                | 0,               |                |                   |                 |         |

| bit 14-12     | -                                | >: PWM6 Inter                        |                  | ts             |                   |                 |         |

|               |                                  | ot is Priority 7 (                   |                  |                |                   |                 |         |

|               | •                                | -                                    |                  |                |                   |                 |         |

|               | •                                |                                      |                  |                |                   |                 |         |

|               | 001 = Interrup                   | ot is Priority 1                     |                  |                |                   |                 |         |

|               |                                  | ot source is dis                     | abled            |                |                   |                 |         |

| bit 11        | Unimplemen                       | ted: Read as '                       | 0'               |                |                   |                 |         |

| bit 10-8      | PWM5IP<2:0                       | >: PWM5 Inter                        | rupt Priority bi | ts             |                   |                 |         |

|               | 111 = Interrup                   | ot is Priority 7 (                   | highest priority | y)             |                   |                 |         |

|               | •                                |                                      |                  |                |                   |                 |         |

|               | •                                |                                      |                  |                |                   |                 |         |

|               | 001 = Interrup                   |                                      |                  |                |                   |                 |         |

|               | -                                | ot source is dis                     |                  |                |                   |                 |         |

| bit 7         | -                                | ted: Read as '                       |                  |                |                   |                 |         |

| bit 6-4       |                                  | >: PWM4 Inter                        | , ,              |                |                   |                 |         |

|               | 111 = Interrup                   | ot is Priority 7 (                   | highest priority | y)             |                   |                 |         |

|               | •                                |                                      |                  |                |                   |                 |         |

|               | •                                |                                      |                  |                |                   |                 |         |

|               | 001 = Interrup<br>000 = Interrup | ot is Priority 1<br>ot source is dis | abled            |                |                   |                 |         |

| bit 3         | Unimplemen                       | ted: Read as '                       | 0'               |                |                   |                 |         |

| bit 2-0       | PWM3IP<2:0                       | >: PWM3 Inter                        | rupt Priority bi | ts             |                   |                 |         |

|               | 111 = Interrup                   | ot is Priority 7 (                   | highest priority | y)             |                   |                 |         |

|               | •                                |                                      |                  |                |                   |                 |         |

|               | •                                |                                      |                  |                |                   |                 |         |

|               | 001 = Interrup                   | at is Priority 1                     |                  |                |                   |                 |         |

|               |                                  |                                      |                  |                |                   |                 |         |

### REGISTER 7-40: IPC24: INTERRUPT PRIORITY CONTROL REGISTER 24

| 11.0         |                                                      | 11.0                                                                       | 11.0                     | 11.0                 | 11.0             | 11.0               | 11.0   |  |  |  |

|--------------|------------------------------------------------------|----------------------------------------------------------------------------|--------------------------|----------------------|------------------|--------------------|--------|--|--|--|

| U-0          | U-0                                                  | U-0                                                                        | U-0                      | U-0                  | U-0              | U-0                | U-0    |  |  |  |

| _            | —                                                    |                                                                            |                          | —                    | —                | —                  | —      |  |  |  |

| bit 15       |                                                      |                                                                            |                          |                      |                  |                    | bit    |  |  |  |

|              |                                                      |                                                                            |                          |                      |                  |                    |        |  |  |  |

| U-0          | R/W-1                                                | R/W-0                                                                      | R/W-0                    | U-0                  | R/W-1            | R/W-0              | R/W-0  |  |  |  |

| —            | AC4IP2                                               | AC4IP1                                                                     | AC4IP0                   | —                    | AC3IP2           | AC3IP1             | AC3IP0 |  |  |  |

| bit 7        |                                                      |                                                                            |                          |                      |                  |                    | bit    |  |  |  |

|              |                                                      |                                                                            |                          |                      |                  |                    |        |  |  |  |

| Legend:      |                                                      |                                                                            |                          |                      |                  |                    |        |  |  |  |

| R = Readat   |                                                      | W = Writable                                                               |                          |                      | mented bit, read |                    |        |  |  |  |

| -n = Value a | at POR                                               | '1' = Bit is set                                                           |                          | '0' = Bit is cleared |                  | x = Bit is unknown |        |  |  |  |

| bit 6-4      | 111 = Interru<br>•<br>001 = Interru<br>000 = Interru | Analog Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis | highest priorit<br>abled |                      |                  |                    |        |  |  |  |

| bit 3        | -                                                    | ted: Read as '                                                             |                          |                      |                  |                    |        |  |  |  |

|              | AC3IP<2:0>:                                          | Analog Compa                                                               |                          |                      |                  |                    |        |  |  |  |

| bit 2-0      |                                                      | 111 = Interrupt is Priority 7 (highest priority)                           |                          |                      |                  |                    |        |  |  |  |

| bit 2-0      | 111 = Interru                                        | pt is Priority 7 (                                                         | nignest priorit          | y)                   |                  |                    |        |  |  |  |

| bit 2-0      | 111 = Interru<br>•                                   | pt is Priority 7 (                                                         | nignest priorit          | <b>y</b> )           |                  |                    |        |  |  |  |

| bit 2-0      | 111 = Interru<br>•                                   | pt is Priority 7 (                                                         | nignest priorit          | <i>y</i> /           |                  |                    |        |  |  |  |

| bit 2-0      | •<br>•                                               | pt is Priority 7 (<br>pt is Priority 1                                     | nignest priorit          | <i>y</i> /           |                  |                    |        |  |  |  |

### REGISTER 7-42: IPC26: INTERRUPT PRIORITY CONTROL REGISTER 26

### 9.1.3 PLL CONFIGURATION

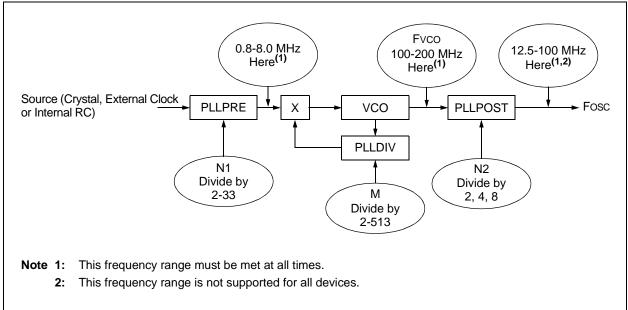

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides significant flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 9-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected in the range of 0.8 MHz to 8 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor, 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor, 'N2'. This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4 or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 100 MHz, which generates device operating speeds of 6.25-50 MIPS.

#### FIGURE 9-2: PLL BLOCK DIAGRAM

For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by Equation 9-2.

### EQUATION 9-2: Fosc CALCULATION

| FOSC = FIN *                  | ( M )                |

|-------------------------------|----------------------|

| $\Gamma OSC = \Gamma IN^{-1}$ | $\overline{N1 * N2}$ |

For example, suppose a 10 MHz crystal is being used with the selected oscillator mode of XT with PLL (see Equation 9-3).

- If PLLPRE<4:0> = 0000, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz.

- If PLLDIV<8:0> = 0x26, then M = 40. This yields a VCO output of 5 x 40 = 200 MHz, which is within the 100-200 MHz ranged needed.

- If PLLPOST<1:0> = 00, then N2 = 2. This provides a Fosc of 200/2 = 100 MHz. The resultant device operating speed is 100/2 = 40 MIPS.

### EQUATION 9-3: XT WITH PLL MODE EXAMPLE

FCY =

$$\frac{\text{Fosc}}{2} = \frac{1}{2} \left( \frac{10000000 * 40}{2 * 2} \right) = 50 \text{ MIPS}$$

| R/W-0         | R-0                                                                                                                                  | R/W-1                                                       | U-0           | U-0              | R/W-1                                   | R/W-1           | R/W-1     |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------|------------------|-----------------------------------------|-----------------|-----------|

| ENAPLL        | APLLCK                                                                                                                               | SELACLK                                                     | _             | —                | APSTSCLR2                               | APSTSCLR1       | APSTSCLR0 |

| bit 15        |                                                                                                                                      |                                                             |               |                  |                                         |                 | bit 8     |

|               |                                                                                                                                      |                                                             |               |                  |                                         |                 |           |

| R/W-0         | R/W-0                                                                                                                                | U-0                                                         | U-0           | U-0              | U-0                                     | U-0             | U-0       |

| ASRCSEL       | FRCSEL                                                                                                                               | —                                                           |               | —                |                                         | —               |           |

| bit 7         |                                                                                                                                      |                                                             |               |                  |                                         |                 | bit C     |

| Legend:       |                                                                                                                                      |                                                             |               |                  |                                         |                 |           |

| R = Readable  | e bit                                                                                                                                | W = Writable b                                              | oit           | U = Unimpler     | mented bit, read                        | as '0'          |           |

| -n = Value at | POR                                                                                                                                  | '1' = Bit is set                                            |               | '0' = Bit is cle | ared                                    | x = Bit is unkr | nown      |

| bit 15        | 1 = APLL is e                                                                                                                        |                                                             | ole bit       |                  |                                         |                 |           |

|               | 0 = APLL is d                                                                                                                        |                                                             |               |                  |                                         |                 |           |

| bit 14        |                                                                                                                                      | LL Locked Statu                                             | •             | nly)             |                                         |                 |           |

|               |                                                                                                                                      | that auxiliary Pl<br>that auxiliary Pl                      |               | ck               |                                         |                 |           |

| bit 13        | SELACLK: S                                                                                                                           | elect Auxiliary C                                           | Clock Source  | for Auxiliary C  | lock Divider bit                        |                 |           |

|               |                                                                                                                                      |                                                             |               |                  | auxiliary clock di<br>e auxiliary clock |                 |           |

| bit 12-11     | Unimplemen                                                                                                                           | ted: Read as '0                                             | ,             |                  |                                         |                 |           |

| bit 10-8      | APSTSCLR<                                                                                                                            | 2:0>: Auxiliary                                             | Clock Output  | Divider bits     |                                         |                 |           |

|               | 111 = Divideo<br>110 = Divideo<br>101 = Divideo<br>011 = Divideo<br>010 = Divideo<br>010 = Divideo<br>001 = Divideo<br>000 = Divideo | d bý 2<br>d by 4<br>d by 8<br>d by 16<br>d by 32<br>d by 64 |               |                  |                                         |                 |           |

| bit 7         | ASRCSEL: S                                                                                                                           | elect Reference                                             | Clock Source  | e for Auxiliary  | Clock bit                               |                 |           |

|               |                                                                                                                                      | scillator is the c                                          |               |                  |                                         |                 |           |

| bit 6         |                                                                                                                                      | lect Reference (<br>RC clock for au                         |               | for Auxiliary P  |                                         |                 |           |

|               | 0 = Input cloc                                                                                                                       | k source is dete                                            | ermined by th | e ASRCSEL b      | it setting                              |                 |           |

### REGISTER 9-5: ACLKCON: AUXILIARY CLOCK DIVISOR CONTROL REGISTER

NOTES:

## 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70193) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 11.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

| R/W-0              | U-0                                      | R/W-0                        | U-0                       | U-0                          | U-0              | U-0                | U-0         |

|--------------------|------------------------------------------|------------------------------|---------------------------|------------------------------|------------------|--------------------|-------------|

| TON <sup>(2)</sup> | _                                        | TSIDL <sup>(1)</sup>         | —                         | —                            | _                | —                  | _           |

| bit 15             |                                          |                              |                           |                              |                  |                    | bit         |

|                    |                                          |                              |                           |                              |                  |                    |             |

| U-0                | R/W-0                                    | R/W-0                        | R/W-0                     | U-0                          | U-0              | R/W-0              | U-0         |

|                    | TGATE <sup>(2)</sup>                     | TCKPS1 <sup>(2)</sup>        | TCKPS0 <sup>(2)</sup>     | —                            |                  | TCS <sup>(2)</sup> | _           |

| bit 7              |                                          |                              |                           |                              |                  |                    | bit         |

|                    |                                          |                              |                           |                              |                  |                    |             |

| Legend:            |                                          |                              |                           |                              |                  |                    |             |

| R = Reada          |                                          | W = Writable                 |                           | •                            | mented bit, rea  |                    |             |

| -n = Value         | at POR                                   | '1' = Bit is set             |                           | '0' = Bit is cle             | eared            | x = Bit is unkno   | own         |

|                    | TON: Timery                              | On hit(2)                    |                           |                              |                  |                    |             |

| bit 15             | 1 = Starts 16-                           |                              |                           |                              |                  |                    |             |

|                    | 0 = Stops 16-                            |                              |                           |                              |                  |                    |             |

| bit 14             | -                                        | ted: Read as '               | 0'                        |                              |                  |                    |             |

| bit 13             | -                                        | ry Stop in Idle N            |                           |                              |                  |                    |             |

|                    | 1 = Discontin                            | ues timer opera              | ation when dev            | vice enters Idle             | e mode           |                    |             |

|                    | 0 = Continues                            | s timer operatio             | n in Idle mode            | 9                            |                  |                    |             |

| bit 12-7           | -                                        | ted: Read as '               |                           |                              |                  |                    |             |

| bit 6              |                                          | ery Gated Time               | Accumulation              | Enable bit <sup>(2)</sup>    |                  |                    |             |

|                    | When TCS =                               |                              |                           |                              |                  |                    |             |

|                    | This bit is ign<br>When TCS =            |                              |                           |                              |                  |                    |             |

|                    |                                          | <u>o.</u><br>ne accumulatior | n is enabled              |                              |                  |                    |             |

|                    | 0 = Gated tim                            | ne accumulatior              | n is disabled             |                              |                  |                    |             |

| bit 5-4            | TCKPS<1:0>                               | : Timery Input               | Clock Prescal             | e Select bits <sup>(2)</sup> | )                |                    |             |

|                    | 11 = 1:256 pr                            |                              |                           |                              |                  |                    |             |

|                    | 10 = 1:64 pre<br>01 = 1:8 pres           |                              |                           |                              |                  |                    |             |

|                    | 01 = 1.0  pres<br>00 = 1:1  pres         |                              |                           |                              |                  |                    |             |

| bit 3-2            | -                                        | ted: Read as '               | 0'                        |                              |                  |                    |             |

| bit 1              | TCS: Timery                              | Clock Source S               | Select bit <sup>(2)</sup> |                              |                  |                    |             |

|                    |                                          | clock from TxCl              |                           |                              |                  |                    |             |

|                    | 0 = Internal c                           | lock (Fosc/2)                |                           |                              |                  |                    |             |

| bit 0              | Unimplemen                               | ted: Read as '               | 0'                        |                              |                  |                    |             |

|                    | When 32-bit timer<br>bit must be cleared |                              | -                         | -                            | rx Control regis | ster (TxCON<3>)    | , the TSIDL |

### **REGISTER 13-2:** TyCON: TIMERY CONTROL REGISTER (y = 3, 5)

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), these bits have no effect.

## 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70005157) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

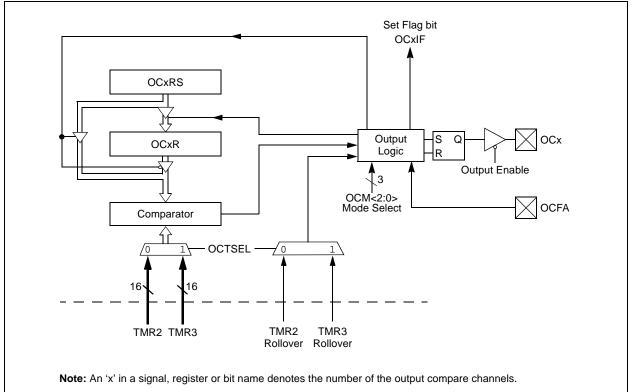

The output compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- PWM mode with Fault Protection

### FIGURE 15-1: OUTPUT COMPARE x MODULE BLOCK DIAGRAM

### 15.1 Output Compare Modes

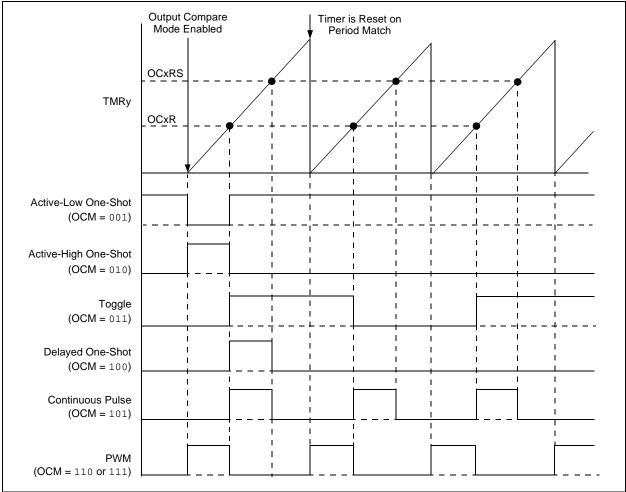

Configure the Output Compare modes by setting the appropriate Output Compare Mode (OCM<2:0>) bits in the Output Compare Control (OCxCON<2:0>) register. Table 15-1 lists the different bit settings for the Output Compare modes. Figure 15-2 illustrates the output compare operation for various modes. The user

TABLE 15-1: OUTPUT COMPARE MODES

application must disable the associated timer when writing to the Output Compare Control registers to avoid malfunctions.

Note: See "Output Compare" (DS70005157) in the "dsPIC33/PIC24 Family Reference Manual" for OCxR and OCxRS register restrictions.

| OCM<2:0> | Mode                         | OCx Pin Initial State                                                  | OCx Interrupt Generation         |  |  |

|----------|------------------------------|------------------------------------------------------------------------|----------------------------------|--|--|

| 000      | Module Disabled              | Controlled by GPIO register                                            | —                                |  |  |

| 001      | Active-Low One-Shot          | 0                                                                      | OCx rising edge                  |  |  |

| 010      | Active-High One-Shot         | 1                                                                      | OCx falling edge                 |  |  |

| 011      | Toggle                       | Current output is maintained                                           | OCx rising and falling edge      |  |  |

| 100      | Delayed One-Shot             | 0                                                                      | OCx falling edge                 |  |  |

| 101      | Continuous Pulse             | 0                                                                      | OCx falling edge                 |  |  |

| 110      | PWM without Fault Protection | <ul><li>'0' if OCxR is zero,</li><li>'1' if OCxR is non-zero</li></ul> | No interrupt                     |  |  |

| 111      | PWM with Fault Protection    | <ul><li>'0' if OCxR is zero,</li><li>'1' if OCxR is non-zero</li></ul> | OCFA falling edge for OC1 to OC4 |  |  |

### FIGURE 15-2: OUTPUT COMPARE x OPERATION

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0      | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3(1) | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 |                         |                         |                         |            |                        |                        | bit 0                  |

| Legend: ⊦          | HC = Hardware Clearable bit | HS = Hardware Settable bit         |                    |  |  |

|--------------------|-----------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit V | N = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR  | 1' = Bit is set             | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15  | PTEN: PWM Module Enable bit                                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = PWM module is enabled</li> <li>0 = PWM module is disabled</li> </ul>                                                                       |

| bit 14  | Unimplemented: Read as '0'                                                                                                                              |

| bit 13  | PTSIDL: PWM Time Base Stop in Idle Mode bit                                                                                                             |

|         | <ul> <li>1 = PWM time base halts in CPU Idle mode</li> <li>0 = PWM time base runs in CPU Idle mode</li> </ul>                                           |

| bit 12  | SESTAT: Special Event Interrupt Status bit                                                                                                              |

|         | <ul><li>1 = Special event interrupt is pending</li><li>0 = Special event interrupt is not pending</li></ul>                                             |

| bit 11  | SEIEN: Special Event Interrupt Enable bit                                                                                                               |

|         | <ul> <li>1 = Special event interrupt is enabled</li> <li>0 = Special event interrupt is disabled</li> </ul>                                             |

| bit 10  | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                |

|         | <ul> <li>1 = Active Period register is updated immediately</li> <li>0 = Active Period register updates occur on PWM cycle boundaries</li> </ul>         |

| bit 9   | SYNCPOL: Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                       |

|         | <ul><li>1 = SYNCIx/SYNCO1 polarity is inverted (active-low)</li><li>0 = SYNCIx/SYNCO1 is active-high</li></ul>                                          |

| bit 8   | SYNCOEN: Primary Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|         | <ul><li>1 = SYNCO1 output is enabled</li><li>0 = SYNCO1 output is disabled</li></ul>                                                                    |

| bit 7   | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|         | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul> |

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup>                                                                                          |

|         | 111 = Reserved<br>101 = Reserved<br>011 = SYNCI4<br>010 = SYNCI3<br>001 = SYNCI2<br>000 = SYNCI1                                                        |

| Note 1. | These bits should be shanged only when DTEN. A In addition when using the SVNChy facture, the                                                           |

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

## REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                            |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                        |

|       | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit.<br/>Hardware clears at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as $I^2C$ master)                                                                                                                                                                  |

|       | 1 = Enables Receive mode for $I^2C$ . Hardware clears at the end of the eighth bit of the master receive data byte.                                                                                                                |

|       | 0 = Receive sequence is not in progress                                                                                                                                                                                            |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|       | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware clears at the end of the master Stop sequence.                                                                                                                        |

|       | 0 = Stop condition is not in progress                                                                                                                                                                                              |

| bit 1 | RSEN: Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                              |

|       | 1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware clears at the end of the master Repeated Start sequence.                                                                                                    |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                                                                    |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                        |

|       | 1 = Initiates Start condition on SDAx and SCLx pins. Hardware clears at the end of the master Start sequence.                                                                                                                      |

|       | 0 = Start condition is not in progress                                                                                                                                                                                             |

| U-0                                    | U-0                                                                                                                                                                                                                                        | U-0              | U-0       | U-0               | U-0                | U-0                | U-0                        |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|-------------------|--------------------|--------------------|----------------------------|--|--|

| _                                      | _                                                                                                                                                                                                                                          | _                | _         | _                 | _                  | _                  | _                          |  |  |

| bit 15                                 |                                                                                                                                                                                                                                            |                  |           |                   |                    |                    | bit                        |  |  |

|                                        |                                                                                                                                                                                                                                            |                  |           |                   |                    |                    |                            |  |  |

| R/W-0                                  | R/W-0                                                                                                                                                                                                                                      | R/W-0            | R/W-0     | R/W-0             | R/W-0              | R/W-0              | R/W-0                      |  |  |

| IRQEN12                                | PEND12                                                                                                                                                                                                                                     | SWTRG12          | TRGSRC124 | TRGSRC123         | TRGSRC122          | TRGSRC121          | TRGSRC12                   |  |  |

| bit 7                                  |                                                                                                                                                                                                                                            |                  |           |                   |                    | •                  | bit                        |  |  |

|                                        |                                                                                                                                                                                                                                            |                  |           |                   |                    |                    |                            |  |  |

| Legend:                                |                                                                                                                                                                                                                                            |                  |           |                   |                    |                    |                            |  |  |

| R = Readable                           | bit                                                                                                                                                                                                                                        | W = Writable bit |           | U = Unimplem      | ented bit, read    | as 'O'             |                            |  |  |

| -n = Value at I                        | POR                                                                                                                                                                                                                                        | '1' = Bit is set |           | '0' = Bit is clea | ared               | x = Bit is unknown |                            |  |  |

|                                        |                                                                                                                                                                                                                                            |                  |           |                   |                    |                    |                            |  |  |

| bit 15-8                               | Unimplemented: Read as '0'                                                                                                                                                                                                                 |                  |           |                   |                    |                    |                            |  |  |

| bit 7                                  | IRQEN12: Interrupt Request Enable 12 bit                                                                                                                                                                                                   |                  |           |                   |                    |                    |                            |  |  |

|                                        | 1 = Enables IRQ generation when requested conversion of Channels AN25 and AN24 is comp                                                                                                                                                     |                  |           |                   |                    |                    | s completed                |  |  |

| bit 6                                  | 0 = IRQ is not generated                                                                                                                                                                                                                   |                  |           |                   |                    |                    |                            |  |  |

| DILO                                   | PEND12: Pending Conversion Status 12 bit                                                                                                                                                                                                   |                  |           |                   |                    |                    |                            |  |  |

|                                        | <ul> <li>1 = Conversion of Channels AN25 and AN24 is pending; set when selected trigger is asserted</li> <li>0 = Conversion is complete</li> </ul>                                                                                         |                  |           |                   |                    |                    | serted                     |  |  |

| bit 5 SWTRG12: Software Trigger 12 bit |                                                                                                                                                                                                                                            |                  |           |                   |                    |                    |                            |  |  |

|                                        | <ul> <li>1 = Starts conversion of AN25 (INTREF) and AN24 (EXTREF) if selected by the TRGSRCx&lt;4:0&gt; I<br/>This bit is automatically cleared by hardware when the PEND12 bit is set.</li> <li>0 = Conversion has not started</li> </ul> |                  |           |                   |                    |                    | Cx<4:0> bits <sup>(*</sup> |  |  |

| Note 1: The                            |                                                                                                                                                                                                                                            |                  |           | software trigge   | r prior to setting | g this bit to '1'. | lf other                   |  |  |

## REGISTER 22-12: ADCPC6: ADC CONVERT PAIR CONTROL REGISTER 6<sup>(2)</sup>

- conversions are in progress, the conversion is performed when the conversion resources are available.

- 2: This register is not available on dsPIC33FJ32GS406 and dsPIC33FJ64GS406 devices.

## 23.0 HIGH-SPEED ANALOG COMPARATOR

- This data sheet summarizes the features of Note 1: dsPIC33FJ32GS406/606/608/610 the dsPIC33FJ64GS406/606/608/610 and families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed Analog Comparator" (DS70296) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33F Switch Mode Power Supply (SMPS) comparator module monitors current and/or voltage transients that may be too fast for the CPU and ADC to capture.

### 23.1 Features Overview

The SMPS comparator module offers the following major features:

- 16 Selectable Comparator Inputs

- Up to Four Analog Comparators

- 10-Bit DAC for each Analog Comparator

- Programmable Output Polarity

- Interrupt Generation Capability

- DACOUT Pin to provide DAC Output

- DAC has Three Ranges of Operation:

- AVdd/2

- Internal Reference (INTREF)

- External Reference (EXTREF)

- ADC Sample-and-Convert Trigger Capability

- · Disable Capability reduces Power Consumption

- Functional Support for PWM module:

- PWM duty cycle control

- PWM period control

- PWM Fault detect

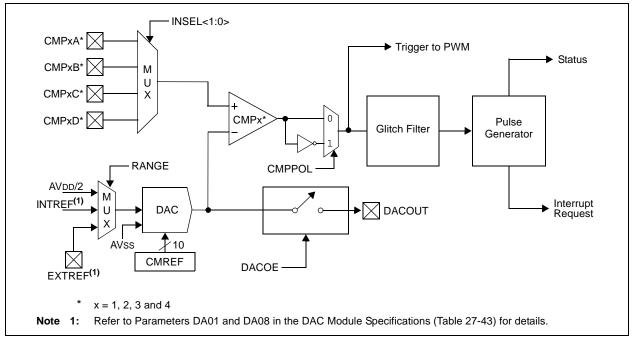

### 23.2 Module Description

Figure 23-1 shows a functional block diagram of one analog comparator from the SMPS comparator module. The analog comparator provides high-speed operation with a typical delay of 20 ns. The comparator has a typical offset voltage of  $\pm 5$  mV. The negative input of the comparator is always connected to the DAC circuit. The positive input of the comparator is connected to an analog multiplexer that selects the desired source pin.

The analog comparator input pins are typically shared with pins used by the Analog-to-Digital Converter (ADC) module. Both the comparator and the ADC can use the same pins at the same time. This capability enables a user to measure an input voltage with the ADC and detect voltage transients with the comparator.

#### FIGURE 23-1: HIGH-SPEED ANALOG COMPARATOR x MODULE BLOCK DIAGRAM

| AC CHARACTERISTICS |                 |                                                       |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |       |                        |  |

|--------------------|-----------------|-------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------|--|

| Param<br>No. Symb  |                 | Characteristic                                        |                           | Min <sup>(1)</sup>                                                                                                                                                                                                                                                                  | Max  | Units | Conditions             |  |

| IM10               | TLO:SCL         | Clock Low Time                                        | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                     | —    | μS    |                        |  |

|                    |                 |                                                       | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                     |      | μS    |                        |  |

|                    |                 |                                                       | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                     |      | μS    |                        |  |

| IM11 THI:SCL       | Clock High Time | 100 kHz mode                                          | Tcy/2 (BRG + 1)           |                                                                                                                                                                                                                                                                                     | μS   |       |                        |  |

|                    |                 |                                                       | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                     |      | μS    |                        |  |

|                    |                 |                                                       | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                     | _    | μS    |                        |  |

| IM20               | TF:SCL          | SDAx and SCLx                                         | 100 kHz mode              | _                                                                                                                                                                                                                                                                                   | 300  | ns    | CB is specified to be  |  |

|                    |                 | Fall Time                                             | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                         | 300  | ns    | from 10 to 400 pF      |  |

|                    |                 |                                                       | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                                                                                                                   | 100  | ns    |                        |  |

| IM21 TR:SCL        | TR:SCL          | SDAx and SCLx                                         | 100 kHz mode              | _                                                                                                                                                                                                                                                                                   | 1000 | ns    | CB is specified to be  |  |

|                    |                 | Rise Time                                             | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                         | 300  | ns    | from 10 to 400 pF      |  |

|                    |                 |                                                       | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                                                                                                                   | 300  | ns    | 1                      |  |

| IM25               | TSU:DAT         | Data Input<br>Setup Time                              | 100 kHz mode              | 250                                                                                                                                                                                                                                                                                 | _    | ns    |                        |  |