Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                       |

| Number of I/O              | 58                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

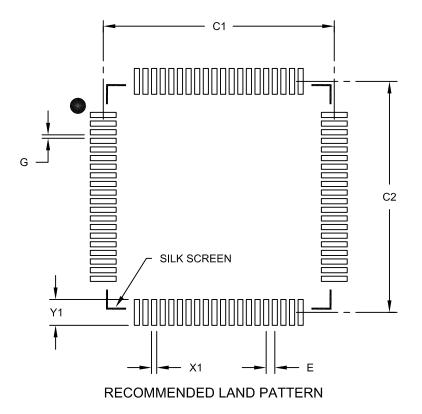

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs406t-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File<br>Name | SFR<br>Addr | Bit 15         | Bit 14                                                                                                               | Bit 13  | Bit 12  | Bit 11   | Bit 10  | Bit 9     | Bit 8  | Bit 7     | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------|---------|---------|----------|---------|-----------|--------|-----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON9      | 0520        | FLTSTAT        | CLSTAT                                                                                                               | TRGSTAT | FLTIEN  | CLIEN    | TRGIEN  | ITB       | MDCS   | DTC1      | DTC0    | DTCP     | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON9       | 0522        | PENH           | PENL                                                                                                                 | POLH    | POLL    | PMOD1    | PMOD0   | OVRENH    | OVRENL | OVRDAT1   | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON9      | 0524        | IFLTMOD        | CLSRC4                                                                                                               | CLSRC3  | CLSRC2  | CLSRC1   | CLSRC0  | CLPOL     | CLMOD  | FLTSRC4   | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC9         | 0526        |                | PDC9<15:0> 0                                                                                                         |         |         |          |         |           |        |           |         |          |          |          | 0000     |          |          |               |

| PHASE9       | 0528        | PHASE9<15:0>   |                                                                                                                      |         |         |          |         |           |        |           |         |          | 0000     |          |          |          |          |               |

| DTR9         | 052A        | — — DTR9<13:0> |                                                                                                                      |         |         |          |         |           |        |           |         |          | 0000     |          |          |          |          |               |

| ALTDTR9      | 052A        |                | ALTDTR9<13:0>                                                                                                        |         |         |          |         |           |        |           |         |          | 0000     |          |          |          |          |               |

| SDC9         | 052E        |                |                                                                                                                      |         |         |          |         |           | SDC    | <15:0>    |         |          |          |          |          |          |          | 0000          |

| SPHASE9      | 0530        |                |                                                                                                                      |         |         |          |         |           | SPHAS  | E9<15:0>  |         |          |          |          |          |          |          | 0000          |

| TRIG9        | 0532        |                |                                                                                                                      |         |         |          |         |           | TRGCM  | /IP<15:0> |         |          |          |          |          |          |          | 0000          |

| TRGCON9      | 0534        | TRGDIV3        | TRGDIV2                                                                                                              | TRGDIV1 | TRGDIV0 | -        | -       | Ι         | _      | DTM       |         | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG9       | 0536        |                |                                                                                                                      |         |         |          |         |           | STRGC  | MP<15:0>  |         |          |          |          |          |          |          | 0000          |

| PWMCAP9      | 0538        |                |                                                                                                                      |         |         |          |         | PWMCAP<12 | ::0>   |           |         |          |          |          | _        | _        | _        | 0000          |

| LEBCON9      | 053A        | PHR            | PHF                                                                                                                  | PLR     | PLF     | FLTLEBEN | CLLEBEN | Ι         | _      | -         |         | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY9      | 053C        | _              | _                                                                                                                    | _       | _       |          |         |           | L      | EB<8:0>   |         |          |          |          | —        | _        | _        | 0000          |

| AUXCON9      | 053E        | HRPDIS         | HRPDIS HRDDIS — — BLANKSEL3 BLANKSEL2 BLANKSEL1 BLANKSEL0 — — CHOPSEL3 CHOPSEL2 CHOPSEL1 CHOPSEL0 CHOPHEN CHOPLEN 00 |         |         |          |         |           |        |           |         | 0000     |          |          |          |          |          |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-32: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ32GS610 AND dsPIC33FJ64GS610 DEVICES ONLY (CONTINUED)

| File<br>Name | SFR<br>Addr | Bit 15             | Bit 14             | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------------------|--------------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ADCBUF22     | 036C        | ADC Data Buffer 22 |                    |        |        |        |        |       |       |       |       |       | xxxx  |       |       |       |       |               |

| ADCBUF23     | 036E        | ADC Data Buffer 23 |                    |        |        |        |        |       |       |       |       | XXXX  |       |       |       |       |       |               |

| ADCBUF24     | 0370        | ADC Data Buffer 24 |                    |        |        |        |        |       |       |       |       | XXXX  |       |       |       |       |       |               |

| ADCBUF25     | 0372        |                    | ADC Data Buffer 25 |        |        |        |        |       |       |       |       |       | xxxx  |       |       |       |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- Upper boundary addresses for incrementing buffers

- Lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

# 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWMx bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume<br>word-sized data (LSb of every EA is<br>always clear). The XB value is scaled<br>accordingly to generate compatible (byte) |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | addresses.                                                                                                                                                           |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed         |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | Addressing should not be enabled           |  |  |  |  |  |  |  |  |  |

|       | together. If an application attempts to do |  |  |  |  |  |  |  |  |  |

|       | so, Bit-Reversed Addressing will assume    |  |  |  |  |  |  |  |  |  |

|       | priority when active for the X WAGU and X  |  |  |  |  |  |  |  |  |  |

|       | WAGU, and Modulo Addressing will be        |  |  |  |  |  |  |  |  |  |

|       | disabled. However, Modulo Addressing will  |  |  |  |  |  |  |  |  |  |

|       | continue to function in the X RAGU.        |  |  |  |  |  |  |  |  |  |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

### 4.6 Interfacing Program and Data Memory Spaces

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices' architecture uses a 24-bit-wide program space and a 16-bit-wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJ32GS406/ 606/608/610 and dsPIC33FJ64GS406/606/608/610 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

### 4.6.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-68 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word and D<15:0> refers to a data space word.

|                          | Access        | Program Space Address        |           |                                   |                     |     |  |  |  |  |

|--------------------------|---------------|------------------------------|-----------|-----------------------------------|---------------------|-----|--|--|--|--|

| Access Type              | Space         | <23>                         | <22:16>   | <15>                              | <14:1>              | <0> |  |  |  |  |

| Instruction Access       | User          | 0 PC<22:1> 0                 |           |                                   |                     |     |  |  |  |  |

| (Code Execution)         |               | 0xx xxxx xxxx xxxx xxxx xxx0 |           |                                   |                     |     |  |  |  |  |

| TBLRD/TBLWT              | User          | TB                           | LPAG<7:0> | Data EA<15:0>                     |                     |     |  |  |  |  |

| (Byte/Word Read/Write)   |               | 0                            | xxx xxxx  | XXX                               | XXXX XXXX XXXX XXXX |     |  |  |  |  |

|                          | Configuration | TB                           | LPAG<7:0> | Data EA<15:0>                     |                     |     |  |  |  |  |

|                          |               | 1                            | xxx xxxx  | XXXX XXXX XXXX XXXX               |                     |     |  |  |  |  |

| Program Space Visibility | User          | 0                            | PSVPAG<7  | 7:0> Data EA<14:0> <sup>(1)</sup> |                     |     |  |  |  |  |

| (Block Remap/Read)       |               | 0                            | XXXX XXXX | 2                                 | xxx xxxx xxxx xxxx  |     |  |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

| U-0          | U-0                                                                   | U-0              | U-0              | U-0              | R/W-1            | R/W-0              | R/W-0    |  |  |  |  |

|--------------|-----------------------------------------------------------------------|------------------|------------------|------------------|------------------|--------------------|----------|--|--|--|--|

| _            |                                                                       | —                | —                | —                | MI2C2IP2         | MI2C2IP1           | MI2C2IP0 |  |  |  |  |

| bit 15       |                                                                       |                  |                  |                  |                  |                    | bit 8    |  |  |  |  |

|              |                                                                       |                  |                  |                  |                  |                    |          |  |  |  |  |

| U-0          | R/W-1                                                                 | R/W-0            | R/W-0            | U-0              | U-0              | U-0                | U-0      |  |  |  |  |

| —            | SI2C2IP2                                                              | SI2C2IP1         | SI2C2IP0         | —                | _                | —                  | —        |  |  |  |  |

| bit 7        |                                                                       |                  |                  |                  |                  |                    | bit 0    |  |  |  |  |

|              |                                                                       |                  |                  |                  |                  |                    |          |  |  |  |  |

| Legend:      |                                                                       |                  |                  |                  |                  |                    |          |  |  |  |  |

| R = Readab   | le bit                                                                | W = Writable     | bit              | U = Unimple      | mented bit, read | d as '0'           |          |  |  |  |  |

| -n = Value a | t POR                                                                 | '1' = Bit is set | t                | '0' = Bit is cle | eared            | x = Bit is unknown |          |  |  |  |  |

|              |                                                                       |                  |                  |                  |                  |                    |          |  |  |  |  |

| bit 15-11    | Unimplemen                                                            | ted: Read as '   | 0'               |                  |                  |                    |          |  |  |  |  |

| bit 10-8     | MI2C2IP<2:0                                                           | >: I2C2 Maste    | r Events Interr  | upt Priority bit | S                |                    |          |  |  |  |  |

|              | 111 = Interru                                                         | pt is Priority 7 | (highest priorit | y interrupt)     |                  |                    |          |  |  |  |  |

|              | •                                                                     |                  |                  |                  |                  |                    |          |  |  |  |  |

|              | •                                                                     |                  |                  |                  |                  |                    |          |  |  |  |  |

|              | 001 = Interru                                                         | pt is Priority 1 |                  |                  |                  |                    |          |  |  |  |  |

|              | -                                                                     | pt source is dis |                  |                  |                  |                    |          |  |  |  |  |

| bit 7        | Unimplemen                                                            | ted: Read as '   | 0'               |                  |                  |                    |          |  |  |  |  |

| bit 6-4      |                                                                       | I2C2 Slave       | -                |                  |                  |                    |          |  |  |  |  |

|              | <pre>111 = Interrupt is Priority 7 (highest priority interrupt)</pre> |                  |                  |                  |                  |                    |          |  |  |  |  |

|              |                                                                       |                  |                  |                  |                  |                    |          |  |  |  |  |

|              | •                                                                     |                  |                  |                  |                  |                    |          |  |  |  |  |

|              | 001 = Interru                                                         |                  |                  |                  |                  |                    |          |  |  |  |  |

|              | -                                                                     | pt source is dis |                  |                  |                  |                    |          |  |  |  |  |

| bit 3-0      | Unimplemen                                                            | ted: Read as '   | 0'               |                  |                  |                    |          |  |  |  |  |

|              |                                                                       |                  |                  |                  |                  |                    |          |  |  |  |  |

## REGISTER 7-31: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

| U-0                            | U-0                                                                                                                                                                                                                    | U-0                                                                         | U-0             | U-0                  | R/W-1            | R/W-0              | R/W-0   |  |  |  |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------|----------------------|------------------|--------------------|---------|--|--|--|--|

| —                              | —                                                                                                                                                                                                                      | —                                                                           | —               | —                    | QEI1IP2          | QEI1IP1            | QEI1IP0 |  |  |  |  |

| bit 15                         |                                                                                                                                                                                                                        |                                                                             |                 |                      |                  |                    | bit 8   |  |  |  |  |

|                                |                                                                                                                                                                                                                        |                                                                             |                 |                      |                  |                    |         |  |  |  |  |

| U-0                            | R/W-1                                                                                                                                                                                                                  | R/W-0                                                                       | R/W-0           | U-0                  | U-0              | U-0                | U-0     |  |  |  |  |

|                                | PSEMIP2                                                                                                                                                                                                                | PSEMIP1                                                                     | PSEMIP0         | —                    | —                |                    | _       |  |  |  |  |

| bit 7                          |                                                                                                                                                                                                                        |                                                                             |                 |                      |                  |                    | bit 0   |  |  |  |  |

|                                |                                                                                                                                                                                                                        |                                                                             |                 |                      |                  |                    |         |  |  |  |  |

| Legend:                        |                                                                                                                                                                                                                        |                                                                             |                 |                      |                  |                    |         |  |  |  |  |

| R = Readabl                    |                                                                                                                                                                                                                        | W = Writable                                                                |                 | •                    | mented bit, read | d as '0'           |         |  |  |  |  |

| -n = Value at                  | POR                                                                                                                                                                                                                    | '1' = Bit is set                                                            |                 | '0' = Bit is cleared |                  | x = Bit is unknown |         |  |  |  |  |

| bit 15-11<br>bit 10-8<br>bit 7 | Unimplemented: Read as '0'<br>QEI1IP<2:0>: QEI1 Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)<br>•<br>•<br>001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |                                                                             |                 |                      |                  |                    |         |  |  |  |  |

|                                | •                                                                                                                                                                                                                      | ted: Read as '                                                              |                 |                      |                  |                    |         |  |  |  |  |

| bit 6-4                        | 111 = Interrup<br>•<br>•<br>001 = Interrup                                                                                                                                                                             | >: PWM Specia<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis | highest priorit | •                    | onty dits        |                    |         |  |  |  |  |

| bit 3-0                        | Unimplemen                                                                                                                                                                                                             | ted: Read as '                                                              | 0'              |                      |                  |                    |         |  |  |  |  |

|                                |                                                                                                                                                                                                                        |                                                                             |                 |                      |                  |                    |         |  |  |  |  |

### REGISTER 7-33: IPC14: INTERRUPT PRIORITY CONTROL REGISTER 14

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

|                                                                      |                                                            |                  |                 |                  |                   | -                  |       |  |  |  |  |  |

|----------------------------------------------------------------------|------------------------------------------------------------|------------------|-----------------|------------------|-------------------|--------------------|-------|--|--|--|--|--|

| U-0                                                                  | R/W-1                                                      | R/W-0            | R/W-0           | U-0              | U-0               | U-0                | U-0   |  |  |  |  |  |

|                                                                      | QEI2IP2                                                    | QEI2IP1          | QEI2IP0         | —                | —                 |                    | —     |  |  |  |  |  |

| bit 15                                                               |                                                            |                  |                 |                  |                   |                    | bit 8 |  |  |  |  |  |

|                                                                      |                                                            |                  |                 |                  |                   |                    |       |  |  |  |  |  |

| U-0                                                                  | R/W-1                                                      | R/W-0            | R/W-0           | U-0              | U-0               | U-0                | U-0   |  |  |  |  |  |

| —                                                                    | PSESMIP2                                                   | PSESMIP1         | PSESMIP0        | —                | —                 | —                  |       |  |  |  |  |  |

| bit 7                                                                |                                                            |                  |                 |                  |                   |                    | bit 0 |  |  |  |  |  |

|                                                                      |                                                            |                  |                 |                  |                   |                    |       |  |  |  |  |  |

| Legend:                                                              |                                                            |                  |                 |                  |                   |                    |       |  |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                            |                  |                 |                  |                   |                    |       |  |  |  |  |  |

| -n = Value at                                                        | t POR                                                      | '1' = Bit is set | :               | '0' = Bit is cle | ared              | x = Bit is unknown |       |  |  |  |  |  |

|                                                                      |                                                            |                  |                 |                  |                   |                    |       |  |  |  |  |  |

| bit 15                                                               | Unimplemented: Read as '0'                                 |                  |                 |                  |                   |                    |       |  |  |  |  |  |

| bit 14-12                                                            | QEI2IP<2:0>                                                | QEI2 Interrup    | t Priority bits |                  |                   |                    |       |  |  |  |  |  |

|                                                                      | 111 = Interrupt is Priority 7 (highest priority interrupt) |                  |                 |                  |                   |                    |       |  |  |  |  |  |

|                                                                      | •                                                          |                  |                 |                  |                   |                    |       |  |  |  |  |  |

|                                                                      |                                                            |                  |                 |                  |                   |                    |       |  |  |  |  |  |

|                                                                      | 001 = Interrupt is Priority 1                              |                  |                 |                  |                   |                    |       |  |  |  |  |  |

|                                                                      | 000 = Interrupt source is disabled                         |                  |                 |                  |                   |                    |       |  |  |  |  |  |

| bit 11-7                                                             | Unimplemen                                                 | ted: Read as '   | 0'              |                  |                   |                    |       |  |  |  |  |  |

| bit 6-4                                                              | PSESMIP<2:                                                 | 0>: PWM Spec     | cial Event Sec  | ondary Match     | Interrupt Priorit | ty bits            |       |  |  |  |  |  |

|                                                                      | 111 = Interrupt is Priority 7 (highest priority interrupt) |                  |                 |                  |                   |                    |       |  |  |  |  |  |

|                                                                      | •                                                          |                  |                 |                  |                   |                    |       |  |  |  |  |  |

|                                                                      |                                                            |                  |                 |                  |                   |                    |       |  |  |  |  |  |

|                                                                      | 001 = Interru                                              | ot is Priority 1 |                 |                  |                   |                    |       |  |  |  |  |  |

|                                                                      | 000 = Interru                                              | pt source is dis | abled           |                  |                   |                    |       |  |  |  |  |  |

| bit 3-0                                                              | Unimplemen                                                 | ted: Read as '   | 0'              |                  |                   |                    |       |  |  |  |  |  |

|                                                                      |                                                            |                  |                 |                  |                   |                    |       |  |  |  |  |  |

#### REGISTER 7-36: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| U-0    | U-0 | U-0 | HS/HC-0 | R/W-0 | R/W-0               | R/W-0   | R/W-0   |

|--------|-----|-----|---------|-------|---------------------|---------|---------|

| —      | —   | —   | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL | SYNCOEN |

| bit 15 |     |     |         |       |                     |         | bit 8   |

| R/W-0  | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|----------|----------|----------|---------|---------|---------|---------|

| SYNCEN | SYNCSRC2 | SYNCSRC1 | SYNCSRC0 | SEVTPS3 | SEVTPS2 | SEVTPS1 | SEVTPS0 |

| bit 7  |          |          |          |         |         |         | bit 0   |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit  |                    |

|-------------------|-----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12    | SESTAT: Special Event Interrupt Status bit                                                                                                                       |

|           | 1 = Secondary special event interrupt is pending                                                                                                                 |

|           | 0 = Secondary special event interrupt is not pending                                                                                                             |

| bit 11    | SEIEN: Special Event Interrupt Enable bit                                                                                                                        |

|           | <ul><li>1 = Secondary special event interrupt is enabled</li><li>0 = Secondary special event interrupt is disabled</li></ul>                                     |

| bit 10    | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                         |

|           | <ul><li>1 = Active Secondary Period register is updated immediately</li><li>0 = Active Secondary Period register updates occur on PWM cycle boundaries</li></ul> |

| bit 9     | SYNCPOL: Synchronize Input and Output Polarity bit                                                                                                               |

|           | 1 = SYNCIx/SYNCO2 polarity is inverted (active-low)                                                                                                              |

|           | 0 = SYNCIx/SYNCO2 polarity is active-high                                                                                                                        |

| bit 8     | SYNCOEN: Secondary Master Time Base Synchronization Enable bit                                                                                                   |

|           | <ul><li>1 = SYNCO2 output is enabled.</li><li>0 = SYNCO2 output is disabled</li></ul>                                                                            |

| bit 7     | SYNCEN: External Secondary Master Time Base Synchronization Enable bit                                                                                           |

|           | <ul> <li>1 = External synchronization of secondary time base is enabled</li> <li>0 = External synchronization of secondary time base is disabled</li> </ul>      |

| bit 6-4   | SYNCSRC<2:0>: PWM Secondary Time Base Synchronization Source Selection bits                                                                                      |

|           | 111 = Reserved                                                                                                                                                   |

|           | 101 = Reserved                                                                                                                                                   |

|           | 100 = Reserved<br>011 = SYNCI4                                                                                                                                   |

|           | 010 = SYNCI3                                                                                                                                                     |

|           | 001 = SYNCI2                                                                                                                                                     |

|           | 000 = SYNCI1                                                                                                                                                     |

| bit 3-0   | SEVTPS<3:0>: PWM Secondary Special Event Trigger Output Postscaler Select bits                                                                                   |

|           | 1111 = 1:16 Postcale                                                                                                                                             |

|           | 0001 = 1:2 Postcale                                                                                                                                              |

|           | •                                                                                                                                                                |

|           |                                                                                                                                                                  |

|           | •<br>0000 = 1:1 Postscale                                                                                                                                        |

|           | 0000 = 1.1  FUSISCALE                                                                                                                                            |

Note 1: This bit only applies to the secondary master time base period.

<sup>© 2009-2014</sup> Microchip Technology Inc.

### REGISTER 16-16: DTRx: PWM DEAD-TIME x REGISTER

| U-0    | U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|--------|-------|-------|

| —      | —     |       |       | DTR×  | <13:8> |       |       |

| bit 15 |       |       |       |       |        |       | bit 8 |

|        |       |       |       |       |        |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|        |       |       | DTRx  | <7:0> |        |       |       |

| bit 7  |       |       |       |       |        |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Value for PWMx Dead-Time Unit bits

### REGISTER 16-17: ALTDTRx: PWM ALTERNATE DEAD-TIME x REGISTER

| U-0                                | U-0   | R/W-0 | R/W-0             | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-------|-------------------|------------------------------------|-----------------|-------|-------|--|

| —                                  | —     |       | ALTDTRx<13:8>     |                                    |                 |       |       |  |

| bit 15                             |       |       |                   |                                    |                 |       | bit 8 |  |

|                                    |       |       |                   |                                    |                 |       |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0             | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |  |

|                                    |       |       | ALTD              | Rx<7:0>                            |                 |       |       |  |

| bit 7                              |       |       |                   |                                    |                 |       | bit 0 |  |

|                                    |       |       |                   |                                    |                 |       |       |  |

| Legend:                            |       |       |                   |                                    |                 |       |       |  |

| R = Readable bit W = Writable bit  |       |       | bit               | U = Unimplemented bit, read as '0' |                 |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is clea | ared                               | x = Bit is unkr | nown  |       |  |

|                                    |       |       |                   |                                    |                 |       |       |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Value for PWMx Dead-Time Unit bits

## REGISTER 16-23: LEBCONX: LEADING-EDGE BLANKING CONTROL x REGISTER (CONTINUED)

| bit 1 | BPLH: Blanking in PWMxL High Enable bit                                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> </ul> |

| bit 0 | BPLL: Blanking in PWMxL Low Enable bit                                                                                                                            |

|       | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is low</li> </ul>   |

**Note 1:** The blanking signal is selected via the BLANKSELx bits in the AUXCONx register.

### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UxRX Idle state is '0'                                                                                                                                                         |

|         | 0 = UxRX Idle state is '1'                                                                                                                                                         |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | 11 = 9-bit data, no parity                                                                                                                                                         |

|         | 10 = 8-bit data, odd parity                                                                                                                                                        |

|         | 01 = 8-bit data, even parity                                                                                                                                                       |

|         | 00 = 8-bit data, no parity                                                                                                                                                         |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                      |

|         | 1 = Two Stop bits                                                                                                                                                                  |

|         | 0 = One Stop bit                                                                                                                                                                   |

| Note 1: | Refer to "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual" for information or                                                                                        |

- enabling the UART module for receive or transmit operation. That section of the manual is available on the Microchip web site: www.microchip.com.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| R/W-0                   | R/W-0                                                                                                                                                                                                                   | R/W-0                                                                                                      | U-0                 | U-0                 | U-0                 | U-0                 | U-0                 |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--|--|

| DMABS2                  | DMABS1                                                                                                                                                                                                                  | DMABS0                                                                                                     | —                   | —                   | _                   | —                   | —                   |  |  |

| bit 15                  |                                                                                                                                                                                                                         |                                                                                                            |                     |                     |                     |                     | bit 8               |  |  |

|                         |                                                                                                                                                                                                                         |                                                                                                            |                     |                     |                     |                     |                     |  |  |

| U-0                     | U-0                                                                                                                                                                                                                     | U-0                                                                                                        | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               |  |  |

| —                       | <u> </u>                                                                                                                                                                                                                | <u> </u>                                                                                                   | FSA4 <sup>(1)</sup> | FSA3 <sup>(1)</sup> | FSA2 <sup>(1)</sup> | FSA1 <sup>(1)</sup> | FSA0 <sup>(1)</sup> |  |  |

| bit 7                   |                                                                                                                                                                                                                         |                                                                                                            |                     |                     |                     |                     | bit C               |  |  |

| Lonondi                 |                                                                                                                                                                                                                         |                                                                                                            |                     |                     |                     |                     |                     |  |  |

| Legend:<br>R = Readable | bit                                                                                                                                                                                                                     | W = Writable                                                                                               | bit                 | U = Unimpler        | mented bit, read    | d as '0'            |                     |  |  |

| -n = Value at I         | POR                                                                                                                                                                                                                     | '1' = Bit is set                                                                                           |                     | '0' = Bit is cle    | ared                | x = Bit is unknown  |                     |  |  |

| bit 12-5                | <pre>111 = Reserved<br/>110 = 32 buffers in DMA RAM<br/>101 = 24 buffers in DMA RAM<br/>100 = 16 buffers in DMA RAM<br/>011 = 12 buffers in DMA RAM<br/>010 = 8 buffers in DMA RAM<br/>001 = 6 buffers in DMA RAM</pre> |                                                                                                            |                     |                     |                     |                     |                     |  |  |

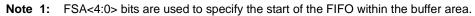

| bit 4-0                 | FSA<4:0>: F<br>11111 = Rea<br>11110 = Rea<br>00001 = TX/f                                                                                                                                                               | ted: Read as '(<br>IFO Area Starts<br>ds Buffer RB31<br>ds Buffer RB30<br>RX Buffer TRB1<br>RX Buffer TRB1 | with Buffer b       | <sub>its</sub> (1)  |                     |                     |                     |  |  |

# REGISTER 21-4: CxFCTRL: ECANx FIFO CONTROL REGISTER

### REGISTER 22-11: ADCPC5: ADC CONVERT PAIR CONTROL REGISTER 5 (CONTINUED)

| bit 12-8 | <b>TRGSRC11&lt;4:0&gt;:</b> Trigger 11 Source Selection bits Selects trigger source for conversion of analog channels AN23 and AN22. |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|

|          | 11111 = Timer2 period match                                                                                                          |

|          | 11110 = PWM Generator 8 current-limit ADC trigger                                                                                    |

|          | 11101 = PWM Generator 7 current-limit ADC trigger                                                                                    |

|          | 11100 = PWM Generator 6 current-limit ADC trigger                                                                                    |

|          | 11011 = PWM Generator 5 current-limit ADC trigger                                                                                    |

|          | 11010 = PWM Generator 4 current-limit ADC trigger                                                                                    |

|          | 11001 = PWM Generator 3 current-limit ADC trigger                                                                                    |

|          | 11000 = PWM Generator 2 current-limit ADC trigger                                                                                    |

|          | 10111 = PWM Generator 1 current-limit ADC trigger                                                                                    |

|          | 10110 = PWM Generator 9 secondary trigger selected                                                                                   |

|          | 10101 = PWM Generator 8 secondary trigger selected                                                                                   |

|          | 10100 = PWM Generator 7 secondary trigger selected                                                                                   |

|          | 10011 = PWM Generator 6 secondary trigger selected                                                                                   |

|          | 10010 = PWM Generator 5 secondary trigger selected                                                                                   |

|          | 10001 = PWM Generator 4 secondary trigger selected                                                                                   |

|          | 10000 = PWM Generator 3 secondary trigger selected<br>01111 = PWM Generator 2 secondary trigger selected                             |

|          | 01110 = PWM Generator 1 secondary trigger selected                                                                                   |

|          | 01101 = PWM secondary Special Event Trigger selected                                                                                 |

|          | 01100 = Timer1 period match                                                                                                          |

|          | 01011 = PWM Generator 8 primary trigger selected                                                                                     |

|          | 01010 = PWM Generator 7 primary trigger selected                                                                                     |

|          | 01001 = PWM Generator 6 primary trigger selected                                                                                     |

|          | 01000 = PWM Generator 5 primary trigger selected                                                                                     |

|          | 00111 = PWM Generator 4 primary trigger selected                                                                                     |

|          | 00110 = PWM Generator 3 primary trigger selected                                                                                     |

|          | 00101 = PWM Generator 2 primary trigger selected                                                                                     |

|          | 00100 = PWM Generator 1 primary trigger selected                                                                                     |

|          | 00011 = PWM Special Event Trigger selected                                                                                           |

|          | 00010 = Global software trigger selected                                                                                             |

|          | 00001 = Individual software trigger selected                                                                                         |

|          | 00000 = No conversion is enabled                                                                                                     |

| bit 7    | IRQEN10: Interrupt Request Enable 10 bit                                                                                             |

|          | 1 = Enables IRQ generation when requested conversion of Channels AN21 and AN20 is completed                                          |

|          | 0 = IRQ is not generated                                                                                                             |

| bit 6    | PEND10: Pending Conversion Status 10 bit                                                                                             |

|          | 1 = Conversion of Channels AN21 and AN20 is pending; set when selected trigger is asserted                                           |

|          | 0 = Conversion is complete                                                                                                           |

| bit 5    |                                                                                                                                      |

| DIL J    | SWTRG10: Software Trigger 10 bit                                                                                                     |

|          | 1 = Starts conversion of AN21 and AN20 (if selected by the TRGSRCx<4:0> bits) <sup>(1)</sup>                                         |

|          | This bit is automatically cleared by hardware when the PEND10 bit is set.<br>0 = Conversion has not started                          |

|          |                                                                                                                                      |

**Note 1:** The trigger source must be set as an individual software trigger prior to setting this bit to '1'. If other conversions are in progress, the conversion is performed when the conversion resources are available.

# REGISTER 22-12: ADCPC6: ADC CONVERT PAIR CONTROL REGISTER 6<sup>(2)</sup> (CONTINUED)

- bit 4-0 TRGSRC12<4:0>: Trigger 12 Source Selection bits Selects trigger source for conversion of analog channels AN25 and AN24. 11111 = Timer2 period match 11110 = PWM Generator 8 current-limit ADC trigger 11101 = PWM Generator 7 current-limit ADC trigger 11100 = PWM Generator 6 current-limit ADC trigger 11011 = PWM Generator 5 current-limit ADC trigger 11010 = PWM Generator 4 current-limit ADC trigger 11001 = PWM Generator 3 current-limit ADC trigger 11000 = PWM Generator 2 current-limit ADC trigger 10111 = PWM Generator 1 current-limit ADC trigger 10110 = PWM Generator 9 secondary trigger selected 10101 = PWM Generator 8 secondary trigger selected 10100 = PWM Generator 7 secondary trigger selected 10011 = PWM Generator 6 secondary trigger selected 10010 = PWM Generator 5 secondary trigger selected 10001 = PWM Generator 4 secondary trigger selected 10000 = PWM Generator 3 secondary trigger selected 01111 = PWM Generator 2 secondary trigger selected 01110 = PWM Generator 1 secondary trigger selected 01101 = PWM secondary Special Event Trigger selected 01100 = Timer1 period match 01011 = PWM Generator 8 primary trigger selected 01010 = PWM Generator 7 primary trigger selected 01001 = PWM Generator 6 primary trigger selected 01000 = PWM Generator 5 primary trigger selected 00111 = PWM Generator 4 primary trigger selected 00110 = PWM Generator 3 primary trigger selected 00101 = PWM Generator 2 primary trigger selected 00100 = PWM Generator 1 primary trigger selected 00011 = PWM Special Event Trigger selected 00010 = Global software trigger selected 00001 = Individual software trigger selected 00000 = No conversion is enabled

- **Note 1:** The trigger source must be set as an individual software trigger prior to setting this bit to '1'. If other conversions are in progress, the conversion is performed when the conversion resources are available.

- 2: This register is not available on dsPIC33FJ32GS406 and dsPIC33FJ64GS406 devices.

### 23.3 Module Applications

This module provides a means for the SMPS dsPIC<sup>®</sup> DSC devices to monitor voltage and currents in a power conversion application. The ability to detect transient conditions and stimulate the dsPIC DSC processor and/or peripherals, without requiring the processor and ADC to constantly monitor voltages or currents, frees the dsPIC DSC to perform other tasks.

The comparator module has a high-speed comparator and an associated 10-bit DAC that provides a programmable reference voltage to the inverting input of the comparator. The polarity of the comparator output is user-programmable. The output of the module can be used in the following modes:

- Generate an Interrupt

- Trigger an ADC Sample-and-Convert Process

- Truncate the PWM Signal (current limit)

- Truncate the PWM Period (current minimum)

- Disable the PWM Outputs (Fault latch)

The output of the comparator module may be used in multiple modes at the same time, such as: 1) generate an interrupt, 2) have the ADC take a sample and convert it, and 3) truncate the PWM output in response to a voltage being detected beyond its expected value.

The comparator module can also be used to wake-up the system from Sleep or Idle mode when the analog input voltage exceeds the programmed threshold voltage.

# 23.4 DAC

The range of the DAC is controlled via an analog multiplexer that selects either AVDD/2, an internal reference source, INTREF, or an external reference source, EXTREF. The full range of the DAC (AVDD/2) will typically be used when the chosen input source pin is shared with the ADC. The reduced range option (INTREF) will likely be used when monitoring current levels using a current sense resistor. Usually, the measured voltages in such applications are small (<1.25V); therefore the option of using a reduced reference range for the comparator extends the available DAC resolution in these applications. The use of an external reference enables the user to connect to a reference that better suits their application.

DACOUT, shown in Figure 23-1, can only be associated with a single comparator at a given time.

Note: It should be ensured in software that multiple DACOE bits are not set. The output on the DACOUT pin will be indeterminate if multiple comparators enable the DAC output.

### 23.5 Interaction with I/O Buffers

If the comparator module is enabled and a pin has been selected as the source for the comparator, then the chosen I/O pad must disable the digital input buffer associated with the pad to prevent excessive currents in the digital buffer due to analog input voltages.

### 23.6 Digital Logic

The CMPCONx register (see Register 23-1) provides the control logic that configures the comparator module. The digital logic provides a glitch filter for the comparator output to mask transient signals in less than two instruction cycles. In Sleep or Idle mode, the glitch filter is bypassed to enable an asynchronous path from the comparator to the interrupt controller. This asynchronous path can be used to wake-up the processor from Sleep or Idle mode.

The comparator can be disabled while in Idle mode if the CMPSIDL bit is set. If a device has multiple comparators, if any CMPSIDL bit is set, then the entire group of comparators will be disabled while in Idle mode. This behavior reduces complexity in the design of the clock control logic for this module.

The digital logic also provides a one TCY width pulse generator for triggering the ADC and generating interrupt requests.

The CMPDACx (see Register 23-2) register provides the digital input value to the reference DAC.

If the module is disabled, the DAC and comparator are disabled to reduce power consumption.

### 23.7 Comparator Input Range

The comparator has a limitation for the input Common-Mode Range (CMR) of (AVDD - 1.5V), typical. This means that both inputs should not exceed this range. As long as one of the inputs is within the Common-Mode Range, the comparator output will be correct. However, any input exceeding the CMR limitation will cause the comparator input to be saturated.

If both inputs exceed the CMR, the comparator output will be indeterminate.

### 23.8 DAC Output Range

The DAC has a limitation for the maximum reference voltage input of (AVDD - 1.6) volts. An external reference voltage input should not exceed this value or the reference DAC output will become indeterminate.

# 23.9 Comparator Registers

The comparator module is controlled by the following registers:

- CMPCONx: Comparator Control x Register

- CMPDACx: Comparator DAC Control x Register

### 24.8 Code Protection and CodeGuard™ Security

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices offer the intermediate implementation of CodeGuard<sup>™</sup> Security. CodeGuard Security enables multiple parties to securely share resources (memory, interrupts and peripherals) on a single chip. This feature helps protect individual Intellectual Property in collaborative system designs.

When coupled with software encryption libraries, CodeGuard Security can be used to securely update Flash even when multiple IPs reside on a single chip. The code protection features are controlled by the Configuration registers: FBS and FGS.

Secure segment and RAM protection is not implemented in dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices.

| Note: |         |       | "CodeGuard™         |             |

|-------|---------|-------|---------------------|-------------|

|       | (DS701  | 99)   | in the "dsPIC33/PI  | C24 Family  |

|       | Referei | nce I | Manual" for further | information |

|       | on usa  | ge, c | configuration and c | peration of |

|       | CodeG   | uard  | Security.           |             |

| TABLE 24-3: CODE FLASH SECURITY SEGMENT SIZES FOR 64-KBYTE DEVICE | S |

|-------------------------------------------------------------------|---|

|-------------------------------------------------------------------|---|

| BSS<2:0> = x11, 0K                       | BSS<2:0> = x10, 1K                                                                                                                | BSS<2:0> = x01, 4K                                                                                   | BSS<2:0> = x00, 8K                                                                                   |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| VS = 256 IW 00000h<br>0001FEh<br>000200h | VS = 256 IW         000000h           0001FEh         000200h           000200h         0007FEh           000800h         000800h | VS = 256 IW         000000h           BS = 3840 IW         000200h           001FFEh         002000h | VS = 256 IW         000000h<br>0001FEh<br>000200h           BS = 7936 IW         0003FFEh<br>004000h |

| GS = 21760 IW<br>00ABFEh                 | GS = 20992 IW<br>00ABFEh                                                                                                          | GS = 17920 IW<br>00ABFEh                                                                             | GS = 13824 IW<br>00ABFEh                                                                             |

### TABLE 24-4: CODE FLASH SECURITY SEGMENT SIZES FOR 32-KBYTE DEVICES