Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                       |

| Number of I/O              | 58                                                                               |

| Program Memory Size        | 32КВ (32К х 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

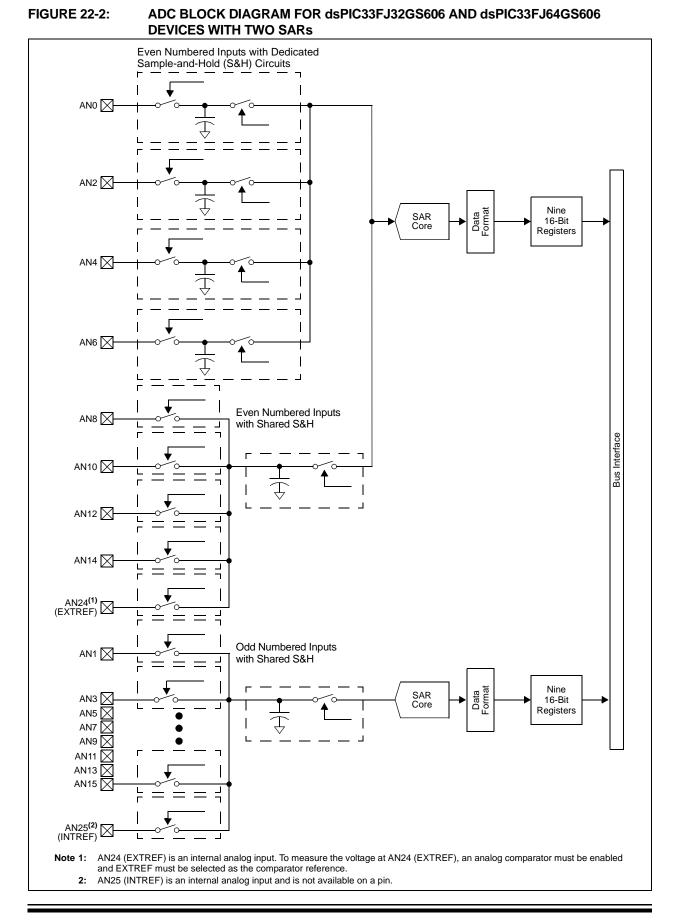

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs406t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ64GS606 DEVICES (CONTINUED)

| File    | SFR  |        |          |          |          |        |          |          |          |       |           |           |           |         |          |          |          | All    |

|---------|------|--------|----------|----------|----------|--------|----------|----------|----------|-------|-----------|-----------|-----------|---------|----------|----------|----------|--------|

| Name    | Addr | Bit 15 | Bit 14   | Bit 13   | Bit 12   | Bit 11 | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6     | Bit 5     | Bit 4     | Bit 3   | Bit 2    | Bit 1    | Bit 0    | Resets |

| IPC21   | 00CE | _      | —        | —        | —        | _      | _        |          | —        |       | ADCP12IP2 | ADCP12IP1 | ADCP12IP0 | _       | —        |          | —        | 0040   |

| IPC23   | 00D2 | —      | PWM2IP2  | PWM2IP1  | PWM2IP0  |        | PWM1IP2  | PWM1IP1  | PWM1IP0  |       | —         | -         | -         | —       | —        | -        | —        | 4400   |

| IPC24   | 00D4 | _      | PWM6IP2  | PWM6IP1  | PWM6IP0  |        | PWM5IP2  | PWM5IP1  | PWM5IP0  | _     | PWM4IP2   | PWM4IP1   | PWM4IP0   | _       | PWM3IP2  | PWM3IP1  | PWM3IP0  | 4444   |

| IPC25   | 00D6 | _      | AC2IP2   | AC2IP1   | AC2IP0   |        | PWM9IP2  | PWM9IP1  | PWM9IP0  | _     | PWM8IP2   | PWM8IP1   | PWM8IP0   | _       | PWM7IP2  | PWM7IP1  | PWM7IP0  | 4000   |

| IPC26   | 00D8 | _      | _        | _        | _        |        | _        | _        | _        | _     | AC4IP2    | AC4IP1    | AC4IP0    | _       | AC3IP2   | AC3IP1   | AC3IP0   | 0044   |

| IPC27   | 00DA | _      | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 |        | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | _     | _         | _         | _         | _       | _        | _        | _        | 4400   |

| IPC28   | 00DC | _      | ADCP5IP2 | ADCP5IP1 | ADCP5IP0 |        | ADCP4IP2 | ADCP4IP1 | ADCP4IP0 | _     | ADCP3IP2  | ADCP3IP1  | ADCP3IP0  | _       | ADCP2IP2 | ADCP2IP1 | ADCP2IP0 | 4444   |

| IPC29   | 00DE | _      | _        | _        | _        |        | _        | _        | _        | _     | ADCP7IP2  | ADCP7IP1  | ADCP7IP0  | _       | ADCP6IP2 | ADCP6IP1 | ADCP6IP0 | 0004   |

| INTTREG | 00E0 | _      | _        | _        | _        | ILR3   | ILR2     | ILR1     | ILR0     | _     | VECNUM6   | VECNUM5   | VECNUM4   | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000   |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ32GS406 AND dsPIC33FJ64GS406 DEVICES (CONTINUED) |  |

|------------------------------------------------------------------------------------------------------------|--|

|------------------------------------------------------------------------------------------------------------|--|

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14   | Bit 13   | Bit 12   | Bit 11 | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|--------|----------|----------|----------|--------|----------|----------|----------|-------|----------|----------|----------|---------|----------|----------|----------|---------------|

| IPC24        | 00D4        |        | PWM6IP2  | PWM6IP1  | PWM6IP0  | _      | PWM5IP2  | PWM5IP1  | PWM5IP0  | _     | PWM4IP2  | PWM4IP1  | PWM4IP0  | _       | PWM3IP2  | PWM3IP1  | PWM3IP0  | 4444          |

| IPC27        | 00DA        | _      | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | -      | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | _     | _        | _        | _        | _       | _        | _        | _        | 4400          |

| IPC28        | 00DC        | _      | ADCP5IP2 | ADCP5IP1 | ADCP5IP0 | _      | ADCP4IP2 | ADCP4IP1 | ADCP4IP0 | _     | ADCP3IP2 | ADCP3IP1 | ADCP3IP0 |         | ADCP2IP2 | ADCP2IP1 | ADCP2IP0 | 4444          |

| IPC29        | 00DE        | _      | _        | _        | —        | _      | _        |          |          | _     | ADCP7IP2 | ADCP7IP1 | ADCP7IP0 |         | ADCP6IP2 | ADCP6IP1 | ADCP6IP0 | 0004          |

| INTTREG      | 00E0        | _      | _        | _        | _        | ILR3   | ILR2     | ILR1     | ILR0     | _     | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

## TABLE 4-13: OUTPUT COMPARE REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7      | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|------------|-------------|------------|--------|-------|-------|--------|-------|-------|-------|---------------|

| OC1RS        | 0180        |        |        |        |        |        |        | Output Cor | npare 1 Sec | ondary Re  | gister |       |       |        |       |       |       | xxxx          |

| OC1R         | 0182        |        |        |        |        |        |        | Outp       | ut Compare  | 1 Register |        |       |       |        |       |       |       | xxxx          |

| OC1CON       | 0184        |        | _      | OCSIDL | _      | _      | _      | _          | _           | _          | _      | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC2RS        | 0186        |        |        |        |        |        |        | Output Cor | npare 2 Sec | ondary Re  | gister |       |       |        |       |       |       | xxxx          |

| OC2R         | 0188        |        |        |        |        |        |        | Outp       | ut Compare  | 2 Register |        |       |       |        |       |       |       | xxxx          |

| OC2CON       | 018A        |        | _      | OCSIDL | _      | _      | _      | _          | _           | _          | _      | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC3RS        | 018C        |        |        |        |        |        |        | Output Cor | npare 3 Sec | ondary Re  | gister |       |       |        |       |       |       | xxxx          |

| OC3R         | 018E        |        |        |        |        |        |        | Outp       | ut Compare  | 3 Register |        |       |       |        |       |       |       | xxxx          |

| OC3CON       | 0190        |        | _      | OCSIDL | _      | _      | _      | _          | _           | _          | _      | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC4RS        | 0192        |        |        |        |        |        |        | Output Cor | npare 4 Sec | ondary Re  | gister |       |       |        |       |       |       | xxxx          |

| OC4R         | 0194        |        |        |        |        |        |        | Outp       | ut Compare  | 4 Register |        |       |       |        |       |       |       | xxxx          |

| OC4CON       | 0196        | _      | _      | OCSIDL | _      | —      | _      | —          | —           | _          | _      | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

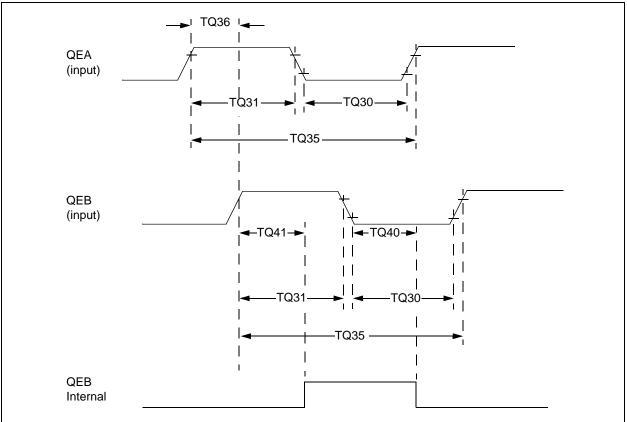

# TABLE 4-14: QEI1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7       | Bit 6    | Bit 5  | Bit 4   | Bit 3   | Bit 2  | Bit 1 | Bit 0    | All<br>Resets |

|--------------|-------------|--------|--------|---------|--------|--------|--------|-------|-------|-------------|----------|--------|---------|---------|--------|-------|----------|---------------|

| QEI1CON      | 01E0        | CNTERR | _      | QEISIDL | INDX   | UPDN   | QEIM2  | QEIM1 | QEIM0 | SWPAB       | PCDOUT   | TQGATE | TQCKPS1 | TQCKPS0 | POSRES | TQCS  | UPDN_SRC | 0000          |

| DFLT1CON     | 01E2        | _      | _      | _       | _      | _      | IMV1   | IMV0  | CEID  | QEOUT       | QECK2    | QECK1  | QECK0   | _       | _      | —     | _        | 0000          |

| POS1CNT      | 01E4        |        |        |         |        |        |        |       | Pos   | ition Count | er<15:0> |        |         |         |        |       |          | 0000          |

| MAX1CNT      | 01E6        |        |        |         |        |        |        |       | Мах   | imum Cour   | nt<15:0> |        |         |         |        |       |          | FFFF          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-15: QEI2 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7       | Bit 6    | Bit 5  | Bit 4   | Bit 3   | Bit 2  | Bit 1 | Bit 0    | All<br>Resets |

|--------------|-------------|--------|--------|---------|--------|--------|--------|-------|-------|-------------|----------|--------|---------|---------|--------|-------|----------|---------------|

| QEI2CON      | 01F0        | CNTERR | _      | QEISIDL | INDX   | UPDN   | QEIM2  | QEIM1 | QEIM0 | SWPAB       | PCDOUT   | TQGATE | TQCKPS1 | TQCKPS0 | POSRES | TQCS  | UPDN_SRC | 0000          |

| DFLT2CON     | 01F2        | -      | -      | -       | _      |        | IMV1   | IMV0  | CEID  | QEOUT       | QECK2    | QECK1  | QECK0   | -       | -      | _     | _        | 0000          |

| POS2CNT      | 01F4        |        |        |         |        |        |        |       | Pos   | ition Count | er<15:0> |        |         |         |        |       |          | 0000          |

| MAX2CNT      | 01F6        |        |        |         |        |        |        |       | Мах   | imum Cou    | nt<15:0> |        |         |         |        |       |          | FFFF          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 5.2 RTSP Operation

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 27-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the Table Write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

# 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

The programming time depends on the FRC accuracy (see Table 27-20) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time and Word Write Cycle Time parameters (see Table 27-12).

## EQUATION 5-1: PROGRAMMING TIME

$\frac{T}{7.37 \text{ MHz} \times (FRC \text{ Accuracy})\% \times (FRC \text{ Tuning})\%}$

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 2\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `b000000, the minimum row write time is equal to Equation 5-2.

# EQUATION 5-2: MINIMUM ROW WRITE TIME

| $T_{RW} = \cdot$ | 11064 Cycles                                        | = 1.473 ms |

|------------------|-----------------------------------------------------|------------|

| IKW = 2          | $7.37  MHz \times (1 + 0.02) \times (1 - 0.000938)$ | -1.4/3 ms  |

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM ROW WRITE TIME

| $T_{RW} =$ | <u>— 11064 Cycles</u> = $1.533$ ms                                            |

|------------|-------------------------------------------------------------------------------|

| INW -      | $7.37 \text{ MHz} \times (1 - 0.02) \times (1 - 0.000938) = 1.555 \text{ ms}$ |

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

# 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

## 6.2 Power-on Reset (POR)

A Power-on Reset (POR) circuit ensures the device is reset from power-on. The POR circuit is active until VDD crosses the VPOR threshold and the delay, TPOR, has elapsed. The delay, TPOR, ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 27.0 "Electrical Characteristics" for details.

The Power-on Reset (POR) status bit in the Reset Control (RCON<0>) register is set to indicate the Power-on Reset.

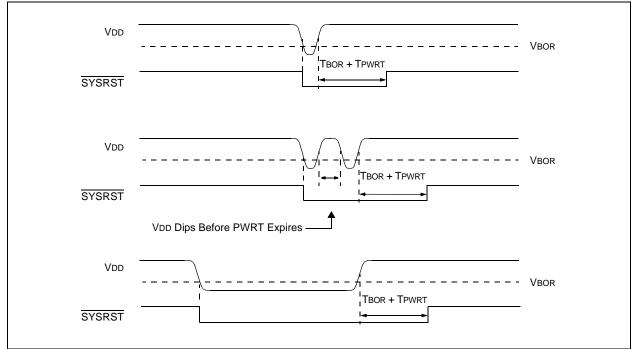

## 6.3 Brown-out Reset (BOR) and Power-up Timer (PWRT)

The on-chip regulator has a Brown-out Reset (BOR) circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses the

VBOR threshold and the delay, TBOR, has elapsed. The delay, TBOR, ensures the voltage regulator output becomes stable.

The Brown-out Reset (BOR) status bit in the Reset Control (RCON<1>) register is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides a Power-up Time Delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The Power-up Timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select (FPWRT<2:0>) bits in the FPOR Configuration (FPOR<2:0>) register, which provides eight settings (from 0 ms to 128 ms). Refer to **Section 24.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The Reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point

#### FIGURE 6-3: BROWN-OUT SITUATIONS

| TABLE 7-1:       | INTERRUP                   | T VECTORS (CO         | NTINUED)              | 1                                  |

|------------------|----------------------------|-----------------------|-----------------------|------------------------------------|

| Vector<br>Number | Interrupt<br>Request (IQR) | IVT Address           | AIVT Address          | Interrupt Source                   |

| 63-64            | 55-56                      | 0x000082-             | 0x000182-             | Reserved                           |

|                  |                            | 0x000084              | 0x000184              |                                    |

| 65               | 57                         | 0x000086              | 0x000186              | PWM PSEM Special Event Match       |

| 66               | 58                         | 0x000088              | 0x000188              | QEI1 – Position Counter Compare    |

| 67-72            | 59-64                      | 0x00008A-<br>0x000094 | 0x00018A-<br>0x000194 | Reserved                           |

| 73               | 65                         | 0x000096              | 0x000196              | U1E – UART1 Error Interrupt        |

| 74               | 66                         | 0x000098              | 0x000198              | U2E – UART2 Error Interrupt        |

| 75-77            | 67-69                      | 0x00009A-             | 0x00019A-             | Reserved                           |

| 1011             | 01 00                      | 0x00009E              | 0x00019E              |                                    |

| 78               | 70                         | 0x0000A0              | 0x0001A0              | C1TX – ECAN1 Transmit Data Request |

| 79               | 71                         | 0x0000A2              | 0x0001A2              | Reserved                           |

| 80               | 72                         | 0x0000A4              | 0x0001A4              | Reserved                           |

| 81               | 73                         | 0x0000A6              | 0x0001A6              | PWM Secondary Special Event Match  |

| 82               | 74                         | 0x0000A8              | 0x0001A8              | Reserved                           |

| 83               | 75                         | 0x0000AA              | 0x0001AA              | QEI2 – Position Counter Compare    |

| 84-88            | 76-80                      | 0x0000AC-             | 0x0001AC-             | Reserved                           |

| 04 00            | 10.00                      | 0x0000B4              | 0x0001B4              |                                    |

| 89               | 81                         | 0x0000B6              | 0x0001B6              | ADC Pair 8 Conversion Done         |

| 90               | 82                         | 0x0000B8              | 0x0001B8              | ADC Pair 9 Conversion Done         |

| 91               | 83                         | 0x0000BA              | 0x0001BA              | ADC Pair 10 Conversion Done        |

| 92               | 84                         | 0x0000BC              | 0x0001B/              | ADC Pair 11 Conversion Done        |

| 93               | 85                         | 0x0000BE              | 0x0001BE              | ADC Pair 12 Conversion Done        |

| 94-101           | 86-93                      | 0x0000C0-             | 0x0001DL              | Reserved                           |

| 34-101           | 00-93                      | 0x0000CE              | 0x0001CE              | Iteselved                          |

| 102              | 94                         | 0x0000D0              | 0x0001D0              | PWM1 – PWM1 Interrupt              |

| 103              | 95                         | 0x0000D2              | 0x0001D2              | PWM2 – PWM2 Interrupt              |

| 104              | 96                         | 0x0000D4              | 0x0001D4              | PWM3 – PWM3 Interrupt              |

| 105              | 97                         | 0x0000D6              | 0x0001D6              | PWM4 – PWM4 Interrupt              |

| 106              | 98                         | 0x0000D8              | 0x0001D8              | PWM5 – PWM5 Interrupt              |

| 107              | 99                         | 0x0000DA              | 0x0001DA              | PWM6 – PWM6 Interrupt              |

| 108              | 100                        | 0x0000DC              | 0x0001DC              | PWM7– PWM7 Interrupt               |

| 109              | 101                        | 0x0000DE              | 0x0001DE              | PWM8 – PWM8 Interrupt              |

| 110              | 102                        | 0x0000E0              | 0x0001E0              | PWM9 – PWM9 Interrupt              |

| 111              | 103                        | 0x0000E2              | 0x00001E2             | CMP2 – Analog Comparator 2         |

| 112              | 104                        | 0x0000E4              | 0x0001E4              | CMP3 – Analog Comparator 3         |

| 113              | 105                        | 0x0000E6              | 0x0001E6              | CMP4 – Analog Comparator 4         |

| 114-117          | 106-109                    | 0x0000E8-             | 0x0001E8-             | Reserved                           |

|                  |                            | 0x0000EE              | 0x0001EE              |                                    |

| 118              | 110                        | 0x0000F0              | 0x0001F0              | ADC Pair 0 Convert Done            |

| 119              | 111                        | 0x0000F2              | 0x0001F2              | ADC Pair 1 Convert Done            |

| 120              | 112                        | 0x0000F4              | 0x0001F4              | ADC Pair 2 Convert Done            |

| 121              | 113                        | 0x0000F6              | 0x0001F6              | ADC Pair 3 Convert Done            |

| 122              | 114                        | 0x0000F8              | 0x0001F8              | ADC Pair 4 Convert Done            |

| 123              | 115                        | 0x0000FA              | 0x0001FA              | ADC Pair 5 Convert Done            |

| 124              | 116                        | 0x0000FC              | 0x0001FC              | ADC Pair 6 Convert Done            |

| 125              | 117                        | 0x0000FE              | 0x0001FE              | ADC Pair 7 Convert Done            |

|                  |                            |                       | st Natural Order Pric |                                    |

TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

| REGISTER 7    | 7-6: IFS1: I    | NTERRUPT                          | FLAG STAT       |                  | ER 1            |                 |         |

|---------------|-----------------|-----------------------------------|-----------------|------------------|-----------------|-----------------|---------|

| R/W-0         | R/W-0           | R/W-0                             | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0   |

| U2TXIF        | U2RXIF          | INT2IF                            | T5IF            | T4IF             | OC4IF           | OC3IF           | DMA2IF  |

| bit 15        |                 |                                   |                 |                  |                 |                 | bit 8   |

| U-0           | U-0             | U-0                               | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0   |

| _             | _               | _                                 | INT1IF          | CNIF             | AC1IF           | MI2C1IF         | SI2C1IF |

| bit 7         |                 |                                   |                 |                  |                 |                 | bit (   |

| Legend:       |                 |                                   |                 |                  |                 |                 |         |

| R = Readable  | e bit           | W = Writable                      | bit             | U = Unimpler     | mented bit, rea | d as '0'        |         |

| -n = Value at | POR             | '1' = Bit is set                  | t               | '0' = Bit is cle | ared            | x = Bit is unkr | iown    |

| bit 12        | U2TXIF: UAR     | RT2 Transmitte                    | r Interrupt Fla | g Status bit     |                 |                 |         |

|               | 1 = Interrupt r | request has oc                    | curred          | -                |                 |                 |         |

|               | •               | request has no                    |                 |                  |                 |                 |         |

| bit 11        |                 | RT2 Receiver I                    |                 | Status bit       |                 |                 |         |

|               |                 | request has oc                    |                 |                  |                 |                 |         |

| bit 13        | -               | request has no                    |                 | :.               |                 |                 |         |

| DIL 13        |                 | nal Interrupt 2<br>request has oc | 0               | п                |                 |                 |         |

|               | •               | request has no                    |                 |                  |                 |                 |         |

| bit 12        | -               | Interrupt Flag                    |                 |                  |                 |                 |         |

|               | 1 = Interrupt r | request has oc<br>request has no  | curred          |                  |                 |                 |         |

| bit 11        | -               | Interrupt Flag                    |                 |                  |                 |                 |         |

|               |                 | request has oc                    |                 |                  |                 |                 |         |

|               |                 | request has no                    |                 |                  |                 |                 |         |

| bit 10        | OC4IF: Outpu    | ut Compare Ch                     | nannel 4 Interr | upt Flag Status  | s bit           |                 |         |

|               | •               | request has oc<br>request has no  |                 |                  |                 |                 |         |

| bit 9         | -               | -                                 |                 | upt Flag Status  | bit             |                 |         |

|               | -               | request has oc                    |                 | optillag etailet | 2               |                 |         |

|               | •               | equest has no                     |                 |                  |                 |                 |         |

| bit 8         | DMA2IF: DM      | A Channel 2 D                     | ata Transfer (  | Complete Interr  | upt Flag Status | s bit           |         |

|               |                 | request has oc<br>request has no  |                 |                  |                 |                 |         |

| bit 7-5       | Unimplemen      | ted: Read as '                    | 0'              |                  |                 |                 |         |

| bit 4         | INT1IF: Exter   | nal Interrupt 1                   | Flag Status b   | it               |                 |                 |         |

|               |                 | request has oc<br>request has no  |                 |                  |                 |                 |         |

| bit 3         | -               | -                                 |                 | Flag Status bit  |                 |                 |         |

|               | 1 = Interrupt r | request has oc<br>request has no  | curred          | -                |                 |                 |         |

| bit 2         | •               | g Comparator                      |                 | ag Status bit    |                 |                 |         |

| -             |                 | request has oc                    | -               | J                |                 |                 |         |

|               | 0 = Interrupt r | -                                 |                 |                  |                 |                 |         |

# REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

| U-0                          | U-0                                | U-0             | U-0              | U-0                             | U-0                   | U-0             | U-0     |

|------------------------------|------------------------------------|-----------------|------------------|---------------------------------|-----------------------|-----------------|---------|

| _                            | —                                  |                 | —                | —                               | —                     | _               | —       |

| bit 15                       |                                    |                 |                  |                                 |                       |                 | bit 8   |

| U-0                          | R/W-0                              | R/W-0           | R/W-0            | R/W-0                           | R/W-0                 | R/W-0           | R/W-0   |

|                              | IC4IF                              | IC3IF           | DMA3IF           | C1IF <sup>(1)</sup>             | C1RXIF <sup>(1)</sup> | SPI2IF          | SPI2EIF |

| bit 7                        |                                    | 10011           | Divition         | 0111                            | Onota                 | 01 1211         | bit (   |

|                              |                                    |                 |                  |                                 |                       |                 | _       |

| <b>Legend:</b><br>R = Readab | le hit                             | W = Writable    | bit              | II – I Inimpler                 | mented bit, read      | as '0'          |         |

| -n = Value a                 |                                    | 1' = Bit is se  |                  | $0^{\circ} = \text{Bit is cle}$ |                       | x = Bit is unki | าดพท    |

|                              |                                    |                 | -                |                                 |                       |                 |         |

| bit 15-7                     | Unimplement                        | ted: Read as    | ʻ0'              |                                 |                       |                 |         |

| bit 6                        | -                                  |                 | el 4 Interrupt F | -lag Status bit                 |                       |                 |         |

|                              | 1 = Interrupt r                    | equest has oc   | curred           | C                               |                       |                 |         |

|                              | 0 = Interrupt r                    | equest has no   | ot occurred      |                                 |                       |                 |         |

| bit 5                        |                                    | -               | el 3 Interrupt F | lag Status bit                  |                       |                 |         |

|                              | 1 = Interrupt r                    |                 |                  |                                 |                       |                 |         |

| bit 4                        | 0 = Interrupt r                    | •               |                  | amplata latarr                  | unt Flog Statua k     | .:+             |         |

| DIL 4                        | 1 = Interrupt r                    |                 |                  |                                 | upt Flag Status b     | JIL             |         |

|                              | 0 = Interrupt r                    |                 |                  |                                 |                       |                 |         |

| bit 3                        |                                    | -               | pt Flag Status   | bit <sup>(1)</sup>              |                       |                 |         |

|                              | 1 = Interrupt r                    | equest has oc   | curred           |                                 |                       |                 |         |

|                              | 0 = Interrupt r                    | •               |                  |                                 | ~~~                   |                 |         |

| bit 2                        |                                    |                 | vent Interrupt   | Flag Status bit                 | (1)                   |                 |         |

|                              | 1 = Interrupt r<br>0 = Interrupt r |                 |                  |                                 |                       |                 |         |

| bit 1                        | -                                  | -               | ot Flag Status b | vit                             |                       |                 |         |

|                              | 1 = Interrupt r                    | •               | •                | Л                               |                       |                 |         |

|                              | 0 = Interrupt r                    |                 |                  |                                 |                       |                 |         |

| bit 0                        | SPI2EIF: SPI2                      | 2 Error Interru | pt Flag Status   | bit                             |                       |                 |         |

|                              | 1 = Interrupt r                    |                 |                  |                                 |                       |                 |         |

|                              | 0 – Interrupt r                    | equest has no   | t occurred       |                                 |                       |                 |         |

#### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

**Note 1:** Interrupts are disabled on devices without ECAN<sup>™</sup> modules.

NOTES:

| REGISTER      | 12-1: T1CO                           | N: TIMER1 C                  | ONTROL RE       | EGISTER          |                  |                  |     |

|---------------|--------------------------------------|------------------------------|-----------------|------------------|------------------|------------------|-----|

| R/W-0         | U-0                                  | R/W-0                        | U-0             | U-0              | U-0              | U-0              | U-0 |

| TON           | _                                    | TSIDL                        | _               | _                | _                | —                | _   |

| bit 15        |                                      |                              |                 |                  |                  |                  | bit |

| U-0           | D/M/ O                               | D/M O                        | DM/ 0           | 11.0             | D/M/ O           | D/M/ O           | U-0 |

| 0-0           | R/W-0<br>TGATE                       | R/W-0<br>TCKPS1              | R/W-0<br>TCKPS0 | U-0              | R/W-0<br>TSYNC   | R/W-0<br>TCS     | 0-0 |

| bit 7         | IGALE                                | TORFOT                       | TCKF 30         | _                | TSTINC           | 103              | bit |

|               |                                      |                              |                 |                  |                  |                  | bit |

| Legend:       |                                      |                              |                 |                  |                  |                  |     |

| R = Readable  | e bit                                | W = Writable                 | bit             | U = Unimpler     | mented bit, read | d as '0'         |     |

| -n = Value at | POR                                  | '1' = Bit is set             |                 | '0' = Bit is cle | ared             | x = Bit is unkno | own |

|               |                                      |                              |                 |                  |                  |                  |     |

| bit 15        | TON: Timer1                          |                              |                 |                  |                  |                  |     |

|               | 1 = Starts 16-<br>0 = Stops 16-      |                              |                 |                  |                  |                  |     |

| bit 14        | -                                    | ted: Read as '               | 0'              |                  |                  |                  |     |

| bit 13        | -                                    | 1 Stop in Idle N             |                 |                  |                  |                  |     |

|               |                                      | ues module op                |                 | device enters I  | dle mode         |                  |     |

|               |                                      | s module opera               |                 |                  |                  |                  |     |

| bit 12-7      | Unimplemen                           | ted: Read as '               | 0'              |                  |                  |                  |     |

| bit 6         | TGATE: Time                          | er1 Gated Time               | Accumulation    | n Enable bit     |                  |                  |     |

|               | When TCS =                           |                              |                 |                  |                  |                  |     |

|               | This bit is ign                      |                              |                 |                  |                  |                  |     |

|               | <u>When TCS =</u><br>1 = Gated times | <u>0:</u><br>ne accumulatior | n is anahlad    |                  |                  |                  |     |

|               |                                      | ne accumulation              |                 |                  |                  |                  |     |

| bit 5-4       | TCKPS<1:0>                           | Timer1 Input                 | Clock Prescale  | e Select bits    |                  |                  |     |

|               | 11 <b>= 1:256</b>                    |                              |                 |                  |                  |                  |     |

|               | 10 = 1:64                            |                              |                 |                  |                  |                  |     |

|               | 01 = 1:8<br>00 = 1:1                 |                              |                 |                  |                  |                  |     |

| bit 3         |                                      | ted: Read as '               | 0'              |                  |                  |                  |     |

| bit 2         | -                                    | er1 External Clo             |                 | chronization Se  | elect bit        |                  |     |

|               | When TCS =                           |                              |                 |                  |                  |                  |     |

|               | 1 = Synchron                         | izes external c              |                 |                  |                  |                  |     |

|               |                                      | synchronize ex               | ternal clock in | nput             |                  |                  |     |

|               | When TCS =<br>This bit is ign        |                              |                 |                  |                  |                  |     |

| bit 1         | -                                    | Clock Source S               | Select bit      |                  |                  |                  |     |

| N.L. 1        |                                      |                              |                 | vicina, educ)    |                  |                  |     |

|               | $\perp = External of$                | Clock from 11C               | K DIN (ON THE   | risina eaaei     |                  |                  |     |

|               | 1 = External c<br>0 = Internal c     | clock from T1C<br>lock (FCY) | K pin (on the   | nsing eage)      |                  |                  |     |

# REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| HS/HC-0       | HS/HC-0                                                      | HS/HC-0                                      | R/W-0                 | R/W-0            | R/W-0                           | R/W-0                         | R/W-0               |

|---------------|--------------------------------------------------------------|----------------------------------------------|-----------------------|------------------|---------------------------------|-------------------------------|---------------------|

| FLTSTAT(      | <sup>1)</sup> CLSTAT <sup>(1)</sup>                          | TRGSTAT                                      | FLTIEN                | CLIEN            | TRGIEN                          | ITB <sup>(3)</sup>            | MDCS <sup>(3)</sup> |

| bit 15        |                                                              |                                              |                       |                  |                                 |                               | bit 8               |

| DAMO          | DAM 0                                                        | D/M/ O                                       |                       | R/W-0            | DAMA                            | DAMO                          | DAMO                |

| R/W-0         | R/W-0                                                        | R/W-0<br>DTCP <sup>(4)</sup>                 | U-0                   |                  | R/W-0<br>CAM <sup>(2,3,5)</sup> | R/W-0<br>XPRES <sup>(6)</sup> | R/W-0               |

| DTC1<br>bit 7 | DTC0                                                         | DICPO                                        | —                     | MTBS             | CAM                             | APRES(*)                      | IUE<br>bit          |

|               |                                                              |                                              |                       |                  |                                 |                               |                     |

| Legend:       |                                                              | HC = Hardware                                | Clearable bit         | HS = Hardw       | are Settable bit                |                               |                     |

| R = Reada     | ble bit                                                      | W = Writable b                               | it                    | U = Unimple      | mented bit, rea                 | d as '0'                      |                     |

| -n = Value    | at POR                                                       | '1' = Bit is set                             |                       | '0' = Bit is cl  | eared                           | x = Bit is unk                | nown                |

| bit 15        | FLTSTAT: Fa                                                  | ult Interrupt Stat                           | us bit <sup>(1)</sup> |                  |                                 |                               |                     |

|               |                                                              | rrupt is pending                             |                       |                  |                                 |                               |                     |

|               |                                                              | nterrupt is pend                             |                       |                  |                                 |                               |                     |

|               |                                                              | ared by setting F                            |                       |                  |                                 |                               |                     |

| bit 14        |                                                              | rent-Limit Interru                           | •                     |                  |                                 |                               |                     |

|               |                                                              | mit interrupt is pe<br>nt-limit interrupt is |                       |                  |                                 |                               |                     |

|               |                                                              | ared by setting C                            |                       |                  |                                 |                               |                     |

| bit 13        | TRGSTAT: Tr                                                  | igger Interrupt S                            | tatus bit             |                  |                                 |                               |                     |

|               |                                                              | terrupt is pendin                            | •                     |                  |                                 |                               |                     |

|               |                                                              | r interrupt is pen<br>ared by setting T      |                       |                  |                                 |                               |                     |

| bit 12        |                                                              | t Interrupt Enabl                            |                       |                  |                                 |                               |                     |

|               |                                                              | rrupt is enabled                             | o on                  |                  |                                 |                               |                     |

|               |                                                              | rrupt is disabled                            | and FLTSTAT b         | oit is cleared   |                                 |                               |                     |

| bit 11        | CLIEN: Curre                                                 | ent-Limit Interrup                           | t Enable bit          |                  |                                 |                               |                     |

|               |                                                              | mit interrupt is e<br>mit interrupt is di    |                       | STAT bit is cle  | ared                            |                               |                     |

| bit 10        | TRGIEN: Trig                                                 | ger Interrupt En                             | able bit              |                  |                                 |                               |                     |

|               |                                                              | event generates<br>/ent interrupts a         |                       |                  | is cleared                      |                               |                     |

| bit 9         |                                                              | dent Time Base                               |                       |                  |                                 |                               |                     |

|               | 1 = PHASEx/                                                  | SPHASEx regist                               | ters provide tim      | •                | •                               | enerator                      |                     |

| bit 8         |                                                              | er Duty Cycle Re                             | -                     |                  |                                 |                               |                     |

|               | 1 = MDC regi                                                 | ster provides du<br>d SDCx registers         | ty cycle informa      | ation for this P |                                 | generator                     |                     |

| Note 1:       | Software must cle                                            | ear the interrupt                            | status here and       | l in the corresp | oonding IFSx bit                | in the interrup               | t controller.       |

|               | The Independent<br>CAM bit is ignore                         |                                              | e (ITB = 1) mus       | st be enabled t  | o use Center-A                  | igned mode. If                | ITB = 0, the        |

| 3:            | These bits should                                            | I not be changed                             | after the PWM         | l is enabled by  | setting PTEN (                  | PTCON<15>)                    | = 1.                |

|               | For DTCP to be e                                             |                                              |                       |                  |                                 |                               |                     |

|               | Center-Aligned m<br>registers. The hig<br>the fastest clock. |                                              |                       |                  |                                 |                               |                     |

| 6:            | Configure CLMO<br>Reset mode.                                | D (FCLCONX<8                                 | 3>) = 0 and ITB       | (PWMCONx         | <9>) = 1 to ope                 | rate in Externa               | al Period           |

# REGISTER 16-11: PWMCONX: PWM CONTROL x REGISTER

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| U-0                 | U-0                                | U-0                                 | R/W-0                  | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                |

|---------------------|------------------------------------|-------------------------------------|------------------------|---------------------------------------|----------------------|----------------------|----------------------|

| _                   | _                                  | _                                   | DISSCK                 | DISSDO                                | MODE16               | SMP                  | CKE <sup>(1)</sup>   |

| bit 15              |                                    |                                     |                        |                                       |                      |                      | bit 8                |

| R/W-0               | R/W-0                              | R/W-0                               | R/W-0                  | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                |

| SSEN <sup>(3)</sup> | CKP                                | MSTEN                               | SPRE2 <sup>(2)</sup>   | SPRE1 <sup>(2)</sup>                  | SPRE0 <sup>(2)</sup> | PPRE1 <sup>(2)</sup> | PPRE0 <sup>(2)</sup> |

| bit 7               |                                    |                                     |                        |                                       |                      |                      | bit (                |

| Legend:             |                                    |                                     |                        |                                       |                      |                      |                      |

| R = Readat          | ole bit                            | W = Writable                        | bit                    | U = Unimpler                          | mented bit, read     | l as '0'             |                      |

| -n = Value a        | at POR                             | '1' = Bit is set                    | :                      | '0' = Bit is cle                      | ared                 | x = Bit is unkr      | nown                 |

| bit 15-13           | Unimplemen                         | ted: Read as '                      | 0'                     |                                       |                      |                      |                      |

| bit 12              | DISSCK: Disa                       | able SCKx Pin                       | bit (SPI Maste         | er modes only)                        |                      |                      |                      |

|                     |                                    | PI clock is disa<br>PI clock is ena | · •                    | tions as I/O                          |                      |                      |                      |

| bit 11              | DISSDO: Dis                        | able SDOx Pir                       | bit                    |                                       |                      |                      |                      |

|                     |                                    | is not used by is controlled by     |                        | unctions as I/C                       | )                    |                      |                      |

| oit 10              | -                                  | ord/Byte Comm                       | -                      | ect hit                               |                      |                      |                      |

|                     |                                    | cation is word-                     |                        |                                       |                      |                      |                      |

|                     |                                    | cation is byte-                     |                        |                                       |                      |                      |                      |

| bit 9               | SMP: SPIx D                        | ata Input Sam                       | ole Phase bit          |                                       |                      |                      |                      |

|                     |                                    | a is sampled at                     |                        | ta output time<br>data output tin     | ne                   |                      |                      |

|                     | Slave mode:                        |                                     |                        | n Slave mode.                         |                      |                      |                      |

| bit 8               | CKE: SPIx C                        | lock Edge Sele                      | ect bit <sup>(1)</sup> |                                       |                      |                      |                      |

|                     |                                    |                                     |                        |                                       | clock state to Id    |                      |                      |

| bit 7               | SSEN: Slave                        | Select Enable                       | bit (Slave mo          | de) <sup>(3)</sup>                    |                      |                      |                      |

|                     |                                    | s used for Slav<br>s not used by n  |                        | controlled by p                       | ort function         |                      |                      |

| bit 6               |                                    | olarity Select                      |                        |                                       |                      |                      |                      |

|                     |                                    |                                     |                        | ve state is a lov<br>e state is a hig |                      |                      |                      |

| bit 5               | MSTEN: Mas                         | ter Mode Enat                       | ole bit                |                                       |                      |                      |                      |

|                     | 1 = Master m<br>0 = Slave mo       |                                     |                        |                                       |                      |                      |                      |

|                     | The CKE bit is not<br>(FRMEN = 1). | used in the Fr                      | amed SPI mod           | des. Program t                        | his bit to '0' for   | the Framed SP        | l modes              |

| -                   | Do not set both pri                | mary and seco                       | ondary prescal         | ers to a value                        | of 1:1.              |                      |                      |

| 3: 1                | This bit must be cl                | eared when FF                       | RMEN = 1.              |                                       |                      |                      |                      |

### REGISTER 18-2: SPIxCON1: SPIx CONTROL REGISTER 1

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| Bit Field  | Register | RTSP Effect | Description                                                                                                                                                |

|------------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMPPOL1    | FCMP     | Immediate   | Comparator Hysteresis Polarity bit (for odd numbered comparators)<br>1 = Hysteresis is applied to falling edge<br>0 = Hysteresis is applied to rising edge |

| HYST1<1:0> | FCMP     | Immediate   | Comparator Hysteresis Select bits<br>11 = 45 mV hysteresis<br>10 = 30 mV hysteresis<br>01 = 15 mV hysteresis<br>00 = No hysteresis                         |

| <b>TABLE 24-2:</b> | dsPIC33F CONFIGURATION BITS DESCRIPTION ( | (CONTINUED) |

|--------------------|-------------------------------------------|-------------|

|                    | usi lossi oolii lookanon bito beookii hon |             |

| DC CHA | RACTER | ISTICS                                                                                  | <b>Standar</b><br>(unless<br>Operatir | otherw | /ise sta | <b>ted)</b><br>-40°C | <b>Ins: 3.0V to 3.6V</b><br>$C \le TA \le +85^{\circ}C$ for Industrial<br>$C \le TA \le +125^{\circ}C$ for Extended |

|--------|--------|-----------------------------------------------------------------------------------------|---------------------------------------|--------|----------|----------------------|---------------------------------------------------------------------------------------------------------------------|

| Param. | Symbol | Characteristic                                                                          | Min.                                  | Тур.   | Max.     | Units                | Conditions                                                                                                          |

| DO20A  | Voh1   | <b>Output High Voltage</b><br>I/O Pins:<br>4x Sink Driver Pins – RA0-RA7,               | 1.5                                   | _      | _        | V                    | Іон ≥ -12 mA, Voo = 3.3V<br>(See <b>Note</b> 1)                                                                     |

|        |        | RA14, RA15, RB0-RB15,<br>RC1-RC4, RC12-RC14, RD0-RD2,                                   | 2.0                                   | —      | -        | V                    | IOH ≥ -11 mA, VDD = 3.3V<br>(See <b>Note 1</b> )                                                                    |

|        |        | RD8-RD12, RD14, RD15, RE8,<br>RE9, RF0-RF8, RF12, RF13,<br>RG0-RG3, RG6-RG9, RG14, RG15 | 3.0                                   | —      | —        | V                    | IOH ≥ -3 mA, VDD = 3.3V<br>(See <b>Note 1</b> )                                                                     |

|        |        | <b>Output High Voltage</b><br>I/O Pins:<br>8x Sink Driver Pin – RC15                    | 1.5                                   | _      | _        | V                    | Іон ≥ -16 mA, Voo = 3.3V<br>(See <b>Note 1</b> )                                                                    |

|        |        |                                                                                         | 2.0                                   | _      | -        | V                    | IOH ≥ -12 mA, VDD = 3.3V<br>(See <b>Note 1</b> )                                                                    |

|        |        |                                                                                         | 3.0                                   | —      | —        | V                    | IOH ≥ -4 mA, VDD = 3.3V<br>(See <b>Note 1</b> )                                                                     |

|        |        | <b>Output High Voltage</b><br>I/O Pins:<br>16x Sink Driver Pins – RA9, RA10,            | 1.5                                   | _      | _        | V                    | ІОн ≥ -30 mA, VDD = 3.3V<br>(See <b>Note 1</b> )                                                                    |

|        |        | RD3-RD7, RD13, RE0-RE7,<br>RG12, RG13                                                   | 2.0                                   | —      | —        | V                    | $\begin{array}{l} \mbox{IOH} \geq -25 \mbox{ mA, VDD} = 3.3 \mbox{V} \\ \mbox{(See Note 1)} \end{array}$            |

|        |        |                                                                                         | 3.0                                   | _      | _        | V                    | IOH ≥ -8 mA, VDD = 3.3V<br>(See <b>Note 1</b> )                                                                     |

#### TABLE 27-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS (CONTINUED)

Note 1: Parameters are characterized, but not tested.

## TABLE 27-11: ELECTRICAL CHARACTERISTICS: BROWN-OUT RESET (BOR)

| DC CHAR      | ACTERIST | ICS                                 | (unless otherw | Standard Operating Conditions: 3.0V to $3.6V^{(3)}$<br>unless otherwise stated)<br>Deprating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |      |       |            |  |

|--------------|----------|-------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------------|--|

| Param<br>No. | Symbol   | Character                           | Characteristic |                                                                                                                                                                                                                        | Тур | Max  | Units | Conditions |  |

| BO10         | VBOR     | BOR Event on VDD Tra<br>High-to-Low | ansition       | 2.6                                                                                                                                                                                                                    |     | 2.95 | V     | See Note 2 |  |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

2: The device will operate as normal until the VDDMIN threshold is reached.

**3:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules, such as the ADC, etc., will function but with degraded performance below VDDMIN.

# TABLE 27-34:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       | ARACTERIS             | rics                                                         | Standard Op<br>(unless othe<br>Operating ter | erwise st          | t <b>ated)</b><br>e -40° | C ≤ TA ≤ | <b>IV to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------|-----------------------|--------------------------------------------------------------|----------------------------------------------|--------------------|--------------------------|----------|------------------------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                          | Тур <sup>(2)</sup> | Max                      | Units    | Conditions                                                       |

| SP70         | TscP                  | Maximum SCKx Input Frequency                                 | —                                            |                    | 15                       | MHz      | See Note 3                                                       |

| SP72         | TscF                  | SCKx Input Fall Time                                         | —                                            | _                  | _                        | ns       | See Parameter DO32 and <b>Note 4</b>                             |

| SP73         | TscR                  | SCKx Input Rise Time                                         | —                                            |                    |                          | ns       | See Parameter DO31 and <b>Note 4</b>                             |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                   | —                                            |                    |                          | ns       | See Parameter DO32 and <b>Note 4</b>                             |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                   | —                                            |                    |                          | ns       | See Parameter DO31 and <b>Note 4</b>                             |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                            | 6                  | 20                       | ns       |                                                                  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                           |                    |                          | ns       |                                                                  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                           |                    | —                        | ns       |                                                                  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                           |                    | _                        | ns       |                                                                  |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                          |                    |                          | ns       |                                                                  |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                           | —                  | 50                       | ns       | See Note 4                                                       |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 Tcy + 40                                 | —                  | _                        | ns       | See Note 4                                                       |

| SP60         | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                     | —                                            | _                  | 50                       | ns       |                                                                  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCKx clock, generated by the master, must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

| DC CHA        | RACTERI | ISTICS                                                             | Standard Operating Conditions (unless otherwise stated)Operating temperature: $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |               |       |                                                                                                |  |  |

|---------------|---------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------|-------|------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol  | Characteristic                                                     | Min                                                                                                                                                                                      | Тур | Мах           | Units | Comments                                                                                       |  |  |

| DA10          | RLOAD   | Resistive Output Load<br>Impedance                                 | ЗК                                                                                                                                                                                       | _   | —             | Ω     |                                                                                                |  |  |

| DA11          | CLOAD   | Output Load<br>Capacitance                                         | —                                                                                                                                                                                        | 20  | 35            | pF    |                                                                                                |  |  |

| DA12          | Ιουτ    | Output Current Drive<br>Strength                                   | 200                                                                                                                                                                                      | 300 | 400           | μΑ    | Sink and source                                                                                |  |  |

| DA13          | VRANGE  | Full Output Drive<br>Strength Voltage Range                        | AVss + 250 mV                                                                                                                                                                            | _   | AVDD – 900 mV | V     |                                                                                                |  |  |

| DA14          | VLRANGE | Output Drive Voltage<br>Range at Reduced<br>Current Drive of 50 μA | AVss + 50 mV                                                                                                                                                                             | _   | AVDD – 500 mV | V     |                                                                                                |  |  |