Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 50 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                        |

| Number of I/O              | 58                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 4K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b; D/A 1x10b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs606-50i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. The following pages show their pinout diagrams.

#### TABLE 1: dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 CONTROLLER FAMILIES

|                  |      | ()                            |                   |               |               |                |      |                               |     |       |              |     |                    |                     |            |      |      | ADC                            |                          |          |           |

|------------------|------|-------------------------------|-------------------|---------------|---------------|----------------|------|-------------------------------|-----|-------|--------------|-----|--------------------|---------------------|------------|------|------|--------------------------------|--------------------------|----------|-----------|

| Device           | Pins | Program Flash Memory (Kbytes) | RAM (Bytes)       | 16-Bit Timers | Input Capture | Output Compare | UART | Quadrature Encoder Interfaces | IdS | ECAN™ | DMA Channels | WMd | Analog Comparators | External Interrupts | DAC Output | I²C™ | SARs | Sample-and-Hold (S&H) Circuits | Analog-to-Digital Inputs | I/O Pins | Packages  |

| dsPIC33FJ32GS406 | 64   | 32                            | 4K                | 5             | 4             | 4              | 2    | 1                             | 2   | 0     | 0            | 6x2 | 0                  | 5                   | 0          | 2    | 1    | 5                              | 16                       | 58       | PT,<br>MR |

| dsPIC33FJ32GS606 | 64   | 32                            | 4K                | 5             | 4             | 4              | 2    | 2                             | 2   | 0     | 0            | 6x2 | 4                  | 5                   | 1          | 2    | 2    | 6                              | 16                       | 58       | PT,<br>MR |

| dsPIC33FJ32GS608 | 80   | 32                            | 4K                | 5             | 4             | 4              | 2    | 2                             | 2   | 0     | 0            | 8x2 | 4                  | 5                   | 1          | 2    | 2    | 6                              | 18                       | 74       | PT        |

| dsPIC33FJ32GS610 | 100  | 32                            | 4K                | 5             | 4             | 4              | 2    | 2                             | 2   | 0     | 0            | 9x2 | 4                  | 5                   | 1          | 2    | 2    | 6                              | 24                       | 85       | PT,<br>PF |

| dsPIC33FJ64GS406 | 64   | 64                            | 8K                | 5             | 4             | 4              | 2    | 1                             | 2   | 0     | 0            | 6x2 | 0                  | 5                   | 0          | 2    | 1    | 5                              | 16                       | 58       | PT,<br>MR |

| dsPIC33FJ64GS606 | 64   | 64                            | 9K(1)             | 5             | 4             | 4              | 2    | 2                             | 2   | 1     | 4            | 6x2 | 4                  | 5                   | 1          | 2    | 2    | 6                              | 16                       | 58       | PT,<br>MR |

| dsPIC33FJ64GS608 | 80   | 64                            | 9K <sup>(1)</sup> | 5             | 4             | 4              | 2    | 2                             | 2   | 1     | 4            | 8x2 | 4                  | 5                   | 1          | 2    | 2    | 6                              | 18                       | 74       | PT        |

| dsPIC33FJ64GS610 | 100  | 64                            | 9K <sup>(1)</sup> | 5             | 4             | 4              | 2    | 2                             | 2   | 1     | 4            | 9x2 | 4                  | 5                   | 1          | 2    | 2    | 6                              | 24                       | 85       | PT,<br>PF |

Note 1: RAM size is inclusive of 1-Kbyte DMA RAM.

#### TABLE 4-28: UART1 REGISTER MAP

| File Name | SFR<br>Addr.                             | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7    | Bit 6    | Bit 5 | Bit 4       | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------------------------------------------|----------|--------|----------|--------|--------|--------|-------|------------------------|----------|----------|-------|-------------|---------|--------|--------|-------|---------------|

| U1MODE    | 0220                                     | UARTEN   | —      | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0                   | WAKE     | LPBACK   | ABAUD | URXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA     | 0222                                     | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISEL1 | URXISEL0 | ADDEN | RIDLE       | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG   | 0224                                     | _        | —      | _        | _      | _      | —      | —     |                        |          |          | UART1 | Transmit Re | egister |        |        |       | xxxx          |

| U1RXREG   | 0226                                     | _        | —      | _        | _      | _      | —      | _     | UART1 Receive Register |          |          |       |             |         | 0000   |        |       |               |

| U1BRG     | U1BRG 0228 Baud Rate Generator Prescaler |          |        |          |        |        |        |       |                        | 0000     |          |       |             |         |        |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-29: UART2 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15   | Bit 14                          | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7    | Bit 6    | Bit 5 | Bit 4      | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|----------|---------------------------------|----------|--------|--------|--------|-------|------------------------|----------|----------|-------|------------|---------|--------|--------|-------|---------------|

| U2MODE       | 0230        | UARTEN   | _                               | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                   | WAKE     | LPBACK   | ABAUD | URXINV     | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232        | UTXISEL1 | UTXINV                          | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISEL1 | URXISEL0 | ADDEN | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234        | _        | _                               | _        | _      | —      | _      | _     |                        |          |          | UART2 | Transmit R | egister |        |        |       | xxxx          |

| U2RXREG      | 0236        | _        | _                               | _        | _      | —      | _      | _     | UART2 Receive Register |          |          |       |            |         | 0000   |        |       |               |

| U2BRG        | 0238        |          | Baud Rate Generator Prescaler 0 |          |        |        |        |       |                        |          |          | 0000  |            |         |        |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 7-13: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | OC1IE: Output Compare Channel 1 Interrupt Enable bit |

|-------|------------------------------------------------------|

|       | 1 = Interrupt request is enabled                     |

|       | 0 = Interrupt request is not enabled                 |

| bit 1 | IC1IE: Input Capture Channel 1 Interrupt Enable bit  |

|       | 1 = Interrupt request is enabled                     |

|       | 0 = Interrupt request is not enabled                 |

| bit 0 | INTOIE: External Interrupt 0 Enable bit              |

|       | 1 = Interrupt request is enabled                     |

0 = Interrupt request is not enabled

© 2009-2014 Microchip Technology Inc.

| R/W-0         | R/W-0                                           | U-0                                 | U-0         | U-0              | U-0              | R/W-0           | R/W-0  |  |  |  |  |

|---------------|-------------------------------------------------|-------------------------------------|-------------|------------------|------------------|-----------------|--------|--|--|--|--|

| ADCP1IE       | ADCP0IE                                         |                                     | _           |                  |                  | AC4IE           | AC3IE  |  |  |  |  |

| bit 15        |                                                 |                                     |             |                  |                  |                 | bit 8  |  |  |  |  |

|               |                                                 |                                     |             |                  |                  |                 |        |  |  |  |  |

| R/W-0         | U-0                                             | U-0                                 | U-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| AC2IE         |                                                 | _                                   | _           | PWM6IE           | PWM5IE           | PWM4IE          | PWM3IE |  |  |  |  |

| bit 7         |                                                 |                                     |             |                  |                  |                 | bit (  |  |  |  |  |

| Legend:       |                                                 |                                     |             |                  |                  |                 |        |  |  |  |  |

| R = Readabl   | e bit                                           | W = Writable                        | bit         | U = Unimpler     | nented bit, read | as '0'          |        |  |  |  |  |

| -n = Value at | POR                                             | '1' = Bit is set                    |             | '0' = Bit is cle | ared             | x = Bit is unkn | own    |  |  |  |  |

|               |                                                 |                                     |             |                  |                  |                 |        |  |  |  |  |

| bit 15        | ADCP1IE: AD                                     | DC Pair 1 Conv                      | ersion Done | Interrupt Enable | e bit            |                 |        |  |  |  |  |

|               |                                                 | request is enab                     |             |                  |                  |                 |        |  |  |  |  |

| hi+ 1 /       | •                                               | request is not e                    |             | Interrupt Enchl  | a hit            |                 |        |  |  |  |  |

| bit 14        |                                                 | request is enab                     |             | Interrupt Enable | e bit            |                 |        |  |  |  |  |

|               |                                                 | request is not e                    |             |                  |                  |                 |        |  |  |  |  |

| bit 13-10     | Unimplemen                                      | ted: Read as '                      | 0'          |                  |                  |                 |        |  |  |  |  |

| bit 9         | AC4IE: Analog Comparator 4 Interrupt Enable bit |                                     |             |                  |                  |                 |        |  |  |  |  |

|               | •                                               | request is enab<br>request is not e |             |                  |                  |                 |        |  |  |  |  |

| bit 8         | -                                               | g Comparator                        |             | nable bit        |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt r                                 | request is enab                     | led         |                  |                  |                 |        |  |  |  |  |

|               | -                                               | request is not e                    |             |                  |                  |                 |        |  |  |  |  |

| bit 7         |                                                 | g Comparator                        | -           | hable bit        |                  |                 |        |  |  |  |  |

|               | •                                               | request is enab<br>request is not e |             |                  |                  |                 |        |  |  |  |  |

| bit 6-4       | -                                               | ted: Read as '                      |             |                  |                  |                 |        |  |  |  |  |

| bit 3         | -                                               | /M6 Interrupt E                     |             |                  |                  |                 |        |  |  |  |  |

|               |                                                 | request is enab                     |             |                  |                  |                 |        |  |  |  |  |

|               | 0 = Interrupt r                                 | request is not e                    | nabled      |                  |                  |                 |        |  |  |  |  |

| bit 2         |                                                 | /M5 Interrupt E                     |             |                  |                  |                 |        |  |  |  |  |

|               |                                                 | request is enab<br>request is not e |             |                  |                  |                 |        |  |  |  |  |

| bit 1         | •                                               | /M4 Interrupt E                     |             |                  |                  |                 |        |  |  |  |  |

|               |                                                 | request is enab                     |             |                  |                  |                 |        |  |  |  |  |

|               |                                                 | request is not e                    |             |                  |                  |                 |        |  |  |  |  |

| bit 0         | PWM3IE: PWM3 Interrupt Enable bit               |                                     |             |                  |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt r                                 | equest is enab                      | led         |                  |                  |                 |        |  |  |  |  |

|               | ∩ – Interrupt r                                 | request is not e                    | nablad      |                  |                  |                 |        |  |  |  |  |

# REGISTER 7-19: IEC6: INTERRUPT ENABLE CONTROL REGISTER 6

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| 11.0                                                                       |                                                              |                                      |                 |     |         |         |         |  |  |

|----------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------|-----------------|-----|---------|---------|---------|--|--|

| U-0                                                                        | U-0                                                          | U-0                                  | U-0             | U-0 | R/W-1   | R/W-0   | R/W-0   |  |  |

| _                                                                          | —                                                            | _                                    | —               | —   | INT4IP2 | INT4IP1 | INT4IP0 |  |  |

| bit 15                                                                     |                                                              |                                      |                 |     |         |         | bit 8   |  |  |

|                                                                            |                                                              |                                      |                 |     |         |         |         |  |  |

| U-0                                                                        | R/W-1                                                        | R/W-0                                | R/W-0           | U-0 | U-0     | U-0     | U-0     |  |  |

| —                                                                          | - INT3IP2 INT3IP1 INT3IP0                                    |                                      |                 |     |         |         |         |  |  |

| bit 7                                                                      |                                                              |                                      |                 |     |         |         | bit (   |  |  |

|                                                                            |                                                              |                                      |                 |     |         |         |         |  |  |

| Legend:                                                                    |                                                              |                                      |                 |     |         |         |         |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'         |                                                              |                                      |                 |     |         |         |         |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                              |                                      |                 |     |         |         |         |  |  |

| bit 10-8                                                                   | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup | ot source is dis                     | highest priorit |     |         |         |         |  |  |

| bit 7                                                                      | =                                                            | ted: Read as '                       |                 |     |         |         |         |  |  |

| bit 6-4                                                                    | 111 = Interru<br>•<br>•                                      | External Internot is Priority 7 (    |                 |     |         |         |         |  |  |

|                                                                            | 001 = Interru<br>000 = Interru                               | ot is Priority 1<br>ot source is dis | abled           |     |         |         |         |  |  |

## REGISTER 7-32: IPC13: INTERRUPT PRIORITY CONTROL REGISTER 13

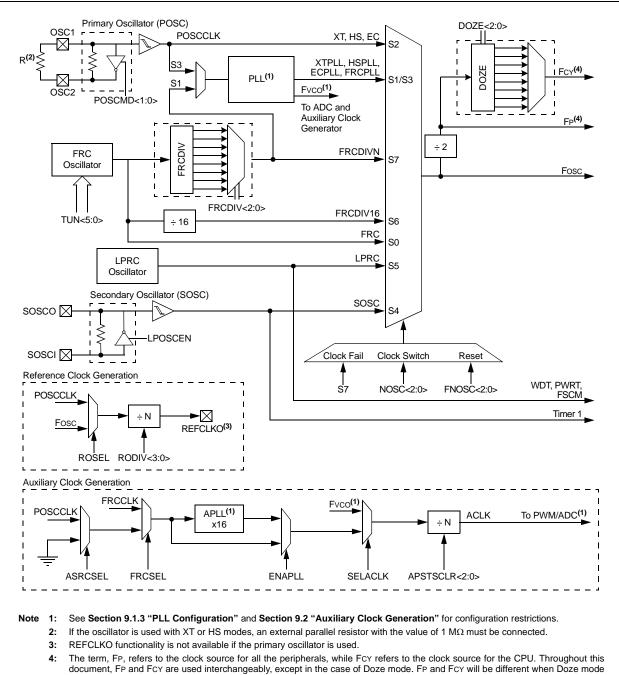

#### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

is used in any ratio other than 1:1, which is the default.

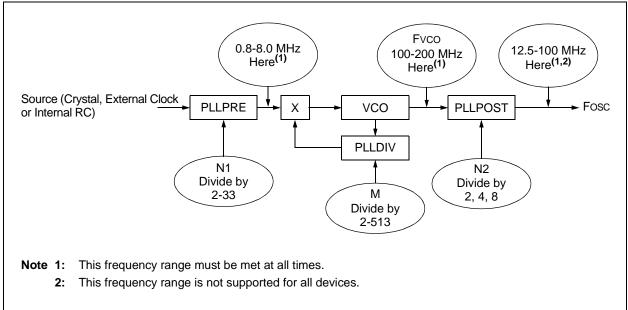

#### 9.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides significant flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 9-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected in the range of 0.8 MHz to 8 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor, 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor, 'N2'. This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4 or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 100 MHz, which generates device operating speeds of 6.25-50 MIPS.

#### FIGURE 9-2: PLL BLOCK DIAGRAM

For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by Equation 9-2.

#### EQUATION 9-2: Fosc CALCULATION

| FOSC = FIN *                  | ( M )                |

|-------------------------------|----------------------|

| $\Gamma OSC = \Gamma IN^{-1}$ | $\overline{N1 * N2}$ |

For example, suppose a 10 MHz crystal is being used with the selected oscillator mode of XT with PLL (see Equation 9-3).

- If PLLPRE<4:0> = 0000, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz.

- If PLLDIV<8:0> = 0x26, then M = 40. This yields a VCO output of 5 x 40 = 200 MHz, which is within the 100-200 MHz ranged needed.

- If PLLPOST<1:0> = 00, then N2 = 2. This provides a Fosc of 200/2 = 100 MHz. The resultant device operating speed is 100/2 = 40 MIPS.

#### EQUATION 9-3: XT WITH PLL MODE EXAMPLE

FCY =

$$\frac{\text{Fosc}}{2} = \frac{1}{2} \left( \frac{10000000 * 40}{2 * 2} \right) = 50 \text{ MIPS}$$

| REGISTER 9      | -2: CLKD                      |                  | DIVISOR REC                           | SISTER               |                  |                    |              |  |  |  |  |  |

|-----------------|-------------------------------|------------------|---------------------------------------|----------------------|------------------|--------------------|--------------|--|--|--|--|--|

| R/W-0           | R/W-0                         | R/W-1            | R/W-1                                 | R/W-0                | R/W-0            | R/W-0              | R/W-0        |  |  |  |  |  |

| ROI             | DOZE2                         | DOZE1            | DOZE0                                 | DOZEN <sup>(1)</sup> | FRCDIV2          | FRCDIV1            | FRCDIV0      |  |  |  |  |  |

| bit 15          | ·                             |                  |                                       |                      |                  | ·                  | bit 8        |  |  |  |  |  |

|                 |                               |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

| R/W-0           | R/W-1                         | U-0              | R/W-0                                 | R/W-0                | R/W-0            | R/W-0              | R/W-0        |  |  |  |  |  |

| PLLPOST1        | PLLPOST0                      | —                | PLLPRE4                               | PLLPRE3              | PLLPRE2          | PLLPRE1            | PLLPRE0      |  |  |  |  |  |

| bit 7           |                               |                  |                                       |                      |                  |                    | bit 0        |  |  |  |  |  |

| Legend:         |                               |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

| R = Readable    | bit                           | W = Writable     | bit                                   | U = Unimpler         | mented bit, read | d as '0'           |              |  |  |  |  |  |

| -n = Value at F |                               | '1' = Bit is se  |                                       | '0' = Bit is cle     |                  | x = Bit is unkr    | nown         |  |  |  |  |  |

|                 | U.V.                          |                  |                                       | 0 - Bit io oid       |                  |                    |              |  |  |  |  |  |

| bit 15          | ROI: Recover                  | r on Interrupt b | bit                                   |                      |                  |                    |              |  |  |  |  |  |

|                 |                               | -                |                                       | d the processo       | or clock/periphe | ral clock ratio is | s set to 1:1 |  |  |  |  |  |

|                 |                               |                  | ct on the DOZE                        |                      |                  |                    |              |  |  |  |  |  |

| bit 14-12       | DOZE<2:0>:                    | Processor Clo    | ck Reduction S                        | Select bits          |                  |                    |              |  |  |  |  |  |

|                 | 111 = FCY/12                  | -                |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 110 = FCY/64                  |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 101 = FCY/32<br>100 = FCY/16  |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 100 = FCY/10<br>011 = FCY/8 ( |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 010 = FCY/4                   |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 001 = FCY/2                   |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 000 = FCY/1                   |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

| bit 11          |                               | e Mode Enabl     |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 |                               |                  | fies the ratio be<br>eral clock ratio |                      | ripheral clocks  | and the process    | sor clocks   |  |  |  |  |  |

| bit 10-8        | FRCDIV<2:0                    | Internal Fas     | t RC Oscillator                       | Postscaler bit       | s                |                    |              |  |  |  |  |  |

|                 | 111 <b>= FRC d</b> i          | •                |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 110 = FRC di                  |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 101 = FRC di<br>100 = FRC di  | •                |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 011 = FRC di                  |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 010 = FRC di                  | -                |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 001 <b>= FRC d</b>            |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 |                               | ivide-by-1 (def  | ,                                     |                      |                  |                    |              |  |  |  |  |  |

| bit 7-6         |                               |                  | Output Divide                         | r Select bits (a     | lso denoted as   | 'N2', PLL posts    | caler)       |  |  |  |  |  |

|                 | 11 = Output/8                 |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 10 = Reserve<br>01 = Output/4 |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 00 = Output/2                 |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

| bit 5           | •                             | ted: Read as     | '0'                                   |                      |                  |                    |              |  |  |  |  |  |

| bit 4-0         | •                             |                  |                                       | Divider bits (a      | also denoted as  | 'N1', PLL pres     | caler)       |  |  |  |  |  |

|                 | 00000 = Inpu<br>00001 = Inpu  | ıt/2 (default)   |                                       |                      |                  | , , ,              | ,            |  |  |  |  |  |

|                 | •                             |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | •                             |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | •                             |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | 11111 = Inpu                  | ıt/33            |                                       |                      |                  |                    |              |  |  |  |  |  |

|                 | •                             |                  |                                       |                      |                  |                    |              |  |  |  |  |  |

#### \_\_\_\_\_

Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

| REGISTER     | R 10-2: PMD2                                                                      | 2: PERIPHER                            | AL MODUL     | E DISABLE C       | ONTROL RE        | GISTER 2        |       |  |  |

|--------------|-----------------------------------------------------------------------------------|----------------------------------------|--------------|-------------------|------------------|-----------------|-------|--|--|

| U-0          | U-0                                                                               | U-0                                    | U-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |

|              |                                                                                   | <u> </u>                               |              | IC4MD             | IC3MD            | IC2MD           | IC1MD |  |  |

| bit 15       |                                                                                   |                                        |              |                   |                  |                 | bit 8 |  |  |

| U-0          | U-0                                                                               | U-0                                    | U-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |

|              | —                                                                                 | OC4MD OC3MD OC2MD                      |              |                   |                  |                 |       |  |  |

| bit 7        |                                                                                   |                                        |              |                   |                  |                 | bit C |  |  |

| Legend:      |                                                                                   |                                        |              |                   |                  |                 |       |  |  |

| R = Readab   | ole bit                                                                           | W = Writable b                         | it           | U = Unimplem      | nented bit, read | d as '0'        |       |  |  |

| -n = Value a | at POR                                                                            | '1' = Bit is set                       |              | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |

| bit 15-12    | Unimplemen                                                                        | ted: Read as '0                        | ,            |                   |                  |                 |       |  |  |

| bit 11       | -                                                                                 | Capture 4 Mod                          |              | it                |                  |                 |       |  |  |

|              | 1 = Input Capture 4 module is disabled                                            |                                        |              |                   |                  |                 |       |  |  |

|              | 0 = Input Cap                                                                     | oture 4 module is                      | s enabled    |                   |                  |                 |       |  |  |

| bit 19       | IC3MD: Input Capture 3 Module Disable bit                                         |                                        |              |                   |                  |                 |       |  |  |

|              | 1 = Input Capture 3 module is disabled                                            |                                        |              |                   |                  |                 |       |  |  |

|              | 0 = Input Capture 3 module is enabled                                             |                                        |              |                   |                  |                 |       |  |  |

| bit 9        |                                                                                   | Capture 2 Mod                          |              | it                |                  |                 |       |  |  |

|              |                                                                                   | oture 2 module is<br>oture 2 module is |              |                   |                  |                 |       |  |  |

| bit 8        |                                                                                   | Capture 1 Mod                          |              | it                |                  |                 |       |  |  |

| bit o        |                                                                                   | oture 1 module is                      |              | n                 |                  |                 |       |  |  |

|              |                                                                                   | oture 1 module is                      |              |                   |                  |                 |       |  |  |

| bit 7-4      | Unimplemen                                                                        | ted: Read as '0                        | ,            |                   |                  |                 |       |  |  |

| bit 3        | OC4MD: Out                                                                        | put Compare 4 N                        | Module Disat | ole bit           |                  |                 |       |  |  |

|              |                                                                                   | ompare 4 modul                         |              |                   |                  |                 |       |  |  |

|              | 0 = Output Co                                                                     | ompare 4 modul                         | e is enabled |                   |                  |                 |       |  |  |

| bit 2        |                                                                                   | put Compare 3 N                        |              |                   |                  |                 |       |  |  |

|              | 1 = Output Compare 3 module is disabled<br>0 = Output Compare 3 module is enabled |                                        |              |                   |                  |                 |       |  |  |

| bit 1        | OC2MD: Out                                                                        | put Compare 2 N                        | Module Disat | ole bit           |                  |                 |       |  |  |

|              |                                                                                   | ompare 2 modul<br>ompare 2 modul       |              |                   |                  |                 |       |  |  |

| bit 0        | •                                                                                 | put Compare 1                          |              | ole bit           |                  |                 |       |  |  |

| -            |                                                                                   | ompare 1 modul                         |              | -                 |                  |                 |       |  |  |

|              | 0 = Output Co                                                                     |                                        |              |                   |                  |                 |       |  |  |

# REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

NOTES:

| TABLE 24-2:       dsPIC33F CONFIGURATION BITS DESCRIPTION |          |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-----------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit Field                                                 | Register | RTSP Effect                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| BWRP                                                      | FBS      | Immediate                                                                                              | Boot Segment Program Flash Write Protection bit<br>1 = Boot segment can be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| BSS<2:0>                                                  | FBS      | Immediate                                                                                              | Boot Segment Program Flash Code Protection Size bits         X11 = No boot program Flash segment         Boot Space is 256 Instruction Words (except interrupt vectors):         110 = Standard security; boot program Flash segment ends at         0x0003FE         010 = High security; boot program Flash segment ends at         0x0003FE         Boot Space is 768 Instruction Words (except interrupt vectors):         101 = Standard security; boot program Flash segment ends at         0x0007FE         001 = High security; boot program Flash segment ends at         0x0007FE         001 = High security; boot program Flash segment ends at         0x0007FE         001 = Standard security; boot program Flash segment ends at         0x0007FE         Boot Space is 1792 Instruction Words (except interrupt vectors):         100 = Standard security; boot program Flash segment ends at         0x000FFE         000 = High security; boot program Flash segment ends at         0x000FFE         000 = High security; boot program Flash segment ends at         0x000FFE |  |  |  |  |  |  |

| GSS<1:0>                                                  | FGS      | Immediate                                                                                              | General Segment Code-Protect bits<br>11 = User program memory is not code-protected<br>10 = Standard security<br>0x = High security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| GWRP                                                      | FGS      | Immediate                                                                                              | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| IESO                                                      | FOSCSEL  | Immediate                                                                                              | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start-up device with FRC, then automatically switch to the user selected oscillator source when ready</li> <li>0 = Start-up device with user selected oscillator source</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| FNOSC<2:0>                                                | FOSCSEL  | If clock switch<br>is enabled,<br>RTSP effect<br>is on any<br>device Reset;<br>otherwise,<br>immediate | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) Oscillator with Postscaler<br>110 = Internal Fast RC (FRC) Oscillator with Divide-by-16<br>101 = LPRC Oscillator<br>100 = Secondary (LP) Oscillator<br>011 = Primary (XT, HS, EC) Oscillator with PLL<br>010 = Primary (XT, HS, EC) Oscillator<br>001 = Internal Fast RC (FRC) Oscillator with PLL<br>000 = FRC Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| FCKSM<1:0>                                                | FOSC     | Immediate                                                                                              | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| OSCIOFNC                                                  | FOSC     | Immediate                                                                                              | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is the general purpose digital I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| POSCMD<1:0>                                               | FOSC     | Immediate                                                                                              | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

####

| DC CHA | RACTER                                                                       | ISTICS                                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |                                                  |                                                                                                          |  |  |  |

|--------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| Param. | Symbol                                                                       | Characteristic                                                                          | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max. | Units                                            | Conditions                                                                                               |  |  |  |

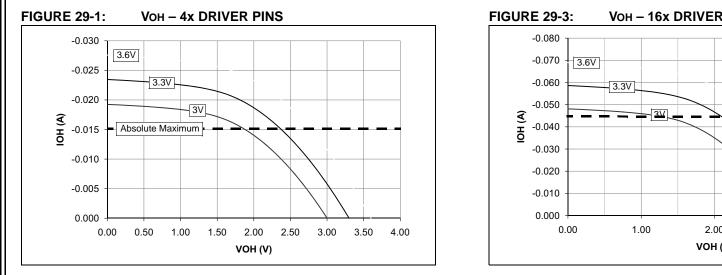

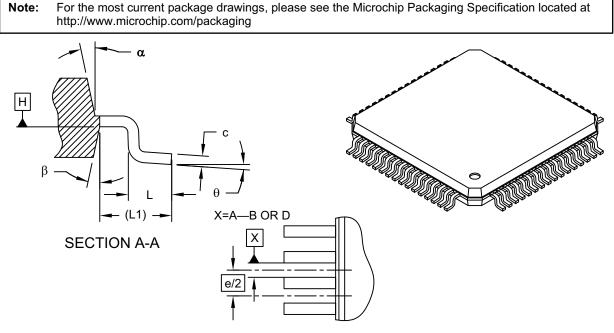

| DO20A  | Voh1                                                                         | <b>Output High Voltage</b><br>I/O Pins:<br>4x Sink Driver Pins – RA0-RA7,               | 1.5                                                                                                                                                                                                                                                                                     | _    | _    | V                                                | Іон ≥ -12 mA, Voo = 3.3V<br>(See <b>Note</b> 1)                                                          |  |  |  |

|        | RA14, RA15, RB0-RB15,<br>RC1-RC4, RC12-RC14, RD0-RD2,                        | 2.0                                                                                     | —                                                                                                                                                                                                                                                                                       | -    | V    | IOH ≥ -11 mA, VDD = 3.3V<br>(See <b>Note 1</b> ) |                                                                                                          |  |  |  |

|        | RE9, RF0-RF8, R<br>RG0-RG3, RG6-R                                            | RD8-RD12, RD14, RD15, RE8,<br>RE9, RF0-RF8, RF12, RF13,<br>RG0-RG3, RG6-RG9, RG14, RG15 | 3.0                                                                                                                                                                                                                                                                                     | —    | —    | V                                                | IOH ≥ -3 mA, VDD = 3.3V<br>(See <b>Note 1</b> )                                                          |  |  |  |

|        |                                                                              | Output High Voltage<br>I/O Pins:<br>8x Sink Driver Pin – RC15                           | 1.5                                                                                                                                                                                                                                                                                     | _    | _    | V                                                | Іон ≥ -16 mA, Voo = 3.3V<br>(See <b>Note 1</b> )                                                         |  |  |  |

|        |                                                                              |                                                                                         | 2.0                                                                                                                                                                                                                                                                                     | _    | -    | V                                                | IOH ≥ -12 mA, VDD = 3.3V<br>(See <b>Note 1</b> )                                                         |  |  |  |

|        |                                                                              |                                                                                         | 3.0                                                                                                                                                                                                                                                                                     | —    | —    | V                                                | IOH ≥ -4 mA, VDD = 3.3V<br>(See <b>Note 1</b> )                                                          |  |  |  |

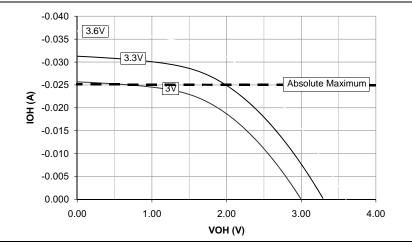

|        | <b>Output High Voltage</b><br>I/O Pins:<br>16x Sink Driver Pins – RA9, RA10, |                                                                                         | 1.5                                                                                                                                                                                                                                                                                     | _    | _    | V                                                | ІОн ≥ -30 mA, VDD = 3.3V<br>(See <b>Note 1</b> )                                                         |  |  |  |

|        |                                                                              | RD3-RD7, RD13, RE0-RE7,<br>RG12, RG13                                                   | 2.0                                                                                                                                                                                                                                                                                     | —    | —    | V                                                | $\begin{array}{l} \mbox{IOH} \geq -25 \mbox{ mA, VDD} = 3.3 \mbox{V} \\ \mbox{(See Note 1)} \end{array}$ |  |  |  |

|        |                                                                              |                                                                                         |                                                                                                                                                                                                                                                                                         | _    | _    | V                                                | IOH ≥ -8 mA, VDD = 3.3V<br>(See <b>Note 1</b> )                                                          |  |  |  |

#### TABLE 27-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS (CONTINUED)

Note 1: Parameters are characterized, but not tested.

## TABLE 27-11: ELECTRICAL CHARACTERISTICS: BROWN-OUT RESET (BOR)

| DC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V}^{(3)} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |          |                    |     |      |       |            |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-----|------|-------|------------|

| Param<br>No.       | Symbol | Character                                                                                                                                                                                                                                                                                 | istic    | Min <sup>(1)</sup> | Тур | Max  | Units | Conditions |

| BO10               | VBOR   | BOR Event on VDD Tra<br>High-to-Low                                                                                                                                                                                                                                                       | ansition | 2.6                |     | 2.95 | V     | See Note 2 |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

2: The device will operate as normal until the VDDMIN threshold is reached.

**3:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules, such as the ADC, etc., will function but with degraded performance below VDDMIN.

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

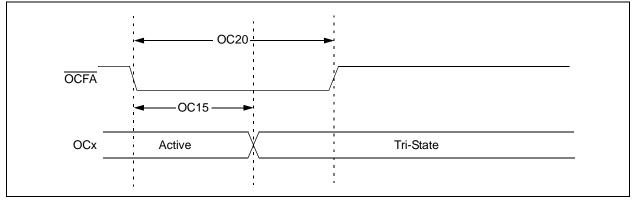

#### FIGURE 27-8: OUTPUT COMPARE x/PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 27-28: SIMPLE OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |          |     |          |       |            |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                       | Min      | Тур | Max      | Units | Conditions |

| OC15               | TFD    | Fault Input to PWM I/O<br>Change                                                                                                                                                                                                                                                    | _        |     | Tcy + 20 | ns    |            |

| OC20               | TFLT   | Fault Input Pulse Width                                                                                                                                                                                                                                                             | Tcy + 20 | _   | —        | ns    |            |

**Note 1:** These parameters are characterized but not tested in manufacturing.

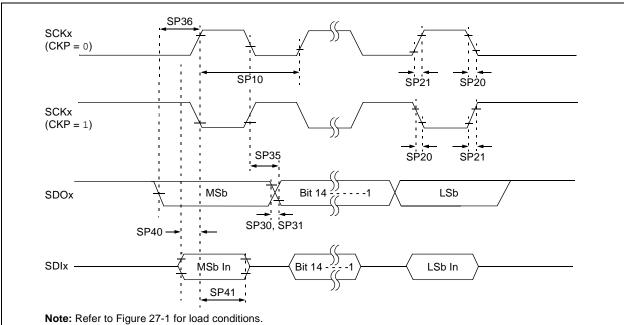

# FIGURE 27-13: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 27-32:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |

|--------------------|-----------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                 | Min                                                                                                                                                                                                                                                                                 | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP10               | TscP                  | Maximum SCKx Frequency                        |                                                                                                                                                                                                                                                                                     | —                  | 10  | MHz   | See Note 3                           |

| SP20               | TscF                  | SCKx Output Fall Time                         | _                                                                                                                                                                                                                                                                                   | —                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP21               | TscR                  | SCKx Output Rise Time                         | _                                                                                                                                                                                                                                                                                   | —                  | _   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30               | TdoF                  | SDOx Data Output Fall Time                    | _                                                                                                                                                                                                                                                                                   | —                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31               | TdoR                  | SDOx Data Output Rise Time                    | _                                                                                                                                                                                                                                                                                   | —                  | _   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge     | _                                                                                                                                                                                                                                                                                   | 6                  | 20  | ns    |                                      |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                                                                                                                                                                                                                                                                  | —                  | _   | ns    |                                      |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                                                                                                                                                                                                                                                                  | -                  | _   | ns    |                                      |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30                                                                                                                                                                                                                                                                                  | —                  | —   | ns    |                                      |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPIx pins.

#### DC AND AC DEVICE CHARACTERISTICS GRAPHS 29.0

The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes Note: only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

#### **VOH – 8x DRIVER PINS FIGURE 29-2:**

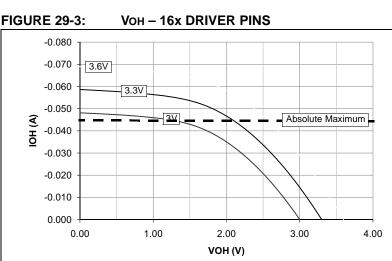

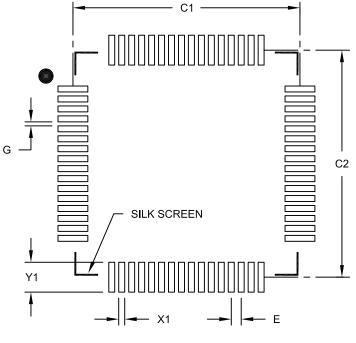

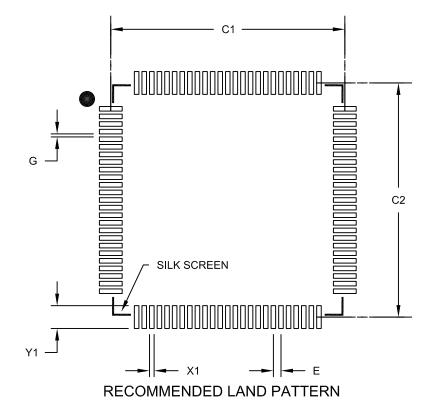

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

DETAIL 1

|                          | Units | Ν         | ILLIMETER | S    |  |

|--------------------------|-------|-----------|-----------|------|--|

| Dimension Limits         |       | MIN       | NOM       | MAX  |  |

| Number of Leads          | N     |           | 64        |      |  |

| Lead Pitch               | е     |           | 0.50 BSC  |      |  |

| Overall Height           | Α     | -         | -         | 1.20 |  |

| Molded Package Thickness | A2    | 0.95      | 1.00      | 1.05 |  |

| Standoff                 | A1    | 0.05      | -         | 0.15 |  |

| Foot Length              | L     | 0.45      | 0.60      | 0.75 |  |

| Footprint                | L1    | 1.00 REF  |           |      |  |

| Foot Angle               | ø     | 0°        | 3.5°      | 7°   |  |

| Overall Width            | E     | 12.00 BSC |           |      |  |

| Overall Length           | D     | 12.00 BSC |           |      |  |

| Molded Package Width     | E1    | 10.00 BSC |           |      |  |

| Molded Package Length    | D1    | 10.00 BSC |           |      |  |

| Lead Thickness           | С     | 0.09      | -         | 0.20 |  |

| Lead Width               | b     | 0.17      | 0.22      | 0.27 |  |

| Mold Draft Angle Top     | α     | 11°       | 12°       | 13°  |  |

| Mold Draft Angle Bottom  | β     | 11°       | 12°       | 13°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.