Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10b; D/A 1x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs610-e-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

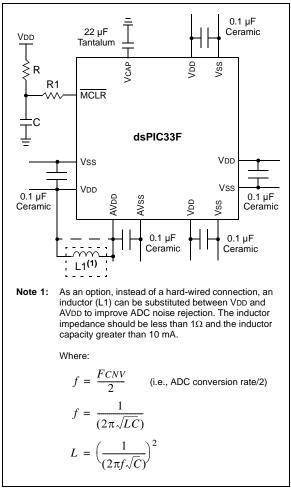

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

#### 2.3 Capacitor on Internal Voltage Regulator (VCAP)

A low-ESR (< 0.5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a minimum capacitor of 22  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 27.0 "Electrical Characteristics"** for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 24.2** "**On-Chip Voltage Regulator**" for details.

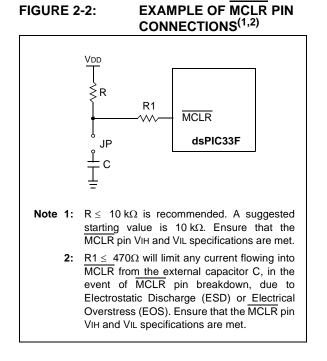

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### TABLE 4-30: SPI1 REGISTER MAP

| File Name | SFR<br>Addr. | Bit 15 | Bit 14                                         | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-----------|--------------|--------|------------------------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|-------|--------|--------|---------------|

| SPI1STAT  | 0240         | SPIEN  | _                                              | SPISIDL | _      | _      | _      |       |       | —     | SPIROV |       |       | _     |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1  | 0242         | _      | _                                              | —       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000          |

| SPI1CON2  | 0244         | FRMEN  | SPIFSD                                         | FRMPOL  | _      | _      | _      | _     | _     | _     | _      | _     | _     | _     | _     | FRMDLY | _      | 0000          |

| SPI1BUF   | 0248         |        | SPI1 Transmit and Receive Buffer Register 0000 |         |        |        |        |       |       |       |        | 0000  |       |       |       |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-31: SPI2 REGISTER MAP

| File Name | SFR<br>Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8       | Bit 7       | Bit 6       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-----------|--------------|--------|--------|---------|--------|--------|--------|----------|-------------|-------------|-------------|-------|-------|-------|-------|--------|--------|---------------|

| SPI2STAT  | 0260         | SPIEN  | —      | SPISIDL | —      | —      | _      |          | —           | _           | SPIROV      | _     | _     | _     | _     | SPITBF | SPIRBF | 0000          |

| SPI2CON1  | 0262         | _      | -      | _       | DISSCK | DISSDO | MODE16 | SMP      | CKE         | SSEN        | CKP         | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000          |

| SPI2CON2  | 0264         | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _      | _        | _           | _           | _           | _     | _     | _     | _     | FRMDLY | _      | 0000          |

| SPI2BUF   | 0268         |        |        |         |        |        |        | SPI2 Tra | nsmit and F | Receive But | fer Registe | r     |       |       |       |        |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-66: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing      |

|-------|-----------------------------------------------|

|       | mode specified in the instruction can differ  |

|       | for the source and destination EA. How-       |

|       | ever, the 4-bit Wb (Register Offset) field is |

|       | shared by both source and destination         |

|       | (but typically only used by one).             |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through Register Indirect tables.

The two-source operand, prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the MAC class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.3.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- Upper boundary addresses for incrementing buffers

- Lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

#### 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWMx bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume<br>word-sized data (LSb of every EA is<br>always clear). The XB value is scaled<br>accordingly to generate compatible (byte) |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | addresses.                                                                                                                                                           |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed         |

|-------|--------------------------------------------|

|       | Addressing should not be enabled           |

|       | together. If an application attempts to do |

|       | so, Bit-Reversed Addressing will assume    |

|       | priority when active for the X WAGU and X  |

|       | WAGU, and Modulo Addressing will be        |

|       | disabled. However, Modulo Addressing will  |

|       | continue to function in the X RAGU.        |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "**Reset**" (DS70192) in the "*dsPIC33/PIC24 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: Software RESET Instruction

- WDTO: Watchdog Timer Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

| Note: | Refer to the specific peripheral section or |

|-------|---------------------------------------------|

|       | Section 3.0 "CPU" of this data sheet for    |

|       | register Reset states.                      |

All types of device Reset sets a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| U-0              | U-0                                                                                                                                                                                    | U-0                                                                                                                                                                   | U-0                                                                                          | U-0                               | R/W-1              | R/W-0           | R/W-0   |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------|--------------------|-----------------|---------|--|--|--|--|

| _                | _                                                                                                                                                                                      | _                                                                                                                                                                     | —                                                                                            |                                   | DMA1IP2            | DMA1IP1         | DMA1IP0 |  |  |  |  |

| bit 15           | ·                                                                                                                                                                                      |                                                                                                                                                                       | -                                                                                            |                                   | •                  |                 | bit 8   |  |  |  |  |

| U-0              | R/W-1                                                                                                                                                                                  | R/W-0                                                                                                                                                                 | R/W-0                                                                                        | U-0                               | R/W-1              | R/W-0           | R/W-0   |  |  |  |  |

| _                | ADIP2                                                                                                                                                                                  | ADIP1                                                                                                                                                                 | ADIP0                                                                                        |                                   | U1TXIP2            | U1TXIP1         | U1TXIP0 |  |  |  |  |

| bit 7            |                                                                                                                                                                                        |                                                                                                                                                                       |                                                                                              |                                   |                    |                 | bit     |  |  |  |  |

| Legend:          |                                                                                                                                                                                        |                                                                                                                                                                       |                                                                                              |                                   |                    |                 |         |  |  |  |  |

| R = Readab       | le bit                                                                                                                                                                                 | W = Writable                                                                                                                                                          | bit                                                                                          | U = Unimpler                      | mented bit, read   | l as '0'        |         |  |  |  |  |

| -n = Value a     | t POR                                                                                                                                                                                  | '1' = Bit is set                                                                                                                                                      |                                                                                              | '0' = Bit is cle                  | ared               | x = Bit is unkr | nown    |  |  |  |  |

| oit 15-11        | Unimplomon                                                                                                                                                                             | ted: Read as '                                                                                                                                                        | 0'                                                                                           |                                   |                    |                 |         |  |  |  |  |

|                  | -                                                                                                                                                                                      |                                                                                                                                                                       |                                                                                              |                                   |                    |                 |         |  |  |  |  |

| bit 10-8         |                                                                                                                                                                                        |                                                                                                                                                                       |                                                                                              | =                                 | e Interrupt Priori | ly bits         |         |  |  |  |  |

|                  | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul>                                                                                                         |                                                                                                                                                                       |                                                                                              |                                   |                    |                 |         |  |  |  |  |

|                  |                                                                                                                                                                                        |                                                                                                                                                                       |                                                                                              |                                   |                    |                 |         |  |  |  |  |

|                  | •                                                                                                                                                                                      |                                                                                                                                                                       |                                                                                              |                                   |                    |                 |         |  |  |  |  |

|                  | •                                                                                                                                                                                      |                                                                                                                                                                       |                                                                                              |                                   |                    |                 |         |  |  |  |  |

|                  |                                                                                                                                                                                        | pt is Priority 1<br>pt source is dis                                                                                                                                  | abled                                                                                        |                                   |                    |                 |         |  |  |  |  |

| bit 7            | 000 = Interru                                                                                                                                                                          |                                                                                                                                                                       |                                                                                              |                                   |                    |                 |         |  |  |  |  |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen                                                                                                                                                            | pt source is dis                                                                                                                                                      | 0'                                                                                           | Interrupt Priori                  | ty bits            |                 |         |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>ADIP<2:0>: /                                                                                                                                            | pt source is dis<br><b>ited:</b> Read as '                                                                                                                            | 0'<br>ion Complete                                                                           | -                                 | ty bits            |                 |         |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>ADIP<2:0>: /                                                                                                                                            | pt source is dis<br><b>Ited:</b> Read as '<br>ADC1 Conversi                                                                                                           | 0'<br>ion Complete                                                                           | -                                 | ty bits            |                 |         |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>ADIP<2:0>: /                                                                                                                                            | pt source is dis<br><b>Ited:</b> Read as '<br>ADC1 Conversi                                                                                                           | 0'<br>ion Complete                                                                           | -                                 | ty bits            |                 |         |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>ADIP<2:0>: /<br>111 = Interru<br>•<br>•                                                                                                                 | pt source is dis<br><b>ited:</b> Read as '<br>ADC1 Conversi<br>pt is Priority 7 (                                                                                     | 0'<br>ion Complete                                                                           | -                                 | ty bits            |                 |         |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>ADIP<2:0>: /<br>111 = Interru<br>•<br>•<br>001 = Interru                                                                                                | pt source is dis<br><b>Ited:</b> Read as '<br>ADC1 Conversi                                                                                                           | <sup>0'</sup><br>ion Complete<br>(highest priorit                                            | -                                 | ty bits            |                 |         |  |  |  |  |

| bit 6-4          | 000 = Interru<br>Unimplemen<br>ADIP<2:0>: /<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru                                                                               | pt source is dis<br><b>ited:</b> Read as '<br>ADC1 Conversi<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                             | <sup>0'</sup><br>ion Complete<br>(highest priorit<br>abled                                   | -                                 | ty bits            |                 |         |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>ADIP<2:0>: /<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen                                                                 | pt source is dis<br><b>ited:</b> Read as '<br>ADC1 Conversi<br>pt is Priority 7 (<br>pt is Priority 1                                                                 | <sup>0'</sup><br>ion Complete<br>(highest priorit<br>abled<br>0'                             | y interrupt)                      | ty bits            |                 |         |  |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>ADIP<2:0>: /<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0>                                                  | pt source is dis<br><b>ated:</b> Read as '<br>ADC1 Conversi<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ated:</b> Read as '                   | 0'<br>ion Complete<br>(highest priorit<br>abled<br>0'<br>smitter Interru                     | ty interrupt)<br>pt Priority bits | ty bits            |                 |         |  |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>ADIP<2:0>: /<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0>                                                  | pt source is dis<br><b>ited:</b> Read as '<br>ADC1 Conversi<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as '<br>>: UART1 Trans | 0'<br>ion Complete<br>(highest priorit<br>abled<br>0'<br>smitter Interru                     | ty interrupt)<br>pt Priority bits | ty bits            |                 |         |  |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>ADIP<2:0>: /<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0>                                                  | pt source is dis<br><b>ited:</b> Read as '<br>ADC1 Conversi<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as '<br>>: UART1 Trans | 0'<br>ion Complete<br>(highest priorit<br>abled<br>0'<br>smitter Interru                     | ty interrupt)<br>pt Priority bits | ty bits            |                 |         |  |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>ADIP<2:0>: /<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0><br>111 = Interru<br>•<br>•<br>•<br>001 = Interru | pt source is dis<br><b>ited:</b> Read as '<br>ADC1 Conversi<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as '<br>>: UART1 Trans | 0'<br>ion Complete<br>(highest priorit<br>abled<br>0'<br>smitter Interru<br>(highest priorit | ty interrupt)<br>pt Priority bits | ty bits            |                 |         |  |  |  |  |

#### REGISTER 7-24: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

#### 11.2 Open-Drain Configuration

In addition to the PORTx, LATx and TRISx registers for data control, some digital only port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (for example, 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

Refer to "**Pin Diagrams**" for the available pins and their functionality.

#### 11.3 Configuring Analog Port Pins

The ADPCFG and TRISx registers control the operation of the Analog-to-Digital port pins. The port pins that are to function as analog inputs must have their corresponding TRISx bit set (input). If the TRISx bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The ADPCFG and ADPCFG2 registers have a default value of 0x000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORTx register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP. An example is shown in Example 11-1.

## 11.5 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 30 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a Change-of-State.

Four control registers are associated with the Change Notification (CN) module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables an CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin and eliminate the need for external resistors when the push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on Change Notification pins should always be disabled when the port pin is configured as a digital output.

| MOV  | 0xFF00, W0 | Configure PORTB<15:8> as | s inputs |

|------|------------|--------------------------|----------|

| MOV  | W0, TRISBB | and PORTB<7:0> as output | ts       |

| NOP  |            | Delay 1 cycle            |          |

| BTSS | PORTB, #13 | Next Instruction         |          |

|      |            |                          |          |

#### EQUATION 11-1: PORT WRITE/READ EXAMPLE

| R/W-0           | R/W-0                                                                                               | R/W-0                                    | R/W-0                      | R/W-0                 | R/W-0                      | R/W-0                  | R/W-0  |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------|-----------------------|----------------------------|------------------------|--------|--|--|--|--|--|

| PENH            | PENL                                                                                                | POLH                                     | POLL                       | PMOD1 <sup>(1)</sup>  | PMOD0 <sup>(1)</sup>       | OVRENH                 | OVRENL |  |  |  |  |  |

| bit 15          | •                                                                                                   | •                                        | •                          |                       |                            |                        | bit    |  |  |  |  |  |

| R/W-0           | R/W-0                                                                                               | R/W-0                                    | R/W-0                      | R/W-0                 | R/W-0                      | R/W-0                  | R/W-0  |  |  |  |  |  |

| OVRDAT1         | OVRDAT0                                                                                             | FLTDAT1 <sup>(2)</sup>                   | FLTDAT0 <sup>(2)</sup>     | CLDAT1 <sup>(2)</sup> | CLDAT0 <sup>(2)</sup>      | SWAP                   | OSYNC  |  |  |  |  |  |

| bit 7           | orribrito                                                                                           | 1210/111                                 | 1212/110                   | 020/01                | 0LB/110                    | 01114                  | bit    |  |  |  |  |  |

| Legend:         |                                                                                                     |                                          |                            |                       |                            |                        |        |  |  |  |  |  |

| R = Readable    | bit                                                                                                 | W = Writable                             | bit                        | U = Unimplen          | nented bit, read           | as '0'                 |        |  |  |  |  |  |

| -n = Value at I |                                                                                                     | '1' = Bit is set                         |                            | '0' = Bit is clea     |                            | x = Bit is unkn        | iown   |  |  |  |  |  |

|                 | -                                                                                                   |                                          |                            |                       |                            |                        |        |  |  |  |  |  |

| bit 15          |                                                                                                     | xH Output Pin                            |                            |                       |                            |                        |        |  |  |  |  |  |

|                 |                                                                                                     | dule controls P<br>dule controls P       |                            |                       |                            |                        |        |  |  |  |  |  |

| bit 14          |                                                                                                     |                                          | •                          |                       |                            |                        |        |  |  |  |  |  |

| DIL 14          |                                                                                                     | L Output Pin C<br>dule controls P        |                            |                       |                            |                        |        |  |  |  |  |  |

|                 |                                                                                                     |                                          |                            |                       |                            |                        |        |  |  |  |  |  |

| bit 13          | <ul> <li>0 = GPIO module controls PWMxL pin</li> <li>POLH: PWMxH Output Pin Polarity bit</li> </ul> |                                          |                            |                       |                            |                        |        |  |  |  |  |  |

|                 |                                                                                                     | oin is active-low                        |                            |                       |                            |                        |        |  |  |  |  |  |

|                 | -                                                                                                   | oin is active-hig                        |                            |                       |                            |                        |        |  |  |  |  |  |

| pit 12          | POLL: PWMxL Output Pin Polarity bit                                                                 |                                          |                            |                       |                            |                        |        |  |  |  |  |  |

|                 |                                                                                                     | oin is active-low<br>oin is active-hig   |                            |                       |                            |                        |        |  |  |  |  |  |

| bit 11-10       | PMOD<1:0>:                                                                                          | PWM # I/O Pir                            | n Mode bits <sup>(1)</sup> |                       |                            |                        |        |  |  |  |  |  |

|                 |                                                                                                     | D pin pair is in t                       |                            |                       | mode                       |                        |        |  |  |  |  |  |

|                 |                                                                                                     | D pin pair is in t<br>D pin pair is in t |                            |                       |                            |                        |        |  |  |  |  |  |

|                 |                                                                                                     | D pin pair is in t                       |                            |                       | node                       |                        |        |  |  |  |  |  |

| bit 9           | OVRENH: OV                                                                                          | verride Enable                           | for PWMxH Pi               | n bit                 |                            |                        |        |  |  |  |  |  |

|                 | 1 = OVRDAT                                                                                          | <1> provides d                           | ata for output             | on PWMxH pir          | ı                          |                        |        |  |  |  |  |  |

|                 | 0                                                                                                   | nerator provides                         |                            |                       | pin                        |                        |        |  |  |  |  |  |

| bit 8           |                                                                                                     | erride Enable f                          |                            |                       |                            |                        |        |  |  |  |  |  |

|                 |                                                                                                     | <0> provides d<br>nerator provides       |                            |                       |                            |                        |        |  |  |  |  |  |

| bit 7-6         | OVRDAT<1:0                                                                                          | <b>)&gt;:</b> Data for PV                | /MxH, PWMxL                | Pins if Overrie       | de is Enabled b            | its                    |        |  |  |  |  |  |

|                 |                                                                                                     | = 1, OVRDAT<<br>= 1, OVRDAT<             |                            |                       |                            |                        |        |  |  |  |  |  |

| bit 5-4         | FLTDAT<1:0:                                                                                         | >: State for PW                          | MxH and PW                 | MxL Pins if FL1       | MOD is Enable              | ed bits <sup>(2)</sup> |        |  |  |  |  |  |

|                 |                                                                                                     | CLCONx<15>)                              |                            |                       |                            |                        |        |  |  |  |  |  |

|                 |                                                                                                     | ve, then FLTDA<br>ve, then FLTDA         |                            |                       |                            |                        |        |  |  |  |  |  |

|                 |                                                                                                     | ve, then FLIDA<br>CLCONx<15>)            |                            |                       |                            |                        |        |  |  |  |  |  |

|                 |                                                                                                     |                                          |                            |                       | <u>.</u><br>ate for PWMxH. |                        |        |  |  |  |  |  |

|                 |                                                                                                     |                                          | AT<0> provide              |                       |                            |                        |        |  |  |  |  |  |

#### REGISTER 16-19: IOCONX: PWM I/O CONTROL X REGISTER

**Note 1:** These bits should not be changed after the PWM module is enabled (PTEN = 1).

NOTES:

| R/W-0         | R/W-0                                                                                                                         | R/W-0                                                                                        | R/W-0                                                             | R/W-0                              | R/W-0           | R/W-0              | R/W-0  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------|-----------------|--------------------|--------|--|--|--|

| F15BP3        | F15BP2                                                                                                                        | F15BP1                                                                                       | F15BP0                                                            | F14BP3                             | F14BP2          | F14BP1             | F14BP0 |  |  |  |

| bit 15        |                                                                                                                               |                                                                                              |                                                                   |                                    | ·               |                    | bit 8  |  |  |  |

|               |                                                                                                                               |                                                                                              |                                                                   |                                    |                 |                    |        |  |  |  |

| R/W-0         | R/W-0                                                                                                                         | R/W-0                                                                                        | R/W-0                                                             | R/W-0                              | R/W-0           | R/W-0              | R/W-0  |  |  |  |

| F13BP3        | F13BP2                                                                                                                        | F13BP1                                                                                       | F13BP0                                                            | F12BP3                             | F12BP2          | F12BP1             | F12BP0 |  |  |  |

| bit 7         |                                                                                                                               |                                                                                              |                                                                   |                                    |                 |                    | bit 0  |  |  |  |

|               |                                                                                                                               |                                                                                              |                                                                   |                                    |                 |                    |        |  |  |  |

| Legend:       |                                                                                                                               |                                                                                              |                                                                   |                                    |                 |                    |        |  |  |  |

| R = Readab    | le bit                                                                                                                        | W = Writable                                                                                 | bit                                                               | U = Unimplemented bit, read as '0' |                 |                    |        |  |  |  |

| -n = Value at | t POR                                                                                                                         | '1' = Bit is set                                                                             |                                                                   | '0' = Bit is cle                   | ared            | x = Bit is unknown |        |  |  |  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | RX Buffer Ma<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | n RX FIFO but<br>n RX Buffer 14<br>n RX Buffer 1<br>n RX Buffer 0 | ffer<br>1                          |                 |                    |        |  |  |  |

| bit 11-8      | F14BP<3:0>                                                                                                                    | : RX Buffer Ma                                                                               | sk for Filter 14                                                  | l bits (same va                    | lues as bits<15 | :12>)              |        |  |  |  |

| bit 7-4       | F13BP<3:0>                                                                                                                    | : RX Buffer Ma                                                                               | sk for Filter 13                                                  | 3 bits (same va                    | lues as bits<15 | :12>)              |        |  |  |  |

| bit 3-0       | F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits<15:12>)                                                    |                                                                                              |                                                                   |                                    |                 |                    |        |  |  |  |

|               |                                                                                                                               |                                                                                              |                                                                   |                                    |                 |                    |        |  |  |  |

#### REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

| RXFUL7  | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1 | RXFUL0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

#### **REGISTER 21-22: CXRXFUL1: ECANX RECEIVE BUFFER FULL REGISTER 1**

| bit | 7 |  |

|-----|---|--|

|     |   |  |

| Legend:           | C = Writeable, but only '0' can be written to clear the bit |                             |                    |  |

|-------------------|-------------------------------------------------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read | l as '0'           |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty

#### REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writeable, but on | C = Writeable, but only '0' can be written to clear the bit |                    |  |  |

|-------------------|-----------------------|-------------------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit                                       | , read as '0'      |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                                        | x = Bit is unknown |  |  |

bit 15-0 RXFUL<31:16>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty

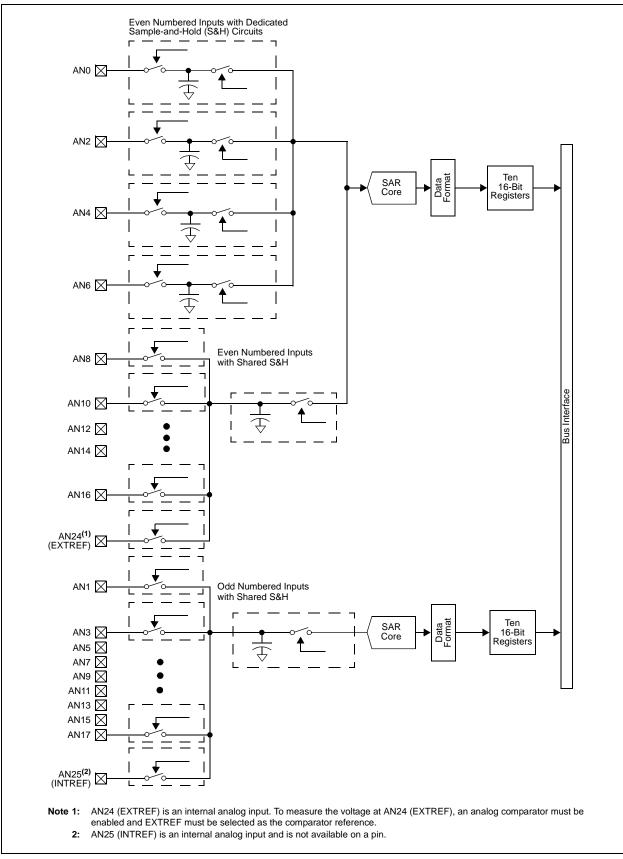

#### FIGURE 22-3: ADC BLOCK DIAGRAM FOR dsPIC33FJ32GS608 AND dsPIC33FJ64GS608 DEVICES WITH TWO SARs

#### REGISTER 22-8: ADCPC2: ADC CONVERT PAIR CONTROL REGISTER 2 (CONTINUED)

| bit 12-8 | TRGSRC5<4:0>: Trigger 5 Source Selection bits                                                          |

|----------|--------------------------------------------------------------------------------------------------------|

|          | Selects trigger source for conversion of Analog Channels AN11 and AN10.                                |

|          | 11111 = Timer2 period match                                                                            |

|          | 11110 = PWM Generator 8 current-limit ADC trigger<br>11101 = PWM Generator 7 current-limit ADC trigger |

|          | 11100 = PWM Generator 6 current-limit ADC trigger                                                      |

|          | 11001 = PWM Generator 5 current-limit ADC trigger                                                      |

|          | 11010 = PWM Generator 4 current-limit ADC trigger                                                      |

|          | 11001 = PWM Generator 3 current-limit ADC trigger                                                      |

|          | 11000 = PWM Generator 2 current-limit ADC trigger                                                      |

|          | 10111 = PWM Generator 1 current-limit ADC trigger                                                      |

|          | 10110 = PWM Generator 9 secondary trigger selected                                                     |

|          | 10101 = PWM Generator 8 secondary trigger selected                                                     |

|          | 10100 = PWM Generator 7 secondary trigger selected                                                     |

|          | 10011 = PWM Generator 6 secondary trigger selected                                                     |

|          | 10010 = PWM Generator 5 secondary trigger selected                                                     |

|          | 10001 = PWM Generator 4 secondary trigger selected                                                     |

|          | 10000 = PWM Generator 3 secondary trigger selected                                                     |

|          | 01111 = PWM Generator 2 secondary trigger selected                                                     |

|          | 01110 = PWM Generator 1 secondary trigger selected                                                     |

|          | 01101 = PWM secondary Special Event Trigger selected                                                   |

|          | 01100 = Timer1 period match                                                                            |

|          | 01011 = PWM Generator 8 primary trigger selected                                                       |

|          | 01010 = PWM Generator 7 primary trigger selected                                                       |

|          | 01001 = PWM Generator 6 primary trigger selected<br>01000 = PWM Generator 5 primary trigger selected   |

|          | 00111 = PWM Generator 4 primary trigger selected                                                       |

|          | 00110 = PWM Generator 3 primary trigger selected                                                       |

|          | 00101 = PWM Generator 2 primary trigger selected                                                       |

|          | 00100 = PWM Generator 1 primary trigger selected                                                       |

|          | 00011 = PWM Special Event Trigger selected                                                             |

|          | 00010 = Global software trigger selected                                                               |

|          | 00001 = Individual software trigger selected                                                           |

|          | 00000 = No conversion is enabled                                                                       |

| bit 7    | IRQEN4: Interrupt Request Enable 4 bit                                                                 |

|          | 1 = Enables IRQ generation when requested conversion of Channels AN9 and AN8 is completed              |

|          | 0 = IRQ is not generated                                                                               |

| bit 6    | PEND4: Pending Conversion Status 4 bit                                                                 |

|          | 1 = Conversion of Channels AN9 and AN8 is pending; set when selected trigger is asserted               |

|          | 0 = Conversion is complete                                                                             |

| bit 5    | SWTRG4: Software Trigger 4 bit                                                                         |

|          | 1 = Starts conversion of AN9 and AN8 (if selected by the TRGSRCx<4:0> bits) <sup>(1)</sup>             |

|          | This bit is automatically cleared by hardware when the PEND4 bit is set.                               |

|          | 0 = Conversion has not started                                                                         |

|          |                                                                                                        |

**Note 1:** The trigger source must be set as an individual software trigger prior to setting this bit to '1'. If other conversions are in progress, the conversion is performed when the conversion resources are available.

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| R/W-0            | R/W-0                                                                                                                                              | R/W-0                         | R/W-0                     | R/W-0                              | R/W-0                           | R/W-0              | R/W-0        |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------|------------------------------------|---------------------------------|--------------------|--------------|--|--|

| IRQEN7           | PEND7                                                                                                                                              | SWTRG7                        | TRGSRC74                  | TRGSRC73                           | TRGSRC72                        | TRGSRC71           | TRGSRC70     |  |  |

| bit 15           |                                                                                                                                                    |                               |                           |                                    |                                 |                    | bit 8        |  |  |

|                  |                                                                                                                                                    |                               |                           |                                    |                                 |                    |              |  |  |

| R/W-0            | R/W-0                                                                                                                                              | R/W-0                         | R/W-0                     | R/W-0                              | R/W-0                           | R/W-0              | R/W-0        |  |  |

| IRQEN6           | PEND6                                                                                                                                              | SWTRG6                        | TRGSRC64                  | TRGSRC63                           | TRGSRC62                        | TRGSRC61           | TRGSRC60     |  |  |

| bit 7            |                                                                                                                                                    |                               |                           |                                    |                                 |                    | bit 0        |  |  |

|                  |                                                                                                                                                    |                               |                           |                                    |                                 |                    |              |  |  |

| Legend:          |                                                                                                                                                    |                               |                           |                                    |                                 |                    |              |  |  |

| R = Readable bit |                                                                                                                                                    | W = Writable bit              |                           | U = Unimplemented bit, read as '0' |                                 |                    |              |  |  |

| -n = Value at    | POR                                                                                                                                                | '1' = Bit is set              |                           | '0' = Bit is cleared               |                                 | x = Bit is unknown |              |  |  |

|                  |                                                                                                                                                    |                               |                           |                                    |                                 |                    |              |  |  |

| bit 15           | IRQEN7: Inte                                                                                                                                       | errupt Request                | Enable 7 bit              |                                    |                                 |                    |              |  |  |

|                  | 1 = Enables I<br>0 = IRQ is no                                                                                                                     | •                             | when request              | ed conversion                      | of Channels Al                  | N15 and AN14       | is completed |  |  |

| bit 14           | PEND7: Pen                                                                                                                                         | ding Conversio                | n Status 7 bit            |                                    |                                 |                    |              |  |  |

|                  | <ul> <li>1 = Conversion of Channels AN15 and AN14 is pending; set when selected trigger is asserted</li> <li>0 = Conversion is complete</li> </ul> |                               |                           |                                    |                                 | sserted            |              |  |  |

| bit 13           | SWTRG7: So                                                                                                                                         | WTRG7: Software Trigger 7 bit |                           |                                    |                                 |                    |              |  |  |

|                  | 1 = Starts co<br>This bit i                                                                                                                        | nversion of AN                | 15 and AN14 cleared by ha | •                                  | the TRGSRCx<<br>he PEND7 bit is | ,                  |              |  |  |

#### REGISTER 22-9: ADCPC3: ADC CONVERT PAIR CONTROL REGISTER 3

**Note 1:** The trigger source must be set as an individual software trigger prior to setting this bit to '1'. If other conversions are in progress, the conversion is performed when the conversion resources are available.

#### **REGISTER 22-11: ADCPC5: ADC CONVERT PAIR CONTROL REGISTER 5 (CONTINUED)**

| bit 4-0 | <b>TRGSRC10&lt;4:0&gt;:</b> Trigger 10 Source Selection bits<br>Selects trigger source for conversion of analog channels AN21 and AN20.<br>11111 = Timer2 period match |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11110 = PWM Generator 8 current-limit ADC trigger                                                                                                                      |

|         | 11101 = PWM Generator 7 current-limit ADC trigger                                                                                                                      |

|         | 11100 = PWM Generator 6 current-limit ADC trigger                                                                                                                      |

|         | 11011 = PWM Generator 5 current-limit ADC trigger                                                                                                                      |

|         | 11010 = PWM Generator 4 current-limit ADC trigger                                                                                                                      |

|         | 11001 = PWM Generator 3 current-limit ADC trigger                                                                                                                      |

|         | 11000 = PWM Generator 2 current-limit ADC trigger                                                                                                                      |

|         | 10111 = PWM Generator 1 current-limit ADC trigger                                                                                                                      |

|         | 10110 = PWM Generator 9 secondary trigger selected                                                                                                                     |

|         | 10101 = PWM Generator 8 secondary trigger selected                                                                                                                     |

|         | 10100 = PWM Generator 7 secondary trigger selected                                                                                                                     |

|         | 10011 = PWM Generator 6 secondary trigger selected                                                                                                                     |

|         | 10010 = PWM Generator 5 secondary trigger selected                                                                                                                     |

|         | 10001 = PWM Generator 4 secondary trigger selected                                                                                                                     |

|         | 10000 = PWM Generator 3 secondary trigger selected                                                                                                                     |

|         | 01111 = PWM Generator 2 secondary trigger selected                                                                                                                     |

|         | 01110 = PWM Generator 1 secondary trigger selected                                                                                                                     |

|         | 01101 = PWM secondary Special Event Trigger selected                                                                                                                   |

|         | 01100 = Timer1 period match                                                                                                                                            |

|         | 01011 = PWM Generator 8 primary trigger selected                                                                                                                       |