Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

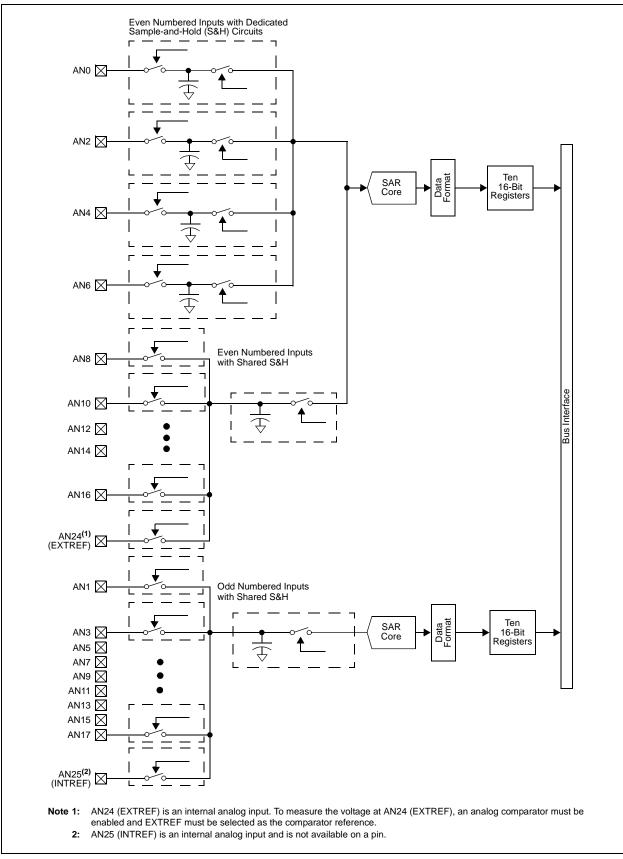

| Data Converters            | A/D 24x10b; D/A 1x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs610-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/ PIC24 Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33/PIC24 Family Reference Manual sections. The information in this data sheet supersedes the information in the FRM.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ32GS406/606/ 608/610 and dsPIC33FJ64GS406/606/608/610 family of 16-bit Digital Signal Controllers (DSC) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors")

- VCAP (see Section 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins"**)

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

# TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ32GS608/610 AND dsPIC33FJ64GS608/610 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3         | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------|---------|---------|---------------|---------|---------|---------|---------------|

| CNEN1        | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE         | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2        | 0062        | _       | _       | _       | _       | _       | _       | _      | _      | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE        | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1        | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | <b>CN3PUE</b> | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2        | 006A        | —       | _       | _       | _       | _       | _       | -      |        | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE       | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ32GS406/606 AND dsPIC33FJ64GS406/606 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------|--------|--------|--------|---------|---------|---------|---------------|

| CNEN1        | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE   | CN6IE   | CN5IE  | CN4IE  | CN3IE  | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2        | 0062        | _       | -       | _       | -       | -       |         |        | _      | CN23IE  | CN22IE  | _      |        | -      | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1        | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE  | CN6PUE  | CN5PUE | CN4PUE | CN3PUE | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2        | 006A        | —       | _       | _       | _       | _       | _       | _      | _      | CN23PUE | CN22PUE | _      | _      | _      | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: HIGH-SPEED PWM GENERATOR 2 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12       | Bit 11    | Bit 10        | Bit 9     | Bit 8     | Bit 7    | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|---------|---------|---------|--------------|-----------|---------------|-----------|-----------|----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON2      | 0440        | FLTSTAT | CLSTAT  | TRGSTAT | FLTIEN       | CLIEN     | TRGIEN        | ITB       | MDCS      | DTC1     | DTC0    | DTCP     |          | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON2       | 0442        | PENH    | PENL    | POLH    | POLL         | PMOD1     | PMOD0         | OVRENH    | OVRENL    | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON2      | 0444        | IFLTMOD | CLSRC4  | CLSRC3  | CLSRC2       | CLSRC1    | CLSRC0        | CLPOL     | CLMOD     | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC2         | 0446        |         |         |         |              |           |               |           | PDC2      | 2<15:0>  |         |          |          |          |          |          |          | 0000          |

| PHASE2       | 0448        |         |         |         | PHASE2<15:0> |           |               |           |           |          |         | 0000     |          |          |          |          |          |               |

| DTR2         | 044A        | _       | _       |         |              |           |               |           |           | DTR2     | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR2      | 044C        | _       | _       |         |              |           | ALTDTR2<13:0> |           |           |          |         |          |          | 0000     |          |          |          |               |

| SDC2         | 044E        |         |         |         |              |           | SDC2<15:0>    |           |           |          |         |          |          |          |          |          | 0000     |               |

| SPHASE2      | 0450        |         |         |         |              |           |               |           | SPHAS     | E2<15:0> |         |          |          |          |          |          |          | 0000          |

| TRIG2        | 0452        |         |         |         |              |           |               | TRGCMP<12 | 2:0>      |          |         |          |          |          | _        | _        | —        | 0000          |

| TRGCON2      | 0454        | TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0      | _         | _             | —         | _         | DTM      | _       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG2       | 0456        |         |         |         |              |           |               | STRGCMP<1 | 2:0>      |          |         |          |          |          | _        | _        | —        | 0000          |

| PWMCAP2      | 0458        |         |         |         |              |           |               | PWMCAP<1  | 2:0>      |          |         |          |          |          | _        | _        | —        | 0000          |

| LEBCON2      | 045A        | PHR     | PHF     | PLR     | PLF          | FLTLEBEN  | CLLEBEN       | _         | _         | _        | _       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY2      | 045C        | _       | _       | _       | —            | •         |               |           | L         | EB<8:0>  | •       |          |          | -        |          |          |          | 0000          |

| AUXCON2      | 045E        | HRPDIS  | HRDDIS  | _       | _            | BLANKSEL3 | BLANKSEL2     | BLANKSEL1 | BLANKSEL0 | _        | —       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4      | +-35.       |        | H-OF L                  |        |          | C REGIS  |          | AF FUR   | USFICS   | DFJJZ(      | 55400 | AND us  | SPIC33FJ  | 9463400  |          | 3        |           |               |

|--------------|-------------|--------|-------------------------|--------|----------|----------|----------|----------|----------|-------------|-------|---------|-----------|----------|----------|----------|-----------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                  | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6 | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0     | All<br>Resets |

| ADCON        | 0300        | ADON   | -                       | ADSIDL | SLOWCLK  | _        | GSWTRG   |          | FORM     | EIE         | ORDER | SEQSAMP | ASYNCSAMP | —        | ADCS2    | ADCS1    | ADCS0     | 0003          |

| ADPCFG       | 0302        |        |                         |        |          |          |          |          | PC       | FG<15:0>    |       |         |           |          |          |          |           | 0000          |

| ADSTAT       | 0306        | —      | _                       | _      | P12RDY   | _        | _        | _        | —        | P7RDY       | P6RDY | P5RDY   | P4RDY     | P3RDY    | P2RDY    | P1RDY    | PORDY     | 0000          |

| ADBASE       | 0308        |        |                         |        |          |          |          |          | ADBASE<1 | 5:1>        |       |         |           |          |          |          | —         | 0000          |

| ADCPC0       | 030A        | IRQEN1 | PEND1                   | SWTRG1 | TRGSRC14 | TRGSRC13 | TRGSRC12 | TRGSRC11 | TRGSRC10 | IRQEN0      | PEND0 | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00  | 0000          |

| ADCPC1       | 030C        | IRQEN3 | PEND3                   | SWTRG3 | TRGSRC34 | TRGSRC33 | TRGSRC32 | TRGSRC31 | TRGSRC30 | IRQEN2      | PEND2 | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20  | 0000          |

| ADCPC2       | 030E        | IRQEN5 | PEND5                   | SWTRG5 | TRGSRC54 | TRGSRC53 | TRGSRC52 | TRGSRC51 | TRGSRC50 | IRQEN4      | PEND4 | SWTRG4  | TRGSRC44  | TRGSRC43 | TRGSRC42 | TRGSRC41 | TRGSRC40  | 0000          |

| ADCPC3       | 0310        | IRQEN7 | PEND7                   | SWTRG7 | TRGSRC74 | TRGSRC73 | TRGSRC72 | TRGSRC71 | TRGSRC70 | IRQEN6      | PEND6 | SWTRG6  | TRGSRC64  | TRGSRC63 | TRGSRC62 | TRGSRC61 | TRGSRC640 | 0000          |

| ADCBUF0      | 0340        |        |                         |        |          |          |          |          | ADC I    | Data Buffer | 0     |         |           |          |          |          |           | xxxx          |

| ADCBUF1      | 0342        |        | ADC Data Buffer 1 xxxx  |        |          |          |          |          |          |             | xxxx  |         |           |          |          |          |           |               |

| ADCBUF2      | 0344        |        | ADC Data Buffer 2 xxxx  |        |          |          |          |          |          |             |       |         | xxxx      |          |          |          |           |               |

| ADCBUF3      | 0346        |        |                         |        |          |          |          |          | ADC I    | Data Buffer | 3     |         |           |          |          |          |           | xxxx          |

| ADCBUF4      | 0348        |        |                         |        |          |          |          |          | ADC I    | Data Buffer | 4     |         |           |          |          |          |           | xxxx          |

| ADCBUF5      | 034A        |        |                         |        |          |          |          |          | ADC I    | Data Buffer | 5     |         |           |          |          |          |           | xxxx          |

| ADCBUF6      | 034C        |        |                         |        |          |          |          |          | ADC I    | Data Buffer | 6     |         |           |          |          |          |           | xxxx          |

| ADCBUF7      | 034E        |        |                         |        |          |          |          |          | ADC I    | Data Buffer | 7     |         |           |          |          |          |           | xxxx          |

| ADCBUF8      | 0350        |        |                         |        |          |          |          |          | ADC I    | Data Buffer | 8     |         |           |          |          |          |           | xxxx          |

| ADCBUF9      | 0352        |        |                         |        |          |          |          |          | ADC I    | Data Buffer | 9     |         |           |          |          |          |           | xxxx          |

| ADCBUF10     | 0354        |        |                         |        |          |          |          |          | ADC D    | Data Buffer | 10    |         |           |          |          |          |           | xxxx          |

| ADCBUF11     | 0356        |        | ADC Data Buffer 11 xxxx |        |          |          |          |          |          |             |       |         |           |          |          |          |           |               |

| ADCBUF12     | 0358        |        | ADC Data Buffer 12 xxxx |        |          |          |          |          |          |             |       | xxxx    |           |          |          |          |           |               |

| ADCBUF13     | 035A        |        | ADC Data Buffer 13 xxxx |        |          |          |          |          |          |             |       | xxxx    |           |          |          |          |           |               |

| ADCBUF14     | 035C        |        |                         |        |          |          |          |          | ADC D    | ata Buffer  | 14    |         |           |          |          |          |           | xxxx          |

| ADCBUF15     | 035E        |        | ADC Data Buffer 15 xxxx |        |          |          |          |          |          |             |       | xxxx    |           |          |          |          |           |               |

#### TABLE 4-35: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ32GS406 AND dsPIC33FJ64GS406 DEVICES

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 4.4 Modulo Addressing

Modulo Addressing mode is a method used to provide an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Υ   | Space       | Modulo      | Addressing   | EA   |

|-------|-----|-------------|-------------|--------------|------|

|       | cal | culations   | assume      | word-sized   | data |

|       | (LS | Sb of every | / EA is alw | /ays clear). |      |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

# 4.4.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that will operate with Modulo Addressing:

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

#### MOV #0x1100, W0 Byte W0, XMODSRT MOV ;set modulo start address Address MOV #0x1163. W0 MOV W0, MODEND ;set modulo end address 0x1100 MOV #0x8001, W0 MOV W0, MODCON ;enable W1, X AGU for modulo MOV #0x0000, W0 ;W0 holds buffer fill value MOV #0x1110, W1 ;point W1 to buffer 0x1163 DO AGAIN, #0x31 ;fill the 50 buffer locations MOV WO, [W1++] ;fill the next location AGAIN: INC W0, W0 ; increment the fill value Start Addr = 0x1100End Addr = 0x1163Length = 0x0032 Words

#### FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| U-0           | U-0           | U-0              | U-0              | U-0              | R/W-1           | R/W-0           | R/W-0  |

|---------------|---------------|------------------|------------------|------------------|-----------------|-----------------|--------|

| _             | —             | —                | —                | —                | U2EIP2          | U2EIP1          | U2EIP0 |

| bit 15        | ·             |                  |                  |                  |                 |                 | bit 8  |

|               |               |                  |                  |                  |                 |                 |        |

| U-0           | R/W-1         | R/W-0            | R/W-0            | U-0              | U-0             | U-0             | U-0    |

| _             | U1EIP2        | U1EIP1           | U1EIP0           | —                | _               | —               | —      |

| bit 7         |               |                  |                  |                  |                 |                 | bit C  |

|               |               |                  |                  |                  |                 |                 |        |

| Legend:       |               |                  |                  |                  |                 |                 |        |

| R = Readable  | e bit         | W = Writable     | bit              | U = Unimple      | mented bit, rea | d as '0'        |        |

| -n = Value at | POR           | '1' = Bit is set | t                | '0' = Bit is cle | eared           | x = Bit is unkr | nown   |

|               |               |                  |                  |                  |                 |                 |        |

| bit 15-11     | Unimplemen    | ted: Read as '   | 0'               |                  |                 |                 |        |

| bit 10-8      | U2EIP<2:0>:   | UART2 Error      | Interrupt Priori | ty bits          |                 |                 |        |

|               | 111 = Interru | pt is Priority 7 | (highest priorit | y interrupt)     |                 |                 |        |

|               | •             |                  |                  |                  |                 |                 |        |

|               | •             |                  |                  |                  |                 |                 |        |

|               | 001 = Interru | pt is Priority 1 |                  |                  |                 |                 |        |

|               |               | pt source is dis | sabled           |                  |                 |                 |        |

| bit 7         | Unimplemen    | ted: Read as '   | 0'               |                  |                 |                 |        |

| bit 6-4       | U1EIP<2:0>:   | UART1 Error      | Interrupt Priori | ty bits          |                 |                 |        |

|               | 111 = Interru | pt is Priority 7 | (highest priorit | y interrupt)     |                 |                 |        |

|               | •             |                  |                  |                  |                 |                 |        |

|               | •             |                  |                  |                  |                 |                 |        |

|               | 001 = Interru | pt is Priority 1 |                  |                  |                 |                 |        |

|               |               | pt source is dis | sabled           |                  |                 |                 |        |

| bit 3-0       | Unimplemen    | ted: Read as '   | 0'               |                  |                 |                 |        |

|               |               |                  |                  |                  |                 |                 |        |

### REGISTER 7-34: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| R/W-0         | R/W-0        | R/W-0                               | R/W-0   | R/W-0             | R/W-0           | R/W-0                | U-0   |

|---------------|--------------|-------------------------------------|---------|-------------------|-----------------|----------------------|-------|

| T5MD          | T4MD         | T3MD                                | T2MD    | T1MD              | QEI1MD          | PWMMD <sup>(1)</sup> | _     |

| bit 15        |              |                                     |         |                   |                 |                      | bit   |

|               |              |                                     |         |                   |                 |                      |       |

| R/W-0         | R/W-0        | R/W-0                               | R/W-0   | R/W-0             | U-0             | R/W-0                | R/W-0 |

| I2C1MD        | U2MD         | U1MD                                | SPI2MD  | SPI1MD            | —               | C1MD                 | ADCMD |

| bit 7         |              |                                     |         |                   |                 |                      | bit   |

| Legend:       |              |                                     |         |                   |                 |                      |       |

| R = Readabl   | le bit       | W = Writable                        | bit     | U = Unimplem      | nented bit, rea | d as '0'             |       |

| -n = Value at | t POR        | '1' = Bit is set                    |         | '0' = Bit is clea | ared            | x = Bit is unkno     | own   |

|               |              |                                     |         |                   |                 |                      |       |

| bit 15        | T5MD: Timer  | 5 Module Disal                      | ole bit |                   |                 |                      |       |

|               |              | odule is disable                    |         |                   |                 |                      |       |

|               |              | odule is enable                     |         |                   |                 |                      |       |

| bit 14        |              | 4 Module Disal                      |         |                   |                 |                      |       |

|               |              | odule is disable<br>odule is enable |         |                   |                 |                      |       |

| bit 13        |              | 3 Module Disat                      |         |                   |                 |                      |       |

|               |              | odule is disable                    |         |                   |                 |                      |       |

|               | 0 = Timer3 m | odule is enable                     | ed      |                   |                 |                      |       |

| bit 12        | T2MD: Timer  | 2 Module Disat                      | ole bit |                   |                 |                      |       |

|               |              | odule is disable<br>odule is enable |         |                   |                 |                      |       |

| bit 11        | T1MD: Timer  | 1 Module Disat                      | ole bit |                   |                 |                      |       |

|               |              | odule is disable<br>odule is enable |         |                   |                 |                      |       |

| bit 10        | QEI1MD: QE   | I1 Module Disa                      | ble bit |                   |                 |                      |       |

|               |              | dule is disabled                    |         |                   |                 |                      |       |

|               |              | dule is enabled                     | (1)     |                   |                 |                      |       |

| bit 9         |              | /M Module Disa                      |         |                   |                 |                      |       |

|               |              | dule is disabled<br>dule is enabled |         |                   |                 |                      |       |

| bit 8         | Unimplemen   | ted: Read as '                      | 0'      |                   |                 |                      |       |

| bit 7         | 12C1MD: 12C  | 1 Module Disat                      | ole bit |                   |                 |                      |       |

|               |              | lule is disabled<br>lule is enabled |         |                   |                 |                      |       |

| bit 6         | U2MD: UART   | 2 Module Disa                       | ble bit |                   |                 |                      |       |

|               | -            | odule is disabl<br>odule is enable  |         |                   |                 |                      |       |

| bit 5         | U1MD: UART   | 1 Module Disa                       | ble bit |                   |                 |                      |       |

|               |              | odule is disabl<br>odule is enable  |         |                   |                 |                      |       |

| bit 4         |              | 2 Module Disa                       |         |                   |                 |                      |       |

| -             | 1 = SPI2 mod | lule is disabled                    |         |                   |                 |                      |       |

# REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** Once the PWM module is re-enabled (PWMMD is set to '1' and then set to '0'), all PWM registers must be re-initialized.

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| U-0          | U-0          | U-0                                 | U-0            | U-0               | R/W-0            | U-0              | U-0   |

|--------------|--------------|-------------------------------------|----------------|-------------------|------------------|------------------|-------|

| —            | —            | —                                   | —              | —                 | CMPMD            | —                | —     |

| bit 15       |              |                                     |                |                   |                  |                  | bit 8 |

|              |              |                                     |                |                   |                  |                  |       |

| U-0          | U-0          | R/W-0                               | U-0            | U-0               | U-0              | R/W-0            | U-0   |

| —            | —            | QEI2MD                              |                | —                 | —                | I2C2MD           | —     |

| bit 7        |              |                                     |                |                   |                  |                  | bit 0 |

|              |              |                                     |                |                   |                  |                  |       |

| Legend:      |              |                                     |                |                   |                  |                  |       |

| R = Readab   | le bit       | W = Writable                        | bit            | U = Unimplen      | nented bit, read | d as '0'         |       |

| -n = Value a | t POR        | '1' = Bit is set                    |                | '0' = Bit is clea | ared             | x = Bit is unkno | own   |

|              |              |                                     |                |                   |                  |                  |       |

| bit 15-11    | Unimplemen   | ted: Read as '                      | כ'             |                   |                  |                  |       |

| bit 10       | CMPMD: Ana   | alog Comparato                      | or Module Disa | ble bit           |                  |                  |       |

|              |              | omparator mode                      |                |                   |                  |                  |       |

| bit 9-6      | Unimplemen   | ted: Read as '                      | )'             |                   |                  |                  |       |

| bit 5        | QEI2MD: QE   | I2 Module Disa                      | ble bit        |                   |                  |                  |       |

|              |              | dule is disabled<br>dule is enabled |                |                   |                  |                  |       |

| bit 4-2      | Unimplemen   | ted: Read as '                      | )'             |                   |                  |                  |       |

| bit 1        | -            | 2 Module Disab                      |                |                   |                  |                  |       |

|              | 1 = I2C2 mod | lule is disabled                    |                |                   |                  |                  |       |

|              | 0 = I2C2 mod | lule is enabled                     |                |                   |                  |                  |       |

| bit 0        | Unimplemen   | ted: Read as '                      | )'             |                   |                  |                  |       |

|              |              |                                     |                |                   |                  |                  |       |

# REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

#### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0        | U-0                                                                     | U-0                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                     | U-0                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| —          | —                                                                       | —                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            |                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| U-0        | U-0                                                                     | U-0                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| —          | —                                                                       | _                                                                                                                                                                  | REFOMD                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ·          | •                                                                       |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| e bit      | W = Writable I                                                          | oit                                                                                                                                                                | U = Unimplem                                                                                                                                                                                                                                                                                                                                                            | nented bit, read                                                                                                                                                                                                                                                                                                            | l as '0'                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| POR        | '1' = Bit is set                                                        |                                                                                                                                                                    | '0' = Bit is clea                                                                                                                                                                                                                                                                                                                                                       | ared                                                                                                                                                                                                                                                                                                                        | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                            | nown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |