Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10b; D/A 1x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs610-i-pt |

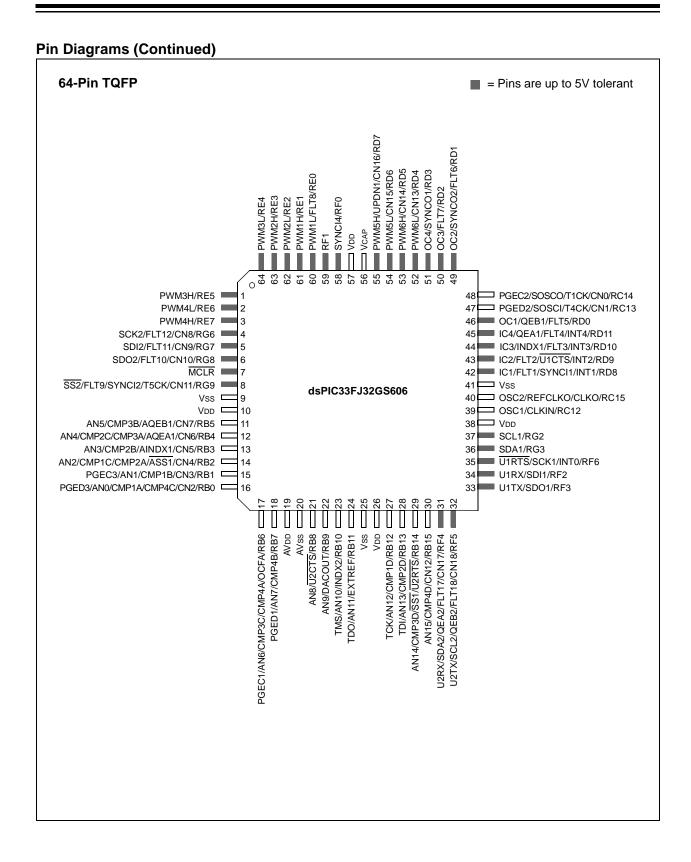

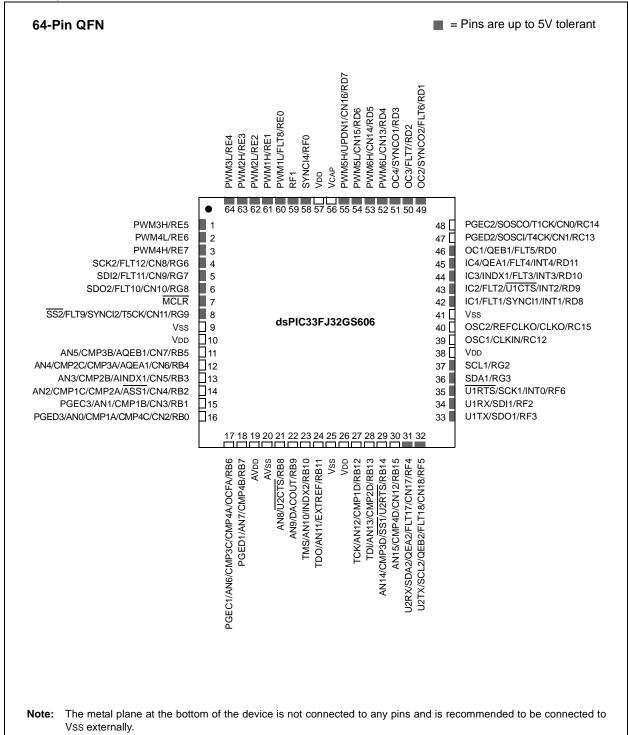

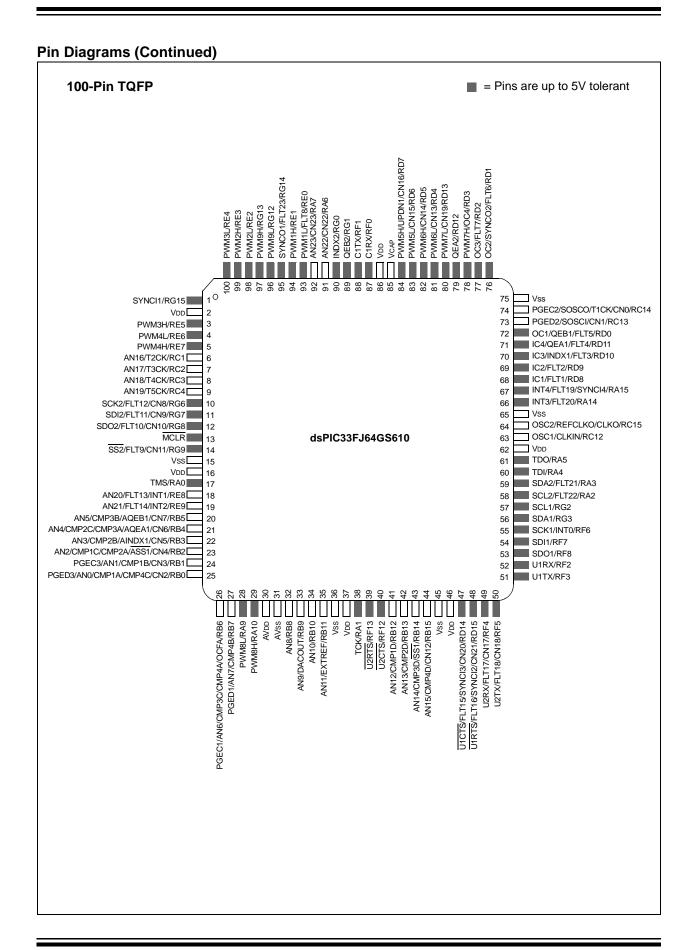

# Pin Diagrams (Continued)

#### **TABLE 4-1: CPU CORE REGISTER MAP (CONTINUED)**

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8         | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|------------|---------------|----------|-------|-------|--------|-------|-------|-------|-------|---------------|

| CORCON       | 0044        | _      | _      | _      | US     | EDT    | DL2    | DL1        | DL0           | SATA     | SATB  | SATDW | ACCSAT | IPL3  | PSV   | RND   | IF    | 0000          |

| MODCON       | 0046        | XMODEN | YMODEN | -      | 1      | BWM3   | BWM2   | BWM1       | BWM0          | YWM3     | YWM2  | YWM1  | YWM0   | XWM3  | XWM2  | XWM1  | XWM0  | 0000          |

| XMODSRT      | 0048        |        |        |        |        |        | X      | (S<15:1>   |               |          |       |       |        |       |       |       | 0     | xxxx          |

| XMODEND      | 004A        |        |        |        |        |        | X      | (E<15:1>   |               |          |       |       |        |       |       |       | 1     | xxxx          |

| YMODSRT      | 004C        |        |        |        |        |        | Y      | ′S<15:1>   |               |          |       |       |        |       |       |       | 0     | xxxx          |

| YMODEND      | 004E        |        |        |        |        |        | Y      | ′E<15:1>   |               |          |       |       |        |       |       |       | 1     | xxxx          |

| XBREV        | 0050        | BREN   | XB14   | XB13   | XB12   | XB11   | XB10   | XB9        | XB8           | XB7      | XB6   | XB5   | XB4    | XB3   | XB2   | XB1   | XB0   | xxxx          |

| DISICNT      | 0052        |        | _      |        |        |        |        | Disable II | nterrupts Cou | nter Reg | ister |       |        | •     |       | •     |       | xxxx          |

dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-22: HIGH-SPEED PWM GENERATOR 6 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9      | Bit 8     | Bit 7     | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|---------|---------|---------|---------|-----------|-----------|------------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON6      | 04C0        | FLTSTAT | CLSTAT  | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB        | MDCS      | DTC1      | DTC0     | DTCP     | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON6       | 04C2        | PENH    | PENL    | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH     | OVRENL    | OVRDAT1   | OVRDAT0  | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON6      | 04C4        | IFLTMOD | CLSRC4  | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL      | CLMOD     | FLTSRC4   | FLTSRC3  | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC6         | 04C6        |         |         |         |         |           |           |            | PDC       | 6<15:0>   |          |          |          |          |          |          |          | 0000          |

| PHASE6       | 04C8        |         |         |         |         |           |           |            | PHAS      | E6<15:0>  |          |          |          |          |          |          |          | 0000          |

| DTR6         | 04CA        | -       | _       |         |         |           |           |            |           | DTR6      | S<13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR6      | 04CA        | 1       | I       |         |         |           |           |            |           | ALTDTF    | R6<13:0> |          |          |          |          |          |          | 0000          |

| SDC6         | 04CE        |         |         |         |         |           |           |            | SDC       | 6<15:0>   |          |          |          |          |          |          |          | 0000          |

| SPHASE6      | 04D0        |         |         |         |         |           |           |            | SPHAS     | SE6<15:0> |          |          |          |          |          |          |          | 0000          |

| TRIG6        | 04D2        |         |         |         |         |           |           | TRGCMP<12  | :0>       |           |          |          |          |          | _        | I        | _        | 0000          |

| TRGCON6      | 04D4        | TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 | _         | 1         | I          | I         | DTM       | _        | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG6       | 04D6        |         |         |         |         |           | ;         | STRGCMP<12 | 2:0>      |           |          |          |          |          | _        | I        | _        | 0000          |

| PWMCAP6      | 04D8        |         |         |         |         |           |           | PWMCAP<12  | :0>       |           |          |          |          |          | _        | _        | _        | 0000          |

| LEBCON6      | 04DA        | PHR     | PHF     | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | ı          | ı         | _         | _        | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY6      | 04DC        | _       | -       | _       | _       |           | •         | •          | L         | EB<8:0>   |          | •        |          |          | _        | ı        | _        | 0000          |

| AUXCON6      | 04DE        | HRPDIS  | HRDDIS  | _       | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1  | BLANKSEL0 | _         | _        | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-30: SPI1 REGISTER MAP

| File Name | SFR<br>Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8      | Bit 7      | Bit 6       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-----------|--------------|--------|--------|---------|--------|--------|--------|-----------|------------|------------|-------------|-------|-------|-------|-------|--------|--------|---------------|

| SPI1STAT  | 0240         | SPIEN  | _      | SPISIDL |        | ı      | _      | _         | ı          |            | SPIROV      | ı     | _     |       |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1  | 0242         | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP       | CKE        | SSEN       | CKP         | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000          |

| SPI1CON2  | 0244         | FRMEN  | SPIFSD | FRMPOL  | _      | -      | _      | _         | -          | -          | _           | -     | _     | _     |       | FRMDLY | _      | 0000          |

| SPI1BUF   | 0248         |        |        |         |        |        |        | SPI1 Tran | smit and R | eceive Buf | fer Registe | r     |       |       |       | •      |        | 0000          |

$\textbf{Legend:} \quad x = \text{unknown value on Reset,} \\ \textbf{--} = \text{unimplemented, read as '0'}. \\ \textbf{Reset values are shown in hexadecimal.}$

## TABLE 4-31: SPI2 REGISTER MAP

| File Name | SFR<br>Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8       | Bit 7       | Bit 6       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-----------|--------------|--------|--------|---------|--------|--------|--------|----------|-------------|-------------|-------------|-------|-------|-------|-------|--------|--------|---------------|

| SPI2STAT  | 0260         | SPIEN  | _      | SPISIDL | _      | _      | _      | _        | _           | _           | SPIROV      | _     | _     | _     | _     | SPITBF | SPIRBF | 0000          |

| SPI2CON1  | 0262         | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP      | CKE         | SSEN        | CKP         | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000          |

| SPI2CON2  | 0264         | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _      | _        | _           | _           | _           | _     | _     | _     | _     | FRMDLY | _      | 0000          |

| SPI2BUF   | 0268         |        |        |         |        |        |        | SPI2 Tra | nsmit and F | Receive But | fer Registe | r     |       |       |       |        |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 6.2 Power-on Reset (POR)

A Power-on Reset (POR) circuit ensures the device is reset from power-on. The POR circuit is active until VDD crosses the VPOR threshold and the delay, TPOR, has elapsed. The delay, TPOR, ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 27.0 "Electrical Characteristics" for details.

The Power-on Reset (POR) status bit in the Reset Control (RCON<0>) register is set to indicate the Power-on Reset.

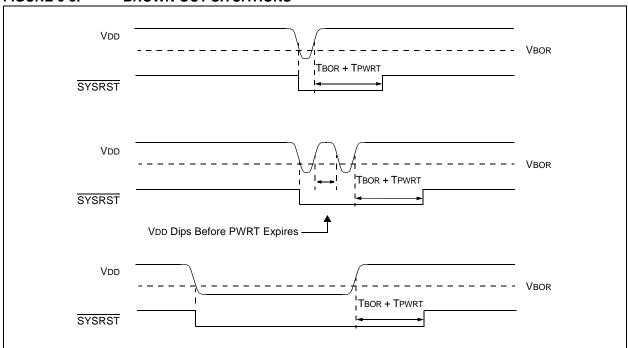

# 6.3 Brown-out Reset (BOR) and Power-up Timer (PWRT)

The on-chip regulator has a Brown-out Reset (BOR) circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses the

VBOR threshold and the delay, TBOR, has elapsed. The delay, TBOR, ensures the voltage regulator output becomes stable.

The Brown-out Reset (BOR) status bit in the Reset Control (RCON<1>) register is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides a Power-up Time Delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The Power-up Timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select (FPWRT<2:0>) bits in the FPOR Configuration (FPOR<2:0>) register, which provides eight settings (from 0 ms to 128 ms). Refer to **Section 24.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The Reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point

FIGURE 6-3: BROWN-OUT SITUATIONS

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|--------|---------|---------|-------|-------|-------|

| NSTDIS | OVAERR | OVBERR | COVAERR | COVBERR | OVATE | OVBTE | COVTE |

| bit 15 |        |        |         |         |       |       | bit 8 |

| R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|----------|---------|---------|---------|---------|--------|---------|-------|

| SFTACERR | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL | _     |

| bit 7    |         |         |         |         |        |         | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **NSTDIS:** Interrupt Nesting Disable bit

1 = Interrupt nesting is disabled

0 = Interrupt nesting is enabled

bit 14 OVAERR: Accumulator A Overflow Trap Flag bit

1 = Trap was rate says and overflow of Accumulator A

0 = Trap was not caused by an overflow of Accumulator A

bit 13 **OVBERR:** Accumulator B Overflow Trap Flag bit

1 = Trap was caused by an overflow of Accumulator B

0 = Trap was not caused by an overflow of Accumulator B

bit 12 COVAERR: Accumulator A Catastrophic Overflow Trap Flag bit

1 = Trap was caused by a catastrophic overflow of Accumulator A

0 = Trap was not caused by a catastrophic overflow of Accumulator A

bit 11 COVBERR: Accumulator B Catastrophic Overflow Trap Flag bit

1 = Trap was caused by a catastrophic overflow of Accumulator B

0 = Trap was not caused by a catastrophic overflow of Accumulator B

bit 10 OVATE: Accumulator A Overflow Trap Enable bit

1 = Trap overflow of Accumulator A

0 = Trap is disabled

bit 9 **OVBTE:** Accumulator B Overflow Trap Enable bit

1 = Trap overflow of Accumulator B

0 = Trap is disabled

bit 8 **COVTE:** Catastrophic Overflow Trap Enable bit

1 = Trap on a catastrophic overflow of Accumulator A or B is enabled

0 = Trap is disabled

bit 7 SFTACERR: Shift Accumulator Error Status bit

1 = Math error trap was caused by an invalid accumulator shift

0 = Math error trap was not caused by an invalid accumulator shift

bit 6 **DIV0ERR:** Arithmetic Error Status bit

1 = Math error trap was caused by a divide-by-zero

0 = Math error trap was not caused by a divide-by-zero

bit 5 DMACERR: DMA Controller Error Status bit

1 = DMA Controller error trap has occurred

0 = DMA Controller error trap has not occurred

bit 4 MATHERR: Arithmetic Error Status bit

1 = Math error trap has occurred

0 = Math error trap has not occurred

## REGISTER 7-34: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1  | R/W-0  | R/W-0  |

|--------|-----|-----|-----|-----|--------|--------|--------|

| _      | _   | _   |     | _   | U2EIP2 | U2EIP1 | U2EIP0 |

| bit 15 |     |     |     |     |        |        | bit 8  |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0   |

|-------|--------|--------|--------|-----|-----|-----|-------|

| _     | U1EIP2 | U1EIP1 | U1EIP0 | _   | _   | _   | _     |

| bit 7 |        |        |        |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10-8 **U2EIP<2:0>:** UART2 Error Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

.

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7 Unimplemented: Read as '0'

bit 6-4 **U1EIP<2:0>:** UART1 Error Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

.

\_

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

#### REGISTER 7-44: IPC28: INTERRUPT PRIORITY CONTROL REGISTER 28

| U-0    | R/W-1    | R/W-0    | R/W-0    | U-0 | R/W-1    | R/W-0    | R/W-0    |

|--------|----------|----------|----------|-----|----------|----------|----------|

| _      | ADCP5IP2 | ADCP5IP1 | ADCP5IP0 | _   | ADCP4IP2 | ADCP4IP1 | ADCP4IP0 |

| bit 15 |          |          |          |     |          |          | bit 8    |

| U-0   | R/W-1    | R/W-0    | R/W-0    | U-0 | R/W-1    | R/W-0    | R/W-0    |

|-------|----------|----------|----------|-----|----------|----------|----------|

| _     | ADCP3IP2 | ADCP3IP1 | ADCP3IP0 | _   | ADCP2IP2 | ADCP2IP1 | ADCP2IP0 |

| bit 7 |          |          |          |     |          |          | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-12 ADCP5IP<2:0>: ADC Pair 5 Conversion Done Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 ADCP4IP<2:0>: ADC Pair 4 Conversion Done Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

\_

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 ADCP3IP<2:0>: ADC Pair 3 Conversion Done Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

.

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2-0 ADCP2IP<2:0>: ADC Pair 2 Conversion Done Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

\_

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| PIC33FJ32GS40 | 6/606/608/610 and dsPIC | 33FJ64GS406/606/608/610 |

|---------------|-------------------------|-------------------------|

| OTES:         |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

|               |                         |                         |

# REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

bit 3

SPI1MD: SPI1 Module Disable bit

1 = SPI1 module is disabled

0 = SPI1 module is enabled

bit 2

Unimplemented: Read as '0'

bit 1

C1MD: ECAN1 Module Disable bit

1 = ECAN1 module is disabled

0 = ECAN1 module is enabled

bit 0

ADCMD: ADC Module Disable bit

1 = ADC module is disabled

0 = ADC module is enabled

Note 1: Once the PWM module is re-enabled (PWMMD is set to '1' and then set to '0'), all PWM registers must be re-initialized.

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 5 **ADDEN:** Address Character Detect bit (bit 8 of received data = 1)

- 1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect

- 0 = Address Detect mode is disabled

- bit 4 RIDLE: Receiver Idle bit (read-only)

- 1 = Receiver is Idle

- 0 = Receiver is active

- bit 3 **PERR:** Parity Error Status bit (read-only)

- 1 = Parity error has been detected for the current character (the character at the top of the receive FIFO)

- 0 = Parity error has not been detected

- bit 2 FERR: Framing Error Status bit (read-only)

- 1 = Framing error has been detected for the current character (the character at the top of the receive FIFO)

- 0 = Framing error has not been detected

- bit 1 OERR: Receive Buffer Overrun Error Status bit (clear/read-only)

- 1 = Receive buffer has overflowed

- $0 = \text{Receive buffer has not overflowed; clearing a previously set OERR bit } (1 \rightarrow 0 \text{ transition)}$  will reset the receiver buffer and the UxRSR to the empty state

- bit 0 URXDA: UARTx Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

- Note 1: Refer to "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UART module for transmit operation. That section of the manual is available on the Microchip web site: www.microchip.com.

#### REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| F7BP3  | F7BP2 | F7BP1 | F7BP0 | F6BP3 | F6BP2 | F6BP1 | F6BP0 |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| F5BP3 | F5BP2 | F5BP1 | F5BP0 | F4BP3 | F4BP2 | F4BP1 | F4BP0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 **F7BP<3:0>:** RX Buffer Mask for Filter 7 bits

1111 = Filter hits received in RX FIFO buffer 1110 = Filter hits received in RX Buffer 14

•

•

0001 = Filter hits received in RX Buffer 1 0000 = Filter hits received in RX Buffer 0

bit 11-8 **F6BP<3:0>:** RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) bit 7-4 **F5BP<3:0>:** RX Buffer Mask for Filter 5 bits (same values as bits<15:12>)

bit 3-0 **F4BP<3:0>:** RX Buffer Mask for Filter 4 bits (same values as bits<15:12>)

**DEVICES WITH TWO SARs** Even Numbered Inputs with Dedicated Sample-and-Hold (S&H) Circuits AN0 AN2 Ten SAR Core 16-Bit Registers AN4 AN6 🔀 Even Numbered Inputs AN8 with Shared S&H AN10 AN12 AN14 🔀 AN16 AN24<sup>(1)</sup> (EXTREF) AN1 🛛 Odd Numbered Inputs with Shared S&H Data Format Ten SAR AN3 X 16-Bit Core Registers AN5 AN7 X AN9 🗙 AN11 🗙 AN13 AN15 AN17

AN24 (EXTREF) is an internal analog input. To measure the voltage at AN24 (EXTREF), an analog comparator must be

enabled and EXTREF must be selected as the comparator reference. AN25 (INTREF) is an internal analog input and is not available on a pin.

**FIGURE 22-3:** ADC BLOCK DIAGRAM FOR dsPIC33FJ32GS608 AND dsPIC33FJ64GS608

AN25<sup>(2)</sup> (INTREF)

## REGISTER 22-4: ADPCFG: ADC PORT CONFIGURATION REGISTER

| R/W-0                     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| PCFG<15:8> <sup>(1)</sup> |       |       |       |       |       |       |       |  |

| bit 15                    |       |       |       |       |       |       |       |  |

| R/W-0                    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| PCFG<7:0> <sup>(1)</sup> |       |       |       |       |       |       |       |  |

| bit 7                    |       |       |       | bit 0 |       |       |       |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

# bit 15-0 **PCFG<15:0>:** ADC Port Configuration Control bits<sup>(1)</sup>

- 1 = Port pin in Digital mode, port read input is enabled; Analog-to-Digital input multiplexer is connected to AVss

- 0 = Port pin in Analog mode, port read input is disabled; Analog-to-Digital samples the pin voltage

**Note 1:** Not all PCFGx bits are available on all devices. See Figure 22-1, Figure 22-2, Figure 22-3 and Figure 22-4 for the available analog inputs (PCFGx = ANx, where x = 0-15).

#### REGISTER 22-5: ADPCFG2: ADC PORT CONFIGURATION REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0                      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|----------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| PCFG<23:16> <sup>(1)</sup> |       |       |       |       |       |       |       |  |

| bit 7                      |       |       |       |       |       |       |       |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 PCFG<23:16>: ADC Port Configuration Control bits<sup>(1)</sup>

- 1 = Port pin in Digital mode, port read input is enabled; Analog-to-Digital input multiplexer is connected to AVss

- 0 = Port pin in Analog mode, port read input is disabled; Analog-to-Digital samples the pin voltage

**Note 1:** Not all PCFGx bits are available on all devices. See Figure 22-1, Figure 22-2, Figure 22-3 and Figure 22-4 for the available analog inputs (PCFGx = ANx, where x can be 0 through 15).

### REGISTER 22-8: ADCPC2: ADC CONVERT PAIR CONTROL REGISTER 2 (CONTINUED)

bit 12-8 TRGSRC5<4:0>: Trigger 5 Source Selection bits Selects trigger source for conversion of Analog Channels AN11 and AN10. 11111 = Timer2 period match 11110 = PWM Generator 8 current-limit ADC trigger 11101 = PWM Generator 7 current-limit ADC trigger 11100 = PWM Generator 6 current-limit ADC trigger 11011 = PWM Generator 5 current-limit ADC trigger 11010 = PWM Generator 4 current-limit ADC trigger 11001 = PWM Generator 3 current-limit ADC trigger 11000 = PWM Generator 2 current-limit ADC trigger 10111 = PWM Generator 1 current-limit ADC trigger 10110 = PWM Generator 9 secondary trigger selected 10101 = PWM Generator 8 secondary trigger selected 10100 = PWM Generator 7 secondary trigger selected 10011 = PWM Generator 6 secondary trigger selected 10010 = PWM Generator 5 secondary trigger selected 10001 = PWM Generator 4 secondary trigger selected 10000 = PWM Generator 3 secondary trigger selected 01111 = PWM Generator 2 secondary trigger selected 01110 = PWM Generator 1 secondary trigger selected 01101 = PWM secondary Special Event Trigger selected 01100 = Timer1 period match 01011 = PWM Generator 8 primary trigger selected 01010 = PWM Generator 7 primary trigger selected 01001 = PWM Generator 6 primary trigger selected 01000 = PWM Generator 5 primary trigger selected 00111 = PWM Generator 4 primary trigger selected 00110 = PWM Generator 3 primary trigger selected 00101 = PWM Generator 2 primary trigger selected 00100 = PWM Generator 1 primary trigger selected 00011 = PWM Special Event Trigger selected 00010 = Global software trigger selected 00001 = Individual software trigger selected 00000 = No conversion is enabled bit 7 IRQEN4: Interrupt Request Enable 4 bit 1 = Enables IRQ generation when requested conversion of Channels AN9 and AN8 is completed 0 = IRQ is not generated bit 6 PEND4: Pending Conversion Status 4 bit 1 = Conversion of Channels AN9 and AN8 is pending; set when selected trigger is asserted 0 = Conversion is complete bit 5 SWTRG4: Software Trigger 4 bit 1 = Starts conversion of AN9 and AN8 (if selected by the TRGSRCx<4:0> bits)(1) This bit is automatically cleared by hardware when the PEND4 bit is set. 0 = Conversion has not started

**Note 1:** The trigger source must be set as an individual software trigger prior to setting this bit to '1'. If other conversions are in progress, the conversion is performed when the conversion resources are available.

TABLE 27-31: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHA       | AC CHARACTERISTICS    |                                           |     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |     |       |                                      |  |  |

|--------------|-----------------------|-------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------------------------|--|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>             | Min | Typ <sup>(2)</sup>                                                                                                                                                                                                                               | Max | Units | Conditions                           |  |  |

| SP10         | TscP                  | Maximum SCKx Frequency                    | _   | _                                                                                                                                                                                                                                                | 15  | MHz   | See Note 3                           |  |  |

| SP20         | TscF                  | SCKx Output Fall Time                     | _   |                                                                                                                                                                                                                                                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |  |  |

| SP21         | TscR                  | SCKx Output Rise Time                     | _   |                                                                                                                                                                                                                                                  | _   | ns    | See Parameter DO31 and <b>Note 4</b> |  |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                | _   |                                                                                                                                                                                                                                                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |  |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                | _   | _                                                                                                                                                                                                                                                | _   | ns    | See Parameter DO31 and <b>Note 4</b> |  |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge    | _   | 6                                                                                                                                                                                                                                                | 20  | ns    |                                      |  |  |

| SP36         | TdiV2scH,<br>TdiV2scL | SDOx Data Output Setup to First SCKx Edge | 30  | _                                                                                                                                                                                                                                                | _   | ns    |                                      |  |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

## 30.1 Package Marking Information (Continued)

100-Lead TQFP (12x12x1 mm)

100-Lead TQFP (14x14x1mm)

#### Example

## Example

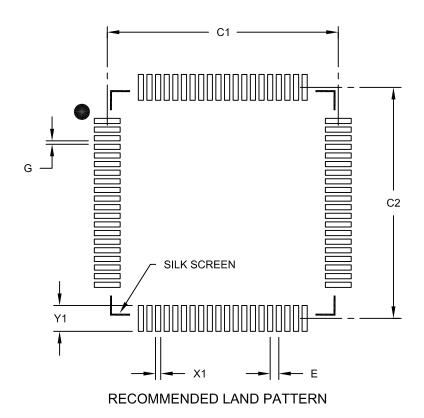

80-Lead Plastic Thin Quad Flatpack (PT) -12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |       |      |

|--------------------------|-------------|----------|-------|------|

| Dimension                | MIN         | NOM      | MAX   |      |

| Contact Pitch            |             | 0.50 BSC |       |      |

| Contact Pad Spacing      | C1          |          | 13.40 |      |

| Contact Pad Spacing      | C2          |          | 13.40 |      |

| Contact Pad Width (X80)  | X1          |          |       | 0.30 |

| Contact Pad Length (X80) | Y1          |          |       | 1.50 |

| Distance Between Pads    | G           | 0.20     |       | ·    |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2092B