Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 50 MIPs                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                         |

| Number of I/O              | 85                                                                                 |

| Program Memory Size        | 32KB (32K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                |                                                                                    |

| RAM Size                   | 4K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 24x10b; D/A 1x10b                                                              |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-TQFP                                                                           |

| Supplier Device Package    | 100-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs610t-50i-pt |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

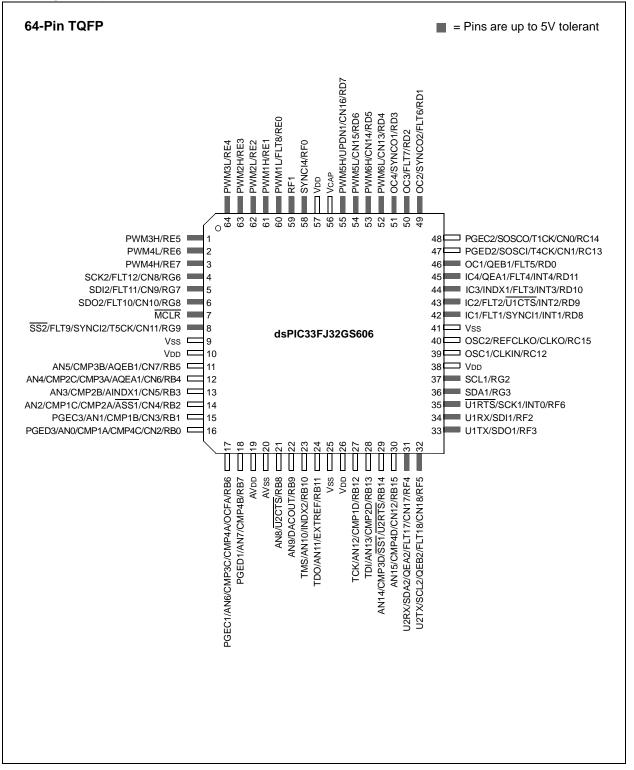

#### Pin Diagrams (Continued)

#### TABLE 4-1: CPU CORE REGISTER MAP (CONTINUED)

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8         | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-----------|---------------|----------|-------|-------|--------|-------|-------|-------|-------|---------------|

| CORCON       | 0044        | _      | —      | _      | US     | EDT    | DL2    | DL1       | DL0           | SATA     | SATB  | SATDW | ACCSAT | IPL3  | PSV   | RND   | IF    | 0000          |

| MODCON       | 0046        | XMODEN | YMODEN | -      | _      | BWM3   | BWM2   | BWM1      | BWM0          | YWM3     | YWM2  | YWM1  | YWM0   | XWM3  | XWM2  | XWM1  | XWM0  | 0000          |

| XMODSRT      | 0048        |        |        |        |        |        | Х      | (S<15:1>  |               |          |       |       |        |       |       |       | 0     | xxxx          |

| XMODEND      | 004A        |        |        |        |        |        | Х      | (E<15:1>  |               |          |       |       |        |       |       |       | 1     | xxxx          |

| YMODSRT      | 004C        |        |        |        |        |        | Y      | ′S<15:1>  |               |          |       |       |        |       |       |       | 0     | xxxx          |

| YMODEND      | 004E        |        |        |        |        |        | Y      | ′E<15:1>  |               |          |       |       |        |       |       |       | 1     | xxxx          |

| XBREV        | 0050        | BREN   | XB14   | XB13   | XB12   | XB11   | XB10   | XB9       | XB8           | XB7      | XB6   | XB5   | XB4    | XB3   | XB2   | XB1   | XB0   | xxxx          |

| DISICNT      | 0052        | _      | —      |        |        |        |        | Disable I | nterrupts Cou | nter Reg | ister |       |        |       |       |       |       | xxxx          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0         | R/W-0               | U-0                                 | U-0            | U-0                   | U-0               | U-0              | R/W-0         |

|---------------|---------------------|-------------------------------------|----------------|-----------------------|-------------------|------------------|---------------|

| TRAPR         | IOPUWR              | —                                   | —              | —                     | —                 | —                | VREGS         |

| bit 15        |                     |                                     | •              | •                     | •                 |                  | bit 8         |

| R/W-0         | R/W-0               | R/W-0                               | R/W-0          | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |

| EXTR          | SWR                 | SWDTEN <sup>(2)</sup>               | WDTO           | SLEEP                 | IDLE              | BOR              | POR           |

| bit 7         |                     |                                     |                |                       |                   |                  | bit C         |

| Legend:       |                     |                                     |                |                       |                   |                  |               |

| R = Readabl   | le bit              | W = Writable                        | bit            | U = Unimpler          | mented bit, read  | t as '0'         |               |

| -n = Value at |                     | '1' = Bit is set                    |                | '0' = Bit is cle      |                   | x = Bit is unk   | nown          |

|               |                     |                                     |                |                       |                   |                  |               |

| bit 15        | TRAPR: Trap         | Reset Flag bit                      |                |                       |                   |                  |               |

|               |                     | onflict Reset ha                    |                |                       |                   |                  |               |

|               | 0 = A Trap C        | onflict Reset ha                    | s not occurre  | d                     |                   |                  |               |

| bit 14        |                     | egal Opcode or                      |                |                       | -                 |                  |               |

|               |                     | al opcode dete                      |                | gal address mo        | ode or Uninitia   | lized W registe  | er used as an |

|               |                     | Pointer caused                      |                | Booot hoo not         | occurred          |                  |               |

| bit 13-9      | -                   | I Opcode or Un                      |                | Reset has not o       | occurred          |                  |               |

| bit 8         | -                   | nted: Read as '<br>age Regulator \$ |                | a Sloop hit           |                   |                  |               |

| DILO          |                     | egulator is activ                   | •              | •                     |                   |                  |               |

|               |                     | egulator goes ir                    |                |                       | ep                |                  |               |

| bit 7         | -                   | nal Reset Pin (                     |                | io do dalling old     | ,                 |                  |               |

|               |                     | Clear (pin) Res                     | -              | red                   |                   |                  |               |

|               |                     | Clear (pin) Res                     |                |                       |                   |                  |               |

| bit 6         |                     | are Reset Flag (                    |                |                       |                   |                  |               |

|               | 1 = A reset         | instruction has                     | been execute   | ed                    |                   |                  |               |

|               | 0 = A  RESET        | instruction has                     | not been exe   | cuted                 |                   |                  |               |

| bit 5         | SWDTEN: So          | oftware Enable/                     | Disable of W   | DT bit <sup>(2)</sup> |                   |                  |               |

|               | 1 = WDT is e        |                                     |                |                       |                   |                  |               |

|               | 0 = WDT is d        |                                     | a aut Elas hi  |                       |                   |                  |               |

| bit 4         |                     | hdog Timer Tin<br>e-out has occur   | -              | τ                     |                   |                  |               |

|               |                     | e-out has occur                     |                |                       |                   |                  |               |

| bit 3         |                     | e-up from Slee                      |                |                       |                   |                  |               |

|               |                     | as been in Slee                     | •              |                       |                   |                  |               |

|               |                     | as not been in S                    |                |                       |                   |                  |               |

| bit 2         | IDLE: Wake-         | up from Idle Fla                    | ig bit         |                       |                   |                  |               |

|               |                     | as been in Idle i                   | -              |                       |                   |                  |               |

|               | 0 = Device ha       | as not been in I                    | dle mode       |                       |                   |                  |               |

| bit 1         | BOR: Brown          | -out Reset Flag                     | bit            |                       |                   |                  |               |

|               | 1 = A Brown-        | out Reset has o                     | occurred       |                       |                   |                  |               |

|               |                     | out Reset has r                     |                |                       |                   |                  |               |

| bit 0         |                     | on Reset Flag                       |                |                       |                   |                  |               |

|               |                     | on Reset has o<br>on Reset has n    |                |                       |                   |                  |               |

| Note 1: A     | II of the Reset sta |                                     |                | d in software. S      | Settina one of th | ese bits in soft | ware does not |

|               | ause a device Re    |                                     |                |                       |                   |                  |               |

| 2. If         | the FWDTEN Co       | onfiguration hit                    | is '1' (unnroa | rammed) the V         | WDT is always (   | anabled regar    | these of the  |

## REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

cause a device Reset.

If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| U-0          | U-0           | U-0                              | U-0           | U-0              | U-0              | U-0             | U-0     |

|--------------|---------------|----------------------------------|---------------|------------------|------------------|-----------------|---------|

| _            | —             | —                                | —             | _                | _                | _               | _       |

| bit 15       | ÷             |                                  |               |                  |                  |                 | bit 8   |

|              |               |                                  |               |                  |                  |                 |         |

| U-0          | U-0           | R/W-0                            | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| —            | —             | ADCP7IF                          | ADCP6IF       | ADCP5IF          | ADCP4IF          | ADCP3IF         | ADCP2IF |

| bit 7        |               |                                  |               |                  |                  |                 | bit C   |

|              |               |                                  |               |                  |                  |                 |         |

| Legend:      | 1 1 2         |                                  | 1.14          |                  |                  |                 |         |

| R = Readab   |               | W = Writable                     |               | •                | mented bit, read |                 |         |

| -n = Value a | t POR         | '1' = Bit is set                 |               | '0' = Bit is cle | ared             | x = Bit is unkr | iown    |

| bit 15-6     | Unimplomor    | nted: Read as '                  | 0'            |                  |                  |                 |         |

| bit 5        | -             |                                  |               | ntorrupt Elog S  | Yotuo hit        |                 |         |

| DIL D        |               | DC Pair 7 Conv<br>request has oc |               | nterrupt Flag S  |                  |                 |         |

|              |               | request has no                   |               |                  |                  |                 |         |

| bit 4        | ADCP6IF: A    | DC Pair 6 Conv                   | ersion Done I | nterrupt Flag S  | Status bit       |                 |         |

|              |               | request has oc                   |               |                  |                  |                 |         |

|              | •             | request has no                   |               |                  |                  |                 |         |

| bit 3        |               | DC Pair 5 Conv                   |               | nterrupt Flag S  | Status bit       |                 |         |

|              |               | request has oc<br>request has no |               |                  |                  |                 |         |

| bit 2        |               | DC Pair 4 Conv                   |               | nterrupt Flag S  | status bit       |                 |         |

|              |               | request has oc                   |               |                  |                  |                 |         |

|              |               | request has no                   |               |                  |                  |                 |         |

| bit 1        | ADCP3IF: AD   | DC Pair 3 Conv                   | ersion Done I | nterrupt Flag S  | status bit       |                 |         |

|              |               | request has oc                   |               |                  |                  |                 |         |

|              | -             | request has no                   |               |                  |                  |                 |         |

| bit 0        |               | DC Pair 2 Conv                   |               | nterrupt Flag S  | Status bit       |                 |         |

|              | •             | request has oc                   |               |                  |                  |                 |         |

|              | 0 = interrupt | request has no                   | loccurrea     |                  |                  |                 |         |

#### REGISTER 7-12: IFS7: INTERRUPT FLAG STATUS REGISTER 7

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| U-0          | R/W-1              | R/W-0                                    | R/W-0           | U-0              | R/W-1             | R/W-0           | R/W-0   |

|--------------|--------------------|------------------------------------------|-----------------|------------------|-------------------|-----------------|---------|

| _            | U2TXIP2            | U2TXIP1                                  | U2TXIP0         | _                | U2RXIP2           | U2RXIP1         | U2RXIP0 |

| bit 15       |                    |                                          |                 |                  |                   |                 | bit 8   |

|              |                    | <b>D</b> 444 a                           |                 |                  | -                 | <b>D</b> 444 a  |         |

| U-0          | R/W-1              | R/W-0                                    | R/W-0           | U-0              | R/W-1             | R/W-0           | R/W-0   |

|              | INT2IP2            | INT2IP1                                  | INT2IP0         |                  | T5IP2             | T5IP1           | T5IP0   |

| bit 7        |                    |                                          |                 |                  |                   |                 | bit     |

| Legend:      |                    |                                          |                 |                  |                   |                 |         |

| R = Readab   | le bit             | W = Writable                             | bit             | U = Unimple      | emented bit, read | d as '0'        |         |

| -n = Value a | t POR              | '1' = Bit is set                         |                 | '0' = Bit is cl  | eared             | x = Bit is unkr | nown    |

| bit 15       | Unimplomor         | tod: Pood oo '                           | 0'              |                  |                   |                 |         |

| bit 14-12    | -                  | n <b>ted:</b> Read as '<br>>: UART2 Tran |                 | nt Priority hits |                   |                 |         |

| 510 11 12    |                    | pt is Priority 7 (                       |                 | •                | ,                 |                 |         |

|              | •                  |                                          |                 | ,,               |                   |                 |         |

|              | •                  |                                          |                 |                  |                   |                 |         |

|              | •<br>001 = Interru | pt is Priority 1                         |                 |                  |                   |                 |         |

|              |                    | pt source is dis                         | abled           |                  |                   |                 |         |

| bit 11       |                    | ted: Read as '                           |                 |                  |                   |                 |         |

| bit 10-8     | U2RXIP<2:0         | >: UART2 Rece                            | eiver Interrupt | Priority bits    |                   |                 |         |

|              | 111 = Interru      | pt is Priority 7 (                       | highest priorit | y interrupt)     |                   |                 |         |

|              | •                  |                                          |                 |                  |                   |                 |         |

|              | •                  |                                          |                 |                  |                   |                 |         |

|              | 001 = Interru      | pt is Priority 1                         |                 |                  |                   |                 |         |

|              |                    | pt source is dis                         | abled           |                  |                   |                 |         |

| bit 7        | Unimplemen         | nted: Read as '                          | 0'              |                  |                   |                 |         |

| bit 6-4      | INT2IP<2:0>        | : External Inter                         | rupt 2 Priority | bits             |                   |                 |         |

|              | 111 = Interru      | pt is Priority 7                         | highest priorit | y interrupt)     |                   |                 |         |

|              | •                  |                                          |                 |                  |                   |                 |         |

|              | •                  |                                          |                 |                  |                   |                 |         |

|              | 001 = Interru      | pt is Priority 1                         |                 |                  |                   |                 |         |

|              |                    | pt source is dis                         | abled           |                  |                   |                 |         |

| bit 3        | Unimplemen         | ted: Read as '                           | 0'              |                  |                   |                 |         |

| bit 2-0      | T5IP<2:0>: ⊺       | imer5 Interrupt                          | Priority bits   |                  |                   |                 |         |

|              | 111 = Interru      | pt is Priority 7 (                       | highest priorit | y interrupt)     |                   |                 |         |

|              | •                  |                                          |                 |                  |                   |                 |         |

|              |                    |                                          |                 |                  |                   |                 |         |

|              | •                  |                                          |                 |                  |                   |                 |         |

|              | •<br>001 = Interru | pt is Priority 1                         |                 |                  |                   |                 |         |

### REGISTER 7-28: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

#### 9.1 CPU Clocking System

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices provide six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS, or EC) Oscillator

- Primary Oscillator with PLL

- Low-Power RC (LPRC) Oscillator

- FRC Oscillator with Postscaler

- Secondary (LP) Oscillator

#### 9.1.1 SYSTEM CLOCK SOURCES

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 50 MHz. The crystal is connected to the OSC1 and OSC2 pins

- EC (External Clock): The external clock signal is directly applied to the OSC1 pin

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The LPRC internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase-Locked Loop (PLL) to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 9.1.3 "PLL Configuration"**.

The FRC frequency depends on the FRC accuracy (see Table 27-20) and the value of the FRC Oscillator Tuning register (see Register 9-4).

#### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to **Section 24.1 "Configuration Bits"** for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected), FOSC, is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device and speeds up to 50 MIPS are supported by the device architecture.

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = FOSC/2

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                 | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See Notes |

|-------------------------------------------------|-------------------|-------------|------------|-----------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)   | Internal          | xx          | 111        | 1, 2      |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16) | Internal          | xx          | 110        | 1         |

| Low-Power RC Oscillator (LPRC)                  | Internal          | xx          | 101        | 1         |

| Secondary Oscillator (SOSC)                     | Secondary         | xx          | 100        | —         |

| Primary Oscillator (HS) with PLL (HSPLL)        | Primary           | 10          | 011        | —         |

| Primary Oscillator (XT) with PLL (XTPLL)        | Primary           | 01          | 011        | —         |

| Primary Oscillator (EC) with PLL (ECPLL)        | Primary           | 00          | 011        | 1         |

| Primary Oscillator (HS)                         | Primary           | 10          | 010        | —         |

| Primary Oscillator (XT)                         | Primary           | 01          | 010        | —         |

| Primary Oscillator (EC)                         | Primary           | 00          | 010        | 1         |

| Fast RC Oscillator with PLL (FRCPLL)            | Internal          | xx          | 001        | 1         |

| Fast RC Oscillator (FRC)                        | Internal          | xx          | 000        | 1         |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| R/W-0         | R-0                                                                                                                                  | R/W-1                                                       | U-0           | U-0              | R/W-1                                   | R/W-1           | R/W-1     |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------|------------------|-----------------------------------------|-----------------|-----------|

| ENAPLL        | APLLCK                                                                                                                               | SELACLK                                                     | _             | —                | APSTSCLR2                               | APSTSCLR1       | APSTSCLR0 |

| bit 15        |                                                                                                                                      |                                                             |               |                  |                                         |                 | bit 8     |

|               |                                                                                                                                      |                                                             |               |                  |                                         |                 |           |

| R/W-0         | R/W-0                                                                                                                                | U-0                                                         | U-0           | U-0              | U-0                                     | U-0             | U-0       |

| ASRCSEL       | FRCSEL                                                                                                                               | —                                                           |               | —                |                                         | —               |           |

| bit 7         |                                                                                                                                      |                                                             |               |                  |                                         |                 | bit C     |

| Legend:       |                                                                                                                                      |                                                             |               |                  |                                         |                 |           |

| R = Readable  | e bit                                                                                                                                | W = Writable b                                              | oit           | U = Unimpler     | mented bit, read                        | as '0'          |           |

| -n = Value at | POR                                                                                                                                  | '1' = Bit is set                                            |               | '0' = Bit is cle | ared                                    | x = Bit is unkr | nown      |

| bit 15        | 1 = APLL is e                                                                                                                        |                                                             | ole bit       |                  |                                         |                 |           |

|               | 0 = APLL is d                                                                                                                        |                                                             |               |                  |                                         |                 |           |

| bit 14        |                                                                                                                                      | LL Locked Statu                                             | •             | nly)             |                                         |                 |           |

|               |                                                                                                                                      | that auxiliary Pl<br>that auxiliary Pl                      |               | ck               |                                         |                 |           |

| bit 13        | SELACLK: S                                                                                                                           | elect Auxiliary C                                           | Clock Source  | for Auxiliary C  | lock Divider bit                        |                 |           |

|               |                                                                                                                                      |                                                             |               |                  | auxiliary clock di<br>e auxiliary clock |                 |           |

| bit 12-11     | Unimplemen                                                                                                                           | ted: Read as '0                                             | ,             |                  |                                         |                 |           |

| bit 10-8      | APSTSCLR<                                                                                                                            | 2:0>: Auxiliary                                             | Clock Output  | Divider bits     |                                         |                 |           |

|               | 111 = Divideo<br>110 = Divideo<br>101 = Divideo<br>011 = Divideo<br>010 = Divideo<br>010 = Divideo<br>001 = Divideo<br>000 = Divideo | d bý 2<br>d by 4<br>d by 8<br>d by 16<br>d by 32<br>d by 64 |               |                  |                                         |                 |           |

| bit 7         | ASRCSEL: S                                                                                                                           | elect Reference                                             | Clock Source  | e for Auxiliary  | Clock bit                               |                 |           |

|               |                                                                                                                                      | scillator is the c                                          |               |                  |                                         |                 |           |

| bit 6         |                                                                                                                                      | lect Reference (<br>RC clock for au                         |               | for Auxiliary P  |                                         |                 |           |

|               | 0 = Input cloc                                                                                                                       | k source is dete                                            | ermined by th | e ASRCSEL b      | it setting                              |                 |           |

#### REGISTER 9-5: ACLKCON: AUXILIARY CLOCK DIVISOR CONTROL REGISTER

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 3 SPI1MD: SPI1 Module Disable bit

- 1 = SPI1 module is disabled 0 = SPI1 module is enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 **C1MD:** ECAN1 Module Disable bit 1 = ECAN1 module is disabled

- 0 = ECAN1 module is enabled

- bit 0 ADCMD: ADC Module Disable bit 1 = ADC module is disabled

- 0 = ADC module is enabled

- **Note 1:** Once the PWM module is re-enabled (PWMMD is set to '1' and then set to '0'), all PWM registers must be re-initialized.

| HS/HC-0       | HS/HC-0                                                      | HS/HC-0                                      | R/W-0                 | R/W-0            | R/W-0                           | R/W-0                         | R/W-0               |

|---------------|--------------------------------------------------------------|----------------------------------------------|-----------------------|------------------|---------------------------------|-------------------------------|---------------------|

| FLTSTAT(      | <sup>1)</sup> CLSTAT <sup>(1)</sup>                          | TRGSTAT                                      | FLTIEN                | CLIEN            | TRGIEN                          | ITB <sup>(3)</sup>            | MDCS <sup>(3)</sup> |

| bit 15        |                                                              |                                              |                       |                  |                                 |                               | bit 8               |

| DAMO          | DAM 0                                                        | D/M/ O                                       |                       | R/W-0            | DAMA                            | DAMO                          | DAMO                |

| R/W-0         | R/W-0                                                        | R/W-0<br>DTCP <sup>(4)</sup>                 | U-0                   |                  | R/W-0<br>CAM <sup>(2,3,5)</sup> | R/W-0<br>XPRES <sup>(6)</sup> | R/W-0               |

| DTC1<br>bit 7 | DTC0                                                         | DICPO                                        | —                     | MTBS             | CAM                             | APRES(*)                      | IUE<br>bit          |

|               |                                                              |                                              |                       |                  |                                 |                               |                     |

| Legend:       |                                                              | HC = Hardware                                | Clearable bit         | HS = Hardw       | are Settable bit                |                               |                     |

| R = Reada     | ble bit                                                      | W = Writable b                               | it                    | U = Unimple      | mented bit, rea                 | d as '0'                      |                     |

| -n = Value    | at POR                                                       | '1' = Bit is set                             |                       | '0' = Bit is cl  | eared                           | x = Bit is unk                | nown                |

| bit 15        | FLTSTAT: Fa                                                  | ult Interrupt Stat                           | us bit <sup>(1)</sup> |                  |                                 |                               |                     |

|               |                                                              | rrupt is pending                             |                       |                  |                                 |                               |                     |

|               |                                                              | nterrupt is pend                             |                       |                  |                                 |                               |                     |

|               |                                                              | ared by setting F                            |                       |                  |                                 |                               |                     |

| bit 14        |                                                              | rent-Limit Interru                           | •                     |                  |                                 |                               |                     |

|               |                                                              | mit interrupt is pe<br>nt-limit interrupt is |                       |                  |                                 |                               |                     |

|               |                                                              | ared by setting C                            |                       |                  |                                 |                               |                     |

| bit 13        | TRGSTAT: Tr                                                  | igger Interrupt S                            | tatus bit             |                  |                                 |                               |                     |

|               |                                                              | terrupt is pendin                            | •                     |                  |                                 |                               |                     |

|               |                                                              | r interrupt is pen<br>ared by setting T      |                       |                  |                                 |                               |                     |

| bit 12        |                                                              | t Interrupt Enabl                            |                       |                  |                                 |                               |                     |

|               |                                                              | rrupt is enabled                             | o on                  |                  |                                 |                               |                     |

|               |                                                              | rrupt is disabled                            | and FLTSTAT b         | oit is cleared   |                                 |                               |                     |

| bit 11        | CLIEN: Curre                                                 | ent-Limit Interrup                           | t Enable bit          |                  |                                 |                               |                     |

|               |                                                              | mit interrupt is e<br>mit interrupt is di    |                       | STAT bit is cle  | ared                            |                               |                     |

| bit 10        | TRGIEN: Trig                                                 | ger Interrupt En                             | able bit              |                  |                                 |                               |                     |

|               |                                                              | event generates<br>/ent interrupts a         |                       |                  | is cleared                      |                               |                     |

| bit 9         |                                                              | dent Time Base                               |                       |                  |                                 |                               |                     |

|               | 1 = PHASEx/                                                  | SPHASEx regist                               | ters provide tim      | •                | •                               | enerator                      |                     |

| bit 8         |                                                              | er Duty Cycle Re                             | -                     |                  |                                 |                               |                     |

|               | 1 = MDC regi                                                 | ster provides du<br>d SDCx registers         | ty cycle informa      | ation for this P |                                 | generator                     |                     |

| Note 1:       | Software must cle                                            | ear the interrupt                            | status here and       | l in the corresp | oonding IFSx bit                | in the interrup               | t controller.       |

|               | The Independent<br>CAM bit is ignore                         |                                              | e (ITB = 1) mus       | st be enabled t  | o use Center-A                  | igned mode. If                | TTB = 0, the        |

| 3:            | These bits should                                            | I not be changed                             | after the PWM         | l is enabled by  | setting PTEN (                  | PTCON<15>)                    | = 1.                |

|               | For DTCP to be e                                             |                                              |                       |                  |                                 |                               |                     |

|               | Center-Aligned m<br>registers. The hig<br>the fastest clock. |                                              |                       |                  |                                 |                               |                     |

| 6:            | Configure CLMO<br>Reset mode.                                | D (FCLCONX<8                                 | 3>) = 0 and ITB       | (PWMCONx         | <9>) = 1 to ope                 | rate in Externa               | al Period           |

#### REGISTER 16-11: PWMCONX: PWM CONTROL x REGISTER

NOTES:

| REGISTER 2            | 0-1: UxMO                              | DE: UARTx M                                              | IODE REGI                                             | STER                                    |                                                                        |                  |               |

|-----------------------|----------------------------------------|----------------------------------------------------------|-------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------|------------------|---------------|

| R/W-0                 | U-0                                    | R/W-0                                                    | R/W-0                                                 | R/W-0                                   | U-0                                                                    | R/W-0            | R/W-0         |

| UARTEN <sup>(1)</sup> | —                                      | USIDL                                                    | IREN <sup>(2)</sup>                                   | RTSMD                                   | —                                                                      | UEN1             | UEN0          |

| bit 15                |                                        |                                                          |                                                       |                                         |                                                                        |                  | bit 8         |

|                       | DAMO                                   |                                                          | DAMO                                                  | DAMO                                    | DAM 0                                                                  | DAMA             | DAMA          |

| R/W-0, HC             | R/W-0                                  | R/W-0, HC                                                | R/W-0                                                 | R/W-0                                   | R/W-0                                                                  | R/W-0            | R/W-0         |

| WAKE                  | LPBACK                                 | ABAUD                                                    | URXINV                                                | BRGH                                    | PDSEL1                                                                 | PDSEL0           | STSEL         |

| bit 7                 |                                        |                                                          |                                                       |                                         |                                                                        |                  | bit           |

| Legend:               |                                        | HC = Hardwa                                              | re Clearable b                                        | oit                                     |                                                                        |                  |               |

| R = Readable          | bit                                    | W = Writable                                             | bit                                                   | U = Unimpler                            | mented bit, read                                                       | l as '0'         |               |

| -n = Value at F       | POR                                    | '1' = Bit is set                                         |                                                       | '0' = Bit is cle                        | ared                                                                   | x = Bit is unkn  | own           |

| bit 15                | 1 = UARTx is                           |                                                          | ARTx pins ar                                          |                                         | UARTx as defi<br>y port latches, l                                     |                  |               |

| bit 14                | Unimplemen                             | ted: Read as '                                           | כ'                                                    |                                         |                                                                        |                  |               |

| bit 13                | -                                      | Tx Stop in Idle I                                        |                                                       |                                         |                                                                        |                  |               |

|                       |                                        | nues module op<br>es module opera                        |                                                       |                                         | Idle mode                                                              |                  |               |

| bit 12                | IREN: IrDA®                            | Encoder and D                                            | ecoder Enabl                                          | e bit <sup>(2)</sup>                    |                                                                        |                  |               |

|                       |                                        | oder and decoo<br>oder and decoo                         |                                                       |                                         |                                                                        |                  |               |

| bit 11                | RTSMD: Mod                             | le Selection for                                         | UxRTS Pin b                                           | it                                      |                                                                        |                  |               |

|                       |                                        | oin is in Simple»<br>An is in Flow Co                    |                                                       |                                         |                                                                        |                  |               |

| bit 10                | Unimplemen                             | ted: Read as '                                           | כ'                                                    |                                         |                                                                        |                  |               |

| bit 9-8               | 11 = UxTX,<br>10 = UxTX,<br>01 = UxTX, | UxRX, UxCTS<br>UxRX and UxR<br>and UxRX pins             | K pi <u>ns are en</u><br>and UxRTS p<br>TS pins are e | ins are enable<br>nabled an <u>d us</u> | d; UxCTS pin is<br>d an <u>d used</u><br>ed; UxCTS pin<br>TS and UxRTS | is controlled by | port latches  |

| bit 7                 | WAKE: Wake                             | e-up on Start bit                                        | Detect Durin                                          | g Sleep Mode                            | Enable bit                                                             |                  |               |

|                       | in hardw                               | vill continue to s<br>are on following<br>-up is enabled |                                                       | RX pin; interru                         | pt is generated                                                        | on falling edge  | bit is cleare |

| bit 6                 | LPBACK: UA                             | ARTx Loopback                                            | Mode Select                                           | bit                                     |                                                                        |                  |               |

|                       |                                        | Loopback mod<br>k mode is disat                          |                                                       |                                         |                                                                        |                  |               |

| bit 5                 | •                                      | p-Baud Enable                                            |                                                       |                                         |                                                                        |                  |               |

|                       | 1 = Enables<br>before of               |                                                          | surement on t<br>ed in hardwar                        | e upon comple                           | eter – requires re<br>tion                                             | eception of a Sy | nc field (55h |

| ena                   | abling the UART                        |                                                          | eive or transr                                        |                                         | Reference Manu<br>That section of th                                   |                  |               |

| 2. This               | o footuro io only                      | ( ovoilable for t                                        |                                                       | nodo (PPCU                              | - 0)                                                                   |                  |               |

#### MODELLADT. MODE DECISTED 010TI ~~ . ...

2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| DAAL          | DAAL        | DAA                                                    | D AA/         | D ///            | DAAL             | D ///           | D /// |

|---------------|-------------|--------------------------------------------------------|---------------|------------------|------------------|-----------------|-------|

| R/W-x         | R/W-x       | R/W-x                                                  | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |

| SID10         | SID9        | SID8                                                   | SID7          | SID6             | SID5             | SID4            | SID3  |

| bit 15        |             |                                                        |               |                  |                  |                 | bit 8 |

|               |             |                                                        |               |                  |                  |                 |       |

| R/W-x         | R/W-x       | R/W-x                                                  | U-0           | R/W-x            | U-0              | R/W-x           | R/W-x |

| SID2          | SID1        | SID0                                                   | —             | EXIDE            | —                | EID17           | EID16 |

| bit 7         |             |                                                        |               |                  |                  |                 | bit 0 |

|               |             |                                                        |               |                  |                  |                 |       |

| Legend:       |             |                                                        |               |                  |                  |                 |       |

| R = Readable  | e bit       | W = Writable                                           | bit           | U = Unimplen     | nented bit, read | d as '0'        |       |

| -n = Value at | POR         | '1' = Bit is set                                       |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 4         | 0 = Message | address bit, SI<br>address bit, SI<br>ited: Read as '( | Dx, must be ' |                  |                  |                 |       |

| bit 3         | •           | nded Identifier E                                      |               |                  |                  |                 |       |

| -             |             | only messages<br>only messages<br>:hen:                |               |                  |                  |                 |       |

| bit 2         | Unimplemen  | ted: Read as '                                         | )'            |                  |                  |                 |       |

| bit 1-0       | EID<17:16>: | Extended Ident                                         | ifier bits    |                  |                  |                 |       |

|               | •           | address bit, El<br>address bit, El                     |               |                  |                  |                 |       |

| R/W-0             | R/W-0        | R/W-0            | R/W-0           | R/W-0            | R/W-0            | R/W-0              | R/W-0   |  |

|-------------------|--------------|------------------|-----------------|------------------|------------------|--------------------|---------|--|

| F15MSK1           | F15MSK0      | F14MSK1          | F14MSK0         | F13MSK1          | F13MSK0          | F12MSK1            | F12MSK0 |  |

| bit 15            |              |                  |                 |                  |                  |                    | bit 8   |  |

|                   |              |                  |                 |                  |                  |                    |         |  |

| R/W-0             | R/W-0        | R/W-0            | R/W-0           | R/W-0            | R/W-0            | R/W-0              | R/W-0   |  |

| F11MSK1           | F11MSK0      | F10MSK1          | F10MSK0         | F9MSK1           | F9MSK0           | F8MSK1             | F8MSK0  |  |

| bit 7             |              |                  |                 |                  |                  |                    | bit 0   |  |

|                   |              |                  |                 |                  |                  |                    |         |  |

| Legend:           |              |                  |                 |                  |                  |                    |         |  |

| R = Readable      | bit          | W = Writable     | bit             | U = Unimpler     | mented bit, read | l as '0'           |         |  |

| -n = Value at POR |              | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unknown |         |  |

|                   |              |                  |                 |                  |                  |                    |         |  |

| bit 15-14         | F15MSK<1:0   | >: Mask Sourc    | e for Filter 15 | bits             |                  |                    |         |  |

|                   | 11 = Reserve | ed               |                 |                  |                  |                    |         |  |

|                   |              | nce Mask 2 reg   |                 |                  |                  |                    |         |  |

|                   | 01 = Accepta | nce Mask 1 reg   | gisters contain | mask             |                  |                    |         |  |

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| bit 13-12 | F14MSK<1:0>: Mask Source for Filter 14 bits (same values as bits<15:14>) |

|-----------|--------------------------------------------------------------------------|

00 = Acceptance Mask 0 registers contain mask

bit 11-10 F13MSK<1:0>: Mask Source for Filter 13 bits (same values as bits<15:14>)

bit 9-8 F12MSK<1:0>: Mask Source for Filter 12 bits (same values as bits<15:14>)

bit 7-6 **F11MSK<1:0>:** Mask Source for Filter 11 bits (same values as bits<15:14>)

bit 5-4 **F10MSK<1:0>:** Mask Source for Filter 10 bits (same values as bits<15:14>)

bit 3-2 **F9MSK<1:0>:** Mask Source for Filter 9 bits (same values as bits<15:14>)

bit 1-0 F8MSK<1:0>: Mask Source for Filter 8 bits (same values as bits<15:14>)

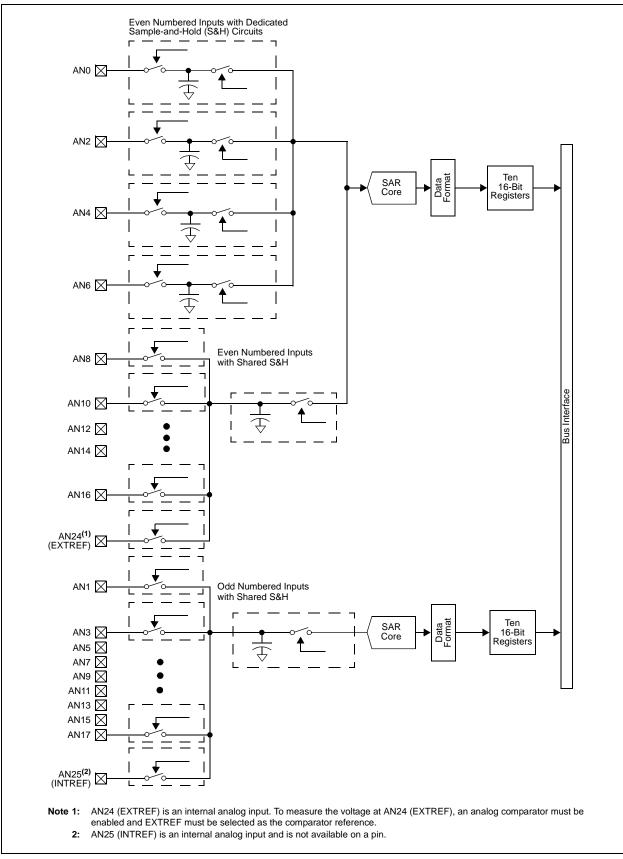

#### FIGURE 22-3: ADC BLOCK DIAGRAM FOR dsPIC33FJ32GS608 AND dsPIC33FJ64GS608 DEVICES WITH TWO SARs

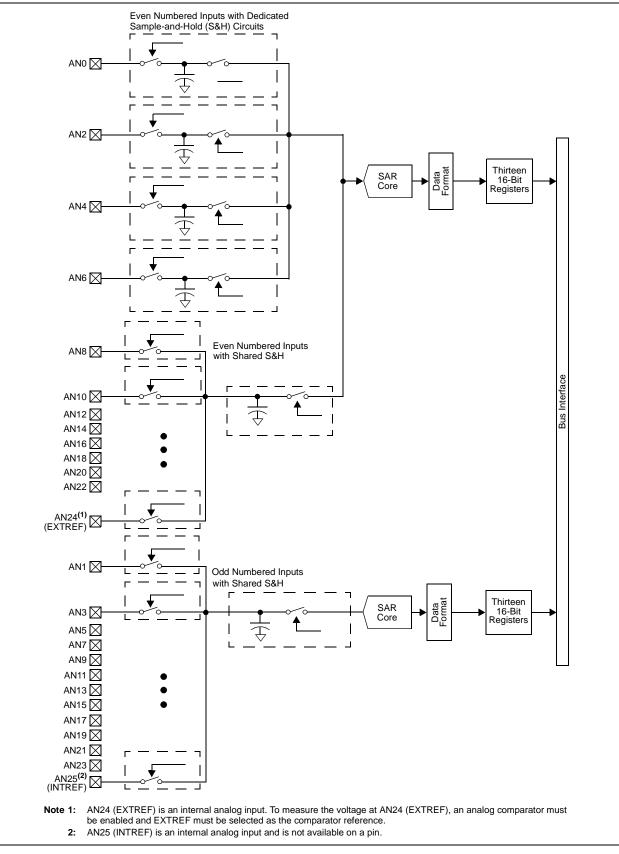

#### FIGURE 22-4: ADC BLOCK DIAGRAM FOR dsPIC33FJ32GS610 AND dsPIC33FJ64GS610 DEVICES WITH TWO SARs

| REGISTER 22-3: | ADBASE: ADC BASE REGISTER <sup>(1,2)</sup> |

|----------------|--------------------------------------------|

|----------------|--------------------------------------------|

| R/W-0  | R/W-0 | R/W-0 | R/W-0       | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------------|---------|-------|-------|-------|

|        |       |       | ADBAS       | E<15:8> |       |       |       |

| bit 15 |       |       |             |         |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0       | R/W-0   | R/W-0 | R/W-0 | U-0   |

|        |       | ŀ     | ADBASE<7:1> |         |       |       | _     |

| bit 7  |       |       |             |         |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-1 ADBASE<15:1>: ADC Base Address bits

This register contains the base address of the user's ADC Interrupt Service Routine jump table. This register, when read, contains the sum of the ADBASE register contents and the encoded value of the PxRDY status bits.

The encoder logic provides the bit number of the highest priority PxRDY bits where P0RDY is the highest priority and P6RDY is the lowest priority.

#### bit 0 Unimplemented: Read as '0'

- Note 1: The encoding results are shifted left two bits so bits 1-0 of the result are always zero.

- 2: As an alternative to using the ADBASE register, the ADCP0-ADCP12 ADC pair conversion complete interrupts can be used to invoke Analog-to-Digital conversion completion routines for individual ADC input pairs.

| TABLE 24-2: | BLE 24-2: dsPIC33F CONFIGURATION BITS DESCRIPTION |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit Field   | Register                                          | RTSP Effect                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| BWRP        | FBS                                               | Immediate                                                                                              | Boot Segment Program Flash Write Protection bit<br>1 = Boot segment can be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| BSS<2:0>    | FBS                                               | Immediate                                                                                              | <ul> <li>Boot Segment Program Flash Code Protection Size bits</li> <li>X11 = No boot program Flash segment</li> <li>Boot Space is 256 Instruction Words (except interrupt vectors):</li> <li>110 = Standard security; boot program Flash segment ends at 0x0003FE</li> <li>010 = High security; boot program Flash segment ends at 0x0003FE</li> <li>Boot Space is 768 Instruction Words (except interrupt vectors):</li> <li>101 = Standard security; boot program Flash segment ends at 0x0007FE</li> <li>001 = High security; boot program Flash segment ends at 0x0007FE</li> <li>Boot Space is 1792 Instruction Words (except interrupt vectors):</li> <li>100 = Standard security; boot program Flash segment ends at 0x0007FE</li> <li>Boot Space is 1792 Instruction Words (except interrupt vectors):</li> <li>100 = Standard security; boot program Flash segment ends at 0x000FFE</li> <li>000 = High security; boot program Flash segment ends at 0x000FFE</li> </ul> |  |  |  |

| GSS<1:0>    | FGS                                               | Immediate                                                                                              | General Segment Code-Protect bits<br>11 = User program memory is not code-protected<br>10 = Standard security<br>0x = High security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| GWRP        | FGS                                               | Immediate                                                                                              | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| IESO        | FOSCSEL                                           | Immediate                                                                                              | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start-up device with FRC, then automatically switch to the user selected oscillator source when ready</li> <li>0 = Start-up device with user selected oscillator source</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| FNOSC<2:0>  | FOSCSEL                                           | If clock switch<br>is enabled,<br>RTSP effect<br>is on any<br>device Reset;<br>otherwise,<br>immediate | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) Oscillator with Postscaler<br>110 = Internal Fast RC (FRC) Oscillator with Divide-by-16<br>101 = LPRC Oscillator<br>100 = Secondary (LP) Oscillator<br>011 = Primary (XT, HS, EC) Oscillator with PLL<br>010 = Primary (XT, HS, EC) Oscillator<br>001 = Internal Fast RC (FRC) Oscillator with PLL<br>000 = FRC Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |