Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10b; D/A 1x10b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

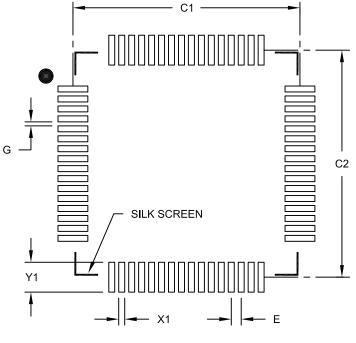

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gs610t-i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

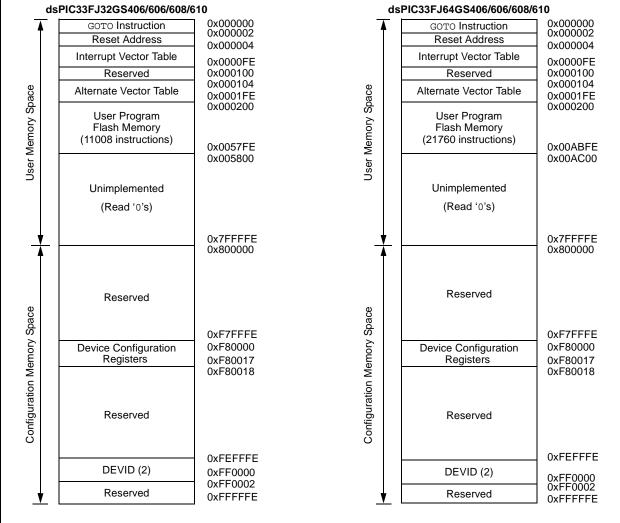

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *dsPIC33/PIC24 Family Reference Manual*, **Program Memory**" (DS70203), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access to program memory from the data space during code execution.

## 4.1 Program Address Space

The program address memory space is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in **Section 4.6 "Interfacing Program and Data Memory Spaces"**.

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory maps are shown in Figure 4-1.

# FIGURE 4-1: PROGRAM MEMORY MAPS FOR dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13   | Bit 12  | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|---------|---------|----------|---------|---------|----------|----------|----------|----------|----------|----------|----------|---------|----------|----------|----------|---------------|

| INTCON1      | 0080        | NSTDIS  | OVAERR  | OVBERR   | COVAERR | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  | _        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | —        | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI    | _        | _       | _       |          | —        |          | —        | _        | —        | INT4EP   | INT3EP  | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0         | 0084        | _       | —       | ADIF     | U1TXIF  | U1RXIF  | SPI1IF   | SPI1EIF  | T3IF     | T2IF     | OC2IF    | IC2IF    | —        | T1IF    | OC1IF    | IC1IF    | INTOIF   | 0000          |

| IFS1         | 0086        | U2TXIF  | U2RXIF  | INT2IF   | T5IF    | T4IF    | OC4IF    | OC3IF    |          | —        | _        | —        | INT1IF   | CNIF    |          | MI2C1IF  | SI2C1IF  | 0000          |

| IFS2         | 0088        | _       | _       | -        | _       | _       | _        | _        | _        | _        | IC4IF    | IC3IF    | _        | -       | _        | SPI2IF   | SPI2EIF  | 0000          |

| IFS3         | 008A        | _       | _       | -        | _       | _       | QEI1IF   | PSEMIF   | _        | _        | INT4IF   | INT3IF   | _        | -       | MI2C2IF  | SI2C2IF  | _        | 0000          |

| IFS4         | 008C        | _       | _       | -        | _       | _       | _        | PSESMIF  | _        | _        | _        | _        | _        | -       | U2EIF    | U1EIF    | _        | 0000          |

| IFS5         | 008E        | PWM2IF  | PWM1IF  | ADCP12IF | _       | _       | _        | _        | _        | _        | _        | _        | _        | -       | _        | _        | _        | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF | -        | _       | _       | _        | _        | _        | _        | _        | _        | _        | PWM6IF  | PWM5IF   | PWM4IF   | PWM3IF   | 0000          |

| IFS7         | 0092        | _       | _       | -        | _       | _       | _        | _        | _        | _        | _        | ADCP7IF  | ADCP6IF  | ADCP5IF | ADCP4IF  | ADCP3IF  | ADCP2IF  | 0000          |

| IEC0         | 0094        | _       | _       | ADIE     | U1TXIE  | U1RXIE  | SPI1IE   | SPI1EIE  | T3IE     | T2IE     | OC2IE    | IC2IE    | _        | T1IE    | OC1IE    | IC1IE    | INT0IE   | 0000          |

| IEC1         | 0096        | U2TXIE  | U2RXIE  | INT2IE   | T5IE    | T4IE    | OC4IE    | OC3IE    | _        | _        | _        | _        | INT1IE   | CNIE    | _        | MI2C1IE  | SI2C1IE  | 0000          |

| IEC2         | 0098        | _       | _       | -        | _       | _       | _        | _        | _        | _        | IC4IE    | IC3IE    | _        | -       | _        | SPI2IE   | SPI2EIE  | 0000          |

| IEC3         | 009A        | _       | _       | _        | _       | _       | QEI1IE   | PSEMIE   | _        | _        | INT4IE   | INT3IE   | _        | -       | MI2C2IE  | SI2C2IE  | _        | 0000          |

| IEC4         | 009C        | _       | —       | —        | —       | _       | _        | PSESMIE  | _        | —        | _        | —        | _        | _       | U2EIE    | U1EIE    | —        | 0000          |

| IEC5         | 009E        | PWM2IE  | PWM1IE  | ADCP12IE | —       | _       | _        | —        | _        | —        | _        | —        | _        | _       | _        | —        | —        | 0000          |

| IEC6         | 00A0        | _       | ADCP0IE | —        | —       | _       | _        | —        | _        | —        | _        | —        | _        | PWM6IE  | PWM5IE   | PWM4IE   | PWM3IE   | 0000          |

| IEC7         | 00A2        |         | _       | -        | _       | _       | _        | _        | _        | _        | _        | ADCP7IE  | ADCP6IE  | ADCP5IE | ADCP4IE  | ADCP3IE  | ADCP2IE  | 0000          |

| IPC0         | 00A4        |         | T1IP2   | T1IP1    | T1IP0   | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2   | IC1IP1   | IC1IP0   | -       | INT0IP2  | INT0IP1  | INT0IP0  | 4444          |

| IPC1         | 00A6        |         | T2IP2   | T2IP1    | T2IP0   | _       | OC2IP2   | OC2IP1   | OC2IP0   | _        | IC2IP2   | IC2IP1   | IC2IP0   | -       | _        | _        | _        | 4440          |

| IPC2         | 00A8        |         | U1RXIP2 | U1RXIP1  | U1RXIP0 | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 | -       | T3IP2    | T3IP1    | T3IP0    | 4444          |

| IPC3         | 00AA        |         | _       | -        | _       | _       | _        | _        | _        | _        | ADIP2    | ADIP1    | ADIP0    | -       | U1TXIP2  | U1TXIP1  | U1TXIP0  | 0044          |

| IPC4         | 00AC        | _       | CNIP2   | CNIP1    | CNIP0   | _       | _        | _        | _        | _        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | -       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 | 4444          |

| IPC5         | 00AE        | _       | _       | -        | _       | _       | _        | _        | _        | _        | _        | _        | _        | -       | INT1IP2  | INT1IP1  | INT1IP0  | 0004          |

| IPC6         | 00B0        | _       | T4IP2   | T4IP1    | T4IP0   | _       | OC4IP2   | OC4IP1   | OC4IP0   | _        | OC3IP2   | OC3IP1   | OC3IP0   | -       | _        | _        | _        | 4440          |

| IPC7         | 00B2        | _       | U2TXIP2 | U2TXIP1  | U2TXIP0 | _       | U2RXIP2  | U2RXIP1  | U2RXIP0  | _        | INT2IP2  | INT2IP1  | INT2IP0  | -       | T5IP2    | T5IP1    | T5IP0    | 4444          |

| IPC8         | 00B4        | _       | _       | _        | _       | _       | _        | _        | _        | _        | SPI2IP2  | SPI2IP1  | SPI2IP0  | -       | SPI2EIP2 | SPI2EIP1 | SPI2EIP0 | 0044          |

| IPC9         | 00B6        | _       | —       | —        | —       | _       | IC4IP2   | IC4IP1   | IC4IP0   | —        | IC3IP2   | IC3IP1   | IC3IP0   | _       | _        | —        | —        | 0440          |

| IPC12        | 00BC        | _       | —       | —        | —       | _       | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 | —        | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 | _       | _        | —        | —        | 0440          |

| IPC13        | 00BE        | —       | —       | —        | —       | _       | INT4IP2  | INT4IP1  | INT4IP0  | _        | INT3IP2  | INT3IP1  | INT3IP0  | _       | —        | _        | —        | 0440          |

| IPC14        | 00C0        | _       | —       | _        | _       | —       | QEI1IP2  | QEI1IP1  | QEI1IP0  | _        | PSEMIP2  | PSEMIP1  | PSEMIP0  | _       | —        | _        | —        | 0440          |

| IPC16        | 00C4        | _       | —       | _        | _       | —       | U2EIP2   | U2EIP1   | U2EIP0   | _        | U1EIP2   | U1EIP1   | U1EIP0   | —       | —        | _        | —        | 0440          |

| IPC18        | 00C8        | _       | —       | —        | —       | —       | —        | —        | —        | —        | PSESMIP2 | PSESMIP1 | PSESMIP0 | _       | —        | _        | —        | 0040          |

| IPC23        | 00D2        | _       | PWM2IP2 | PWM2IP1  | PWM2IP0 | _       | PWM1IP2  | PWM1IP1  | PWM1IP0  | _        | _        | _        | _        | _       | _        | _        | _        | 4400          |

#### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ32GS406 AND dsPIC33FJ64GS406 DEVICES

© 2009-2014 Microchip Technology Inc.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| ; | Set up NVMCO | N for row programming open  | rations                                 |

|---|--------------|-----------------------------|-----------------------------------------|

|   | MOV          | #0x4001, W0                 | ;                                       |

|   | MOV          | W0, NVMCON                  | ; Initialize NVMCON                     |

| ; | Set up a poi | nter to the first program   | memory location to be written           |

| ; | program memo | ry selected, and writes en  | nabled                                  |

|   | MOV          | #0x0000, W0                 | i                                       |

|   | MOV          | W0, TBLPAG                  | ; Initialize PM Page Boundary SFR       |

|   | MOV          | #0x6000, W0                 | ; An example program memory address     |

| ; | Perform the  | TBLWT instructions to writ  | te the latches                          |

| ; | 0th_program_ | word                        |                                         |

|   | MOV          | <pre>#LOW_WORD_0, W2</pre>  | ;                                       |

|   | MOV          | <pre>#HIGH_BYTE_0, W3</pre> | ;                                       |

|   | TBLWTL       | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                  | ; Write PM high byte into program latch |

| ; | lst_program_ | word                        |                                         |

|   | MOV          | #LOW_WORD_1, W2             | i                                       |

|   | MOV          | #HIGH_BYTE_1, W3            | i                                       |

|   | TBLWTL       | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                  | ; Write PM high byte into program latch |

| ; | 2nd_program  | _word                       |                                         |

|   | MOV          | #LOW_WORD_2, W2             | ;                                       |

|   | MOV          | <pre>#HIGH_BYTE_2, W3</pre> | ;                                       |

|   | TBLWTL       | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                  | ; Write PM high byte into program latch |

|   | •            |                             |                                         |

|   | •            |                             |                                         |

|   | •            |                             |                                         |

| ; | 63rd_program | _word                       |                                         |

|   | MOV          | #LOW_WORD_31, W2            | i                                       |

|   | MOV          | #HIGH_BYTE_31, W3           | i                                       |

|   | TBLWTL       | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                  | ; Write PM high byte into program latch |

| 1 |              |                             |                                         |

EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | ; Block all interrupts with priority <7 |

|------|-------------|-----------------------------------------|

|      |             | ; for next 5 instructions               |

| MOV  | #0x55, W0   |                                         |

| MOV  | W0, NVMKEY  | ; Write the 55 key                      |

| MOV  | #0xAA, W1   | i                                       |

| MOV  | W1, NVMKEY  | ; Write the AA key                      |

| BSET | NVMCON, #WR | ; Start the erase sequence              |

| NOP  |             | ; Insert two NOPs after the             |

| NOP  |             | ; erase command is asserted             |

|      |             |                                         |

| U-0          | U-0                                                                                                | U-0                                     | U-0        | U-0              | R/W-0            | R/W-0            | U-0 |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------|-----------------------------------------|------------|------------------|------------------|------------------|-----|--|--|--|--|

| _            | —                                                                                                  | _                                       | _          |                  | QEI1IE           | PSEMIE           | _   |  |  |  |  |

| bit 15       | ·                                                                                                  |                                         |            |                  |                  |                  | bit |  |  |  |  |

|              |                                                                                                    |                                         |            |                  |                  |                  |     |  |  |  |  |

| U-0          | R/W-0                                                                                              | R/W-0                                   | U-0        | U-0              | R/W-0            | R/W-0            | U-0 |  |  |  |  |

|              | INT4IE                                                                                             | INT3IE                                  |            | —                | MI2C2IE          | SI2C2IE          |     |  |  |  |  |

| bit 7        |                                                                                                    |                                         |            |                  |                  |                  | bit |  |  |  |  |

| Legend:      |                                                                                                    |                                         |            |                  |                  |                  |     |  |  |  |  |

| R = Readab   | le bit                                                                                             | W = Writable                            | bit        | U = Unimpler     | mented bit, read | l as '0'         |     |  |  |  |  |

| -n = Value a | t POR                                                                                              | '1' = Bit is set                        |            | '0' = Bit is cle |                  | x = Bit is unkno | own |  |  |  |  |

|              |                                                                                                    |                                         |            |                  |                  |                  |     |  |  |  |  |

| bit 15-11    | Unimplemen                                                                                         | ted: Read as '                          | כ'         |                  |                  |                  |     |  |  |  |  |

| bit 10       | QEI1IE: QEI1                                                                                       | QEI1IE: QEI1 Event Interrupt Enable bit |            |                  |                  |                  |     |  |  |  |  |

|              |                                                                                                    | request is enab                         |            |                  |                  |                  |     |  |  |  |  |

|              | •                                                                                                  | request is not e                        |            |                  |                  |                  |     |  |  |  |  |

| bit 9        |                                                                                                    | /M Special Ever                         |            | rupt Enable bit  | t                |                  |     |  |  |  |  |

|              |                                                                                                    | request is enab<br>request is not e     |            |                  |                  |                  |     |  |  |  |  |

| bit 8-7      |                                                                                                    | ited: Read as '                         |            |                  |                  |                  |     |  |  |  |  |

| bit 6        | -                                                                                                  |                                         |            |                  |                  |                  |     |  |  |  |  |

|              | INT4IE: External Interrupt 4 Enable bit<br>1 = Interrupt request is enabled                        |                                         |            |                  |                  |                  |     |  |  |  |  |

|              | 0 = Interrupt request is not enabled                                                               |                                         |            |                  |                  |                  |     |  |  |  |  |

| bit 6        | INT3IE: Exte                                                                                       | rnal Interrupt 3                        | Enable bit |                  |                  |                  |     |  |  |  |  |

|              |                                                                                                    | request is enab                         |            |                  |                  |                  |     |  |  |  |  |

|              |                                                                                                    | request is not e                        |            |                  |                  |                  |     |  |  |  |  |

| bit 4-3      | -                                                                                                  | ted: Read as '                          |            |                  |                  |                  |     |  |  |  |  |

| bit 2        |                                                                                                    | 2 Master Even                           |            | nable bit        |                  |                  |     |  |  |  |  |

|              | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                                         |            |                  |                  |                  |     |  |  |  |  |

| bit 1        | -                                                                                                  | 2 Slave Events                          |            | able bit         |                  |                  |     |  |  |  |  |

|              |                                                                                                    | request is enab                         | •          |                  |                  |                  |     |  |  |  |  |

|              | 0 = Interrupt                                                                                      |                                         |            |                  |                  |                  |     |  |  |  |  |

|              |                                                                                                    |                                         | liablea    |                  |                  |                  |     |  |  |  |  |

### REGISTER 7-16: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

## 9.4 Oscillator Control Registers

| U-0                 | R-y                                                                                        | R-y                                                                                                                                                 | R-y                                                                                       | U-0              | R/W-y                                       | R/W-y                                    | R/W-y                |

|---------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|---------------------------------------------|------------------------------------------|----------------------|

| _                   | COSC2                                                                                      | COSC1                                                                                                                                               | COSC0                                                                                     | _                | NOSC2 <sup>(2)</sup>                        | NOSC1 <sup>(2)</sup>                     | NOSCO <sup>(2)</sup> |

| bit 15              |                                                                                            |                                                                                                                                                     |                                                                                           |                  |                                             |                                          | bit                  |

|                     |                                                                                            |                                                                                                                                                     |                                                                                           |                  |                                             |                                          |                      |

| R/W-0               | U-0                                                                                        | R-0                                                                                                                                                 | U-0                                                                                       | R/C-0            | U-0                                         | U-0                                      | R/W-0                |

| CLKLOCK             | —                                                                                          | LOCK                                                                                                                                                |                                                                                           | CF               | _                                           | OSWEN                                    |                      |

| bit 7               |                                                                                            |                                                                                                                                                     |                                                                                           |                  |                                             |                                          | bit                  |

| Legend:             |                                                                                            | C = Clearable                                                                                                                                       | e bit                                                                                     | y = Value se     | t from Configura                            | tion bits on PO                          | R                    |

| R = Readable        | e bit                                                                                      | W = Writable                                                                                                                                        | bit                                                                                       | -                | mented bit, read                            |                                          |                      |

| -n = Value at       | POR                                                                                        | '1' = Bit is se                                                                                                                                     | t                                                                                         | '0' = Bit is cle | eared                                       | x = Bit is unkr                          | nown                 |

| bit 15<br>bit 14-12 | COSC<2:0>:<br>111 = Fast R                                                                 | nted: Read as<br>Current Oscill<br>C Oscillator (F<br>C Oscillator (F                                                                               | ator Selection<br>RC) with Divid                                                          | e-by-n           | /)                                          |                                          |                      |

|                     | 100 = Secon<br>011 = Primar<br>010 = Primar<br>001 = Fast R<br>000 = Fast R                | ower RC Oscil<br>dary Oscillator<br>y Oscillator (X<br>y Oscillator (X<br>C Oscillator (F<br>C Oscillator (F                                        | (SOSC)<br>T, HS, EC) with<br>T, HS, EC)<br>RC) with PLL<br>RC)                            | ו PLL            |                                             |                                          |                      |

| bit 11              | Unimplemen                                                                                 | nted: Read as                                                                                                                                       | 0'                                                                                        |                  |                                             |                                          |                      |

| bit 10-8            | NOSC<2:0>:                                                                                 | New Oscillato                                                                                                                                       | r Selection bits                                                                          | <sub>3</sub> (2) |                                             |                                          |                      |

|                     | 110 = Fast R<br>101 = Low-P<br>100 = Secon<br>011 = Primar<br>010 = Primar<br>001 = Fast R | C Oscillator (F<br>C Oscillator (F<br>ower RC Oscill<br>dary Oscillator<br>y Oscillator (X<br>y Oscillator (X<br>C Oscillator (F<br>C Oscillator (F | RC) with Divid<br>lator (LPRC)<br>(SOSC)<br>T, HS, EC) with<br>T, HS, EC)<br>RC) with PLL | e-by-16          |                                             |                                          |                      |

| bit 7               |                                                                                            | Clock Lock Ena                                                                                                                                      |                                                                                           |                  |                                             |                                          |                      |

|                     | 1 = Clock sw                                                                               | vitching is disat                                                                                                                                   | oled, system cl                                                                           | ock source is    | CKSM<1:0> (FC<br>locked<br>n be modified by | L. L |                      |

| bit 6               |                                                                                            | ted: Read as                                                                                                                                        |                                                                                           |                  |                                             |                                          | -                    |

| bit 5               | LOCK: PLL L                                                                                | _ock Status bit                                                                                                                                     | (read-only)                                                                               |                  |                                             |                                          |                      |

|                     | 1 = Indicates                                                                              | that PLL is in I                                                                                                                                    | ock or PLL sta                                                                            |                  | satisfied<br>progress or PLL                | is disabled                              |                      |

| bit 4               |                                                                                            | nted: Read as                                                                                                                                       |                                                                                           |                  | -                                           |                                          |                      |

|                     | rites to this regis<br>sPIC33/PIC24 F                                                      |                                                                                                                                                     |                                                                                           |                  | Oscillator (Par                             | t <b>IV)"</b> (DS7030                    | 7) in the            |

|                     |                                                                                            | -                                                                                                                                                   |                                                                                           |                  | th PLL and FRC                              | PII mode are                             | not permitte         |

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

| R/W-0         | R/W-0                           | R/W-0                               | R/W-0   | R/W-0             | R/W-0           | R/W-0                | U-0   |  |  |  |

|---------------|---------------------------------|-------------------------------------|---------|-------------------|-----------------|----------------------|-------|--|--|--|

| T5MD          | T4MD                            | T3MD                                | T2MD    | T1MD              | QEI1MD          | PWMMD <sup>(1)</sup> | _     |  |  |  |

| bit 15        |                                 |                                     |         |                   |                 |                      | bit   |  |  |  |

|               |                                 |                                     |         |                   |                 |                      |       |  |  |  |

| R/W-0         | R/W-0                           | R/W-0                               | R/W-0   | R/W-0             | U-0             | R/W-0                | R/W-0 |  |  |  |

| I2C1MD        | U2MD                            | U1MD                                | SPI2MD  | SPI1MD            | —               | C1MD                 | ADCMD |  |  |  |

| bit 7         |                                 |                                     |         |                   |                 |                      | bit   |  |  |  |

| Legend:       |                                 |                                     |         |                   |                 |                      |       |  |  |  |

| R = Readabl   | le bit                          | W = Writable                        | bit     | U = Unimplem      | nented bit, rea | d as '0'             |       |  |  |  |

| -n = Value at | t POR                           | '1' = Bit is set                    |         | '0' = Bit is clea | ared            | x = Bit is unkno     | own   |  |  |  |

|               |                                 |                                     |         |                   |                 |                      |       |  |  |  |

| bit 15        | T5MD: Timer                     | 5 Module Disal                      | ole bit |                   |                 |                      |       |  |  |  |

|               |                                 | odule is disable                    |         |                   |                 |                      |       |  |  |  |

|               |                                 | odule is enable                     |         |                   |                 |                      |       |  |  |  |

| bit 14        |                                 | 4 Module Disal                      |         |                   |                 |                      |       |  |  |  |

|               |                                 | odule is disable<br>odule is enable |         |                   |                 |                      |       |  |  |  |

| bit 13        |                                 | 3 Module Disat                      |         |                   |                 |                      |       |  |  |  |

|               |                                 | odule is disable                    |         |                   |                 |                      |       |  |  |  |

|               | 0 = Timer3 m                    | odule is enable                     | ed      |                   |                 |                      |       |  |  |  |

| bit 12        | T2MD: Timer2 Module Disable bit |                                     |         |                   |                 |                      |       |  |  |  |

|               |                                 | odule is disable<br>odule is enable |         |                   |                 |                      |       |  |  |  |

| bit 11        | T1MD: Timer                     | 1 Module Disat                      | ole bit |                   |                 |                      |       |  |  |  |

|               |                                 | odule is disable<br>odule is enable |         |                   |                 |                      |       |  |  |  |

| bit 10        | QEI1MD: QE                      | I1 Module Disa                      | ble bit |                   |                 |                      |       |  |  |  |

|               |                                 | dule is disabled                    |         |                   |                 |                      |       |  |  |  |

|               |                                 | dule is enabled                     | (1)     |                   |                 |                      |       |  |  |  |

| bit 9         |                                 | /M Module Disa                      |         |                   |                 |                      |       |  |  |  |

|               |                                 | dule is disabled<br>dule is enabled |         |                   |                 |                      |       |  |  |  |

| bit 8         | Unimplemen                      | ted: Read as '                      | 0'      |                   |                 |                      |       |  |  |  |

| bit 7         | 12C1MD: 12C                     | 1 Module Disat                      | ole bit |                   |                 |                      |       |  |  |  |

|               |                                 | lule is disabled<br>lule is enabled |         |                   |                 |                      |       |  |  |  |

| bit 6         | U2MD: UART                      | 2 Module Disa                       | ble bit |                   |                 |                      |       |  |  |  |

|               | -                               | odule is disabl<br>odule is enable  |         |                   |                 |                      |       |  |  |  |

| bit 5         | U1MD: UART                      | 1 Module Disa                       | ble bit |                   |                 |                      |       |  |  |  |

|               |                                 | odule is disabl<br>odule is enable  |         |                   |                 |                      |       |  |  |  |

| bit 4         |                                 | 2 Module Disa                       |         |                   |                 |                      |       |  |  |  |

| -             | 1 = SPI2 mod                    | lule is disabled                    |         |                   |                 |                      |       |  |  |  |

## REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** Once the PWM module is re-enabled (PWMMD is set to '1' and then set to '0'), all PWM registers must be re-initialized.

| U-0                               | U-0                                | U-0                                 | U-0            | U-0                                | R/W-0 | U-0              | U-0   |  |  |  |

|-----------------------------------|------------------------------------|-------------------------------------|----------------|------------------------------------|-------|------------------|-------|--|--|--|

| —                                 | —                                  | —                                   | —              | —                                  | CMPMD | —                | —     |  |  |  |

| bit 15                            |                                    |                                     |                |                                    |       |                  | bit 8 |  |  |  |

|                                   |                                    |                                     |                |                                    |       |                  |       |  |  |  |

| U-0                               | U-0                                | R/W-0                               | U-0            | U-0                                | U-0   | R/W-0            | U-0   |  |  |  |

| —                                 | —                                  | QEI2MD                              |                | —                                  | —     | I2C2MD           | —     |  |  |  |

| bit 7                             |                                    |                                     |                |                                    |       |                  | bit 0 |  |  |  |

|                                   |                                    |                                     |                |                                    |       |                  |       |  |  |  |

| Legend:                           |                                    |                                     |                |                                    |       |                  |       |  |  |  |

| R = Readable bit W = Writable bit |                                    |                                     |                | U = Unimplemented bit, read as '0' |       |                  |       |  |  |  |

| -n = Value a                      | -n = Value at POR '1' = Bit is set |                                     |                | '0' = Bit is clea                  | ared  | x = Bit is unkno | own   |  |  |  |

|                                   |                                    |                                     |                |                                    |       |                  |       |  |  |  |

| bit 15-11                         | Unimplemen                         | ted: Read as '                      | כ'             |                                    |       |                  |       |  |  |  |

| bit 10                            | CMPMD: Ana                         | alog Comparato                      | or Module Disa | ble bit                            |       |                  |       |  |  |  |

|                                   |                                    | omparator mode                      |                |                                    |       |                  |       |  |  |  |

| bit 9-6                           | Unimplemen                         | ted: Read as '                      | )'             |                                    |       |                  |       |  |  |  |

| bit 5                             | QEI2MD: QE                         | I2 Module Disa                      | ble bit        |                                    |       |                  |       |  |  |  |

|                                   |                                    | dule is disabled<br>dule is enabled |                |                                    |       |                  |       |  |  |  |

| bit 4-2                           | Unimplemen                         | ted: Read as '                      | )'             |                                    |       |                  |       |  |  |  |

| bit 1                             | -                                  | I2C2MD: I2C2 Module Disable bit     |                |                                    |       |                  |       |  |  |  |

|                                   | 1 = I2C2 mod                       | lule is disabled                    |                |                                    |       |                  |       |  |  |  |

|                                   | 0 = I2C2 mod                       | lule is enabled                     |                |                                    |       |                  |       |  |  |  |

| bit 0                             | Unimplemen                         | ted: Read as '                      | )'             |                                    |       |                  |       |  |  |  |

|                                   |                                    |                                     |                |                                    |       |                  |       |  |  |  |

### REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

#### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0                                                                                                                           | U-0                                                                     | U-0                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| —                                                                                                                             | —                                                                       | —                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                                                                                                               |                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                                                                                                               |                                                                         |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| U-0                                                                                                                           | U-0                                                                     | U-0                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| —                                                                                                                             | —                                                                       | _                                                                                                                                                                  | REFOMD                                                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ·                                                                                                                             | •                                                                       |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |