Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                      |

| Number of I/O              | 58                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs406-e-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

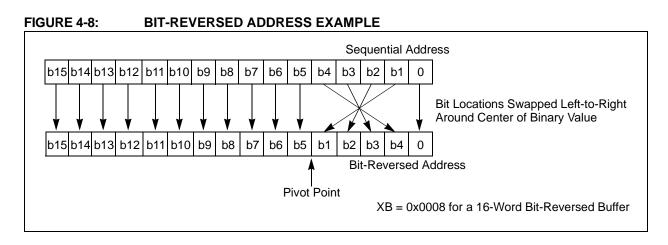

| TABLE | IABLE 4-67: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY) |       |           |         |                      |    |    |    |         |  |  |

|-------|------------------------------------------------------|-------|-----------|---------|----------------------|----|----|----|---------|--|--|

|       |                                                      | Norma | al Addres | SS      | Bit-Reversed Address |    |    |    | ldress  |  |  |

| A3    | A2                                                   | A1    | A0        | Decimal | A3                   | A2 | A1 | A0 | Decimal |  |  |

| 0     | 0                                                    | 0     | 0         | 0       | 0                    | 0  | 0  | 0  | 0       |  |  |

| 0     | 0                                                    | 0     | 1         | 1       | 1                    | 0  | 0  | 0  | 8       |  |  |

| 0     | 0                                                    | 1     | 0         | 2       | 0                    | 1  | 0  | 0  | 4       |  |  |

| 0     | 0                                                    | 1     | 1         | 3       | 1                    | 1  | 0  | 0  | 12      |  |  |

| 0     | 1                                                    | 0     | 0         | 4       | 0                    | 0  | 1  | 0  | 2       |  |  |

| 0     | 1                                                    | 0     | 1         | 5       | 1                    | 0  | 1  | 0  | 10      |  |  |

| 0     | 1                                                    | 1     | 0         | 6       | 0                    | 1  | 1  | 0  | 6       |  |  |

| 0     | 1                                                    | 1     | 1         | 7       | 1                    | 1  | 1  | 0  | 14      |  |  |

| 1     | 0                                                    | 0     | 0         | 8       | 0                    | 0  | 0  | 1  | 1       |  |  |

| 1     | 0                                                    | 0     | 1         | 9       | 1                    | 0  | 0  | 1  | 9       |  |  |

| 1     | 0                                                    | 1     | 0         | 10      | 0                    | 1  | 0  | 1  | 5       |  |  |

| 1     | 0                                                    | 1     | 1         | 11      | 1                    | 1  | 0  | 1  | 13      |  |  |

| 1     | 1                                                    | 0     | 0         | 12      | 0                    | 0  | 1  | 1  | 3       |  |  |

| 1     | 1                                                    | 0     | 1         | 13      | 1                    | 0  | 1  | 1  | 11      |  |  |

| 1     | 1                                                    | 1     | 0         | 14      | 0                    | 1  | 1  | 1  | 7       |  |  |

| 1     | 1                                                    | 1     | 1         | 15      | 1                    | 1  | 1  | 1  | 15      |  |  |

#### TABLE 4-67: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

| REGISTER /      | -3: INTCC                                                  | JN1: INTERR                                                                                                | UPICONIE        |                  | EKI              |                 |       |  |  |  |

|-----------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|-------|--|--|--|

| R/W-0           | R/W-0                                                      | R/W-0                                                                                                      | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| NSTDIS          | OVAERR                                                     | OVBERR                                                                                                     | COVAERR         | COVBERR          | OVATE            | OVBTE           | COVTE |  |  |  |

| bit 15          |                                                            |                                                                                                            |                 |                  |                  |                 | bit 8 |  |  |  |

| R/W-0           | R/W-0                                                      | R/W-0                                                                                                      | R/W-0           | R/W-0            | R/W-0            | R/W-0           | U-0   |  |  |  |

| SFTACERR        | DIV0ERR                                                    | DMACERR                                                                                                    | MATHERR         | ADDRERR          | STKERR           | OSCFAIL         | _     |  |  |  |

| bit 7           |                                                            |                                                                                                            |                 |                  |                  |                 | bit 0 |  |  |  |

| Legend:         |                                                            |                                                                                                            |                 |                  |                  |                 |       |  |  |  |

| R = Readable    | bit                                                        | W = Writable                                                                                               | bit             | U = Unimpler     | nented bit, read | d as '0'        |       |  |  |  |

| -n = Value at F | POR                                                        | '1' = Bit is set                                                                                           |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |

|                 |                                                            |                                                                                                            |                 |                  |                  |                 |       |  |  |  |

| bit 15          | NSTDIS: Inte                                               | errupt Nesting D                                                                                           | isable bit      |                  |                  |                 |       |  |  |  |

|                 |                                                            | nesting is disat                                                                                           |                 |                  |                  |                 |       |  |  |  |

|                 | •                                                          | nesting is enab                                                                                            |                 |                  |                  |                 |       |  |  |  |

| bit 14          |                                                            | ccumulator A O                                                                                             | -               | -                |                  |                 |       |  |  |  |

|                 |                                                            | caused by an                                                                                               |                 |                  | ^                |                 |       |  |  |  |

| hit 10          | -                                                          | not caused by                                                                                              |                 |                  | A                |                 |       |  |  |  |

| bit 13          |                                                            | <b>DVBERR:</b> Accumulator B Overflow Trap Flag bit<br>1 = Trap was caused by an overflow of Accumulator B |                 |                  |                  |                 |       |  |  |  |

|                 | •                                                          | not caused by an                                                                                           |                 |                  | В                |                 |       |  |  |  |

| bit 12          | -                                                          | Accumulator A                                                                                              |                 |                  |                  |                 |       |  |  |  |

|                 |                                                            | caused by a c                                                                                              |                 |                  |                  |                 |       |  |  |  |

|                 | 0 = Trap was                                               | not caused by                                                                                              | a catastrophic  | c overflow of A  | ccumulator A     |                 |       |  |  |  |

| bit 11          | COVBERR: Accumulator B Catastrophic Overflow Trap Flag bit |                                                                                                            |                 |                  |                  |                 |       |  |  |  |

|                 |                                                            | caused by a can be a caused by a caused by                                                                 |                 |                  |                  |                 |       |  |  |  |

| bit 10          | OVATE: Accu                                                | umulator A Ove                                                                                             | rflow Trap En   | able bit         |                  |                 |       |  |  |  |

|                 | 1 = Trap over<br>0 = Trap is di                            | rflow of Accum<br>isabled                                                                                  | ulator A        |                  |                  |                 |       |  |  |  |

| bit 9           | OVBTE: Acc                                                 | umulator B Ove                                                                                             | erflow Trap En  | able bit         |                  |                 |       |  |  |  |

|                 | 1 = Trap over<br>0 = Trap is di                            | rflow of Accum<br>isabled                                                                                  | ulator B        |                  |                  |                 |       |  |  |  |

| bit 8           | COVTE: Cata                                                | astrophic Overf                                                                                            | low Trap Enat   | ole bit          |                  |                 |       |  |  |  |

|                 | 1 = Trap on a<br>0 = Trap is di                            | a catastrophic c<br>isabled                                                                                | verflow of Acc  | cumulator A or   | B is enabled     |                 |       |  |  |  |

| bit 7           | SFTACERR:                                                  | Shift Accumula                                                                                             | tor Error State | us bit           |                  |                 |       |  |  |  |

|                 |                                                            | or trap was cau<br>or trap was not                                                                         | •               |                  |                  |                 |       |  |  |  |

| bit 6           | DIV0ERR: Ar                                                | rithmetic Error S                                                                                          | Status bit      |                  |                  |                 |       |  |  |  |

|                 |                                                            | or trap was cau<br>or trap was not                                                                         | •               | •                |                  |                 |       |  |  |  |

| bit 5           | DMACERR:                                                   | DMA Controller                                                                                             | Error Status    | bit              |                  |                 |       |  |  |  |

|                 |                                                            | ntroller error tra<br>ntroller error tra                                                                   |                 |                  |                  |                 |       |  |  |  |

| bit 4           |                                                            | Arithmetic Error                                                                                           |                 |                  |                  |                 |       |  |  |  |

|                 | 1 = Math erro                                              | or trap has occu<br>or trap has not o                                                                      | irred           |                  |                  |                 |       |  |  |  |

|                 |                                                            | •                                                                                                          |                 |                  |                  |                 |       |  |  |  |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit  |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 0 | INT0IF: External Interrupt 0 Flag Status bit              |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| REGISTER      | 7-13: IEC0:   | INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ENABLE CO       |                  | GISTER 0         |                 |        |

|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|--------|

| U-0           | R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| _             | DMA1IE        | ADIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U1TXIE          | U1RXIE           | SPI1IE           | SPI1EIE         | T3IE   |

| oit 15        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 | bi     |

| R/W-0         | R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T2IE          | OC2IE         | IC2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DMA0IE          | T1IE             | OC1IE            | IC1IE           | INTOIE |

| bit 7         |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 | bi     |

| Legend:       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 |        |

| R = Readabl   | le bit        | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | oit             | U = Unimpler     | nented bit, read | d as '0'        |        |

| -n = Value at |               | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | '0' = Bit is cle |                  | x = Bit is unkr | iown   |

|               |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 |        |

| bit 15        | Unimplemen    | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | )'              |                  |                  |                 |        |

| bit 14        | DMA1IE: DM    | A Channel 1 Da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ata Transfer C  | complete Interr  | upt Enable bit   |                 |        |

|               |               | request is enabl<br>request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                  |                  |                 |        |

| bit 13        | ADIE: ADC1    | Conversion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | mplete Interru  | pt Enable bit    |                  |                 |        |

|               |               | request is enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                  |                  |                 |        |

|               | -             | request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                  |                  |                 |        |

| pit 12        |               | RT1 Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | ible bit         |                  |                 |        |

|               |               | request is enabl<br>request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                  |                  |                 |        |

| bit 11        | •             | RT1 Receiver In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | e hit            |                  |                 |        |

|               | 1 = Interrupt | request is enabl<br>request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | led             |                  |                  |                 |        |

| bit 10        | -             | Event Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 |        |

|               |               | request is enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                  |                  |                 |        |

|               | -             | request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                  |                  |                 |        |

| bit 9         |               | 1 Event Interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 |        |

|               |               | request is enabl<br>request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                  |                  |                 |        |

| bit 8         | -             | Interrupt Enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 |        |

|               | 1 = Interrupt | request is enabling the request is not enabling the request is not enabling the request is not enabled to the request is not e | ed              |                  |                  |                 |        |