Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

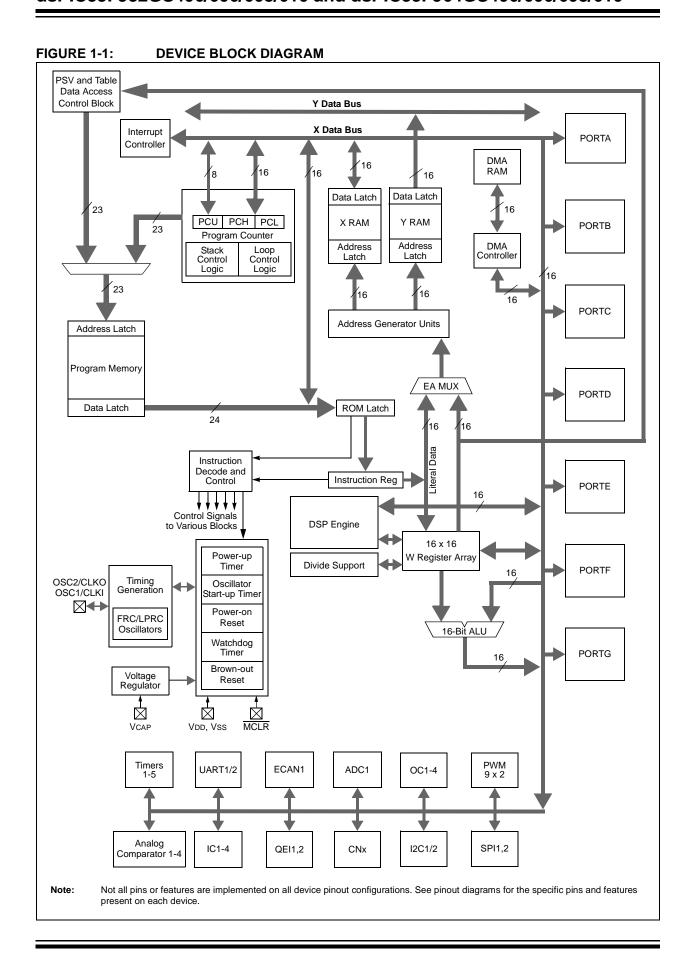

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                      |

| Number of I/O              | 58                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs406-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-32: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ32GS610 AND dsPIC33FJ64GS610 DEVICES ONLY (CONTINUED)

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                   | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------------------------|--------|--------|--------|--------|-------|----------|-------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ADCBUF22     | 036C        |        | ADC Data Buffer 22 xxxxx |        |        |        |        |       |          |             | xxxx  |       |       |       |       |       |       |               |

| ADCBUF23     | 036E        |        |                          |        |        |        |        |       | ADC Data | a Buffer 23 |       |       |       |       |       |       |       | xxxx          |

| ADCBUF24     | 0370        |        |                          |        |        |        |        |       | ADC Data | a Buffer 24 |       |       |       |       |       |       |       | xxxx          |

| ADCBUF25     | 0372        |        | ADC Data Buffer 25 xxxxx |        |        |        |        |       |          | xxxx        |       |       |       |       |       |       |       |               |

dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

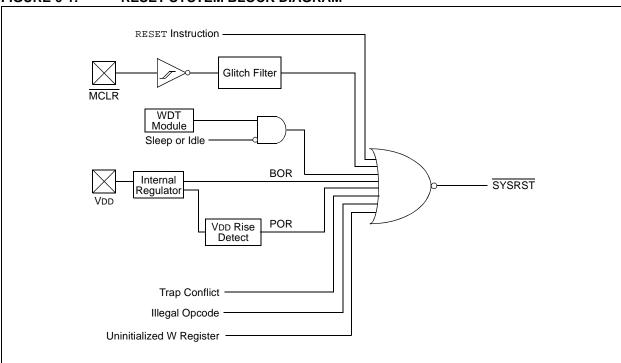

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

#### RCON: RESET CONTROL REGISTER(1) **REGISTER 6-1:**

| R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|--------|-----|-----|-----|-----|-----|-------|

| TRAPR  | IOPUWR | _   | _   | _   | _   | _   | VREGS |

| bit 15 |        |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0                 | R/W-0 | R/W-0 | R/W-0 | R/W-1 | R/W-1 |

|-------|-------|-----------------------|-------|-------|-------|-------|-------|

| EXTR  | SWR   | SWDTEN <sup>(2)</sup> | WDTO  | SLEEP | IDLE  | BOR   | POR   |

| bit 7 |       |                       |       |       |       |       | bit 0 |

Legend:

bit 5

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 TRAPR: Trap Reset Flag bit

1 = A Trap Conflict Reset has occurred

0 = A Trap Conflict Reset has not occurred

bit 14 IOPUWR: Illegal Opcode or Uninitialized W Access Reset Flag bit

1 = An illegal opcode detection, an illegal address mode or Uninitialized W register used as an

Address Pointer caused a Reset

0 = An Illegal Opcode or Uninitialized W Reset has not occurred

bit 13-9 Unimplemented: Read as '0'

bit 8 VREGS: Voltage Regulator Standby During Sleep bit

1 = Voltage regulator is active during Sleep

0 = Voltage regulator goes into Standby mode during Sleep

bit 7 EXTR: External Reset Pin (MCLR) bit

1 = A Master Clear (pin) Reset has occurred

0 = A Master Clear (pin) Reset has not occurred

bit 6 **SWR:** Software Reset Flag (Instruction) bit

> 1 = A RESET instruction has been executed 0 = A RESET instruction has not been executed

**SWDTEN:** Software Enable/Disable of WDT bit(2)

1 = WDT is enabled

0 = WDT is disabled

bit 4 WDTO: Watchdog Timer Time-out Flag bit

1 = WDT time-out has occurred

0 = WDT time-out has not occurred

bit 3 SLEEP: Wake-up from Sleep Flag bit

1 = Device has been in Sleep mode

0 = Device has not been in Sleep mode

IDLE: Wake-up from Idle Flag bit bit 2

1 = Device has been in Idle mode

0 = Device has not been in Idle mode

bit 1 BOR: Brown-out Reset Flag bit

1 = A Brown-out Reset has occurred

0 = A Brown-out Reset has not occurred

bit 0 POR: Power-on Reset Flag bit

1 = A Power-on Reset has occurred

0 = A Power-on Reset has not occurred

Note 1: All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### 6.4 External Reset (EXTR)

The External Reset is generated by driving the MCLR pin low. The MCLR pin is a Schmitt Trigger input with an additional glitch filter. Reset pulses that are longer than the minimum pulse width will generate a Reset. Refer to Section 27.0 "Electrical Characteristics" for minimum pulse width specifications. The External Reset (MCLR) pin (EXTR) bit in the Reset Control (RCON) register is set to indicate the MCLR Reset.

### 6.4.1 EXTERNAL SUPERVISORY CIRCUIT

Many systems have external supervisory circuits that generate Reset signals to reset multiple devices in the system. This external Reset signal can be directly connected to the MCLR pin to reset the device when the rest of system is reset.

#### 6.4.2 INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to reset the device, the External Reset pin (MCLR) should be tied directly or resistively to VDD. In this case, the MCLR pin will not be used to generate a Reset. The External Reset pin (MCLR) does not have an internal pull-up and must not be left unconnected.

#### 6.5 Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the device will assert SYSRST, placing the device in a special Reset state. This Reset state will not re-initialize the clock. The clock source in effect prior to the RESET instruction will remain. SYSRST is released at the next instruction cycle and the Reset vector fetch will commence.

The Software Reset (SWR) flag (instruction) in the Reset Control (RCON<6>) register is set to indicate the Software Reset.

## 6.6 Watchdog Timer Time-out Reset (WDTO)

Whenever a Watchdog Timer Time-out Reset occurs, the device will asynchronously assert SYSRST. The clock source will remain unchanged. A WDT time-out during Sleep or Idle mode will wake-up the processor, but will not reset the processor.

The Watchdog Timer Time-out (WDTO) flag in the Reset Control (RCON<4>) register is set to indicate the Watchdog Timer Reset. Refer to **Section 24.4** "Watchdog Timer (WDT)" for more information on the Watchdog Timer Reset.

#### 6.7 Trap Conflict Reset

If a lower priority hard trap occurs while a higher priority trap is being processed, a hard Trap Conflict Reset occurs. The hard traps include exceptions of Priority Level 13 through Level 15, inclusive. The address error (Level 13) and oscillator error (Level 14) traps fall into this category.

The Trap Reset (TRAPR) flag in the Reset Control (RCON<15>) register is set to indicate the Trap Conflict Reset. Refer to **Section 7.0** "Interrupt Controller" for more information on Trap Conflict Resets.

#### 6.8 Illegal Condition Device Reset

An illegal condition device Reset occurs due to the following sources:

- Illegal Opcode Reset

- · Uninitialized W Register Reset

- Security Reset

The Illegal Opcode or Uninitialized W Access Reset (IOPUWR) flag in the Reset Control (RCON<14>) register is set to indicate the illegal condition device Reset.

#### 6.8.1 ILLEGAL OPCODE RESET

A device Reset is generated if the device attempts to execute an illegal opcode value that is fetched from program memory.

The Illegal Opcode Reset function can prevent the device from executing program memory sections that are used to store constant data. To take advantage of the Illegal Opcode Reset, use only the lower 16 bits of each program memory section to store the data values. The upper 8 bits should be programmed with 3Fh, which is an illegal opcode value.

#### 6.8.2 UNINITIALIZED W REGISTER RESET

Any attempt to use the Uninitialized W register as an Address Pointer will reset the device. The W register array (with the exception of W15) is cleared during all Resets and is considered uninitialized until written to.

#### 6.8.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (Boot and Secure Segment), that operation will cause a Security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a call, jump, computed jump, return, return from subroutine or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an interrupt or trap vector.

Refer to Section 24.8 "Code Protection and CodeGuard™ Security" for more information on Security Reset.

#### REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | U-0   |

|--------|-----|-----|-----|-----|--------|--------|-------|

| _      | _   | _   | _   | _   | QEI1IF | PSEMIF | _     |

| bit 15 |     |     |     |     |        |        | bit 8 |

| U-0   | R/W-0  | R/W-0  | U-0 | U-0 | R/W-0   | R/W-0   | U-0   |

|-------|--------|--------|-----|-----|---------|---------|-------|

| _     | INT4IF | INT3IF | _   | _   | MI2C2IF | SI2C2IF | _     |

| bit 7 |        |        |     |     |         |         | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 Unimplemented: Read as '0'

bit 10 QEI1IF: QEI1 Event Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 9 PSEMIF: PWM Special Event Match Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 8-7 **Unimplemented:** Read as '0'

bit 6 INT4IF: External Interrupt 4 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 5 INT3IF: External Interrupt 3 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 4-3 **Unimplemented:** Read as '0'

bit 2 MI2C2IF: I2C2 Master Events Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 1 SI2C2IF: I2C2 Slave Events Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 **Unimplemented:** Read as '0'

#### REGISTER 16-21: FCLCONx: PWM FAULT CURRENT-LIMIT CONTROL x REGISTER (CONTINUED)

```

CLPOL: Current-Limit Polarity for PWM Generator # bit(1)

bit 9

1 = The selected current-limit source is active-low

0 = The selected current-limit source is active-high

bit 8

CLMOD: Current-Limit Mode Enable for PWM Generator # bit

1 = Current-Limit mode is enabled

0 = Current-Limit mode is disabled

FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator # bits(2,3)

bit 7-3

11111 = Reserved

11110 = Fault 23

11101 = Fault 22

11100 = Fault 21

11011 = Fault 20

11010 = Fault 19

11001 = Fault 18

11000 = Fault 17

10111 = Fault 16

10110 = Fault 15

10101 = Fault 14

10100 = Fault 13

10011 = Fault 12

10010 = Fault 11

10001 = Fault 10

10000 = Fault 9

01111 = Fault 8

01110 = Fault 7

01101 = Fault 6

01100 = Fault 5

01011 = Fault 4

01010 = Fault 3

01001 = Fault 2

01000 = Fault 1

00111 = Reserved

00110 = Reserved

00101 = Reserved

00100 = Reserved

00011 = Analog Comparator 4

00010 = Analog Comparator 3

00001 = Analog Comparator 2

00000 = Analog Comparator 1

FLTPOL: Fault Polarity for PWM Generator # bit<sup>(1)</sup>

bit 2

1 = The selected Fault source is active-low

0 = The selected Fault source is active-high

bit 1-0

FLTMOD<1:0>: Fault Mode for PWM Generator # bits

11 = Fault input is disabled

10 = Reserved

01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

```

- **Note 1:** These bits should be changed only when PTEN (PTCON<15>) = 0.

- 2: When Independent Fault mode is enabled (IFLTMOD = 1) and Fault 1 is used for Current-Limit mode (CLSRC<4:0> = b0000), the Fault Control Source Select bits (FLTSRC<4:0>) should be set to an unused Fault source to prevent Fault 1 from disabling both the PWMxL and PWMxH outputs.

- 3: When Independent Fault mode is enabled (IFLTMOD = 1) and Fault 1 is used for Fault mode (FLTSRC<4:0> = b0000), the Current-Limit Control Source Select bits (CLSRC<4:0>) should be set to an unused current-limit source to prevent the current-limit source from disabling both the PWMxH and PWMxL outputs.

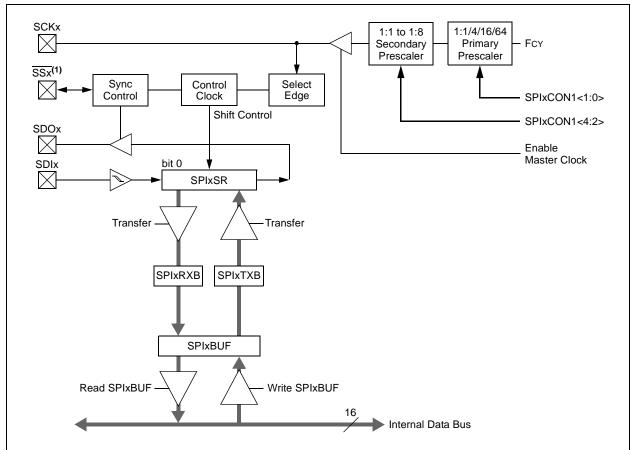

## 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/608/608/610 and dsPIC33FJ64GS406/608/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70005185) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters and so on. The SPI module is compatible with the Motorola® SPI and SIOP modules.

The SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of these four pins:

- SDIx (Serial Data Input)

- SDOx (Serial Data Output)

- SCKx (Shift Clock Input Or Output)

- SSx (Active-Low Slave Select)

In Master mode operation, SCK is a clock output; in Slave mode, it is a clock input.

#### FIGURE 18-1: SPIX MODULE BLOCK DIAGRAM

Note 1: The SPI1 module can be connected to the SS1 or ASS1 pins, which are controlled by clearing or setting the ALTSS1 bit in the FPOR Configuration register. See Section 24.0 "Special Features" for more information.

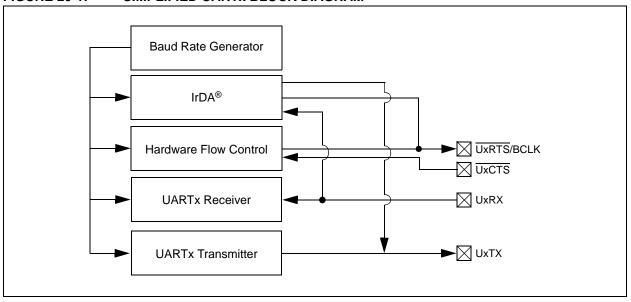

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/608/608/610 and dsPIC33FJ64GS406/608/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 device families. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/JS2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins and also includes an IrDA encoder and decoder.

The primary features of the UARTx module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 10 Mbps to 38 bps at 40 MIPS

- Baud Rates Ranging from 12.5 Mbps to 47 bps at 50 MIPS

- 4-Deep, First-In First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UART Error Conditions

- · Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA® Support

- Support for DMA

A simplified block diagram of the UART module is shown in Figure 20-1. The UART module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- · Asynchronous Receiver

FIGURE 20-1: SIMPLIFIED UARTX BLOCK DIAGRAM

## 21.0 ENHANCED CAN (ECAN™) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "ECAN™" (DS70185) in the dsPIC33/PIC24 Family Reference Manual, which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 21.1 Overview

The Enhanced Controller Area Network (ECAN<sup>TM</sup>) module is a serial interface, useful for communicating with other ECAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33FJ64GS606/608/610 devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN Protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- Standard and Extended Data Frames

- 0-8 Bytes Data Length

- Programmable Bit Rate, up to 1 Mbit/sec

- Automatic Response to Remote Transmission Requests

- Up to 8 Transmit Buffers with Application-Specified Prioritization and Abort Capability (each buffer can contain up to 8 bytes of data)

- Up to 32 Receive Buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 Full (Standard/Extended Identifier) Acceptance Filters

- Three Full Acceptance Filter Masks

- DeviceNet<sup>™</sup> Addressing Support

- Programmable Wake-up Functionality with Integrated Low-Pass Filter

- Programmable Loopback mode Supports Self-Test Operation

- Signaling via Interrupt Capabilities for all CAN Receiver and Transmitter Error States

- · Programmable Clock Source

- Programmable Link to Input Capture module (IC2 for CAN1) for Time-Stamping and Network Synchronization

- · Low-Power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

#### 21.2 Frame Types

The CAN module transmits various types of frames which include data messages, or remote transmission requests initiated by the user, as other frames that are automatically generated for control purposes. The following frame types are supported:

- Standard Data Frame: A standard data frame is generated by a node when the node wishes to transmit data. It includes an 11-bit Standard Identifier (SID), but not an 18-bit Extended Identifier (EID).

- Extended Data Frame: An extended data frame is similar to a standard data frame, but includes an Extended Identifier as well.

- Remote Frame: It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node sends a data frame as a response to this remote request.

- Error Frame: An error frame is generated by any node that detects a bus error. An error frame consists of two fields: an error flag field and an error delimiter field.

- Overload Frame: An overload frame can be generated by a node as a result of two conditions.

First, the node detects a dominant bit during interframe space which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node can generate a maximum of 2 sequential overload frames to delay the start of the next message.

- Interframe Space: Interframe space separates a proceeding frame (of whatever type) from a following data or remote frame.

#### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLTEN7 | FLTEN6 | FLTEN5 | FLTEN4 | FLTEN3 | FLTEN2 | FLTEN1 | FLTEN0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n0 = Disables Filter n

#### REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| F3BP3  | F3BP2 | F3BP1 | F3BP0 | F2BP3 | F2BP2 | F2BP1 | F2BP0 |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| F1BP3 | F1BP2 | F1BP1 | F1BP0 | F0BP3 | F0BP2 | F0BP1 | F0BP0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 F3BP<3:0>: RX Buffer Mask for Filter 3 bits

1111 = Filter hits received in RX FIFO buffer 1110 = Filter hits received in RX Buffer 14

TITO = LINEL LINS LECEIVED III KY DO

•

•

0001 = Filter hits received in RX Buffer 1 0000 = Filter hits received in RX Buffer 0

bit 11-8 **F2BP<3:0>:** RX Buffer Mask for Filter 2 bits (same values as bits<15:12>) bit 7-4 **F1BP<3:0>:** RX Buffer Mask for Filter 1 bits (same values as bits<15:12>)

bit 3-0 F0BP<3:0>: RX Buffer Mask for Filter 0 bits (same values as bits<15:12>)

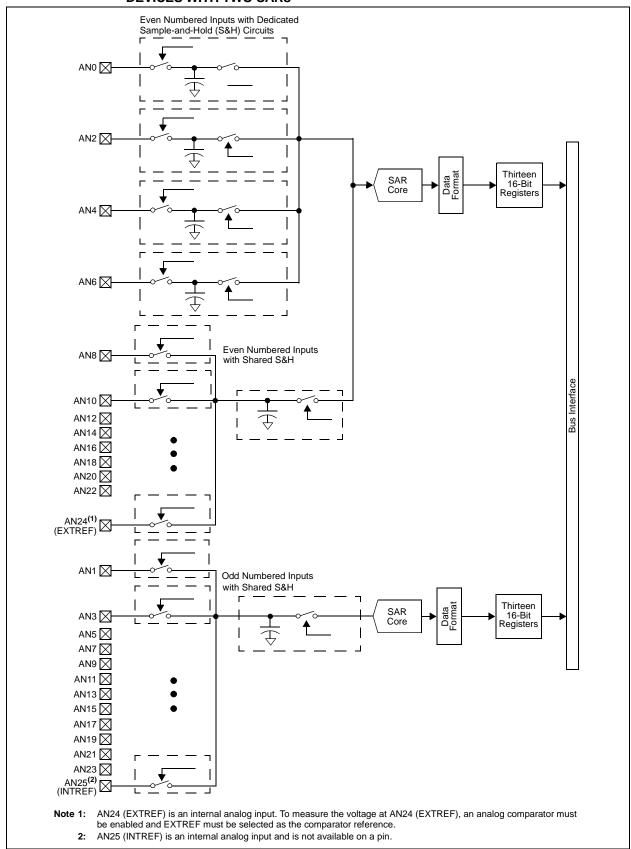

**DEVICES WITH TWO SARs** Even Numbered Inputs with Dedicated Sample-and-Hold (S&H) Circuits AN0 AN2 Ten SAR Core 16-Bit Registers AN4 AN6 🔀 Even Numbered Inputs AN8 with Shared S&H AN10 AN12 AN14 🔀 AN16 AN24<sup>(1)</sup> (EXTREF) AN1 🛛 Odd Numbered Inputs with Shared S&H Data Format Ten SAR AN3 X 16-Bit Core Registers AN5 AN7 X AN9 🗙 AN11 🗙

AN24 (EXTREF) is an internal analog input. To measure the voltage at AN24 (EXTREF), an analog comparator must be

enabled and EXTREF must be selected as the comparator reference. AN25 (INTREF) is an internal analog input and is not available on a pin.

FIGURE 22-3: ADC BLOCK DIAGRAM FOR dsPIC33FJ32GS608 AND dsPIC33FJ64GS608

AN13 ⊠ AN15 ⊠ AN17 ⊠

AN25<sup>(2)</sup> (INTREF)

#### REGISTER 22-6: ADCPC0: ADC CONVERT PAIR CONTROL REGISTER 0 (CONTINUED)

bit 4-0 TRGSRC0<4:0>: Trigger 0 Source Selection bits Selects trigger source for conversion of Analog Channels AN1 and AN0. 11111 = Timer2 period match 11110 = PWM Generator 8 current-limit ADC trigger 11101 = PWM Generator 7 current-limit ADC trigger 11100 = PWM Generator 6 current-limit ADC trigger 11011 = PWM Generator 5 current-limit ADC trigger 11010 = PWM Generator 4 current-limit ADC trigger 11001 = PWM Generator 3 current-limit ADC trigger 11000 = PWM Generator 2 current-limit ADC trigger 10111 = PWM Generator 1 current-limit ADC trigger 10110 = PWM Generator 9 secondary trigger is selected 10101 = PWM Generator 8 secondary trigger is selected 10100 = PWM Generator 7 secondary trigger is selected 10011 = PWM Generator 6 secondary trigger is selected 10010 = PWM Generator 5 secondary trigger is selected 10001 = PWM Generator 4 secondary trigger is selected 10000 = PWM Generator 3 secondary trigger is selected 01111 = PWM Generator 2 secondary trigger is selected 01110 = PWM Generator 1 secondary trigger is selected 01101 = PWM secondary Special Event Trigger is selected 01100 = Timer1 period match 01011 = PWM Generator 8 primary trigger is selected 01010 = PWM Generator 7 primary trigger is selected 01001 = PWM Generator 6 primary trigger is selected 01000 = PWM Generator 5 primary trigger is selected 00111 = PWM Generator 4 primary trigger is selected 00110 = PWM Generator 3 primary trigger is selected 00101 = PWM Generator 2 primary trigger is selected 00100 = PWM Generator 1 primary trigger is selected 00011 = PWM Special Event Trigger is selected 00010 = Global software trigger is selected

00001 = Individual software trigger is selected

00000 = No conversion is enabled

**Note 1:** The trigger source must be set as an individual software trigger prior to setting this bit to '1'. If other conversions are in progress, the conversion is performed when the conversion resources are available.

#### 24.0 SPECIAL FEATURES

# Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest "dsPIC33/PIC24 Family Reference Manual" sections. The information in this data sheet supersedes the information in the FRM.

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- · Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- · JTAG Boundary Scan Interface

- In-Circuit Serial Programming™ (ICSP™)

- In-Circuit Emulation

- Brown-out Reset (BOR)

#### 24.1 Configuration Bits

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices provide non-volatile memory implementations for device Configuration bits. Refer to "Device Configuration" (DS70194) in the "dsPIC33/PIC24 Family Reference Manual" for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 24-2.

Note that address, 0xF80000, is beyond the user program memory space. It belongs to the configuration memory space (0x800000-0xFFFFFF), which can only be accessed using Table Reads and Table Writes.

To prevent inadvertent configuration changes during code execution, all programmable Configuration bits are write-once. After a bit is initially programmed during a power cycle, it cannot be written again. Changing a device configuration requires that power to the device be cycled.

The device Configuration register map is shown in Table 24-1.

TABLE 24-1: DEVICE CONFIGURATION REGISTER MAP

| Address  | Name     | Bit 7                   | Bit 6                   | Bit 5                  | Bit 4  | Bit 3                | Bit 2                  | Bit 1   | Bit 0                |

|----------|----------|-------------------------|-------------------------|------------------------|--------|----------------------|------------------------|---------|----------------------|

| 0xF80000 | FBS      | _                       | _                       | _                      | _      |                      | BSS<2:0>               |         | BWRP                 |

| 0xF80002 | RESERVED | _                       | _                       | _                      | _      | _                    | _                      | _       | _                    |

| 0xF80004 | FGS      | _                       | _                       | _                      | _      | _                    | GSS<1:                 | 0>      | GWRP                 |

| 0xF80006 | FOSCSEL  | IESO                    | -                       | 1                      | _      | -                    | FNO                    | SC<2:0> |                      |

| 0xF80008 | FOSC     | FCKSM                   | M<1:0>                  | 1                      | _      | -                    | OSCIOFNC               | POSCM   | 1D<1:0>              |

| 0xF8000A | FWDT     | FWDTEN                  | WINDIS                  | _                      | WDTPRE |                      | WDTPOST                | <3:0>   |                      |

| 0xF8000C | FPOR     | _                       | ALTQIO                  | ALTSS1                 | _      | _                    | FPW                    | RT<2:0> |                      |

| 0xF8000E | FICD     | Reserved <sup>(1)</sup> | Reserved <sup>(1)</sup> | JTAGEN                 | _      |                      | _                      | ICS<    | :1:0>                |

| 0xF80010 | FCMP     | _                       | _                       | CMPPOL1 <sup>(2)</sup> | HYST1< | :1:0> <sup>(2)</sup> | CMPPOL0 <sup>(2)</sup> | HYST0   | <1:0> <sup>(2)</sup> |

**Legend:** — = unimplemented bit, read as '0'.

Note 1: These bits are reserved for use by development tools and must be programmed as '1'.

2: These bits are reserved on dsPIC33FJXXXGS406 devices and always read as '1'.

#### 26.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 26.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 26.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 26.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 26.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 26.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 26.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 26.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 26.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

| CxFMSKSEL2 (ECANx Filter 15-8 Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   | IPC16 (Interrupt Priority Control 16)                                                                                                                                | . 165                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Selection 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 304                                                                                                                               | IPC17 (Interrupt Priority Control 17)                                                                                                                                | . 166                                                                                                                               |

| CxINTE (ECANx Interrupt Enable)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 295                                                                                                                               | IPC18 (Interrupt Priority Control 18)                                                                                                                                | . 167                                                                                                                               |

| CxINTF (ECANx Interrupt Flag)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 293                                                                                                                               | IPC2 (Interrupt Priority Control 2)                                                                                                                                  | . 154                                                                                                                               |

| CxRXFnEID (ECANx Acceptance Filter n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   | IPC20 (Interrupt Priority Control 20)                                                                                                                                | . 168                                                                                                                               |

| Extended Identifier)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 303                                                                                                                               | IPC21 (Interrupt Priority Control 21)                                                                                                                                | . 169                                                                                                                               |

| CxRXFnSID (ECANx Acceptance Filter n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   | IPC23 (Interrupt Priority Control 23)                                                                                                                                | . 170                                                                                                                               |

| Standard Identifier)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 302                                                                                                                               | IPC24 (Interrupt Priority Control 24)                                                                                                                                | . 171                                                                                                                               |

| CxRXFUL1 (ECANx Receive Buffer Full 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   | IPC25 (Interrupt Priority Control 25)                                                                                                                                |                                                                                                                                     |

| CxRXFUL2 (ECANx Receive Buffer Full 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   | IPC26 (Interrupt Priority Control 26)                                                                                                                                |                                                                                                                                     |

| CxRXMnEID (ECANx Acceptance Filter Mask n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                   | IPC27 (Interrupt Priority Control 27)                                                                                                                                |                                                                                                                                     |

| Extended Identifier)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 305                                                                                                                               | IPC28 (Interrupt Priority Control 28)                                                                                                                                |                                                                                                                                     |

| CxRXMnSID (ECANx Acceptance Filter Mask n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                   | IPC29 (Interrupt Priority Control 29)                                                                                                                                |                                                                                                                                     |

| Standard Identifier)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 305                                                                                                                               | IPC3 (Interrupt Priority Control 3)                                                                                                                                  |                                                                                                                                     |

| CxRXOVF1 (ECANx Receive Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   | IPC4 (Interrupt Priority Control 4)                                                                                                                                  |                                                                                                                                     |

| Overflow 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 307                                                                                                                               | IPC5 (Interrupt Priority Control 5)                                                                                                                                  |                                                                                                                                     |

| CxRXOVF2 (ECANx Receive Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   | IPC6 (Interrupt Priority Control 6)                                                                                                                                  |                                                                                                                                     |

| Overflow 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 307                                                                                                                               | IPC7 (Interrupt Priority Control 7)                                                                                                                                  |                                                                                                                                     |

| CxTRmnCON (ECANx TX/RX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 007                                                                                                                               | IPC8 (Interrupt Priority Control 8)                                                                                                                                  |                                                                                                                                     |

| Buffer mn Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 308                                                                                                                               | IPC9 (Interrupt Priority Control 9)                                                                                                                                  |                                                                                                                                     |

| CxVEC (ECANx Interrupt Code)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   | LEBCONx (Leading-Edge Blanking Control x)                                                                                                                            |                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                   | , , ,                                                                                                                                                                |                                                                                                                                     |

| DFLTxCON (Digital Filter x Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                   | LEBDLYx (Leading-Edge Blanking Delay x)                                                                                                                              |                                                                                                                                     |

| DMACS0 (DMA Controller Status 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   | MDC (PWM Master Duty Cycle)                                                                                                                                          |                                                                                                                                     |

| DMACS1 (DMA Controller Status 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   | NVMCON (Flash Memory Control)                                                                                                                                        |                                                                                                                                     |

| DMAxCNT (DMA Channel x Transfer Count)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   | NVMKEY (Nonvolatile Memory Key)                                                                                                                                      |                                                                                                                                     |

| DMAxCON (DMA Channel x Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 181                                                                                                                               | OCxCON (Output Compare x Control, x = 1-4)                                                                                                                           |                                                                                                                                     |

| DMAxPAD (DMA Channel x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   | OSCCON (Oscillator Control)                                                                                                                                          |                                                                                                                                     |

| Peripheral Address)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                   | OSCTUN (Oscillator Tuning)                                                                                                                                           |                                                                                                                                     |

| DMAxREQ (DMA Channel x IRQ Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 182                                                                                                                               | PDCx (PWM Generator Duty Cycle x)                                                                                                                                    |                                                                                                                                     |

| DMAxSTA (DMA Channel x RAM Start Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   | PHASEx (PWM Primary Phase-Shift x)                                                                                                                                   |                                                                                                                                     |