Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 50 MIPs                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, QEI, POR, PWM, WDT                                         |

| Number of I/O              | 58                                                                                 |

| Program Memory Size        | 64KB (64K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                |                                                                                    |

| RAM Size                   | 8K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 16x10b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 64-TQFP                                                                            |

| Supplier Device Package    | 64-TQFP (10x10)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs406t-50i-pt |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

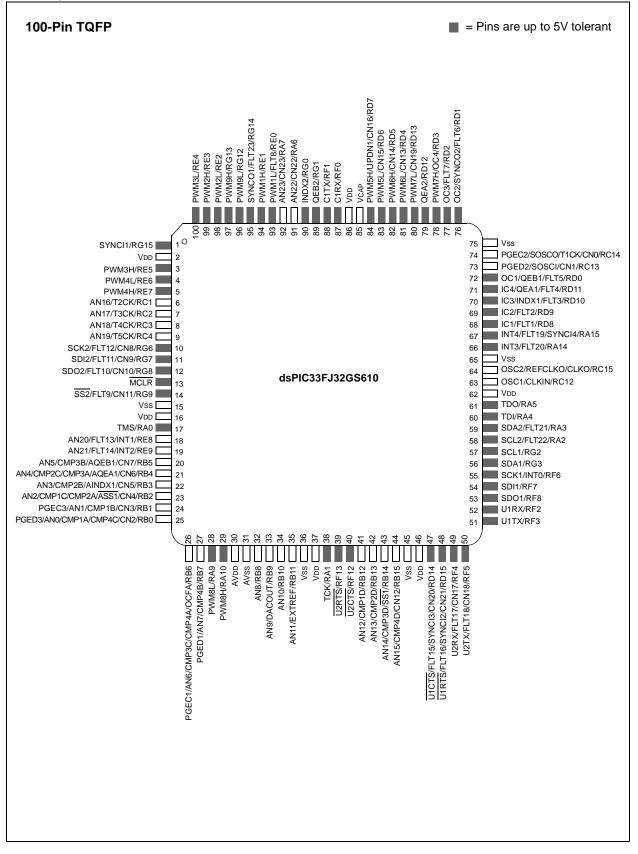

### Pin Diagrams (Continued)

| Pin Name                                | Pin<br>Type | Buffer<br>Type | Description                                                                |

|-----------------------------------------|-------------|----------------|----------------------------------------------------------------------------|

| FLT1-FLT23                              | I           | ST             | Fault inputs to PWM module.                                                |

| SYNCI1-SYNCI4                           | I           | ST             | External synchronization signal to PWM master time base.                   |

| SYNCO1-SYNCO2                           | 0           | —              | PWM master time base for external device synchronization.                  |

| PWM1L                                   | 0           | —              | PWM1 low output.                                                           |

| PWM1H                                   | 0           | —              | PWM1 high output.                                                          |

| PWM2L                                   | 0           | —              | PWM2 low output.                                                           |

| PWM2H                                   | 0           | —              | PWM2 high output.                                                          |

| PWM3L                                   | 0           | —              | PWM3 low output.                                                           |

| PWM3H                                   | 0           | —              | PWM3 high output.                                                          |

| PWM4L                                   | 0           | —              | PWM4 low output.                                                           |

| PWM4H                                   | 0           | —              | PWM4 high output.                                                          |

| PWM5L                                   | 0           | —              | PWM5 low output.                                                           |

| PWM5H                                   | 0           | —              | PWM5 high output.                                                          |

| PWM6L                                   | 0           | —              | PWM6 low output.                                                           |

| PWM6H                                   | 0           | —              | PWM6 high output.                                                          |

| PWM7L                                   | 0           | —              | PWM7 low output.                                                           |

| PWM7H                                   | 0           | —              | PWM7 high output.                                                          |

| PWM8L                                   | 0           | —              | PWM8 low output.                                                           |

| PWM8H                                   | 0           | —              | PWM8 high output.                                                          |

| PWM9L                                   | 0           | —              | PWM9 low output.                                                           |

| PWM9H                                   | 0           | —              | PWM9 high output.                                                          |

| PGED1                                   | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 1.            |

| PGEC1                                   | I           | ST             | Clock input pin for Programming/Debugging Communication Channel            |

| PGED2                                   | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 2.            |

| PGEC2                                   | I           | ST             | Clock input pin for Programming/Debugging Communication Channel            |

| PGED3                                   | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 3.            |

| PGEC3                                   | I           | ST             | Clock input pin for Programming/Debugging Communication Channel            |

| MCLR                                    | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device. |

| AVDD                                    | Р           | P              | Positive supply for analog modules.                                        |

| AVSS                                    | Р           | Р              | Ground reference for analog modules.                                       |

| /DD                                     | Р           | —              | Positive supply for peripheral logic and I/O pins.                         |

| √CAP                                    | Р           | —              | CPU logic filter capacitor connection.                                     |

| /ss                                     | Р           | —              | Ground reference for logic and I/O pins.                                   |

| <b>_egend:</b> CMOS = CM<br>ST = Schmit |             |                |                                                                            |

| TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS (</b> |            |

|------------|----------------------------------|------------|

| TADLE IT.  | FINOUT #O DESCRIFTIONS (         | CONTINUED) |

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-Transistor Logic P = Power

© 2009-2014 Microchip Technology Inc.

The SA and SB bits are modified each time data passes through the adder/subtracter, but can only be cleared by the user application. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow and thus, indicate that a cata-strophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The Overflow and Saturation Status bits can optionally be viewed in the STATUS Register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). Programmers can check one bit in the STATUS Register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This is useful for complex number arithmetic, which typically uses both accumulators.

The device supports three Saturation and Overflow modes:

- Bit 39 Overflow and Saturation:

- When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFF) or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. This condition is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (such as gain calculations).

- Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF) or maximally negative 1.31 value (0x008000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. When this Saturation mode is in effect, the guard bits are not used, so the OA, OB or OAB bits are never set.

- Bit 39 Catastrophic Overflow:

The bit 39 Overflow Status bit from the adder is used to set the SA or SB bit, which remains set until cleared by the user application. No saturation operation is performed, and the accumulator is allowed to overflow, destroying its sign. If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

### 3.6.3 ACCUMULATOR 'WRITE-BACK'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

• W13, Register Direct:

The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

• [W13] + = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

### 3.6.3.1 Round Logic

The round logic is a combinational block that performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value that is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word is simply discarded.

Conventional rounding zero-extends bit 15 of the accumulator and adds it to the ACCxH word (bits 16 through 31 of the accumulator).

- If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented.

- If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged.

A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. In this case, the Least Significant bit (bit 16 of the accumulator) of ACCxH is examined:

- If it is '1', ACCxH is incremented.

- If it is '0', ACCxH is not modified.

Assuming that bit 16 is effectively random in nature, this scheme removes any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see Section 3.6.3.2 "Data Space Write Saturation"). For the MAC class of instructions, the accumulator write-back operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13   | Bit 12  | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|---------|---------|----------|---------|---------|----------|----------|----------|----------|----------|----------|----------|---------|----------|----------|----------|---------------|

| INTCON1      | 0080        | NSTDIS  | OVAERR  | OVBERR   | COVAERR | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  | _        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | —        | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI    | _        | _       | _       |          | —        |          | _        | _        | —        | INT4EP   | INT3EP  | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0         | 0084        | _       | —       | ADIF     | U1TXIF  | U1RXIF  | SPI1IF   | SPI1EIF  | T3IF     | T2IF     | OC2IF    | IC2IF    | —        | T1IF    | OC1IF    | IC1IF    | INTOIF   | 0000          |

| IFS1         | 0086        | U2TXIF  | U2RXIF  | INT2IF   | T5IF    | T4IF    | OC4IF    | OC3IF    |          | _        | _        | —        | INT1IF   | CNIF    |          | MI2C1IF  | SI2C1IF  | 0000          |

| IFS2         | 0088        | _       | _       | -        | _       | _       | _        | _        | _        | _        | IC4IF    | IC3IF    | _        | -       | _        | SPI2IF   | SPI2EIF  | 0000          |

| IFS3         | 008A        | _       | _       | -        | _       | _       | QEI1IF   | PSEMIF   | _        | _        | INT4IF   | INT3IF   | _        | -       | MI2C2IF  | SI2C2IF  | _        | 0000          |

| IFS4         | 008C        | _       | _       | -        | _       | _       | _        | PSESMIF  | _        | _        | _        | _        | _        | -       | U2EIF    | U1EIF    | _        | 0000          |

| IFS5         | 008E        | PWM2IF  | PWM1IF  | ADCP12IF | _       | _       | _        | _        | _        | _        | _        | _        | _        | -       | _        | _        | _        | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF | -        | _       | _       | _        | _        | _        | _        | _        | _        | _        | PWM6IF  | PWM5IF   | PWM4IF   | PWM3IF   | 0000          |

| IFS7         | 0092        | _       | _       | -        | _       | _       | _        | _        | _        | _        | _        | ADCP7IF  | ADCP6IF  | ADCP5IF | ADCP4IF  | ADCP3IF  | ADCP2IF  | 0000          |

| IEC0         | 0094        | _       | _       | ADIE     | U1TXIE  | U1RXIE  | SPI1IE   | SPI1EIE  | T3IE     | T2IE     | OC2IE    | IC2IE    | _        | T1IE    | OC1IE    | IC1IE    | INT0IE   | 0000          |

| IEC1         | 0096        | U2TXIE  | U2RXIE  | INT2IE   | T5IE    | T4IE    | OC4IE    | OC3IE    | _        | _        | _        | _        | INT1IE   | CNIE    | _        | MI2C1IE  | SI2C1IE  | 0000          |

| IEC2         | 0098        | _       | _       | -        | _       | _       | _        | _        | _        | _        | IC4IE    | IC3IE    | _        | -       | _        | SPI2IE   | SPI2EIE  | 0000          |

| IEC3         | 009A        | _       | _       | _        | _       | _       | QEI1IE   | PSEMIE   | _        | _        | INT4IE   | INT3IE   | _        | -       | MI2C2IE  | SI2C2IE  | _        | 0000          |

| IEC4         | 009C        | _       | —       | —        | —       | _       | _        | PSESMIE  | _        | —        | _        | —        | _        | _       | U2EIE    | U1EIE    | —        | 0000          |

| IEC5         | 009E        | PWM2IE  | PWM1IE  | ADCP12IE | —       | _       | _        | —        | _        | —        | _        | —        | _        | _       | _        | —        | —        | 0000          |

| IEC6         | 00A0        | _       | ADCP0IE | —        | —       | _       | _        | —        | _        | —        | _        | —        | _        | PWM6IE  | PWM5IE   | PWM4IE   | PWM3IE   | 0000          |

| IEC7         | 00A2        |         | _       | -        | _       | _       | _        | _        | _        | _        | _        | ADCP7IE  | ADCP6IE  | ADCP5IE | ADCP4IE  | ADCP3IE  | ADCP2IE  | 0000          |

| IPC0         | 00A4        |         | T1IP2   | T1IP1    | T1IP0   | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2   | IC1IP1   | IC1IP0   | -       | INT0IP2  | INT0IP1  | INT0IP0  | 4444          |

| IPC1         | 00A6        |         | T2IP2   | T2IP1    | T2IP0   | _       | OC2IP2   | OC2IP1   | OC2IP0   | _        | IC2IP2   | IC2IP1   | IC2IP0   | -       | _        | _        | _        | 4440          |

| IPC2         | 00A8        |         | U1RXIP2 | U1RXIP1  | U1RXIP0 | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 | -       | T3IP2    | T3IP1    | T3IP0    | 4444          |

| IPC3         | 00AA        |         | _       | -        | _       | _       | _        | _        | _        | _        | ADIP2    | ADIP1    | ADIP0    | -       | U1TXIP2  | U1TXIP1  | U1TXIP0  | 0044          |

| IPC4         | 00AC        | _       | CNIP2   | CNIP1    | CNIP0   | _       | _        | _        | _        | _        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | -       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 | 4444          |

| IPC5         | 00AE        | _       | _       | -        | _       | _       | _        | _        | _        | _        | _        | _        | _        | -       | INT1IP2  | INT1IP1  | INT1IP0  | 0004          |

| IPC6         | 00B0        | _       | T4IP2   | T4IP1    | T4IP0   | _       | OC4IP2   | OC4IP1   | OC4IP0   | _        | OC3IP2   | OC3IP1   | OC3IP0   | -       | _        | _        | _        | 4440          |

| IPC7         | 00B2        | _       | U2TXIP2 | U2TXIP1  | U2TXIP0 | _       | U2RXIP2  | U2RXIP1  | U2RXIP0  | _        | INT2IP2  | INT2IP1  | INT2IP0  | -       | T5IP2    | T5IP1    | T5IP0    | 4444          |

| IPC8         | 00B4        | _       | _       | _        | _       | _       | _        | _        | _        | _        | SPI2IP2  | SPI2IP1  | SPI2IP0  | -       | SPI2EIP2 | SPI2EIP1 | SPI2EIP0 | 0044          |

| IPC9         | 00B6        | _       | —       | —        | —       | _       | IC4IP2   | IC4IP1   | IC4IP0   | —        | IC3IP2   | IC3IP1   | IC3IP0   | _       | _        | —        | —        | 0440          |

| IPC12        | 00BC        | _       | —       | —        | —       | _       | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 | —        | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 | _       | _        | —        | —        | 0440          |

| IPC13        | 00BE        | —       | —       | —        | —       | _       | INT4IP2  | INT4IP1  | INT4IP0  | _        | INT3IP2  | INT3IP1  | INT3IP0  | _       | —        | —        | —        | 0440          |

| IPC14        | 00C0        | _       | —       | _        | _       | —       | QEI1IP2  | QEI1IP1  | QEI1IP0  | _        | PSEMIP2  | PSEMIP1  | PSEMIP0  | _       | —        | _        | —        | 0440          |

| IPC16        | 00C4        | _       | —       | _        | _       | —       | U2EIP2   | U2EIP1   | U2EIP0   | —        | U1EIP2   | U1EIP1   | U1EIP0   | —       | —        | —        | —        | 0440          |

| IPC18        | 00C8        | _       | —       | —        | —       | —       | —        | —        | —        | —        | PSESMIP2 | PSESMIP1 | PSESMIP0 | _       | —        | _        | —        | 0040          |

| IPC23        | 00D2        | _       | PWM2IP2 | PWM2IP1  | PWM2IP0 | _       | PWM1IP2  | PWM1IP1  | PWM1IP0  | _        | _        | _        | _        | _       | _        | _        | _        | 4400          |

#### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ32GS406 AND dsPIC33FJ64GS406 DEVICES

© 2009-2014 Microchip Technology Inc.

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14               | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6  | Bit 5   | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     | All<br>Resets |

|--------------|-------------|--------|----------------------|--------|----------|----------|----------|----------|----------|-------------|--------|---------|-----------|-----------|-----------|-----------|-----------|---------------|

| ADCON        | 0300        | ADON   | _                    | ADSIDL | SLOWCLK  | _        | GSWTRG   | -        | FORM     | EIE         | ORDER  | SEQSAMP | ASYNCSAMP | —         | ADCS2     | ADCS1     | ADCS0     | 0003          |

| ADPCFG       | 0302        |        |                      |        |          |          |          |          | P        | CFG<15:0    | >      |         |           | •         | •         |           | •         | 0000          |

| ADPCFG2      | 0304        | _      | _                    | —      | _        | _        | _        | _        | _        | —           | _      | —       | _         | _         | _         | PCFG      | <17:16>   | 0000          |

| ADSTAT       | 0306        | —      | —                    | _      | P12RDY   | _        | _        | _        | P8RDY    | P7RDY       | P6RDY  | P5RDY   | P4RDY     | P3RDY     | P2RDY     | P1RDY     | PORDY     | 0000          |

| ADBASE       | 0308        |        |                      |        |          |          |          |          | ADBASE<  | :15:1>      |        |         |           |           |           |           | _         | 0000          |

| ADCPC0       | 030A        | IRQEN1 | PEND1                | SWTRG1 | TRGSRC14 | TRGSRC13 | TRGSRC12 | TRGSRC11 | TRGSRC10 | IRQEN0      | PEND0  | SWTRG0  | TRGSRC04  | TRGSRC03  | TRGSRC02  | TRGSRC01  | TRGSRC00  | 0000          |

| ADCPC1       | 030C        | IRQEN3 | PEND3                | SWTRG3 | TRGSRC34 | TRGSRC33 | TRGSRC32 | TRGSRC31 | TRGSRC30 | IRQEN2      | PEND2  | SWTRG2  | TRGSRC24  | TRGSRC23  | TRGSRC22  | TRGSRC21  | TRGSRC20  | 0000          |

| ADCPC2       | 030E        | IRQEN5 | PEND5                | SWTRG5 | TRGSRC54 | TRGSRC53 | TRGSRC52 | TRGSRC51 | TRGSRC50 | IRQEN4      | PEND4  | SWTRG4  | TRGSRC44  | TRGSRC43  | TRGSRC42  | TRGSRC41  | TRGSRC40  | 0000          |

| ADCPC3       | 0310        | IRQEN7 | PEND7                | SWTRG7 | TRGSRC74 | TRGSRC73 | TRGSRC72 | TRGSRC71 | TRGSRC70 | IRQEN6      | PEND6  | SWTRG6  | TRGSRC64  | TRGSRC63  | TRGSRC62  | TRGSRC61  | TRGSRC640 | 0000          |

| ADCPC4       | 0312        | -      |                      |        | _        | _        | -        | _        | _        | IRQEN8      | PEND8  | SWTRG8  | TRGSRC84  | TRGSRC83  | TRGSRC82  | TRGSRC81  | TRGSRC80  | 0000          |

| ADCPC6       | 0316        | -      |                      |        | _        | _        | -        | _        | _        | IRQEN12     | PEND12 | SWTRG12 | TRGSRC124 | TRGSRC123 | TRGSRC122 | TRGSRC121 | TRGSRC120 | 0000          |

| ADCBUF0      | 0340        |        |                      |        |          |          |          |          | ADO      | C Data Buff | er 0   |         |           |           |           |           |           | xxxx          |

| ADCBUF1      | 0342        |        |                      |        |          |          |          |          | ADO      | C Data Buff | er 1   |         |           |           |           |           |           | xxxx          |

| ADCBUF2      | 0344        |        | ADC Data Buffer 2    |        |          |          |          |          |          |             |        |         |           |           |           | xxxx      |           |               |

| ADCBUF3      | 0346        |        | ADC Data Buffer 3    |        |          |          |          |          |          |             |        |         |           |           | xxxx      |           |           |               |

| ADCBUF4      | 0348        |        |                      |        |          |          |          |          | ADO      | C Data Buff | er 4   |         |           |           |           |           |           | xxxx          |

| ADCBUF5      | 034A        |        |                      |        |          |          |          |          | ADO      | C Data Buff | er 5   |         |           |           |           |           |           | xxxx          |

| ADCBUF6      | 034C        |        |                      |        |          |          |          |          | ADO      | C Data Buff | er 6   |         |           |           |           |           |           | xxxx          |

| ADCBUF7      | 034E        |        |                      |        |          |          |          |          | ADO      | C Data Buff | er 7   |         |           |           |           |           |           | xxxx          |

| ADCBUF8      | 0350        |        |                      |        |          |          |          |          | ADO      | C Data Buff | er 8   |         |           |           |           |           |           | xxxx          |

| ADCBUF9      | 0352        |        |                      |        |          |          |          |          | ADO      | C Data Buff | er 9   |         |           |           |           |           |           | xxxx          |

| ADCBUF10     | 0354        |        |                      |        |          |          |          |          | ADC      | Data Buffe  | er 10  |         |           |           |           |           |           | xxxx          |

| ADCBUF11     | 0356        |        |                      |        |          |          |          |          | ADC      | Data Buffe  | er 11  |         |           |           |           |           |           | xxxx          |

| ADCBUF12     | 0358        |        |                      |        |          |          |          |          | ADC      | Data Buffe  | er 12  |         |           |           |           |           |           | xxxx          |

| ADCBUF13     | 035A        |        | ADC Data Buffer 13 x |        |          |          |          |          |          |             |        |         |           | xxxx      |           |           |           |               |

| ADCBUF14     | 035C        |        | ADC Data Buffer 14 x |        |          |          |          |          |          |             |        |         |           | xxxx      |           |           |           |               |

| ADCBUF15     | 035E        |        |                      |        |          |          |          |          | ADC      | Data Buffe  | er 15  |         |           |           |           |           |           | xxxx          |

| ADCBUF16     | 0360        |        |                      |        |          |          |          |          | ADC      | Data Buffe  | er 16  |         |           |           |           |           |           | xxxx          |

| ADCBUF17     | 0362        |        |                      |        |          |          |          |          | ADC      | Data Buffe  | er 17  |         |           |           |           |           |           | xxxx          |

| ADCBUF24     | 0370        |        |                      |        |          |          |          |          | ADC      | Data Buffe  | er 24  |         |           |           |           |           |           | xxxx          |

| ADCBUF25     | 0372        |        |                      |        |          |          |          |          | ADC      | Data Buffe  | er 25  |         |           |           |           |           |           | xxxx          |

#### TABLE 4-33: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ32GS608 AND dsPIC33FJ64GS608 DEVICES

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-45: PORTC REGISTER MAP FOR dsPIC33FJ32GS608 AND dsPIC33FJ64GS608 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|----------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISC        | 02D0        |        | TRISC  | C<15:12> |        | _      | _      | _     | _     | _     | _     | _     | _     | _     | TRISC | <2:1> | _     | F006          |

| PORTC        | 02D2        |        | RC<    | 15:12>   |        | _      | _      | _     | _     | _     | _     | _     | _     | _     | RC<2  | 2:1>  | _     | xxxx          |

| LATC         | 02D4        |        | LATC   | <15:12>  |        | _      | _      |       |       | -     |       | _     | -     | _     | LATC< | <2:1> |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-46: PORTC REGISTER MAP FOR dsPIC33FJ32GS406/606 AND dsPIC33FJ64GS406/606 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|---------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISC        | 02D0        |        | TRISC  | <15:12> |        | _      | —      | _     | _     |       |       | _     | _     | —     | _     | _     | _     | F000          |

| PORTC        | 02D2        |        | RC<    | 15:12>  |        | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | xxxx          |

| LATC         | 02D4        |        | LATC   | <15:12> |        |        | —      |       |       | —     | _     | _     |       | —     | —     |       | —     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-47: PORTD REGISTER MAP FOR dsPIC33FJ32GS608/610 AND dsPIC33FJ64GS608/610 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14        | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|---------------|--------|--------|--------|--------|-------|-------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISD        | 02D8        |        |               |        |        |        |        |       | TRISD | <15:0> |       |       |       |       |       |       |       | FFFF          |

| PORTD        | 02DA        |        |               |        |        |        |        |       | RD<   | 15:0>  |       |       |       |       |       |       |       | xxxx          |

| LATD         | 02DC        |        | LATD<15:0> 01 |        |        |        |        |       |       |        |       | 0000  |       |       |       |       |       |               |

| ODCD         | 02DE        |        | ODCD<15:0> (  |        |        |        |        |       |       |        |       |       | 0000  |       |       |       |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-48: PORTD REGISTER MAP FOR dsPIC33FJ32GS406/606 AND dsPIC33FJ64GS406/606 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|------------|--------|-------|-------|-------|-------|---------|-------|-------|-------|-------|-------|---------------|

| TRISD        | 02D8        | _      | _      | _      | _      |            |        |       |       |       | TRISE | 0<11:0> |       |       |       |       |       | OFFF          |

| PORTD        | 02DA        |        | _      | _      | _      |            |        |       |       |       | RD<   | :11:0>  |       |       |       |       |       | xxxx          |

| LATD         | 02DC        | _      | _      | _      | —      | LATD<11:0> |        |       |       |       |       |         | 0000  |       |       |       |       |               |

| ODCD         | 02DE        | _      | _      | _      | _      | ODCD<11:0> |        |       |       |       |       |         |       | 0000  |       |       |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

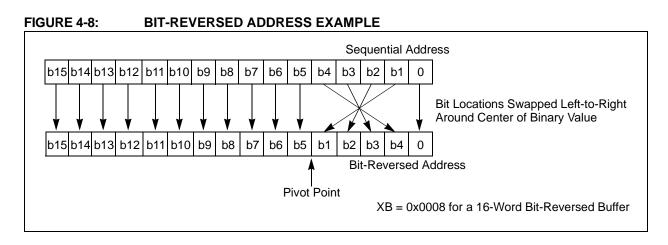

| TABLE | 4-07: | BII-RE | VERSE     | D ADDRESS SEQU | ENCE ( | 16-ENI | RY)     |          |         |

|-------|-------|--------|-----------|----------------|--------|--------|---------|----------|---------|

|       |       | Norma  | al Addres | SS             |        |        | Bit-Rev | ersed Ac | ldress  |

| A3    | A2    | A1     | A0        | Decimal        | A3     | A2     | A1      | A0       | Decimal |

| 0     | 0     | 0      | 0         | 0              | 0      | 0      | 0       | 0        | 0       |

| 0     | 0     | 0      | 1         | 1              | 1      | 0      | 0       | 0        | 8       |

| 0     | 0     | 1      | 0         | 2              | 0      | 1      | 0       | 0        | 4       |

| 0     | 0     | 1      | 1         | 3              | 1      | 1      | 0       | 0        | 12      |

| 0     | 1     | 0      | 0         | 4              | 0      | 0      | 1       | 0        | 2       |

| 0     | 1     | 0      | 1         | 5              | 1      | 0      | 1       | 0        | 10      |

| 0     | 1     | 1      | 0         | 6              | 0      | 1      | 1       | 0        | 6       |

| 0     | 1     | 1      | 1         | 7              | 1      | 1      | 1       | 0        | 14      |

| 1     | 0     | 0      | 0         | 8              | 0      | 0      | 0       | 1        | 1       |

| 1     | 0     | 0      | 1         | 9              | 1      | 0      | 0       | 1        | 9       |

| 1     | 0     | 1      | 0         | 10             | 0      | 1      | 0       | 1        | 5       |

| 1     | 0     | 1      | 1         | 11             | 1      | 1      | 0       | 1        | 13      |

| 1     | 1     | 0      | 0         | 12             | 0      | 0      | 1       | 1        | 3       |

| 1     | 1     | 0      | 1         | 13             | 1      | 0      | 1       | 1        | 11      |

| 1     | 1     | 1      | 0         | 14             | 0      | 1      | 1       | 1        | 7       |

| 1     | 1     | 1      | 1         | 15             | 1      | 1      | 1       | 1        | 15      |

### TABLE 4-67: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| ; | Set up NVMCO | N for row programming open  | rations                                 |

|---|--------------|-----------------------------|-----------------------------------------|

|   | MOV          | #0x4001, W0                 | ;                                       |

|   | MOV          | W0, NVMCON                  | ; Initialize NVMCON                     |

| ; | Set up a poi | nter to the first program   | memory location to be written           |

| ; | program memo | ry selected, and writes en  | nabled                                  |

|   | MOV          | #0x0000, W0                 | i                                       |

|   | MOV          | W0, TBLPAG                  | ; Initialize PM Page Boundary SFR       |

|   | MOV          | #0x6000, W0                 | ; An example program memory address     |

| ; | Perform the  | TBLWT instructions to writ  | te the latches                          |

| ; | 0th_program_ | word                        |                                         |

|   | MOV          | <pre>#LOW_WORD_0, W2</pre>  | ;                                       |

|   | MOV          | <pre>#HIGH_BYTE_0, W3</pre> | ;                                       |

|   | TBLWTL       | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                  | ; Write PM high byte into program latch |

| ; | lst_program_ | word                        |                                         |

|   | MOV          | #LOW_WORD_1, W2             | i                                       |

|   | MOV          | #HIGH_BYTE_1, W3            | i                                       |

|   | TBLWTL       | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                  | ; Write PM high byte into program latch |

| ; | 2nd_program  | _word                       |                                         |

|   | MOV          | #LOW_WORD_2, W2             | ;                                       |

|   | MOV          | <pre>#HIGH_BYTE_2, W3</pre> | ;                                       |

|   | TBLWTL       | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                  | ; Write PM high byte into program latch |

|   | •            |                             |                                         |

|   | •            |                             |                                         |

|   | •            |                             |                                         |

| ; | 63rd_program | _word                       |                                         |

|   | MOV          | #LOW_WORD_31, W2            | i                                       |

|   | MOV          | #HIGH_BYTE_31, W3           | i                                       |

|   | TBLWTL       | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                  | ; Write PM high byte into program latch |

| 1 |              |                             |                                         |

EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | ; Block all interrupts with priority <7 |

|------|-------------|-----------------------------------------|

|      |             | ; for next 5 instructions               |

| MOV  | #0x55, W0   |                                         |

| MOV  | W0, NVMKEY  | ; Write the 55 key                      |

| MOV  | #0xAA, W1   | i                                       |

| MOV  | W1, NVMKEY  | ; Write the AA key                      |

| BSET | NVMCON, #WR | ; Start the erase sequence              |

| NOP  |             | ; Insert two NOPs after the             |

| NOP  |             | ; erase command is asserted             |

|      |             |                                         |

| U-0                          | U-0             | U-0                                                                                                    | U-0              | U-0                             | U-0                   | U-0             | U-0     |  |  |  |  |

|------------------------------|-----------------|--------------------------------------------------------------------------------------------------------|------------------|---------------------------------|-----------------------|-----------------|---------|--|--|--|--|

| _                            | —               | —                                                                                                      | —                | —                               | —                     | _               | —       |  |  |  |  |

| bit 15                       |                 |                                                                                                        |                  |                                 |                       |                 | bit 8   |  |  |  |  |

| U-0                          | R/W-0           | R/W-0                                                                                                  | R/W-0            | R/W-0                           | R/W-0                 | R/W-0           | R/W-0   |  |  |  |  |

|                              | IC4IF           | IC3IF                                                                                                  | DMA3IF           | C1IF <sup>(1)</sup>             | C1RXIF <sup>(1)</sup> | SPI2IF          | SPI2EIF |  |  |  |  |

| bit 7                        |                 | 10011                                                                                                  | Divition         | 0111                            | Onota                 | 01 1211         | bit (   |  |  |  |  |

|                              |                 |                                                                                                        |                  |                                 |                       |                 | _       |  |  |  |  |

| <b>Legend:</b><br>R = Readab | le hit          | W = Writable                                                                                           | bit              | II – I Inimpler                 | mented bit, read      | as '0'          |         |  |  |  |  |

| -n = Value a                 |                 | '1' = Bit is se                                                                                        |                  | $0^{\circ} = \text{Bit is cle}$ |                       | x = Bit is unki | าดพท    |  |  |  |  |

|                              |                 |                                                                                                        | -                |                                 |                       |                 |         |  |  |  |  |

| bit 15-7                     | Unimplement     | ted: Read as                                                                                           | 0'               |                                 |                       |                 |         |  |  |  |  |

| bit 6                        | IC4IF: Input C  | apture Chanr                                                                                           | el 4 Interrupt F | -lag Status bit                 |                       |                 |         |  |  |  |  |

|                              | 1 = Interrupt r | equest has oc                                                                                          | curred           | -                               |                       |                 |         |  |  |  |  |

|                              | 0 = Interrupt r | equest has no                                                                                          | t occurred       |                                 |                       |                 |         |  |  |  |  |

| bit 5                        |                 | IC3IF: Input Capture Channel 3 Interrupt Flag Status bit                                               |                  |                                 |                       |                 |         |  |  |  |  |

|                              | 1 = Interrupt r | •                                                                                                      |                  |                                 |                       |                 |         |  |  |  |  |

| bit 4                        | 0 = Interrupt r | •                                                                                                      |                  | omploto Intorr                  | upt Flag Status b     | <b>.</b>        |         |  |  |  |  |

| DIL 4                        | 1 = Interrupt r |                                                                                                        |                  |                                 | upt Flag Status I     | JIL             |         |  |  |  |  |

|                              | 0 = Interrupt r |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |

| bit 3                        | C1IF: ECAN1     | Event Interru                                                                                          | pt Flag Status   | bit <sup>(1)</sup>              |                       |                 |         |  |  |  |  |

|                              | 1 = Interrupt r |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |

|                              | 0 = Interrupt r | •                                                                                                      |                  |                                 | (4)                   |                 |         |  |  |  |  |

| bit 2                        |                 |                                                                                                        | vent Interrupt   | Flag Status bit                 | <sub>(</sub> (1)      |                 |         |  |  |  |  |

|                              |                 | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                  |                                 |                       |                 |         |  |  |  |  |

| bit 1                        | -               | -                                                                                                      | ot Flag Status b | hit                             |                       |                 |         |  |  |  |  |

|                              | 1 = Interrupt r | •                                                                                                      | •                |                                 |                       |                 |         |  |  |  |  |

|                              | 0 = Interrupt r |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |

| bit 0                        | SPI2EIF: SPI2   | 2 Error Interru                                                                                        | pt Flag Status   | bit                             |                       |                 |         |  |  |  |  |

|                              | 1 = Interrupt r |                                                                                                        |                  |                                 |                       |                 |         |  |  |  |  |

|                              | 0 = Interrupt r | equest has no                                                                                          | t occurred       |                                 |                       |                 |         |  |  |  |  |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

**Note 1:** Interrupts are disabled on devices without ECAN<sup>™</sup> modules.

| REGISTER 7-13: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 |                 |                                     |                |                  |                  |                 |               |  |

|----------------------------------------------------------|-----------------|-------------------------------------|----------------|------------------|------------------|-----------------|---------------|--|

| U-0                                                      | R/W-0           | R/W-0                               | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0         |  |

| _                                                        | DMA1IE          | ADIE                                | U1TXIE         | U1RXIE           | SPI1IE           | SPI1EIE         | T3IE          |  |

| pit 15                                                   |                 |                                     |                |                  |                  |                 | bi            |  |

| R/W-0                                                    | R/W-0           | R/W-0                               | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0         |  |

| T2IE                                                     | OC2IE           | IC2IE                               | DMA0IE         | T1IE             | OC1IE            | IC1IE           | <b>INTOIE</b> |  |

| pit 7                                                    |                 |                                     |                |                  |                  |                 | bi            |  |

| Legend:                                                  |                 |                                     |                |                  |                  |                 |               |  |

| R = Readable                                             | bit             | W = Writable                        | bit            | U = Unimplen     | nented bit, read | d as '0'        |               |  |

| n = Value at                                             | POR             | '1' = Bit is set                    |                | '0' = Bit is cle |                  | x = Bit is unkn | iown          |  |

|                                                          | -               |                                     |                |                  |                  |                 | -             |  |

| oit 15                                                   | Unimplemen      | ted: Read as '                      | י'             |                  |                  |                 |               |  |

| oit 14                                                   | DMA1IE: DM      | A Channel 1 D                       | ata Transfer C | complete Interr  | upt Enable bit   |                 |               |  |

|                                                          |                 | request is enab<br>request is not e |                |                  |                  |                 |               |  |

| oit 13                                                   | ADIE: ADC1      | Conversion Co                       | mplete Interru | pt Enable bit    |                  |                 |               |  |

|                                                          |                 | request is enab                     |                |                  |                  |                 |               |  |

|                                                          | -               | request is not e                    |                |                  |                  |                 |               |  |

| oit 12                                                   |                 | RT1 Transmitter                     |                | ible bit         |                  |                 |               |  |

|                                                          |                 | request is enab<br>request is not e |                |                  |                  |                 |               |  |

| oit 11                                                   | -               | RT1 Receiver Ir                     |                | e hit            |                  |                 |               |  |

|                                                          | 1 = Interrupt ı | request is enab<br>request is not e | led            |                  |                  |                 |               |  |

| oit 10                                                   | -               | Event Interrup                      |                |                  |                  |                 |               |  |

|                                                          |                 | request is enab                     |                |                  |                  |                 |               |  |

|                                                          | 0 = Interrupt i | request is not e                    | nabled         |                  |                  |                 |               |  |

| oit 9                                                    | SPI1EIE: SPI    | 1 Event Interru                     | pt Enable bit  |                  |                  |                 |               |  |

|                                                          |                 | request is enab<br>request is not e |                |                  |                  |                 |               |  |

| oit 8                                                    | T3IE: Timer3    | Interrupt Enabl                     | e bit          |                  |                  |                 |               |  |

|                                                          |                 | request is enab<br>request is not e |                |                  |                  |                 |               |  |

| oit 7                                                    | T2IE: Timer2    | Interrupt Enabl                     | e bit          |                  |                  |                 |               |  |

|                                                          | •               | request is enab                     |                |                  |                  |                 |               |  |

|                                                          | •               | request is not e                    |                |                  |                  |                 |               |  |

| oit 6                                                    | -               | ut Compare Ch                       |                | upt Enable bit   |                  |                 |               |  |

|                                                          |                 | request is enab<br>request is not e |                |                  |                  |                 |               |  |

| oit 5                                                    | •               | Capture Channe                      |                | -nable hit       |                  |                 |               |  |

|                                                          | 1 = Interrupt i | request is enab                     | led            |                  |                  |                 |               |  |

| oit 4                                                    |                 | A Channel 0 Da                      |                | omplete Interr   | upt Enable bit   |                 |               |  |

|                                                          |                 | request is enab                     |                |                  |                  |                 |               |  |

|                                                          |                 | request is not e                    |                |                  |                  |                 |               |  |

| oit 3                                                    | T1IE: Timer1    | Interrupt Enabl                     | e bit          |                  |                  |                 |               |  |

|                                                          | 1 = Interrupt i | roquest is enab                     | امط            |                  |                  |                 |               |  |

#### DECISTED 7 12 INTERDURT ENARLE CONTROL DECISTER A

### REGISTER 16-12: PDCx: PWM GENERATOR DUTY CYCLE x REGISTER<sup>(1,2,3)</sup>

| R/W-0                               | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|-------------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                                     |       |                  | PDC   | <15:8>                             |       |                 |       |

| bit 15                              |       |                  |       |                                    |       |                 | bit 8 |

|                                     |       |                  |       |                                    |       |                 |       |

| R/W-0                               | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|                                     |       |                  | PDC   | x<7:0>                             |       |                 |       |

| bit 7                               |       |                  |       |                                    |       |                 | bit 0 |

| Legend:                             |       |                  |       |                                    |       |                 |       |

| R = Readable bit $W = Writable bit$ |       |                  | it    | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at POR '1                |       | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |

#### bit 15-0 PDCx<15:0>: PWM Generator # Duty Cycle Value bits

- **Note 1:** In Independent PWM mode, the PDCx register controls the PWMxH duty cycle only. In the Complementary, Redundant and Push-Pull PWM modes, the PDCx register controls the duty cycle of both the PWMxH and PWMxL.

- **2:** The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period 0x0009.

- **3:** As the duty cycle gets closer to 0% or 100% of the PWM period (0 to 40 ns, depending on the mode of operation), PWM duty cycle resolution will increase from 1 to 3 LSBs.

### REGISTER 16-13: SDCx: PWM SECONDARY DUTY CYCLE x REGISTER<sup>(1,2,3)</sup>

| R/W-0                               | R/W-0 | R/W-0 | R/W-0             | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |

|-------------------------------------|-------|-------|-------------------|------------------------------------|-----------------|-------|-------|

|                                     |       |       | SDC               | x<15:8>                            |                 |       |       |

| bit 15                              |       |       |                   |                                    |                 |       | bit 8 |

| R/W-0                               | R/W-0 | R/W-0 | R/W-0             | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |

|                                     |       |       |                   | 5x<7:0>                            |                 |       |       |

| bit 7                               |       |       |                   |                                    |                 |       | bit 0 |

| Legend:                             |       |       |                   |                                    |                 |       |       |

| R = Readable bit $W = Writable bit$ |       |       | it                | U = Unimplemented bit, read as '0' |                 |       |       |

| -n = Value at POR '1' = Bit is set  |       |       | '0' = Bit is clea | ared                               | x = Bit is unkr | nown  |       |

bit 15-0 **SDCx<15:0>:** Secondary Duty Cycle bits for PWMxL Output Pin

- **Note 1:** The SDCx register is used in Independent PWM mode only. When used in Independent PWM mode, the SDCx register controls the PWMxL duty cycle.

- **2:** The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period 0x0009.

- **3:** As the duty cycle gets closer to 0% or 100% of the PWM period (0 to 40 ns, depending on the mode of operation), PWM duty cycle resolution will increase from 1 to 3 LSBs.

|                | U-0                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                     | U-0                                                                                                                                        | U-0                                                                                     | R/W-0                                                     | R/W-0           | R/W-0 |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|-------|--|--|--|--|

|                | —                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                       | —                                                                                                                                          | -                                                                                       | IMV1                                                      | IMV0            | CEID  |  |  |  |  |

| bit 15         |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                         |                                                                                                                                            |                                                                                         |                                                           |                 | bit   |  |  |  |  |

|                |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                         |                                                                                                                                            |                                                                                         |                                                           |                 |       |  |  |  |  |

| R/W-0          | R/W-0                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                      | U-0                                                                                     | U-0                                                       | U-0             | U-0   |  |  |  |  |

| QEOUT          | QECK2                                                                                                                                                                                                                                      | QECK1                                                                                                                                                                                                                                                   | QECK0                                                                                                                                      | —                                                                                       |                                                           |                 |       |  |  |  |  |

| bit 7          |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                         |                                                                                                                                            |                                                                                         |                                                           |                 | bit   |  |  |  |  |

| Legend:        |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                         |                                                                                                                                            |                                                                                         |                                                           |                 |       |  |  |  |  |

| R = Readabl    | le bit                                                                                                                                                                                                                                     | W = Writable                                                                                                                                                                                                                                            | bit                                                                                                                                        | U = Unimple                                                                             | mented bit, read                                          | d as '0'        |       |  |  |  |  |

| -n = Value at  | POR                                                                                                                                                                                                                                        | '1' = Bit is set                                                                                                                                                                                                                                        |                                                                                                                                            | '0' = Bit is cle                                                                        | eared                                                     | x = Bit is unkr | nown  |  |  |  |  |

|                |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                         |                                                                                                                                            |                                                                                         |                                                           |                 |       |  |  |  |  |

| bit 15-11      | Unimplemen                                                                                                                                                                                                                                 | ted: Read as '                                                                                                                                                                                                                                          | 0'                                                                                                                                         |                                                                                         |                                                           |                 |       |  |  |  |  |

| bit 10-9       | IMV<1:0>: Inc                                                                                                                                                                                                                              | dex Match Valu                                                                                                                                                                                                                                          | ie bits                                                                                                                                    |                                                                                         |                                                           |                 |       |  |  |  |  |

|                | These bits allow the user application to specify the state of the QEAx and QEBx input pins during a                                                                                                                                        |                                                                                                                                                                                                                                                         |                                                                                                                                            |                                                                                         |                                                           |                 |       |  |  |  |  |

|                | index pulse when the POSxCNT register is to be reset.                                                                                                                                                                                      |                                                                                                                                                                                                                                                         |                                                                                                                                            |                                                                                         |                                                           |                 |       |  |  |  |  |

|                | In x4 Quadrature Count Mode:                                                                                                                                                                                                               |                                                                                                                                                                                                                                                         |                                                                                                                                            |                                                                                         |                                                           |                 |       |  |  |  |  |