Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 50 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, QEI, POR, PWM, WDT                                   |

| Number of I/O              | 58                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 9K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b; D/A 1x10b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

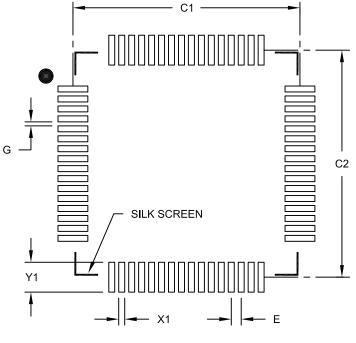

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs606-50i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| File    | <b>34-5</b><br>SFR<br>Addr | Bit 15  | Bit 14  | Bit 13   | Bit 12  | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4         | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All    |

|---------|----------------------------|---------|---------|----------|---------|---------|----------|----------|----------|----------|----------|----------|---------------|---------|----------|----------|----------|--------|

| Name    |                            |         |         |          |         |         |          |          |          |          |          |          |               |         |          |          |          | Resets |

| INTCON1 | 0080                       | NSTDIS  | OVAERR  | OVBERR   | COVAERR | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  | DMACERR  | MATHERR       | ADDRERR | STKERR   | OSCFAIL  |          | 0000   |

| INTCON2 | 0082                       | ALTIVT  | DISI    | —        | —       | _       | —        | —        | —        | —        | —        | —        | INT4EP        | INT3EP  | INT2EP   | INT1EP   | INT0EP   | 0000   |

| IFS0    | 0084                       | —       | DMA1IF  | ADIF     | U1TXIF  | U1RXIF  | SPI1IF   | SPI1EIF  | T3IF     | T2IF     | OC2IF    | IC2IF    | DMA0IF        | T1IF    | OC1IF    | IC1IF    | INTOIF   | 0000   |

| IFS1    | 0086                       | U2TXIF  | U2RXIF  | INT2IF   | T5IF    | T4IF    | OC4IF    | OC3IF    | DMA2IF   | —        | -        | —        | INT1IF        | CNIF    | AC1IF    | MI2C1IF  | SI2C1IF  | 0000   |

| IFS2    | 0088                       | —       | _       | -        | _       | —       | _        | —        | —        | —        | IC4IF    | IC3IF    | DMA3IF        | C1IF    | C1RXIF   | SPI2IF   | SPI2EIF  | 0000   |

| IFS3    | 008A                       | —       | —       | -        | —       | —       | QEI1IF   | PSEMIF   | —        | —        | INT4IF   | INT3IF   | -             | —       | MI2C2IF  | SI2C2IF  | —        | 0000   |

| IFS4    | 008C                       | —       | —       | —        | _       | QEI2IF  | —        | PSESMIF  |          | —        | C1TXIF   | —        | —             | —       | U2EIF    | U1EIF    | —        | 0000   |

| IFS5    | 008E                       | PWM2IF  | PWM1IF  | ADCP12IF | _       | —       | _        | _        | —        | —        | _        | —        | _             | —       | _        | ADCP8IF  | —        | 0000   |

| IFS6    | 0090                       | ADCP1IF | ADCP0IF |          | —       | —       | _        | AC4IF    | AC3IF    | AC2IF    |          | PWM8IF   | PWM7IF        | PWM6IF  | PWM5IF   | PWM4IF   | PWM3IF   | 0000   |

| IFS7    | 0092                       | —       | —       | -        | —       | —       | -        | _        | —        | —        | -        | ADCP7IF  | ADCP6IF       | ADCP5IF | ADCP4IF  | ADCP3IF  | ADCP2IF  | 0000   |

| IEC0    | 0094                       | _       | DMA1IE  | ADIE     | U1TXIE  | U1RXIE  | SPI1IE   | SPI1EIE  | T3IE     | T2IE     | OC2IE    | IC2IE    | DMA0IE        | T1IE    | OC1IE    | IC1IE    | INTOLE   | 0000   |

| IEC1    | 0096                       | U2TXIE  | U2RXIE  | INT2IE   | T5IE    | T4IE    | OC4IE    | OC3IE    | DMA2IE   | _        | —        | _        | INT1IE        | CNIE    | AC1IE    | MI2C1IE  | SI2C1IE  | 0000   |

| IEC2    | 0098                       |         |         | _        | -       | -       | _        | _        | _        | _        | IC4IE    | IC3IE    | <b>DMA3IE</b> | C1IE    | C1RXIE   | SPI2IE   | SPI2EIE  | 0000   |

| IEC3    | 009A                       | —       | _       | -        | _       | _       | QEI1IE   | PSEMIE   | _        | —        | INT4IE   | INT3IE   | _             | _       | MI2C2IE  | SI2C2IE  | _        | 0000   |

| IEC4    | 009C                       | _       | _       | _        | _       | QEI2IE  | _        | PSESMIE  | _        | _        | C1TXIE   | _        | _             | _       | U2EIE    | U1EIE    | _        | 0000   |

| IEC5    | 009E                       | PWM2IE  | PWM1IE  | ADCP12IE | _       | _       | -        | _        | _        | _        |          | _        |               | _       | -        | ADCP8IE  |          | 0000   |

| IEC6    | 00A0                       | ADCP1IE | ADCP0IE | _        | —       | _       | _        | AC4IE    | AC3IE    | AC2IE    | _        | PWM8IE   | PWM7IE        | PWM6IE  | PWM5IE   | PWM4IE   | PWM3IE   | 0000   |

| IEC7    | 00A2                       | _       | _       | _        | _       | _       | _        | _        | _        | _        | _        | ADCP7IE  | ADCP6IE       | ADCP5IE | ADCP4IE  | ADCP3IE  | ADCP2IE  | 0000   |

| IPC0    | 00A4                       | _       | T1IP2   | T1IP1    | T1IP0   | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2   | IC1IP1   | IC1IP0        | _       | INT0IP2  | INT0IP1  | INT0IP0  | 4444   |

| IPC1    | 00A6                       | _       | T2IP2   | T2IP1    | T2IP0   | _       | OC2IP2   | OC2IP1   | OC2IP0   | _        | IC2IP2   | IC2IP1   | IC2IP0        | _       | DMA0IP2  | DMA0IP1  | DMA0IP0  | 4444   |

| IPC2    | 00A8                       | _       | U1RXIP2 | U1RXIP1  | U1RXIP0 | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0      | _       | T3IP2    | T3IP1    | T3IP0    | 4444   |

| IPC3    | 00AA                       | _       | _       |          | —       | _       | DMA1IP2  | DMA1IP1  | DMA1IP0  | _        | ADIP2    | ADIP1    | ADIP0         | —       | U1TXIP2  | U1TXIP1  | U1TXIP0  | 4444   |

| IPC4    | 00AC                       | _       | CNIP2   | CNIP1    | CNIP0   | _       | AC1IP2   | AC1IP1   | AC1IP0   | _        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0      | —       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 | 4444   |

| IPC5    | 00AE                       | _       | _       |          | —       | _       |          | -        | —        | _        |          | —        |               | _       | INT1IP2  | INT1IP1  | INT1IP0  | 0004   |

| IPC6    | 00B0                       | _       | T4IP2   | T4IP1    | T4IP0   | _       | OC4IP2   | OC4IP1   | OC4IP0   | _        | OC3IP2   | OC3IP1   | OC3IP0        | —       | DMA2IP2  | DMA2IP1  | DMA2IP0  | 4444   |

| IPC7    | 00B2                       | _       | U2TXIP2 | U2TXIP1  | U2TXIP0 | _       | U2RXIP2  | U2RXIP1  | U2RXIP0  | _        | INT2IP2  | INT2IP1  | INT2IP0       | _       | T5IP2    | T5IP1    | T5IP0    | 4444   |

| IPC8    | 00B4                       | _       | C1IP2   | C1IP1    | C1IP0   | _       | C1RXIP2  | C1RXIP1  | C1RXIP0  | _        | SPI2IP2  | SPI2IP1  | SPI2IP0       | _       | SPI2EIP2 | SPI2EIP1 | SPI2EIP0 | 4444   |

| IPC9    | 00B6                       | _       | _       | _        | _       | _       | IC4IP2   | IC4IP1   | IC4IP0   | _        | IC3IP2   | IC3IP1   | IC3IP0        | _       | DMA3IP2  | DMA3IP1  | DMA3IP0  | 0444   |

| IPC12   | 00BC                       | _       | _       | _        | _       | _       | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 | _        | SI2C2IP2 | SI2C2IP1 | SI2C2IP0      | _       | _        | _        | _        | 0440   |

| IPC13   | 00BE                       | _       | _       | _        | _       | _       | INT4IP2  | INT4IP1  | INT4IP0  | _        | INT3IP2  | INT3IP1  | INT3IP0       | _       | _        | _        | _        | 0440   |

| IPC14   | 00C0                       | _       | _       | _        | _       | _       | QEI1IP2  | QEI1IP0  | QEI1IP0  | _        | PSEMIP2  | PSEMIP1  | PSEMIP0       | _       | _        | _        | _        | 0440   |

| IPC16   | 00C4                       | _       | _       | _        | _       | _       | U2EIP2   | U2EIP1   | U2EIP0   | _        | U1EIP2   | U1EIP1   | U1EIP0        | _       | _        | _        | _        | 0440   |

| IPC17   | 00C6                       | _       | _       | _        | _       | _       | C1TXIP2  | C1TXIP1  | C1TXIP0  | _        | _        | _        | _             | _       | _        | _        | _        | 0400   |

| IPC18   | 00C8                       |         | QEI2IP2 | QEI2IP1  | QEI2IP0 |         | _        |          | _        | _        | PSESMIP2 | PSESMIP1 | PSESMIP0      |         |          |          |          | 4040   |

# TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ64GS608 DEVICES

| File     | SFR  | Bit 15  | Bit 14 | Bit 13  | Bit 12    | Bit 11    | Bit 10    | Bit 9     | Bit 8       | Bit 7       | Bit 6  | Bit 5   | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     | All    |

|----------|------|---------|--------|---------|-----------|-----------|-----------|-----------|-------------|-------------|--------|---------|-----------|-----------|-----------|-----------|-----------|--------|

| Name     | Addr |         |        |         |           |           |           |           |             |             |        |         |           |           |           |           |           | Resets |

| ADCON    | 0300 | ADON    | _      | ADSIDL  | SLOWCLK   | <u> </u>  | GSWTRG    | —         | FORM        | EIE         | ORDER  | SEQSAMP | ASYNCSAMP | —         | ADCS2     | ADCS1     | ADCS0     | 0003   |

| ADPCFG   | 0302 |         |        |         |           |           |           |           | PCFG        | <15:0>      |        |         |           |           |           |           |           | 0000   |

| ADPCFG2  | 0304 | —       | —      | —       | -         | —         | -         | -         | —           |             |        |         | PC        | FG<23:16> | 1         | 1         | 1         | 0000   |

| ADSTAT   | 0306 | —       | —      | —       | P12RDY    | P11RDY    | P10RDY    | P9RDY     | P8RDY       | P7RDY       | P6RDY  | P5RDY   | P4RDY     | P3RDY     | P2RDY     | P1RDY     | P0RDY     | 0000   |

| ADBASE   | 0308 |         |        |         |           |           |           |           | ADBASE<15:1 | >           |        |         |           |           |           |           | —         | 0000   |

| ADCPC0   | 030A | IRQEN1  | PEND1  | SWTRG1  | TRGSRC14  | TRGSRC13  | TRGSRC12  | TRGSRC11  | TRGSRC10    | IRQEN0      | PEND0  | SWTRG0  | TRGSRC04  | TRGSRC03  | TRGSRC02  | TRGSRC01  | TRGSRC00  | 0000   |

| ADCPC1   | 030C | IRQEN3  | PEND3  | SWTRG3  | TRGSRC34  | TRGSRC33  | TRGSRC32  | TRGSRC31  | TRGSRC30    | IRQEN2      | PEND2  | SWTRG2  | TRGSRC24  | TRGSRC23  | TRGSRC22  | TRGSRC21  | TRGSRC20  | 0000   |

| ADCPC2   | 030E | IRQEN5  | PEND5  | SWTRG5  | TRGSRC54  | TRGSRC53  | TRGSRC52  | TRGSRC51  | TRGSRC50    | IRQEN4      | PEND4  | SWTRG4  | TRGSRC44  | TRGSRC43  | TRGSRC42  | TRGSRC41  | TRGSRC40  | 0000   |

| ADCPC3   | 0310 | IRQEN7  | PEND7  | SWTRG7  | TRGSRC74  | TRGSRC73  | TRGSRC72  | TRGSRC71  | TRGSRC70    | IRQEN6      | PEND6  | SWTRG6  | TRGSRC64  | TRGSRC63  | TRGSRC62  | TRGSRC61  | TRGSRC640 | 0000   |

| ADCPC4   | 0312 | IRQEN9  | PEND9  | SWTRG9  | TRGSRC94  | TRGSRC93  | TRGSRC92  | TRGSRC94  | TRGSRC90    | IRQEN8      | PEND8  | SWTRG8  | TRGSRC84  | TRGSRC83  | TRGSRC82  | TRGSRC81  | TRGSRC80  | 0000   |

| ADCPC5   | 0314 | IRQEN11 | PEND11 | SWTRG11 | TRGSRC114 | TRGSRC113 | TRGSRC112 | TRGSRC111 | TRGSRC110   | IRQEN10     | PEND10 | SWTRG10 | TRGSRC104 | TRGSRC103 | TRGSRC102 | TRGSRC101 | TRGSRC100 | 0000   |

| ADCPC6   | 0316 | _       | -      | _       | _         | _         |           | _         | _           | IRQEN12     | PEND12 | SWTRG12 | TRGSRC124 | TRGSRC123 | TRGSRC122 | TRGSRC121 | TRGSRC120 | 0000   |

| ADCBUF0  | 0340 |         |        |         |           |           |           |           | ADC Da      | a Buffer 0  |        |         |           |           |           |           |           | xxxx   |

| ADCBUF1  | 0342 |         |        |         |           |           |           |           | ADC Da      | a Buffer 1  |        |         |           |           |           |           |           | xxxx   |

| ADCBUF2  | 0344 |         |        |         |           |           |           |           | ADC Da      | a Buffer 2  |        |         |           |           |           |           |           | xxxx   |

| ADCBUF3  | 0346 |         |        |         |           |           |           |           | ADC Da      | a Buffer 3  |        |         |           |           |           |           |           | xxxx   |

| ADCBUF4  | 0348 |         |        |         |           |           |           |           | ADC Da      | a Buffer 4  |        |         |           |           |           |           |           | xxxx   |

| ADCBUF5  | 034A |         |        |         |           |           |           |           | ADC Da      | a Buffer 5  |        |         |           |           |           |           |           | xxxx   |

| ADCBUF6  | 034C |         |        |         |           |           |           |           | ADC Da      | a Buffer 6  |        |         |           |           |           |           |           | xxxx   |

| ADCBUF7  | 034E |         |        |         |           |           |           |           | ADC Da      | a Buffer 7  |        |         |           |           |           |           |           | xxxx   |

| ADCBUF8  | 0350 |         |        |         |           |           |           |           | ADC Da      | a Buffer 8  |        |         |           |           |           |           |           | xxxx   |

| ADCBUF9  | 0352 |         |        |         |           |           |           |           | ADC Da      | a Buffer 9  |        |         |           |           |           |           |           | xxxx   |

| ADCBUF10 | 0354 |         |        |         |           |           |           |           | ADC Dat     | a Buffer 10 |        |         |           |           |           |           |           | xxxx   |

| ADCBUF11 | 0356 |         |        |         |           |           |           |           | ADC Dat     | a Buffer 11 |        |         |           |           |           |           |           | xxxx   |

| ADCBUF12 | 0358 |         |        |         |           |           |           |           | ADC Dat     | a Buffer 12 |        |         |           |           |           |           |           | xxxx   |

| ADCBUF13 | 035A |         |        |         |           |           |           |           | ADC Dat     | a Buffer 13 |        |         |           |           |           |           |           | xxxx   |

| ADCBUF14 | 035C |         |        |         |           |           |           |           | ADC Dat     | a Buffer 14 |        |         |           |           |           |           |           | xxxx   |

| ADCBUF15 | 035E |         |        |         |           |           |           |           | ADC Dat     | a Buffer 15 |        |         |           |           |           |           |           | xxxx   |

| ADCBUF16 | 0360 |         |        |         |           |           |           |           | ADC Dat     | a Buffer 16 |        |         |           |           |           |           |           | xxxx   |

| ADCBUF17 | 0362 |         |        |         |           |           |           |           | ADC Dat     | a Buffer 17 |        |         |           |           |           |           |           | xxxx   |

| ADCBUF18 | 0364 |         |        |         |           |           |           |           | ADC Dat     | a Buffer 18 |        |         |           |           |           |           |           | xxxx   |

| ADCBUF19 | 0366 |         |        |         |           |           |           |           | ADC Dat     | a Buffer 19 |        |         |           |           |           |           |           | xxxx   |

| ADCBUF20 | 0368 |         |        |         |           |           |           |           | ADC Dat     | a Buffer 20 |        |         |           |           |           |           |           | xxxx   |

| ADCBUF21 | 036A |         |        |         |           |           |           |           | ADC Dat     | a Buffer 21 |        |         |           |           |           |           |           | xxxx   |

#### TABLE 4-32: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ32GS610 AND dsPIC33FJ64GS610 DEVICES ONLY

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-41: PORTA REGISTER MAP FOR dsPIC33FJ32GS610 AND dsPIC33FJ64GS610 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|---------|--------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISA        | 02C0        | TRISA  | <15:14> | —      | —      | —      | TRISA  | <10:9> | —     |           |       |       | TRISA | <7:0> |       |       |       | C6FF          |

| PORTA        | 02C2        | RA<1   | 5:14>   | _      | _      | _      | RA<1   | 10:9>  | _     |           |       |       | RA<   | 7:0>  |       |       |       | xxxx          |

| LATA         | 02C4        | LATA<  | 15:14>  | _      | _      | _      | LATA<  | :10:9> | _     | LATA<7:0> |       |       |       |       | 0000  |       |       |               |

| ODCA         | 02C6        | ODCA<  | <15:14> | _      | _      | _      | ODCA.  | <10:9> | _     | _         | _     | ODCA- | <5:4> | _     | _     | ODCA  | <1:0> | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-42: PORTA REGISTER MAP FOR dsPIC33FJ32GS608 AND dsPIC33FJ64GS608 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|---------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISA        | 02C0        | TRISA< | :15:14> | _      | _      | _      | TRISA< | <10:9> | —     | _     | _     | _     | —     | _     | —     | —     | —     | C600          |

| PORTA        | 02C2        | RA<1   | 5:14>   | _      | -      | -      | RA<1   | 0:9>   | -     |       |       | -     | —     |       |       | _     | -     | xxxx          |

| LATA         | 02C4        | LATA<  | 15:14>  | _      | _      | _      | LATA<  | 10:9>  | _     | -     | -     | _     | _     | -     | _     | _     | _     | 0000          |

| ODCA         | 02C6        | ODCA<  | :15:14> | _      |        | _      | ODCA<  | :10:9> |       | _     | _     |       | -     | _     | _     |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-43: PORTB REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14      | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|-------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB        | 02C8        |        | TRISB<15:0> |        |        |        |        |       |       |       |       |       |       |       |       | FFFF  |       |               |

| PORTB        | 02CA        |        |             |        |        |        |        |       |       |       |       |       |       |       | xxxx  |       |       |               |

| LATB         | 02CC        |        |             |        |        |        |        |       |       |       |       |       |       |       | 0000  |       |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-44: PORTC REGISTER MAP FOR dsPIC33FJ32GS610 AND dsPIC33FJ64GS610 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|---------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISC        | 02D0        |        | TRISC  | <15:12> |        | —      |        |       |       | —     |       |       |       | TRISC | <4:1> |       |       | F01E          |

| PORTC        | 02D2        |        | RC<    | 15:12>  |        | _      | _      | _     | _     | -     | _     | _     |       | RC<   | 4:1>  |       | _     | xxxx          |

| LATC         | 02D4        |        | LATC   | <15:12> |        | -      |        |       |       | _     |       | _     |       | LATC  | <4:1> |       | -     | 0000          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER      | 7-13: IEC0:   | INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ENABLE CO       |                  | GISTER 0         |                 |        |

|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|--------|

| U-0           | R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| _             | DMA1IE        | ADIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U1TXIE          | U1RXIE           | SPI1IE           | SPI1EIE         | T3IE   |

| oit 15        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 | bi     |

| R/W-0         | R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T2IE          | OC2IE         | IC2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DMA0IE          | T1IE             | OC1IE            | IC1IE           | INTOIE |

| bit 7         |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 | bi     |

| Legend:       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 |        |

| R = Readabl   | le bit        | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | oit             | U = Unimpler     | nented bit, read | d as '0'        |        |

| -n = Value at |               | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | '0' = Bit is cle |                  | x = Bit is unkr | iown   |

|               |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 |        |

| bit 15        | Unimplemen    | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | )'              |                  |                  |                 |        |

| bit 14        | DMA1IE: DM    | A Channel 1 Da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ata Transfer C  | complete Interr  | upt Enable bit   |                 |        |

|               |               | request is enabl<br>request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                  |                  |                 |        |

| bit 13        | ADIE: ADC1    | Conversion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | mplete Interru  | pt Enable bit    |                  |                 |        |

|               |               | request is enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                  |                  |                 |        |

|               | -             | request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                  |                  |                 |        |

| pit 12        |               | RT1 Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | ible bit         |                  |                 |        |

|               |               | request is enabl<br>request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                  |                  |                 |        |

| bit 11        | •             | RT1 Receiver In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | e hit            |                  |                 |        |

|               | 1 = Interrupt | request is enabl<br>request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | led             |                  |                  |                 |        |

| bit 10        | -             | Event Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                  |                  |                 |        |

|               |               | request is enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                  |                  |                 |        |

|               | -             | request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                  |                  |                 |        |