Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 50 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, QEI, POR, PWM, WDT                                   |

| Number of I/O              | 58                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 9K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b; D/A 1x10b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

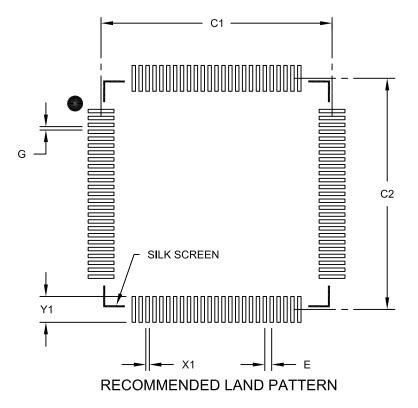

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs606-50i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name             | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                        |

|----------------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN23             | I           | Analog         | Analog input channels.                                                                                                                                                                                                                                             |

| CLKI<br>CLKO         | I<br>O      | ST/CMOS<br>—   | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.<br>Always associated with OSC2 pin function. |

| OSC1                 | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                                                                                    |

| OSC2                 | I/O         | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                        |

| SOSCI                |             | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                                                                                     |

| SOSCO                | 0           |                | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                                                                                    |

| CN0-CN23             | Ι           | ST             | Change Notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                   |

| C1RX                 | I           | ST             | ECAN1 bus receive pin.                                                                                                                                                                                                                                             |

| C1TX                 | 0           | —              | ECAN1 bus transmit pin.                                                                                                                                                                                                                                            |

| IC1-IC4              | Ι           | ST             | Capture Inputs 1 through 4.                                                                                                                                                                                                                                        |

| INDX1, INDX2, AINDX1 | I           | ST             | Quadrature Encoder Index Pulse input.                                                                                                                                                                                                                              |

| QEA1, QEA2, AQEA1    | I           | ST             | Quadrature Encoder Phase A input in QEI mode.                                                                                                                                                                                                                      |

| QEB1, QEB2, AQEB1    | I           | ST             | Auxiliary Timer External Clock/Gate input in Timer mode.<br>Quadrature Encoder Phase A input in QEI mode.<br>Auxiliary Timer External Clock/Gate input in Timer mode.                                                                                              |

| UPDN1                | 0           | CMOS           | Position Up/Down Counter Direction State.                                                                                                                                                                                                                          |

| OCFA                 | I           | ST             | Compare Fault A input.                                                                                                                                                                                                                                             |

| OC1-OC4              | 0           | —              | Compare Outputs 1 through 4.                                                                                                                                                                                                                                       |

| INT0                 | I           | ST             | External Interrupt 0.                                                                                                                                                                                                                                              |

| INT1                 | I           | ST             | External Interrupt 1.                                                                                                                                                                                                                                              |

| INT2                 | I           | ST             | External Interrupt 2.                                                                                                                                                                                                                                              |

| INT3                 | I           | ST             | External Interrupt 3.                                                                                                                                                                                                                                              |

| INT4                 | 1           | ST             | External Interrupt 4.                                                                                                                                                                                                                                              |

| RA0-RA15             | I/O         | ST             | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| RB0-RB15<br>RC0-RC15 | I/O<br>I/O  | ST<br>ST       | PORTB is a bidirectional I/O port.<br>PORTC is a bidirectional I/O port.                                                                                                                                                                                           |

| RD0-RD15             | 1/0         | ST             | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| RE0-RE9              | I/O         | ST             | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| RF0-RF13             | I/O         | ST             | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| RG0-RG15             | I/O         | ST             | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| T1CK                 | 1/0         | ST             | Timer1 external clock input.                                                                                                                                                                                                                                       |

| T2CK                 | i i         | ST             | Timer2 external clock input.                                                                                                                                                                                                                                       |

| T3CK                 | ·           | ST             | Timer3 external clock input.                                                                                                                                                                                                                                       |

| T4CK                 | I           | ST             | Timer4 external clock input.                                                                                                                                                                                                                                       |

| T5CK                 | I           | ST             | Timer5 external clock input.                                                                                                                                                                                                                                       |

| Legend: CMOS = CMC   | )S.comp     | atible input   | or output Analog = Analog input I = Input                                                                                                                                                                                                                          |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-Transistor Logic

P = Power

0 = Output

# 3.4 CPU Control Registers

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| R-0                | R-0                                                     | R/C-0                                                             | R/C-0             | R-0               | R/C-0                | R-0              | R/W-0          |  |  |  |  |

|--------------------|---------------------------------------------------------|-------------------------------------------------------------------|-------------------|-------------------|----------------------|------------------|----------------|--|--|--|--|

| OA                 | OB                                                      | SA <sup>(1)</sup>                                                 | SB <sup>(1)</sup> | OAB               | SAB <sup>(1,4)</sup> | DA               | DC             |  |  |  |  |

| bit 15             |                                                         |                                                                   |                   |                   |                      |                  | bit 8          |  |  |  |  |

|                    |                                                         |                                                                   |                   |                   |                      |                  |                |  |  |  |  |

| R/W-0(             | <sup>3)</sup> R/W-0 <sup>(3)</sup>                      | R/W-0 <sup>(3)</sup>                                              | R-0               | R/W-0             | R/W-0                | R/W-0            | R/W-0          |  |  |  |  |

| IPL2 <sup>(2</sup> | ) IPL1 <sup>(2)</sup>                                   | IPL0 <sup>(2)</sup>                                               | RA                | Ν                 | OV                   | Z                | С              |  |  |  |  |

| bit 7              |                                                         |                                                                   |                   |                   |                      |                  | bit 0          |  |  |  |  |

|                    |                                                         |                                                                   |                   |                   |                      |                  |                |  |  |  |  |

| Legend:            |                                                         | C = Clearable                                                     | bit               |                   |                      |                  |                |  |  |  |  |

| R = Reada          | able bit                                                | W = Writable I                                                    | oit               | U = Unimplei      | mented bit, read     | as '0'           |                |  |  |  |  |

| -n = Value         | at POR                                                  | '1' = Bit is set                                                  |                   | '0' = Bit is cle  | eared                | x = Bit is unkr  | nown           |  |  |  |  |

|                    |                                                         |                                                                   |                   |                   |                      |                  |                |  |  |  |  |

| bit 15             |                                                         | ator A Overflow                                                   |                   |                   |                      |                  |                |  |  |  |  |

|                    |                                                         | ator A has overf<br>ator A has not o                              |                   |                   |                      |                  |                |  |  |  |  |

| bit 14             |                                                         | ator B Overflow                                                   |                   |                   |                      |                  |                |  |  |  |  |

|                    |                                                         | ator B has overf                                                  |                   |                   |                      |                  |                |  |  |  |  |

|                    |                                                         | ator B has not o                                                  |                   |                   |                      |                  |                |  |  |  |  |

| bit 13             | SA: Accumul                                             | SA: Accumulator A Saturation 'Sticky' Status bit <sup>(1)</sup>   |                   |                   |                      |                  |                |  |  |  |  |

|                    |                                                         | 1 = Accumulator A is saturated or has been saturated at some time |                   |                   |                      |                  |                |  |  |  |  |

|                    |                                                         | ator A is not sat                                                 |                   |                   |                      |                  |                |  |  |  |  |

| bit 12             |                                                         | ator B Saturatio                                                  |                   |                   |                      |                  |                |  |  |  |  |

|                    |                                                         | ator B is saturate<br>ator B is not sate                          |                   | en saturated at   | some time            |                  |                |  |  |  |  |

| bit 11             | <b>OAB:</b> OA    C                                     | B Combined A                                                      | ccumulator O      | verflow Status    | bit                  |                  |                |  |  |  |  |

|                    |                                                         | ator A or B has o                                                 |                   | owed              |                      |                  |                |  |  |  |  |

| bit 10             | <b>SAB:</b> SA    S                                     | B Combined Ac                                                     | cumulator 'St     | ticky' Status bit | (1,4)                |                  |                |  |  |  |  |

|                    |                                                         | ator A or B is sa<br>ccumulator A o                               |                   |                   | ed at some time      | in the past      |                |  |  |  |  |

| bit 9              | DA: DO Loop                                             | Active bit                                                        |                   |                   |                      |                  |                |  |  |  |  |

|                    | 1 = DO loop ir<br>0 = DO loop n                         | n progress<br>ot in progress                                      |                   |                   |                      |                  |                |  |  |  |  |

| bit 8              | DC: MCU AL                                              | U Half Carry/Bo                                                   | orrow bit         |                   |                      |                  |                |  |  |  |  |

|                    | of the res                                              | sult occurred                                                     |                   | -                 | data) or 8th low-o   | ·                |                |  |  |  |  |

|                    | •                                                       | -out from the 41<br>he result occuri                              |                   | oit (for byte-siz | ed data) or 8th      | low-order bit (f | for word-sized |  |  |  |  |

| Note 1:            | This bit can be rea                                     | d or cleared (no                                                  | ot set).          |                   |                      |                  |                |  |  |  |  |

| 2:                 | The IPL<2:0> bits<br>Level (IPL). The value $(IPL) = 1$ | are concatenat                                                    | ed with the IF    |                   |                      |                  |                |  |  |  |  |

- IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

- 4: Clearing this bit will clear SA and SB.

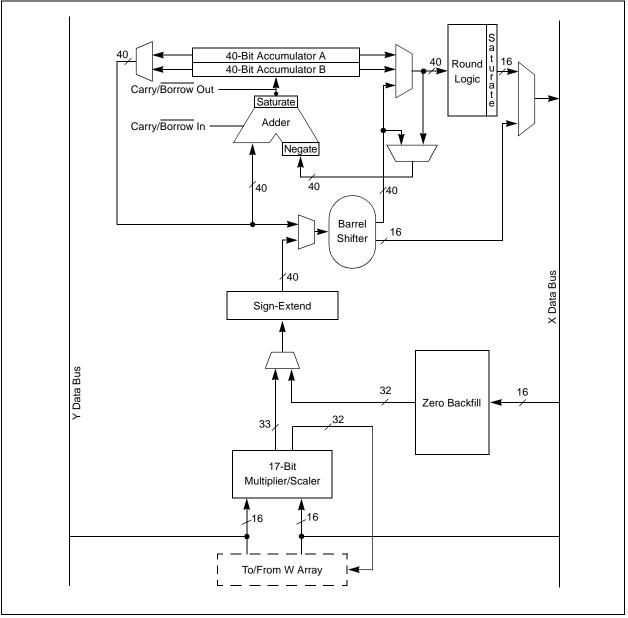

#### FIGURE 3-3: DSP ENGINE BLOCK DIAGRAM

|              | ABLE 4-9: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ32GS608 |         |         |          |         |         |          |          |          |          |          |          |          |         |          |          |          |               |

|--------------|------------------------------------------------------------------|---------|---------|----------|---------|---------|----------|----------|----------|----------|----------|----------|----------|---------|----------|----------|----------|---------------|

| File<br>Name | SFR<br>Addr                                                      | Bit 15  | Bit 14  | Bit 13   | Bit 12  | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| INTCON1      | 0080                                                             | NSTDIS  | OVAERR  | OVBERR   | COVAERR | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  |          | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | —        | 0000          |

| INTCON2      | 0082                                                             | ALTIVT  | DISI    | _        | _       | _       | _        | _        | _        | _        | _        | _        | INT4EP   | INT3EP  | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0         | 0084                                                             | _       | _       | ADIF     | U1TXIF  | U1RXIF  | SPI1IF   | SPI1EIF  | T3IF     | T2IF     | OC2IF    | IC2IF    | —        | T1IF    | OC1IF    | IC1IF    | INTOIF   | 0000          |

| IFS1         | 0086                                                             | U2TXIF  | U2RXIF  | INT2IF   | T5IF    | T4IF    | OC4IF    | OC3IF    | _        | _        | _        | _        | INT1IF   | CNIF    | AC1IF    | MI2C1IF  | SI2C1IF  | 0000          |

| IFS2         | 8800                                                             | _       | _       | _        | _       | _       | _        | _        | _        | —        | IC4IF    | IC3IF    | _        | _       | _        | SPI2IF   | SPI2EIF  | 0000          |

| IFS3         | 008A                                                             | _       | _       | _        | _       | _       | QEI1IF   | PSEMIF   | _        | —        | INT4IF   | INT3IF   | _        | _       | MI2C2IF  | SI2C2IF  | _        | 0000          |

| IFS4         | 008C                                                             | _       | _       | _        | _       | QEI2IF  | _        | PSESMIF  | _        | —        | _        | _        | _        | _       | U2EIF    | U1EIF    | _        | 0000          |

| IFS5         | 008E                                                             | PWM2IF  | PWM1IF  | ADCP12IF | _       | _       | _        | _        | _        | —        | _        | _        | _        | _       | _        | ADCP8IF  | _        | 0000          |

| IFS6         | 0090                                                             | ADCP1IF | ADCP0IF | _        | -       | _       |          | AC4IF    | AC3IF    | AC2IF    |          | PWM8IF   | PWM7IF   | PWM6IF  | PWM5IF   | PWM4IF   | PWM3IF   | 0000          |

| IFS7         | 0092                                                             | _       | _       | _        | _       | _       | _        |          | _        | _        | _        | ADCP7IF  | ADCP6IF  | ADCP5IF | ADCP4IF  | ADCP3IF  | ADCP2IF  | 0000          |

| IEC0         | 0094                                                             |         | _       | ADIE     | U1TXIE  | U1RXIE  | SPI1IE   | SPI1EIE  | T3IE     | T2IE     | OC2IE    | IC2IE    | _        | T1IE    | OC1IE    | IC1IE    | INTOIE   | 0000          |

| IEC1         | 0096                                                             | U2TXIE  | U2RXIE  | INT2IE   | T5IE    | T4IE    | OC4IE    | OC3IE    | _        | _        | -        | _        | INT1IE   | CNIE    | _        | MI2C1IE  | SI2C1IE  | 0000          |

| IEC2         | 0098                                                             | -       | _       | _        | _       | _       |          |          | _        | _        | IC4IE    | IC3IE    | _        |         | _        | SPI2IE   | SPI2EIE  | 0000          |

| IEC3         | 009A                                                             |         | _       | _        | -       | _       | QEI1IE   | PSEMIE   | _        | _        | INT4IE   | INT3IE   | _        |         | MI2C2IE  | SI2C2IE  | _        | 0000          |

| IEC4         | 009C                                                             |         | _       | _        | -       | QEI2IE  |          | PSESMIE  | _        | _        | -        | _        | _        |         | U2EIE    | U1EIE    | _        | 0000          |

| IEC5         | 009E                                                             | PWM2IE  | PWM1IE  | ADCP12IE | -       | _       |          |          | _        | _        |          | _        | _        |         | _        | ADCP8IE  | _        | 0000          |

| IEC6         | 00A0                                                             | ADCP1IE | ADCP0IE | _        | -       | _       |          | AC4IE    | AC3IE    | AC2IE    |          | PWM8IE   | PWM7IE   | PWM6IE  | PWM5IE   | PWM4IE   | PWM3IE   | 0000          |

| IEC7         | 00A2                                                             | _       | _       | _        | _       | _       | _        | _        | _        | _        | _        | ADCP7IE  | ADCP6IE  | ADCP5IE | ADCP4IE  | ADCP3IE  | ADCP2IE  | 0000          |

| IPC0         | 00A4                                                             |         | T1IP2   | T1IP1    | T1IP0   | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2   | IC1IP1   | IC1IP0   |         | INT0IP2  | INT0IP1  | INT0IP0  | 4444          |

| IPC1         | 00A6                                                             |         | T2IP2   | T2IP1    | T2IP0   | _       | OC2IP2   | OC2IP1   | OC2IP0   | _        | IC2IP2   | IC2IP1   | IC2IP0   |         | _        | _        | _        | 4440          |

| IPC2         | 00A8                                                             |         | U1RXIP2 | U1RXIP1  | U1RXIP0 | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 |         | T3IP2    | T3IP1    | T3IP0    | 4444          |

| IPC3         | 00AA                                                             |         | _       | _        | _       | _       |          |          | _        | _        | ADIP2    | ADIP1    | ADIP0    |         | U1TXIP2  | U1TXIP1  | U1TXIP0  | 0044          |

| IPC4         | 00AC                                                             |         | CNIP2   | CNIP1    | CNIP0   | _       | AC1IP2   | AC1IP1   | AC1IP0   | _        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 |         | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 | 4444          |

| IPC5         | 00AE                                                             |         | _       | _        | _       | _       |          |          | _        | _        | -        | _        | _        |         | INT1IP2  | INT1IP1  | INT1IP0  | 0004          |

| IPC6         | 00B0                                                             |         | T4IP2   | T4IP1    | T4IP0   | _       | OC4IP2   | OC4IP1   | OC4IP0   | _        | OC3IP2   | OC3IP1   | OC3IP0   |         | _        | _        | _        | 4440          |

| IPC7         | 00B2                                                             | _       | U2TXIP2 | U2TXIP1  | U2TXIP0 | _       | U2RXIP2  | U2RXIP1  | U2RXIP0  | —        | INT2IP2  | INT2IP1  | INT2IP0  | _       | T5IP2    | T5IP1    | T5IP0    | 4444          |

| IPC8         | 00B4                                                             |         | _       | _        | _       | _       |          |          | _        | _        | SPI2IP2  | SPI2IP1  | SPI2IP0  |         | SPI2EIP2 | SPI2EIP1 | SPI2EIP0 | 0044          |

| IPC9         | 00B6                                                             |         | _       | _        | -       | _       | IC4IP2   | IC4IP1   | IC4IP0   | _        | IC3IP2   | IC3IP1   | IC3IP0   |         | _        | _        | _        | 0440          |

| IPC12        | 00BC                                                             | _       | _       | _        | _       | _       | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 | —        | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 | _       | _        | _        | _        | 0440          |

| IPC13        | 00BE                                                             | _       | _       | _        | _       | _       | INT4IP2  | INT4IP1  | INT4IP0  | —        | INT3IP2  | INT3IP1  | INT3IP0  | _       | —        | _        | —        | 0440          |

| IPC14        | 00C0                                                             | _       | _       | _        | _       | _       | QEI1IP2  | QEI1IP1  | QEI1IP0  | _        | PSEMIP2  | PSEMIP1  | PSEMIP0  | _       | _        | _        | _        | 0440          |

| IPC16        | 00C4                                                             | _       | _       | _        | _       | _       | U2EIP2   | U2EIP1   | U2EIP0   | _        | U1EIP2   | U1EIP1   | U1EIP0   | _       | _        | _        | _        | 0440          |

| IPC18        | 00C8                                                             | _       | QEI2IP2 | QEI2IP1  | QEI2IP0 | _       | —        | —        | —        | _        | PSESMIP2 | PSESMIP1 | PSESMIP0 | _       | _        | _        | _        | 4040          |

| IPC20        | 00CC                                                             |         |         |          |         |         |          | _        |          | _        | ADCP8IP2 | ADCP8IP1 | ADCP8IP0 | _       | _        | _        | _        | 0040          |

#### TABLE 4-9: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ32GS608

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | SFR<br>Addr | Bit 15         | Bit 14            | Bit 13  | Bit 13         Bit 12         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         Bit 0 |           |           |           |           |          |         |          | All<br>Resets |          |          |          |          |      |

|--------------|-------------|----------------|-------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|-----------|----------|---------|----------|---------------|----------|----------|----------|----------|------|

| PWMCON7      | 04E0        | FLTSTAT        | CLSTAT            | TRGSTAT | FLTIEN                                                                                                                                                                                         | CLIEN     | TRGIEN    | ITB       | MDCS      | DTC1     | DTC0    | DTCP     | _             | MTBS     | CAM      | XPRES    | IUE      | 0000 |

| IOCON7       | 04E2        | PENH           | PENL              | POLH    | POLL                                                                                                                                                                                           | PMOD1     | PMOD0     | OVRENH    | OVRENL    | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0       | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000 |

| FCLCON7      | 04E4        | IFLTMOD        | CLSRC4            | CLSRC3  | CLSRC2                                                                                                                                                                                         | CLSRC1    | CLSRC0    | CLPOL     | CLMOD     | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1       | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000 |

| PDC7         | 04E6        |                | PDC7<15:0> (      |         |                                                                                                                                                                                                |           |           |           |           |          |         |          |               | 0000     |          |          |          |      |

| PHASE7       | 04E8        |                | PHASE7<15:0>      |         |                                                                                                                                                                                                |           |           |           |           |          |         |          | 0000          |          |          |          |          |      |

| DTR7         | 04EA        | — — DTR7<13:0> |                   |         |                                                                                                                                                                                                |           |           |           |           |          |         | 0000     |               |          |          |          |          |      |

| ALTDTR7      | 04EA        | _              | — — ALTDTR7<13:0> |         |                                                                                                                                                                                                |           |           |           |           |          |         |          | 0000          |          |          |          |          |      |

| SDC7         | 04EE        |                |                   |         |                                                                                                                                                                                                |           |           |           | SDC.      | 7<15:0>  |         |          |               |          |          |          |          | 0000 |

| SPHASE7      | 04F0        |                |                   |         |                                                                                                                                                                                                |           |           |           | SPHAS     | E7<15:0> |         |          |               |          |          |          |          | 0000 |

| TRIG7        | 04F2        |                |                   |         |                                                                                                                                                                                                |           |           | TRGCMP<12 | ::0>      |          |         |          |               |          | -        | _        | _        | 0000 |

| TRGCON7      | 04F4        | TRGDIV3        | TRGDIV2           | TRGDIV1 | TRGDIV0                                                                                                                                                                                        | _         | _         | _         | _         | DTM      | —       | TRGSTRT5 | TRGSTRT4      | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000 |

| STRIG7       | 04F6        |                |                   |         |                                                                                                                                                                                                |           | ;         | STRGCMP<1 | 2:0>      |          |         |          |               |          | _        | _        | —        | 0000 |

| PWMCAP7      | 04F8        |                |                   |         |                                                                                                                                                                                                |           |           | PWMCAP<12 | 2:0>      |          |         |          |               |          | _        | _        | —        | 0000 |

| LEBCON7      | 04FA        | PHR            | PHF               | PLR     | PLF                                                                                                                                                                                            | FLTLEBEN  | CLLEBEN   | _         | —         | _        | _       | BCH      | BCL           | BPHH     | BPHL     | BPLH     | BPLL     | 0000 |

| LEBDLY7      | 04FC        | _              | LEB<8:0>          |         |                                                                                                                                                                                                |           |           |           |           |          |         |          | 0000          |          |          |          |          |      |

| AUXCON7      | 04FE        | HRPDIS         | HRDDIS            | _       | _                                                                                                                                                                                              | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 | _        | _       | CHOPSEL3 | CHOPSEL2      | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000 |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0         | R/W-0                                                                                                                      | U-0                                                                             | U-0            | U-0                   | U-0               | U-0              | R/W-0         |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------|-----------------------|-------------------|------------------|---------------|--|--|--|--|--|

| TRAPR         | IOPUWR                                                                                                                     | —                                                                               | —              | —                     | —                 | —                | VREGS         |  |  |  |  |  |

| bit 15        |                                                                                                                            |                                                                                 | •              | •                     | •                 |                  | bit 8         |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                      | R/W-0                                                                           | R/W-0          | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |  |  |  |  |  |

| EXTR          | SWR                                                                                                                        | SWDTEN <sup>(2)</sup>                                                           | WDTO           | SLEEP                 | IDLE              | BOR              | POR           |  |  |  |  |  |

| bit 7         |                                                                                                                            |                                                                                 |                |                       |                   |                  | bit C         |  |  |  |  |  |

| Legend:       |                                                                                                                            |                                                                                 |                |                       |                   |                  |               |  |  |  |  |  |

| R = Readabl   | le bit                                                                                                                     | W = Writable                                                                    | bit            | U = Unimpler          | mented bit, read  | t as '0'         |               |  |  |  |  |  |

| -n = Value at |                                                                                                                            | '1' = Bit is set                                                                |                | '0' = Bit is cle      |                   | x = Bit is unk   | nown          |  |  |  |  |  |

|               |                                                                                                                            |                                                                                 |                |                       |                   |                  |               |  |  |  |  |  |

| bit 15        | TRAPR: Trap                                                                                                                | Reset Flag bit                                                                  |                |                       |                   |                  |               |  |  |  |  |  |

|               |                                                                                                                            | onflict Reset ha                                                                |                |                       |                   |                  |               |  |  |  |  |  |

|               | 0 = A Trap C                                                                                                               | onflict Reset ha                                                                | s not occurre  | d                     |                   |                  |               |  |  |  |  |  |

| bit 14        |                                                                                                                            | egal Opcode or                                                                  |                |                       | -                 |                  |               |  |  |  |  |  |

|               |                                                                                                                            | al opcode dete                                                                  |                | gal address mo        | ode or Uninitia   | lized W registe  | er used as an |  |  |  |  |  |

|               |                                                                                                                            | Pointer caused                                                                  |                | Booot hoo not         | occurred          |                  |               |  |  |  |  |  |

| bit 13-9      | -                                                                                                                          | 0 = An Illegal Opcode or Uninitialized W Reset has not occurred                 |                |                       |                   |                  |               |  |  |  |  |  |

| bit 8         | -                                                                                                                          | Unimplemented: Read as '0'<br>VREGS: Voltage Regulator Standby During Sleep bit |                |                       |                   |                  |               |  |  |  |  |  |

| DILO          |                                                                                                                            | egulator is activ                                                               | •              | •                     |                   |                  |               |  |  |  |  |  |

|               |                                                                                                                            |                                                                                 |                |                       | ep                |                  |               |  |  |  |  |  |

| bit 7         | <ul> <li>0 = Voltage regulator goes into Standby mode during Sleep</li> <li>EXTR: External Reset Pin (MCLR) bit</li> </ul> |                                                                                 |                |                       |                   |                  |               |  |  |  |  |  |

|               | 1 = A Master Clear (pin) Reset has occurred                                                                                |                                                                                 |                |                       |                   |                  |               |  |  |  |  |  |

|               | 0 = A Master Clear (pin) Reset has not occurred                                                                            |                                                                                 |                |                       |                   |                  |               |  |  |  |  |  |

| bit 6         |                                                                                                                            | are Reset Flag (                                                                |                |                       |                   |                  |               |  |  |  |  |  |

|               | 1 = A reset                                                                                                                | instruction has                                                                 | been execute   | ed                    |                   |                  |               |  |  |  |  |  |

|               | 0 = A  RESET                                                                                                               | instruction has                                                                 | not been exe   | cuted                 |                   |                  |               |  |  |  |  |  |

| bit 5         | SWDTEN: So                                                                                                                 | oftware Enable/                                                                 | Disable of W   | DT bit <sup>(2)</sup> |                   |                  |               |  |  |  |  |  |

|               | 1 = WDT is e                                                                                                               |                                                                                 |                |                       |                   |                  |               |  |  |  |  |  |

|               | 0 = WDT is d                                                                                                               |                                                                                 | a aut Elas hi  |                       |                   |                  |               |  |  |  |  |  |

| bit 4         |                                                                                                                            | hdog Timer Tin<br>e-out has occur                                               | -              | τ                     |                   |                  |               |  |  |  |  |  |

|               |                                                                                                                            | e-out has occur                                                                 |                |                       |                   |                  |               |  |  |  |  |  |

| bit 3         |                                                                                                                            | e-up from Slee                                                                  |                |                       |                   |                  |               |  |  |  |  |  |

|               |                                                                                                                            | as been in Slee                                                                 | •              |                       |                   |                  |               |  |  |  |  |  |

|               |                                                                                                                            | as not been in S                                                                |                |                       |                   |                  |               |  |  |  |  |  |

| bit 2         | IDLE: Wake-                                                                                                                | up from Idle Fla                                                                | ig bit         |                       |                   |                  |               |  |  |  |  |  |

|               |                                                                                                                            | as been in Idle i                                                               | -              |                       |                   |                  |               |  |  |  |  |  |

|               | 0 = Device ha                                                                                                              | as not been in I                                                                | dle mode       |                       |                   |                  |               |  |  |  |  |  |

| bit 1         | BOR: Brown                                                                                                                 | -out Reset Flag                                                                 | bit            |                       |                   |                  |               |  |  |  |  |  |

|               | 1 = A Brown-                                                                                                               | out Reset has o                                                                 | occurred       |                       |                   |                  |               |  |  |  |  |  |

|               |                                                                                                                            | out Reset has r                                                                 |                |                       |                   |                  |               |  |  |  |  |  |

| bit 0         |                                                                                                                            | on Reset Flag                                                                   |                |                       |                   |                  |               |  |  |  |  |  |

|               |                                                                                                                            | on Reset has o<br>on Reset has n                                                |                |                       |                   |                  |               |  |  |  |  |  |

| Note 1: A     | II of the Reset sta                                                                                                        |                                                                                 |                | d in software. S      | Settina one of th | ese bits in soft | ware does not |  |  |  |  |  |

|               | ause a device Re                                                                                                           |                                                                                 |                |                       |                   |                  |               |  |  |  |  |  |

| 2. If         | the FWDTEN Co                                                                                                              | onfiguration hit                                                                | is '1' (unnroa | rammed) the V         | WDT is always (   | anabled regar    | these of the  |  |  |  |  |  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

cause a device Reset.

If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| U-0           | U-0                        | U-0              | U-0              | U-0              | R/W-1           | R/W-0           | R/W-0  |  |  |  |  |  |

|---------------|----------------------------|------------------|------------------|------------------|-----------------|-----------------|--------|--|--|--|--|--|

| _             | —                          | —                | —                | —                | U2EIP2          | U2EIP1          | U2EIP0 |  |  |  |  |  |

| bit 15        | ·                          |                  |                  |                  |                 |                 | bit 8  |  |  |  |  |  |

|               |                            |                  |                  |                  |                 |                 |        |  |  |  |  |  |

| U-0           | R/W-1                      | R/W-0            | R/W-0            | U-0              | U-0             | U-0             | U-0    |  |  |  |  |  |

| _             | U1EIP2                     | U1EIP1           | U1EIP0           | —                | _               | —               | —      |  |  |  |  |  |

| bit 7         |                            |                  |                  |                  |                 |                 | bit C  |  |  |  |  |  |

|               |                            |                  |                  |                  |                 |                 |        |  |  |  |  |  |

| Legend:       |                            |                  |                  |                  |                 |                 |        |  |  |  |  |  |

| R = Readable  | e bit                      | W = Writable     | bit              | U = Unimple      | mented bit, rea | d as '0'        |        |  |  |  |  |  |

| -n = Value at | POR                        | '1' = Bit is set | t                | '0' = Bit is cle | eared           | x = Bit is unkr | nown   |  |  |  |  |  |

|               |                            |                  |                  |                  |                 |                 |        |  |  |  |  |  |

| bit 15-11     | Unimplemented: Read as '0' |                  |                  |                  |                 |                 |        |  |  |  |  |  |

| bit 10-8      | U2EIP<2:0>:                | UART2 Error      | Interrupt Priori | ty bits          |                 |                 |        |  |  |  |  |  |

|               | 111 = Interru              | pt is Priority 7 | (highest priorit | y interrupt)     |                 |                 |        |  |  |  |  |  |

|               | •                          |                  |                  |                  |                 |                 |        |  |  |  |  |  |

|               | •                          |                  |                  |                  |                 |                 |        |  |  |  |  |  |

|               | 001 = Interru              | pt is Priority 1 |                  |                  |                 |                 |        |  |  |  |  |  |

|               |                            | pt source is dis | sabled           |                  |                 |                 |        |  |  |  |  |  |

| bit 7         | Unimplemen                 | ted: Read as '   | 0'               |                  |                 |                 |        |  |  |  |  |  |

| bit 6-4       | U1EIP<2:0>:                | UART1 Error      | Interrupt Priori | ty bits          |                 |                 |        |  |  |  |  |  |

|               | 111 = Interru              | pt is Priority 7 | (highest priorit | y interrupt)     |                 |                 |        |  |  |  |  |  |

|               | •                          |                  |                  |                  |                 |                 |        |  |  |  |  |  |

|               | •                          |                  |                  |                  |                 |                 |        |  |  |  |  |  |

|               | 001 = Interru              | pt is Priority 1 |                  |                  |                 |                 |        |  |  |  |  |  |

|               |                            | pt source is dis | sabled           |                  |                 |                 |        |  |  |  |  |  |

| bit 3-0       | Unimplemen                 | ted: Read as '   | 0'               |                  |                 |                 |        |  |  |  |  |  |

|               |                            |                  |                  |                  |                 |                 |        |  |  |  |  |  |

#### REGISTER 7-34: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0                                                                | U-0                                                                                                                          | U-0                                                                                                                                                                                                                             | U-0      | U-0          | U-0              | U-0      | U-0      |  |  |  |  |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|------------------|----------|----------|--|--|--|--|

| —                                                                  | —                                                                                                                            | —                                                                                                                                                                                                                               | —        | —            | —                | —        | —        |  |  |  |  |

| bit 15                                                             |                                                                                                                              |                                                                                                                                                                                                                                 |          |              |                  |          | bit 8    |  |  |  |  |

|                                                                    |                                                                                                                              |                                                                                                                                                                                                                                 |          |              |                  |          |          |  |  |  |  |

| U-0                                                                | R/W-1                                                                                                                        | R/W-0                                                                                                                                                                                                                           | R/W-0    | U-0          | R/W-1            | R/W-0    | R/W-0    |  |  |  |  |

| —                                                                  | ADCP7IP2                                                                                                                     | ADCP7IP1                                                                                                                                                                                                                        | ADCP7IP0 |              | ADCP6IP2         | ADCP6IP1 | ADCP6IP0 |  |  |  |  |

| bit 7                                                              |                                                                                                                              |                                                                                                                                                                                                                                 |          |              |                  |          | bit 0    |  |  |  |  |

|                                                                    |                                                                                                                              |                                                                                                                                                                                                                                 |          |              |                  |          |          |  |  |  |  |

| Legend:                                                            |                                                                                                                              |                                                                                                                                                                                                                                 |          |              |                  |          |          |  |  |  |  |

| R = Readabl                                                        | e bit                                                                                                                        | W = Writable                                                                                                                                                                                                                    | bit      | U = Unimplei | mented bit, read | as '0'   |          |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is |                                                                                                                              |                                                                                                                                                                                                                                 |          |              |                  |          | nown     |  |  |  |  |

| bit 15-7<br>bit 6-4<br>bit 3                                       | ADCP7IP<2:0<br>111 = Interrup<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | Unimplemented: Read as '0'<br>ADCP7IP<2:0>: ADC Pair 7 Conversion Done Interrupt 1 Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |          |              |                  |          |          |  |  |  |  |

| bit 2-0                                                            | 111 = Interrup<br>•<br>•<br>001 = Interrup                                                                                   | Unimplemented: Read as '0'<br>ADCP6IP<2:0>: ADC Pair 6 Conversion Done Interrupt 1 Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |          |              |                  |          |          |  |  |  |  |

#### REGISTER 7-45: IPC29: INTERRUPT PRIORITY CONTROL REGISTER 29

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

## REGISTER 8-5: DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0           | R/W-0 |

|-----------------|-------|------------------|------------------------------------|----------------------|-------|-----------------|-------|

|                 |       |                  | PAD<                               | 15:8> <b>(2)</b>     |       |                 |       |

| bit 15          |       |                  |                                    |                      |       |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0           | R/W-0 |

|                 |       |                  |                                    | <7:0> <sup>(2)</sup> |       |                 |       |

| bit 7           |       |                  |                                    |                      |       |                 | bit 0 |

| Legend:         |       |                  |                                    |                      |       |                 |       |

| R = Readable I  | bit   | W = Writable b   | U = Unimplemented bit, read as '0' |                      |       |                 |       |

| -n = Value at P | OR    | '1' = Bit is set |                                    | '0' = Bit is cle     | ared  | x = Bit is unkr | nown  |

bit 15-0 PAD<15:0>: Peripheral Address Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** See Table 8-1 for a complete list of peripheral addresses.

#### REGISTER 16-8: SSEVTCMP: PWM SECONDARY SPECIAL EVENT COMPARE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0             | R/W-0            | R/W-0          | R/W-0 |

|-----------------|-------|------------------|--------|-------------------|------------------|----------------|-------|

|                 |       |                  | SSEVTC | MP<12:5>          |                  |                |       |

| bit 15          |       |                  |        |                   |                  |                | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0             | U-0              | U-0            | U-0   |

| 10,00-0         |       | SSEVTCMP<4:0     |        | 17/07-0           |                  |                |       |

| bit 7           |       |                  |        |                   |                  |                | bit 0 |

| Legend:         |       |                  |        |                   |                  |                |       |

| R = Readable    | bit   | W = Writable b   | oit    | U = Unimplem      | nented bit, read | l as '0'       |       |

| -n = Value at I | POR   | '1' = Bit is set |        | '0' = Bit is clea | ared             | x = Bit is unk | nown  |

bit 15-3 SSEVTCMP<12:0>: Special Event Compare Count Value bits

bit 2-0 Unimplemented: Read as '0'

# **REGISTER 16-9:** CHOP: PWM CHOP CLOCK GENERATOR REGISTER<sup>(1)</sup>

| R/W-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    |

|----------|-----|-----|-----|-----|-----|----------|----------|

| CHPCLKEN | —   | —   | —   | —   | —   | CHOPCLK6 | CHOPCLK5 |

| bit 15   |     |     |     |     |     |          | bit 8    |

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | U-0 | U-0 | U-0   |

|----------|----------|----------|----------|----------|-----|-----|-------|

| CHOPCLK4 | CHOPCLK3 | CHOPCLK2 | CHOPCLK1 | CHOPCLK0 | —   | —   | —     |

| bit 7    |          |          |          |          |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15    | <b>CHPCLKEN:</b> Enable Chop Clock Generator bit<br>1 = Chop clock generator is enabled<br>0 = Chop clock generator is disabled |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| bit 14-10 | Unimplemented: Read as '0'                                                                                                      |

| bit 9-3   | CHOPCLK<6:0>: Chop Clock Divider bits                                                                                           |

|           | Value in 8.32 ns increments. The frequency of the chop clock signal is given by the following expression:                       |

|           | Chop Frequency = 1/(16.64 * (CHOPCLK<6:0> + 1) * Primary Master PWM Input Clock Period)                                         |

| bit 2-0   | Unimplemented: Read as '0'                                                                                                      |

|           |                                                                                                                                 |

**Note 1:** The chop clock generator operates with the primary PWM clock prescaler (PCLKDIV<2:0>) in the PTCON2 register (Register 16-2).

| U-0                                | U-0          | U-0               | U-0                               | R/W-0                              | R/W-0             | R/W-0     | R/W-0 |  |

|------------------------------------|--------------|-------------------|-----------------------------------|------------------------------------|-------------------|-----------|-------|--|

| _                                  | —            | —                 | —                                 |                                    | LEB<              | <8:5>     |       |  |

| bit 15                             |              | -                 |                                   |                                    |                   |           | bit 8 |  |

|                                    |              |                   |                                   |                                    |                   |           |       |  |

| R/W-0                              | R/W-0        | R/W-0             | R/W-0                             | R/W-0                              | U-0               | U-0       | U-0   |  |

|                                    |              | LEB<4:0>          |                                   |                                    | _                 | —         | —     |  |

| bit 7                              |              |                   |                                   |                                    |                   |           | bit 0 |  |

|                                    |              |                   |                                   |                                    |                   |           |       |  |

| Legend:                            |              |                   |                                   |                                    |                   |           |       |  |