Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, QEI, POR, PWM, WDT                                 |

| Number of I/O              | 58                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 9K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b; D/A 1x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs606-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

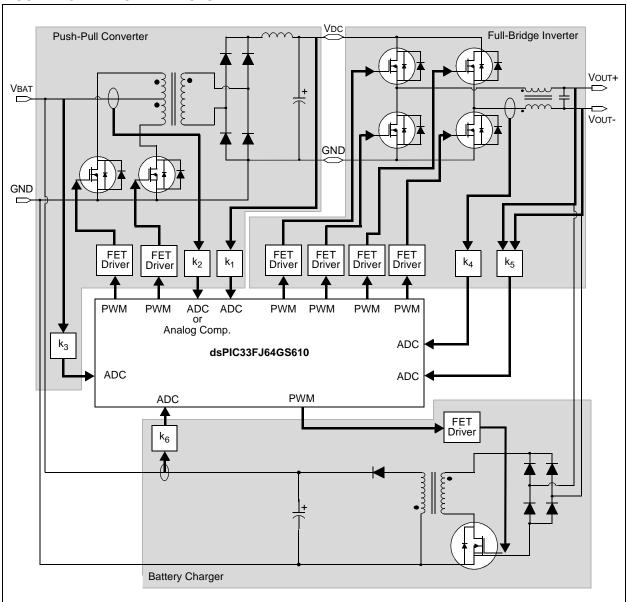

### FIGURE 2-8: OFF-LINE UPS

| REGISTER     |                                  | ON: CORE (                           |                  |                             |                    |                    | <b>.</b> -   |

|--------------|----------------------------------|--------------------------------------|------------------|-----------------------------|--------------------|--------------------|--------------|

| U-0          | U-0                              | U-0                                  | R/W-0            | R/W-0<br>EDT <sup>(1)</sup> | R-0                | R-0                | R-0          |

|              | _                                |                                      | US               | EDI                         | DL2                | DL1                | DL0          |

| bit 15       |                                  |                                      |                  |                             |                    |                    | bit          |

| R/W-0        | R/W-0                            | R/W-1                                | R/W-0            | R/C-0                       | R/W-0              | R/W-0              | R/W-0        |

| SATA         | SATB                             | SATDW                                | ACCSAT           | IPL3 <sup>(2)</sup>         | PSV                | RND                | IF           |

| bit 7        |                                  |                                      |                  |                             |                    |                    | bit          |

| Legend:      |                                  | C = Clearable                        | e bit            |                             |                    |                    |              |

| R = Readab   | le bit                           | W = Writable                         | bit              |                             | mented bit, read   | 1 as '0'           |              |

| -n = Value a | t POR                            | '1' = Bit is se                      | t                | '0' = Bit is cle            | eared              | x = Bit is unkr    | nown         |

| bit 15-13    | Unimplemen                       | ted: Read as                         | ʻ0'              |                             |                    |                    |              |

| bit 12       |                                  | tiply Unsigned                       | -                | ol bit                      |                    |                    |              |

|              |                                  | ine multiplies a<br>ine multiplies a |                  |                             |                    |                    |              |

| bit 11       | •                                | D Loop Termina                       | •                | <sub>it</sub> (1)           |                    |                    |              |

|              | 1 = Terminate<br>0 = No effect   | U U                                  | o loop at the e  | nd of the curre             | ent loop iteration | I                  |              |

| bit 10-8     | DL<2:0>: DO                      | Loop Nesting                         | Level Status b   | its                         |                    |                    |              |

|              | 111 <b>= 7</b> DO <b>I</b> C     | ops are active                       |                  |                             |                    |                    |              |

|              | •                                |                                      |                  |                             |                    |                    |              |

|              | •                                |                                      |                  |                             |                    |                    |              |

|              | 001 = 1  DO Ic<br>000 = 0  DO Ic | oop is active<br>oops are active     |                  |                             |                    |                    |              |

| bit 7        | SATA: ACCA                       | Saturation En                        | able bit         |                             |                    |                    |              |

|              |                                  | ator A saturation                    |                  |                             |                    |                    |              |

| bit 6        |                                  | ator A saturation<br>Saturation Er   |                  |                             |                    |                    |              |

| DIT U        |                                  | ator B saturation                    |                  |                             |                    |                    |              |

|              | 0 = Accumula                     | ator B saturation                    | on is disabled   |                             |                    |                    |              |

| bit 5        |                                  | a Space Write                        | -                |                             | Enable bit         |                    |              |

|              |                                  | ce write satura<br>ce write satura   |                  |                             |                    |                    |              |

| bit 4        |                                  | cumulator Satura                     |                  |                             |                    |                    |              |

|              |                                  | ration (super s                      |                  |                             |                    |                    |              |

|              |                                  | ration (normal                       |                  |                             |                    |                    |              |

| bit 3        |                                  | terrupt Priority                     |                  |                             |                    |                    |              |

|              |                                  | rrupt Priority L<br>rrupt Priority L |                  |                             |                    |                    |              |

| bit 2        | PSV: Prograr                     | n Space Visibi                       | lity in Data Spa | ace Enable bit              |                    |                    |              |

|              | •                                | space is visible<br>space is not vi  | •                |                             |                    |                    |              |

| bit 1        | -                                | ng Mode Sele                         | -                |                             |                    |                    |              |

|              |                                  | onventional) re                      | -                |                             |                    |                    |              |

| 1.10         |                                  | (convergent)                         | -                |                             |                    |                    |              |

| bit 0        | -                                | Fractional Mu                        | -                |                             |                    |                    |              |

|              |                                  | ode is enabled<br>I mode is enab     |                  |                             |                    |                    |              |

| Note 1: ⊺    | his bit will always              | s read as '0'.                       |                  |                             |                    |                    |              |

|              | he IPI 3 hit is cor              |                                      | the IPI ~2.05    | hite (SP-7.5)               | ) to form the CE   | 21 I Interrunt Dri | ority I aval |

# REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

# 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space. All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All Effective Addresses (EAs) are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

## 4.2.6 DMA RAM

Some devices contain 1 Kbyte of dual ported DMA RAM, which is located at the end of Y data space. Memory locations that are part of Y data RAM and are in the DMA RAM space are accessible simultaneously by the CPU and the DMA Controller module. DMA RAM is utilized by the DMA Controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA Controller without having to steal cycles from the CPU.

When the CPU and the DMA Controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

# TABLE 4-1: CPU CORE REGISTER MAP (CONTINUED)

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8         | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-----------|---------------|----------|-------|-------|--------|-------|-------|-------|-------|---------------|

| CORCON       | 0044        | _      | —      | _      | US     | EDT    | DL2    | DL1       | DL0           | SATA     | SATB  | SATDW | ACCSAT | IPL3  | PSV   | RND   | IF    | 0000          |

| MODCON       | 0046        | XMODEN | YMODEN | -      | _      | BWM3   | BWM2   | BWM1      | BWM0          | YWM3     | YWM2  | YWM1  | YWM0   | XWM3  | XWM2  | XWM1  | XWM0  | 0000          |

| XMODSRT      | 0048        |        |        |        |        |        | Х      | (S<15:1>  |               |          |       |       |        |       |       |       | 0     | xxxx          |

| XMODEND      | 004A        |        |        |        |        |        | Х      | (E<15:1>  |               |          |       |       |        |       |       |       | 1     | xxxx          |

| YMODSRT      | 004C        |        |        |        |        |        | Y      | ′S<15:1>  |               |          |       |       |        |       |       |       | 0     | xxxx          |

| YMODEND      | 004E        |        |        |        |        |        | Y      | ′E<15:1>  |               |          |       |       |        |       |       |       | 1     | xxxx          |

| XBREV        | 0050        | BREN   | XB14   | XB13   | XB12   | XB11   | XB10   | XB9       | XB8           | XB7      | XB6   | XB5   | XB4    | XB3   | XB2   | XB1   | XB0   | xxxx          |

| DISICNT      | 0052        | _      | —      |        |        |        |        | Disable I | nterrupts Cou | nter Reg | ister |       |        |       |       |       |       | xxxx          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-11: TIMERS REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9       | Bit 8          | Bit 7         | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|-------------------|--------|--------|--------|----------|-------------|----------------|---------------|--------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1         | 0100        |        |                   |        |        |        |          |             | Timer1 Re      | gister        |              |        |        |       |       |       |       | 0000          |

| PR1          | 0102        |        |                   |        |        |        |          |             | Period Reg     | ister 1       |              |        |        |       |       |       |       | FFFF          |

| T1CON        | 0104        | TON    | —                 | TSIDL  | _      | _      | —        | _           | _              | _             | TGATE        | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000          |

| TMR2         | 0106        |        |                   |        |        |        |          |             | Timer2 Re      | gister        |              |        |        |       |       |       |       | 0000          |

| TMR3HLD      | 0108        |        |                   |        |        |        | Timer3 H | Holding Reg | gister (for 32 | 2-bit timer o | perations of | only)  |        |       |       |       |       | xxxx          |

| TMR3         | 010A        |        |                   |        |        |        |          |             | Timer3 Re      | gister        |              |        |        |       |       |       |       | 0000          |

| PR2          | 010C        |        |                   |        |        |        |          |             | Period Reg     | ister 2       |              |        |        |       |       |       |       | FFFF          |

| PR3          | 010E        |        |                   |        |        |        |          |             | Period Reg     | ister 3       |              |        |        |       |       |       |       | FFFF          |

| T2CON        | 0110        | TON    | _                 | TSIDL  | _      | _      | _        | _           | _              | _             | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T3CON        | 0112        | TON    | _                 | TSIDL  | _      | _      | _        | _           | _              | _             | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4         | 0114        |        |                   |        |        |        |          |             | Timer4 Re      | gister        |              |        |        |       |       |       |       | 0000          |

| TMR5HLD      | 0116        |        |                   |        |        |        | Timer5 H | Holding Reg | gister (for 32 | 2-bit timer o | perations of | only)  |        |       |       |       |       | xxxx          |

| TMR5         | 0118        |        |                   |        |        |        |          |             | Timer5 Re      | gister        |              |        |        |       |       |       |       | 0000          |

| PR4          | 011A        |        |                   |        |        |        |          |             | Period Reg     | ister 4       |              |        |        |       |       |       |       | FFFF          |

| PR5          | 011C        |        | Period Register 5 |        |        |        |          |             |                |               |              | FFFF   |        |       |       |       |       |               |

| T4CON        | 011E        | TON    | _                 | TSIDL  | _      | _      | _        | —           | —              | -             | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   |       | 0000          |

| T5CON        | 0120        | TON    | _                 | TSIDL  | _      | _      | _        | _           | _              | _             | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-12: INPUT CAPTURE REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8       | Bit 7      | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------------|------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| IC1BUF       | 0140        |        |        |        |        |        |        | Inpu  | t 1 Capture | e Register |       |       |       |       |       |       |       | xxxx          |

| IC1CON       | 0142        | _      | —      | ICSIDL | _      | _      | _      | _     | _           | ICTMR      | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

| IC2BUF       | 0144        |        |        |        |        |        |        | Inpu  | t 2 Capture | e Register |       |       |       |       |       |       |       | xxxx          |

| IC2CON       | 0146        | _      | —      | ICSIDL | _      | —      | —      |       | _           | ICTMR      | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

| IC3BUF       | 0148        |        |        |        |        |        |        | Inpu  | t 3 Capture | e Register |       |       |       |       |       |       |       | xxxx          |

| IC3CON       | 014A        | _      | —      | ICSIDL | _      | _      | _      | _     | _           | ICTMR      | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

| IC4BUF       | 014C        |        |        |        |        |        |        | Inpu  | t 4 Capture | e Register |       |       |       |       |       |       |       | xxxx          |

| IC4CON       | 014E        | _      | —      | ICSIDL | _      | _      | _      | _     | _           | ICTMR      | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 8000h and higher maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

# Note: PSV access is temporarily disabled during Table Reads/Writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data, to execute in a single cycle.

#### When CORCON < 2 > = 1 and EA < 15 > = 1: **Program Space** Data Space **PSVPAG** 15 0 0x000000 0x0000 02 Data EA<14:0> 0x010000 0x018000 The data in the page designated by PSVPAG is mapped into the upper half of the data memory 0x8000 space... **PSV** Area ...while the lower 15 bits of the EA specify an exact address within 0xFFFF the PSV area. This corresponds exactly to the same lower 15 bits of the actual program space address. 0x800000

# FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

# 6.4 External Reset (EXTR)

The External Reset is generated by driving the MCLR pin low. The MCLR pin is a Schmitt Trigger input with an additional glitch filter. Reset pulses that are longer than the minimum pulse width will generate a Reset. Refer to **Section 27.0 "Electrical Characteristics"** for minimum pulse width specifications. The External Reset (MCLR) pin (EXTR) bit in the Reset Control (RCON) register is set to indicate the MCLR Reset.

#### 6.4.1 EXTERNAL SUPERVISORY CIRCUIT

Many systems have external supervisory circuits that generate Reset signals to reset multiple devices in the system. This external Reset signal can be directly connected to the MCLR pin to reset the device when the rest of system is reset.

# 6.4.2 INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to reset the device, the External Reset pin (MCLR) should be tied directly or resistively to VDD. In this case, the MCLR pin will not be used to generate a Reset. The External Reset pin (MCLR) does not have an internal pull-up and must not be left unconnected.

# 6.5 Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the device will assert SYSRST, placing the device in a special Reset state. This Reset state will not re-initialize the clock. The clock source in effect prior to the RESET instruction will remain. SYSRST is released at the next instruction cycle and the Reset vector fetch will commence.

The Software Reset (SWR) flag (instruction) in the Reset Control (RCON<6>) register is set to indicate the Software Reset.

# 6.6 Watchdog Timer Time-out Reset (WDTO)

Whenever a Watchdog Timer Time-out Reset occurs, the device will asynchronously assert SYSRST. The clock source will remain unchanged. A WDT time-out during Sleep or Idle mode will wake-up the processor, but will not reset the processor.

The Watchdog Timer Time-out (WDTO) flag in the Reset Control (RCON<4>) register is set to indicate the Watchdog Timer Reset. Refer to **Section 24.4 "Watchdog Timer (WDT)**" for more information on the Watchdog Timer Reset.

# 6.7 Trap Conflict Reset

If a lower priority hard trap occurs while a higher priority trap is being processed, a hard Trap Conflict Reset occurs. The hard traps include exceptions of Priority Level 13 through Level 15, inclusive. The address error (Level 13) and oscillator error (Level 14) traps fall into this category.

The Trap Reset (TRAPR) flag in the Reset Control (RCON<15>) register is set to indicate the Trap Conflict Reset. Refer to **Section 7.0 "Interrupt Controller"** for more information on Trap Conflict Resets.

# 6.8 Illegal Condition Device Reset

An illegal condition device Reset occurs due to the following sources:

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

The Illegal Opcode or Uninitialized W Access Reset (IOPUWR) flag in the Reset Control (RCON<14>) register is set to indicate the illegal condition device Reset.

## 6.8.1 ILLEGAL OPCODE RESET

A device Reset is generated if the device attempts to execute an illegal opcode value that is fetched from program memory.

The Illegal Opcode Reset function can prevent the device from executing program memory sections that are used to store constant data. To take advantage of the Illegal Opcode Reset, use only the lower 16 bits of each program memory section to store the data values. The upper 8 bits should be programmed with 3Fh, which is an illegal opcode value.

#### 6.8.2 UNINITIALIZED W REGISTER RESET

Any attempt to use the Uninitialized W register as an Address Pointer will reset the device. The W register array (with the exception of W15) is cleared during all Resets and is considered uninitialized until written to.

#### 6.8.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (Boot and Secure Segment), that operation will cause a Security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a call, jump, computed jump, return, return from subroutine or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an interrupt or trap vector.

Refer to Section 24.8 "Code Protection and CodeGuard™ Security" for more information on Security Reset.

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| 11.0          |                                                              |                                      |                 |                  |                  |                 |         |

|---------------|--------------------------------------------------------------|--------------------------------------|-----------------|------------------|------------------|-----------------|---------|

| U-0           | U-0                                                          | U-0                                  | U-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |

| _             | —                                                            | _                                    | —               | —                | INT4IP2          | INT4IP1         | INT4IP0 |

| bit 15        |                                                              |                                      |                 |                  |                  |                 | bit 8   |

|               |                                                              |                                      |                 |                  |                  |                 |         |

| U-0           | R/W-1                                                        | R/W-0                                | R/W-0           | U-0              | U-0              | U-0             | U-0     |

| —             | INT3IP2                                                      | INT3IP1                              | INT3IP0         | —                | _                | —               | —       |

| bit 7         |                                                              |                                      |                 |                  |                  |                 | bit (   |

|               |                                                              |                                      |                 |                  |                  |                 |         |

| Legend:       |                                                              |                                      |                 |                  |                  |                 |         |

| R = Readable  | e bit                                                        | W = Writable                         | bit             | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value at | POR                                                          | '1' = Bit is set                     |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 10-8      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup | ot source is dis                     | highest priorit |                  |                  |                 |         |

| bit 7         | =                                                            | ted: Read as '                       |                 |                  |                  |                 |         |

| bit 6-4       | 111 = Interru<br>•<br>•                                      | External Internot is Priority 7 (    |                 |                  |                  |                 |         |

|               | 001 = Interru<br>000 = Interru                               | ot is Priority 1<br>ot source is dis | abled           |                  |                  |                 |         |

# REGISTER 7-32: IPC13: INTERRUPT PRIORITY CONTROL REGISTER 13

NOTES:

| REGISTER 9      | -2: CLKD                      |                  | DIVISOR REC                           | SISTER               |                  |                    |              |

|-----------------|-------------------------------|------------------|---------------------------------------|----------------------|------------------|--------------------|--------------|

| R/W-0           | R/W-0                         | R/W-1            | R/W-1                                 | R/W-0                | R/W-0            | R/W-0              | R/W-0        |

| ROI             | DOZE2                         | DOZE1            | DOZE0                                 | DOZEN <sup>(1)</sup> | FRCDIV2          | FRCDIV1            | FRCDIV0      |

| bit 15          | ·                             |                  |                                       |                      |                  | ·                  | bit 8        |

|                 |                               |                  |                                       |                      |                  |                    |              |

| R/W-0           | R/W-1                         | U-0              | R/W-0                                 | R/W-0                | R/W-0            | R/W-0              | R/W-0        |

| PLLPOST1        | PLLPOST0                      | —                | PLLPRE4                               | PLLPRE3              | PLLPRE2          | PLLPRE1            | PLLPRE0      |

| bit 7           |                               |                  |                                       |                      |                  |                    | bit 0        |

| Legend:         |                               |                  |                                       |                      |                  |                    |              |

| R = Readable    | bit                           | W = Writable     | bit                                   | U = Unimpler         | mented bit, read | d as '0'           |              |

| -n = Value at F |                               | '1' = Bit is se  |                                       | '0' = Bit is cle     |                  | x = Bit is unkr    | nown         |

|                 | U.V.                          |                  |                                       | 0 - Bit io oid       |                  |                    |              |

| bit 15          | ROI: Recover                  | r on Interrupt b | bit                                   |                      |                  |                    |              |

|                 |                               | -                |                                       | d the processo       | or clock/periphe | ral clock ratio is | s set to 1:1 |

|                 |                               |                  | ct on the DOZE                        |                      |                  |                    |              |

| bit 14-12       | DOZE<2:0>:                    | Processor Clo    | ck Reduction S                        | Select bits          |                  |                    |              |

|                 | 111 = FCY/12                  | -                |                                       |                      |                  |                    |              |

|                 | 110 = FCY/64                  |                  |                                       |                      |                  |                    |              |

|                 | 101 = FCY/32<br>100 = FCY/16  |                  |                                       |                      |                  |                    |              |

|                 | 100 = FCY/10<br>011 = FCY/8 ( |                  |                                       |                      |                  |                    |              |

|                 | 010 = FCY/4                   | (doradit)        |                                       |                      |                  |                    |              |

|                 | 001 = FCY/2                   |                  |                                       |                      |                  |                    |              |

|                 | 000 = FCY/1                   |                  |                                       |                      |                  |                    |              |

| bit 11          |                               | e Mode Enabl     |                                       |                      |                  |                    |              |

|                 |                               |                  | fies the ratio be<br>eral clock ratio |                      | ripheral clocks  | and the process    | sor clocks   |

| bit 10-8        | FRCDIV<2:0                    | Internal Fas     | t RC Oscillator                       | Postscaler bit       | s                |                    |              |

|                 | 111 <b>= FRC d</b> i          | •                |                                       |                      |                  |                    |              |

|                 | 110 = FRC di                  |                  |                                       |                      |                  |                    |              |

|                 | 101 = FRC di<br>100 = FRC di  | •                |                                       |                      |                  |                    |              |

|                 | 011 = FRC di                  |                  |                                       |                      |                  |                    |              |

|                 | 010 = FRC di                  | -                |                                       |                      |                  |                    |              |

|                 | 001 <b>= FRC d</b>            |                  |                                       |                      |                  |                    |              |

|                 |                               | ivide-by-1 (def  | ,                                     |                      |                  |                    |              |

| bit 7-6         |                               |                  | Output Divide                         | r Select bits (a     | lso denoted as   | 'N2', PLL posts    | caler)       |

|                 | 11 = Output/8                 |                  |                                       |                      |                  |                    |              |

|                 | 10 = Reserve<br>01 = Output/4 |                  |                                       |                      |                  |                    |              |

|                 | 00 = Output/2                 |                  |                                       |                      |                  |                    |              |

| bit 5           | •                             | ted: Read as     | '0'                                   |                      |                  |                    |              |

| bit 4-0         | •                             |                  |                                       | Divider bits (a      | also denoted as  | 'N1', PLL pres     | caler)       |

|                 | 00000 = Inpu<br>00001 = Inpu  | ıt/2 (default)   |                                       |                      |                  | , , ,              | ,            |

|                 | •                             |                  |                                       |                      |                  |                    |              |

|                 | •                             |                  |                                       |                      |                  |                    |              |

|                 | •                             |                  |                                       |                      |                  |                    |              |

|                 | 11111 = Inpu                  | ıt/33            |                                       |                      |                  |                    |              |

|                 | •                             |                  |                                       |                      |                  |                    |              |

#### \_\_\_\_\_

Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

# 22.3 Module Functionality

The High-Speed, 10-Bit ADC is designed to support power conversion applications when used with the High-Speed PWM module. The ADC may have one or two SAR modules, depending on the device variant. If two SARs are present on a device, two conversions can be processed at a time, yielding 4 Msps conversion rate. If only one SAR is present on a device, only one conversion can be processed at a time, yielding 2 Msps conversion rate. The High-Speed, 10-Bit ADC produces two 10-bit conversion results in a 0.5 microsecond.

The ADC module supports up to 24 external analog inputs and two internal analog inputs. To monitor reference voltage, two internal inputs, AN24 and AN25, are connected to EXTREF and INTREF, respectively.

The analog reference voltage is defined as the device supply voltage (AVDD/AVSS).

The ADC module uses the following control and status registers:

- ADCON: ADC Control Register

- ADSTAT: ADC Status Register

- ADBASE: ADC Base Register<sup>(1,2)</sup>

- ADPCFG: ADC Port Configuration Register

- ADPCFG2: ADC Port Configuration Register 2

- ADCPC0: ADC Convert Pair Control Register 0

- ADCPC1: ADC Convert Pair Control Register 1

- ADCPC2: ADC Convert Pair Control Register 2

- ADCPC3: ADC Convert Pair Control Register 3

- ADCPC4: ADC Convert Pair Control Register 4

- ADCPC5: ADC Convert Pair Control Register 5

- ADCPC6: ADC Convert Pair Control Register 6(2)

The ADCON register controls the operation of the ADC module. The ADSTAT register displays the status of the conversion processes. The ADPCFG registers configure the port pins as analog inputs or as digital I/O. The ADCPCx registers control the triggering of the ADC conversions. See Register 22-1 through Register 22-12 for detailed bit configurations.

Note: A unique feature of the ADC module is its ability to sample inputs in an asynchronous manner. Individual Sample-and-Hold circuits can be triggered independently of each other.

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| R/W-0         | U-0                              | R/W-0                          | U-0            | U-0                                         | U-0             | U-0               | R/W-0        |

|---------------|----------------------------------|--------------------------------|----------------|---------------------------------------------|-----------------|-------------------|--------------|

| CMPON         | —                                | CMPSIDL                        |                | —                                           | _               | —                 | DACOE        |

| bit 15        |                                  |                                |                |                                             |                 |                   | bit          |

|               | <b>D b b c c c c c c c c c c</b> |                                |                | <b>5</b> 444 a                              |                 |                   | -            |

| R/W-0         | R/W-0                            | R/W-0                          | U-0            | R/W-0                                       | U-0             | R/W-0             | R/W-0        |

| INSEL1        | INSEL0                           | EXTREF                         |                | CMPSTAT                                     | —               | CMPPOL            | RANGE        |

| bit 7         |                                  |                                |                |                                             |                 |                   | bit          |

| Legend:       |                                  |                                |                |                                             |                 |                   |              |

| R = Readable  | e bit                            | W = Writable                   | bit            | U = Unimpler                                | nented bit, re  | ad as '0'         |              |

| -n = Value at | POR                              | '1' = Bit is set               |                | '0' = Bit is cle                            | ared            | x = Bit is unkr   | nown         |

|               |                                  |                                |                |                                             |                 |                   |              |

| bit 15        |                                  | mparator Opera                 | •              | it                                          |                 |                   |              |

|               |                                  | ator module is e               |                | uces power con                              | cumption)       |                   |              |

| bit 14        | -                                | ited: Read as '                | -              | uces power con                              | sumption        |                   |              |

| bit 13        | -                                | omparator Stop                 |                | o hit                                       |                 |                   |              |

| DIL 13        |                                  |                                |                | n device enters                             | Idle mode       |                   |              |

|               |                                  | es module oper                 |                |                                             | iule moue.      |                   |              |

|               |                                  |                                |                |                                             | set to '1' disa | bles ALL compa    | rators while |

| bit 12-9      | Unimplemen                       | ted: Read as '                 | 0'             |                                             |                 |                   |              |

| bit 8         | DACOE: DAG                       | C Output Enabl                 | е              |                                             |                 |                   |              |

|               |                                  |                                |                | DACOUT pin <sup>(1)</sup><br>I to the DACOU | T pin           |                   |              |

| bit 7-6       | INSEL<1:0>:                      | Input Source S                 | Select for Co  | mparator bits                               |                 |                   |              |

|               |                                  | CMPxD input p                  |                |                                             |                 |                   |              |

|               |                                  | CMPxC input p                  |                |                                             |                 |                   |              |

|               |                                  | CMPxB input p<br>CMPxA input p |                |                                             |                 |                   |              |

| bit 5         |                                  | able External R                |                |                                             |                 |                   |              |

|               |                                  |                                |                |                                             | mum DAC v       | oltage determine  | d by extern  |

|               | voltage s                        | -                              |                |                                             |                 | enage acternate   |              |

|               |                                  | reference sour<br>bit setting) | ces provide    | reference to D.                             | AC (maximur     | m DAC voltage o   | determined t |

| bit 4         | Unimplemen                       | ted: Read as '                 | 0'             |                                             |                 |                   |              |

| bit 3         | CMPSTAT: C                       | urrent State of                | Comparator     | Output Including                            | g CMPPOL S      | election bit      |              |

| bit 2         | Unimplemen                       | ted: Read as '                 | 0'             |                                             |                 |                   |              |

| bit 1         | CMPPOL: Co                       | omparator Outp                 | out Polarity C | control bit                                 |                 |                   |              |

|               | 1 = Output is                    |                                |                |                                             |                 |                   |              |

|               | 0 = Output is                    |                                |                |                                             |                 |                   |              |

| bit 0         |                                  | ects DAC Outp                  | -              | -                                           |                 |                   |              |

|               | 0                                | ge: Max DAC \<br>ge: Max DAC \ |                | o/2, 1.65V at 3.3<br>EF                     | V AVdd          |                   |              |

|               | ACOUT can be a at multiple comp  |                                |                |                                             |                 | e. The software i |              |

# REGISTER 23-1: CMPCONX: COMPARATOR CONTROL x REGISTER

© 2009-2014 Microchip Technology Inc.

| Bit Field  | Register | RTSP Effect | Description                                                                                                                                                |

|------------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMPPOL1    | FCMP     | Immediate   | Comparator Hysteresis Polarity bit (for odd numbered comparators)<br>1 = Hysteresis is applied to falling edge<br>0 = Hysteresis is applied to rising edge |

| HYST1<1:0> | FCMP     | Immediate   | Comparator Hysteresis Select bits<br>11 = 45 mV hysteresis<br>10 = 30 mV hysteresis<br>01 = 15 mV hysteresis<br>00 = No hysteresis                         |

| <b>TABLE 24-2:</b> | dsPIC33F CONFIGURATION BITS DESCRIPTION ( | (CONTINUED) |

|--------------------|-------------------------------------------|-------------|

|                    | usi lossi oolii lookanon bito beookii hon |             |

# 24.5 JTAG Interface

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface will be provided in future revisions of the document.

# 24.6 In-Circuit Serial Programming

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 family Digital Signal Controllers (DSCs) can be serially programmed while in the end application circuit. This is done with two lines for clock and data and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the Digital Signal Controller just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33F/PIC24H Flash Programming Specification" (DS70152) for details about In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

# 24.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 is selected as a debugger, the incircuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB X IDE. Debugging functionality is controlled through the EMUCx (Emulation/Debug Clock) and EMUDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGECx, PGEDx and the EMUDx/ EMUCx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

# 26.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 26.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 26.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 26.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 26.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# TABLE 27-22:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

| AC CHA       | RACTER | ISTICS                                                         | (unles | s otherwise                     | <b>stated</b><br>ture - | conditions: 3.0V to 3.6V<br>ted)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                                                                     |  |  |  |

|--------------|--------|----------------------------------------------------------------|--------|---------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>                                  | Min    | Тур <sup>(2)</sup>              | Max                     | Units                                                                                                                                             | Conditions                                                                          |  |  |  |

| SY10         | TMCL   | MCLR Pulse Width (low)                                         | 2      | _                               | _                       | μS                                                                                                                                                | -40°C to +85°C                                                                      |  |  |  |

| SY11         | Tpwrt  | Power-up Timer Period                                          |        | 2<br>4<br>16<br>32<br>64<br>128 |                         | ms                                                                                                                                                | -40°C to +85°C,<br>User programmable                                                |  |  |  |

| SY12         | TPOR   | Power-on Reset Delay                                           | 3      | 10                              | 30                      | μS                                                                                                                                                | -40°C to +85°C                                                                      |  |  |  |

| SY13         | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | 0.68   | 0.72                            | 1.2                     | μS                                                                                                                                                |                                                                                     |  |  |  |

| SY20         | Twdt1  | Watchdog Timer Time-out<br>Period                              | —      | —                               | —                       | ms                                                                                                                                                | See Section 24.4 "Watchdog<br>Timer (WDT)" and LPRC<br>Parameter F21a (Table 27-20) |  |  |  |

| SY30         | Tost   | Oscillator Start-up Time                                       | —      | 1024 Tosc                       | _                       |                                                                                                                                                   | Tosc = OSC1 period                                                                  |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

| AC CHARAG            | CTERISTICS                               |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |     |     |     |  |  |  |  |

|----------------------|------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|--|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                        | СКЕ | СКР | SMP |  |  |  |  |

| 15 MHz               | Table 27-31                              | —                                           | _                                                                                                                                                                                                                                                                                 | 0,1 | 0,1 | 0,1 |  |  |  |  |

| 10 MHz               | _                                        | Table 27-32                                 | —                                                                                                                                                                                                                                                                                 | 1   | 0,1 | 1   |  |  |  |  |

| 10 MHz               | _                                        | Table 27-33                                 | —                                                                                                                                                                                                                                                                                 | 0   | 0,1 | 1   |  |  |  |  |

| 15 MHz               | —                                        | —                                           | Table 27-34                                                                                                                                                                                                                                                                       | 1   | 0   | 0   |  |  |  |  |

| 11 MHz               |                                          | —                                           | Table 27-35                                                                                                                                                                                                                                                                       | 1   | 1   | 0   |  |  |  |  |

| 15 MHz               | _                                        | —                                           | Table 27-36                                                                                                                                                                                                                                                                       | 0   | 1   | 0   |  |  |  |  |

| 11 MHz               | _                                        | —                                           | Table 27-37                                                                                                                                                                                                                                                                       | 0   | 0   | 0   |  |  |  |  |

## TABLE 27-30: SPIX MAXIMUM DATA/CLOCK RATE SUMMARY

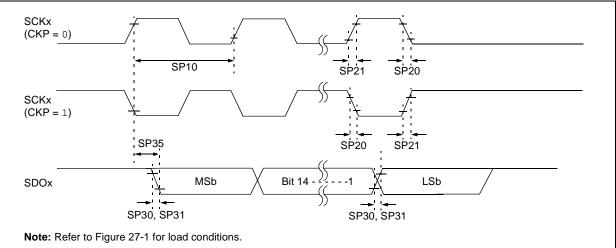

## FIGURE 27-11: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

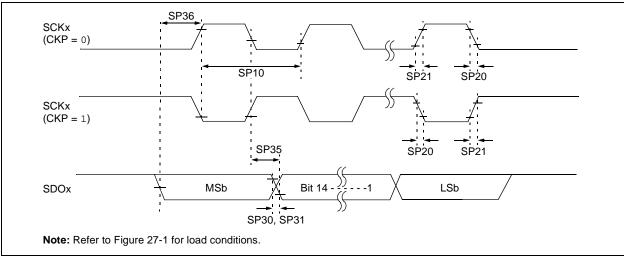

# FIGURE 27-12: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

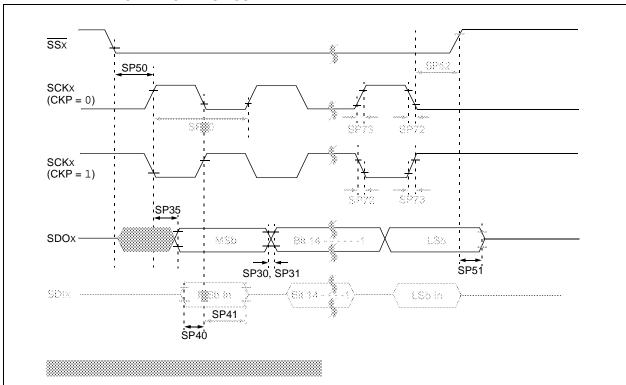

FIGURE 27-18: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

# **30.0 PACKAGING INFORMATION**

# 30.1 Package Marking Information

64-Lead QFN (9x9x0.9mm)

○ S 33FJ32GS 406-I/MR @3 1210017

64-Lead TQFP (10x10x1mm)

80-Lead TQFP (12x12x1mm)

Example

Example

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                 | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (@3)<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |