Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, QEI, POR, PWM, WDT                                 |

| Number of I/O              | 58                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 9K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b; D/A 1x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs606-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-32: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ32GS610 AND dsPIC33FJ64GS610 DEVICES ONLY (CONTINUED)

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|-----------------------|--------|--------|--------|--------|-------|---------|-------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ADCBUF22     | 036C        |        | ADC Data Buffer 22 xx |        |        |        |        |       |         |             | xxxx  |       |       |       |       |       |       |               |

| ADCBUF23     | 036E        |        |                       |        |        |        |        |       | ADC Dat | a Buffer 23 |       |       |       |       |       |       |       | XXXX          |

| ADCBUF24     | 0370        |        | ADC Data Buffer 24    |        |        |        |        |       |         | XXXX        |       |       |       |       |       |       |       |               |

| ADCBUF25     | 0372        |        | ADC Data Buffer 25    |        |        |        |        |       |         |             | xxxx  |       |       |       |       |       |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

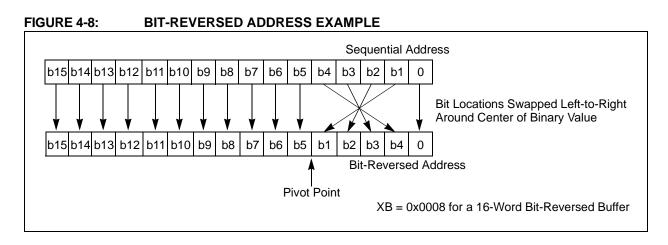

| TABLE | TABLE 4-67: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY) |       |           |         |                      |    |    |    |         |  |  |  |

|-------|------------------------------------------------------|-------|-----------|---------|----------------------|----|----|----|---------|--|--|--|

|       |                                                      | Norma | al Addres | SS      | Bit-Reversed Address |    |    |    |         |  |  |  |

| A3    | A2                                                   | A1    | A0        | Decimal | A3                   | A2 | A1 | A0 | Decimal |  |  |  |

| 0     | 0                                                    | 0     | 0         | 0       | 0                    | 0  | 0  | 0  | 0       |  |  |  |

| 0     | 0                                                    | 0     | 1         | 1       | 1                    | 0  | 0  | 0  | 8       |  |  |  |

| 0     | 0                                                    | 1     | 0         | 2       | 0                    | 1  | 0  | 0  | 4       |  |  |  |

| 0     | 0                                                    | 1     | 1         | 3       | 1                    | 1  | 0  | 0  | 12      |  |  |  |

| 0     | 1                                                    | 0     | 0         | 4       | 0                    | 0  | 1  | 0  | 2       |  |  |  |

| 0     | 1                                                    | 0     | 1         | 5       | 1                    | 0  | 1  | 0  | 10      |  |  |  |

| 0     | 1                                                    | 1     | 0         | 6       | 0                    | 1  | 1  | 0  | 6       |  |  |  |

| 0     | 1                                                    | 1     | 1         | 7       | 1                    | 1  | 1  | 0  | 14      |  |  |  |

| 1     | 0                                                    | 0     | 0         | 8       | 0                    | 0  | 0  | 1  | 1       |  |  |  |

| 1     | 0                                                    | 0     | 1         | 9       | 1                    | 0  | 0  | 1  | 9       |  |  |  |

| 1     | 0                                                    | 1     | 0         | 10      | 0                    | 1  | 0  | 1  | 5       |  |  |  |

| 1     | 0                                                    | 1     | 1         | 11      | 1                    | 1  | 0  | 1  | 13      |  |  |  |

| 1     | 1                                                    | 0     | 0         | 12      | 0                    | 0  | 1  | 1  | 3       |  |  |  |

| 1     | 1                                                    | 0     | 1         | 13      | 1                    | 0  | 1  | 1  | 11      |  |  |  |

| 1     | 1                                                    | 1     | 0         | 14      | 0                    | 1  | 1  | 1  | 7       |  |  |  |

| 1     | 1                                                    | 1     | 1         | 15      | 1                    | 1  | 1  | 1  | 15      |  |  |  |

### TABLE 4-67: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

| U-0           | U-0                                                                                                                                                                                                                         | U-0              | U-0     | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|------------------|------------------|-----------------|---------|--|--|--|

| —             | —                                                                                                                                                                                                                           | —                | —       | —                | QEI1IP2          | QEI1IP1         | QEI1IP0 |  |  |  |

| bit 15        |                                                                                                                                                                                                                             |                  |         |                  |                  |                 | bit 8   |  |  |  |

|               |                                                                                                                                                                                                                             |                  |         |                  |                  |                 |         |  |  |  |

| U-0           | R/W-1                                                                                                                                                                                                                       | R/W-0            | R/W-0   | U-0              | U-0              | U-0             | U-0     |  |  |  |

|               | PSEMIP2                                                                                                                                                                                                                     | PSEMIP1          | PSEMIP0 | —                | —                |                 | _       |  |  |  |

| bit 7         |                                                                                                                                                                                                                             |                  |         |                  |                  |                 | bit 0   |  |  |  |

|               |                                                                                                                                                                                                                             |                  |         |                  |                  |                 |         |  |  |  |

| Legend:       |                                                                                                                                                                                                                             |                  |         |                  |                  |                 |         |  |  |  |

| R = Readabl   |                                                                                                                                                                                                                             | W = Writable     |         | •                | mented bit, read |                 |         |  |  |  |

| -n = Value at | POR                                                                                                                                                                                                                         | '1' = Bit is set |         | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |  |  |  |

| bit 10-8      | 5-11 Unimplemented: Read as '0'<br>QEI1IP<2:0>: QEI1 Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)<br>•<br>•<br>001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |                  |         |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                                                                                                           | ted: Read as '   |         |                  |                  |                 |         |  |  |  |

| bit 6-4       | -4 <b>PSEMIP&lt;2:0&gt;:</b> PWM Special Event Match Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                 |                  |         |                  |                  |                 |         |  |  |  |

| bit 3-0       | Unimplemen                                                                                                                                                                                                                  | ted: Read as '   | 0'      |                  |                  |                 |         |  |  |  |

|               |                                                                                                                                                                                                                             |                  |         |                  |                  |                 |         |  |  |  |

#### REGISTER 7-33: IPC14: INTERRUPT PRIORITY CONTROL REGISTER 14

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| U-0                       | U-0                                                                          | U-0                                                                                  | U-0                                     | U-0              | U-0                        | U-0             | U-0   |

|---------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------|------------------|----------------------------|-----------------|-------|

| _                         | _                                                                            | —                                                                                    | —                                       | _                | —                          | —               | —     |

| bit 15                    |                                                                              |                                                                                      |                                         |                  |                            |                 | bit 8 |

|                           |                                                                              |                                                                                      |                                         |                  |                            |                 |       |

| U-0                       | R/W-1                                                                        | R/W-0                                                                                | R/W-0                                   | U-0              | U-0                        | U-0             | U-0   |

| —                         | ADCP12IP2                                                                    | ADCP12IP1                                                                            | ADCP12IP0                               | —                | —                          | —               | —     |

| bit 7                     |                                                                              |                                                                                      |                                         |                  |                            |                 | bit 0 |

|                           |                                                                              |                                                                                      |                                         |                  |                            |                 |       |

| Legend:                   |                                                                              |                                                                                      |                                         |                  |                            |                 |       |

| R = Readable              | e bit                                                                        | W = Writable                                                                         | bit                                     | U = Unimpler     | nented bit, read           | as '0'          |       |

| -n = Value at POR         |                                                                              |                                                                                      |                                         |                  |                            |                 |       |

| -n = Value at             | POR                                                                          | '1' = Bit is set                                                                     |                                         | '0' = Bit is cle | ared                       | x = Bit is unkr | nown  |

| -n = Value at             | POR                                                                          | '1' = Bit is set                                                                     |                                         | '0' = Bit is cle | ared                       | x = Bit is unkr | nown  |

| -n = Value at<br>bit 15-7 |                                                                              | '1' = Bit is set                                                                     |                                         | '0' = Bit is cle | ared                       | x = Bit is unkr | nown  |

|                           | Unimplemen                                                                   | ted: Read as '                                                                       | 0'                                      |                  | ared<br>pt 1 Priority bits |                 | nown  |

| bit 15-7                  | Unimplemen<br>ADCP12IP<2                                                     | ted: Read as '                                                                       | <sup>0'</sup><br>12 Conversior          | n Done Interru   |                            |                 | nown  |

| bit 15-7                  | Unimplemen<br>ADCP12IP<2                                                     | ted: Read as '<br>:0>: ADC Pair                                                      | <sup>0'</sup><br>12 Conversior          | n Done Interru   |                            |                 | nown  |

| bit 15-7                  | Unimplemen<br>ADCP12IP<2                                                     | ted: Read as '<br>:0>: ADC Pair                                                      | <sup>0'</sup><br>12 Conversior          | n Done Interru   |                            |                 | nown  |

| bit 15-7                  | Unimplement<br>ADCP12IP<2<br>111 = Interrup<br>•<br>•                        | ted: Read as '<br>: <b>0&gt;:</b> ADC Pair<br>ot is Priority 7 (                     | <sup>0'</sup><br>12 Conversior          | n Done Interru   |                            |                 | nown  |

| bit 15-7                  | Unimplement<br>ADCP12IP<2<br>111 = Interrup<br>•<br>•<br>•<br>001 = Interrup | ted: Read as '<br>: <b>0&gt;:</b> ADC Pair<br>ot is Priority 7 (<br>ot is Priority 1 | 0'<br>12 Conversior<br>highest priority | n Done Interru   |                            |                 | nown  |

| bit 15-7                  | Unimplement<br>ADCP12IP<2<br>111 = Interrup<br>•<br>•<br>•<br>001 = Interrup | ted: Read as '<br>: <b>0&gt;:</b> ADC Pair<br>ot is Priority 7 (                     | 0'<br>12 Conversior<br>highest priority | n Done Interru   |                            |                 | nown  |

#### REGISTER 7-38: IPC21: INTERRUPT PRIORITY CONTROL REGISTER 21

#### 7.4 Interrupt Setup Procedures

#### 7.4.1 INITIALIZATION

Complete the following steps to configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |        |      |      |         |           |  |  |

|-------|-------------------------------------------|--------|------|------|---------|-----------|--|--|

|       | initialized                               | such   | that | all  | user    | interrupt |  |  |

|       | sources ar                                | e assi | gned | to P | riority | Level 4.  |  |  |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 7.4.2 INTERRUPT SERVICE ROUTINE

The method used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (C or assembler) and the language development toolsuite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, program will re-enter the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

### 7.4.4 INTERRUPT DISABLE

The following steps outline the procedure to disable all user interrupts:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, EOh, with SRL.

To enable user interrupts, the POP instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of |

|-------|-----------------------------------------------|

|       | 7 or lower can be disabled. Trap sources      |

|       | (Level 8-Level 15) cannot be disabled.        |

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

# REGISTER 8-5: DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|----------------------|-----------------|-----------------|-------|

|                 |       |                  | PAD<  | 15:8> <b>(2)</b>     |                 |                 |       |

| bit 15          |       |                  |       |                      |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  |       | <7:0> <sup>(2)</sup> |                 |                 |       |

| bit 7           |       |                  |       |                      |                 |                 | bit 0 |

| Legend:         |       |                  |       |                      |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimpler         | nented bit, rea | ıd as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle     | ared            | x = Bit is unkr | nown  |

bit 15-0 PAD<15:0>: Peripheral Address Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** See Table 8-1 for a complete list of peripheral addresses.

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

# REGISTER 8-9: DSADR: MOST RECENT DMA RAM ADDRESS REGISTER

| R-0             | R-0 | R-0              | R-0  | R-0                 | R-0          | R-0             | R-0   |

|-----------------|-----|------------------|------|---------------------|--------------|-----------------|-------|

|                 |     |                  | DSAD | R<15:8>             |              |                 |       |

| bit 15          |     |                  |      |                     |              |                 | bit 8 |

|                 |     |                  |      |                     |              |                 |       |

| R-0             | R-0 | R-0              | R-0  | R-0                 | R-0          | R-0             | R-0   |

|                 |     |                  | DSAD | DR<7:0>             |              |                 |       |

| bit 7           |     |                  |      |                     |              |                 | bit 0 |

|                 |     |                  |      |                     |              |                 |       |

| Legend:         |     |                  |      |                     |              |                 |       |

| R = Readable I  | bit | W = Writable bi  | t    | U = Unimplemen      | ted bit, rea | ad as '0'       |       |

| -n = Value at P | OR  | '1' = Bit is set |      | '0' = Bit is cleare | d            | x = Bit is unkr | nown  |

bit 15-0 DSADR<15:0>: Most Recent DMA RAM Address Accessed by DMA Controller bits

| R/W-0         | R/W-0        | R/W-0                               | R/W-0   | R/W-0             | R/W-0           | R/W-0                | U-0   |

|---------------|--------------|-------------------------------------|---------|-------------------|-----------------|----------------------|-------|

| T5MD          | T4MD         | T3MD                                | T2MD    | T1MD              | QEI1MD          | PWMMD <sup>(1)</sup> | _     |

| bit 15        |              |                                     |         |                   |                 |                      | bit   |

|               |              |                                     |         |                   |                 |                      |       |

| R/W-0         | R/W-0        | R/W-0                               | R/W-0   | R/W-0             | U-0             | R/W-0                | R/W-0 |

| I2C1MD        | U2MD         | U1MD                                | SPI2MD  | SPI1MD            | —               | C1MD                 | ADCMD |

| bit 7         |              |                                     |         |                   |                 |                      | bit   |

| Legend:       |              |                                     |         |                   |                 |                      |       |

| R = Readabl   | le bit       | W = Writable                        | bit     | U = Unimplem      | nented bit, rea | d as '0'             |       |

| -n = Value at | t POR        | '1' = Bit is set                    |         | '0' = Bit is clea | ared            | x = Bit is unkno     | own   |

|               |              |                                     |         |                   |                 |                      |       |

| bit 15        | T5MD: Timer  | 5 Module Disal                      | ole bit |                   |                 |                      |       |

|               |              | odule is disable                    |         |                   |                 |                      |       |

|               |              | odule is enable                     |         |                   |                 |                      |       |

| bit 14        |              | 4 Module Disal                      |         |                   |                 |                      |       |

|               |              | odule is disable<br>odule is enable |         |                   |                 |                      |       |

| bit 13        |              | 3 Module Disat                      |         |                   |                 |                      |       |

|               |              | odule is disable                    |         |                   |                 |                      |       |

|               | 0 = Timer3 m | odule is enable                     | ed      |                   |                 |                      |       |

| bit 12        | T2MD: Timer  | 2 Module Disat                      | ole bit |                   |                 |                      |       |

|               |              | odule is disable<br>odule is enable |         |                   |                 |                      |       |

| bit 11        | T1MD: Timer  | 1 Module Disat                      | ole bit |                   |                 |                      |       |

|               |              | odule is disable<br>odule is enable |         |                   |                 |                      |       |

| bit 10        | QEI1MD: QE   | I1 Module Disa                      | ble bit |                   |                 |                      |       |

|               |              | dule is disabled                    |         |                   |                 |                      |       |

|               |              | dule is enabled                     | (1)     |                   |                 |                      |       |

| bit 9         |              | /M Module Disa                      |         |                   |                 |                      |       |

|               |              | dule is disabled<br>dule is enabled |         |                   |                 |                      |       |

| bit 8         | Unimplemen   | ted: Read as '                      | 0'      |                   |                 |                      |       |

| bit 7         | 12C1MD: 12C  | 1 Module Disat                      | ole bit |                   |                 |                      |       |

|               |              | lule is disabled<br>lule is enabled |         |                   |                 |                      |       |

| bit 6         | U2MD: UART   | 2 Module Disa                       | ble bit |                   |                 |                      |       |

|               | -            | odule is disabl<br>odule is enable  |         |                   |                 |                      |       |

| bit 5         | U1MD: UART   | 1 Module Disa                       | ble bit |                   |                 |                      |       |

|               |              | odule is disabl<br>odule is enable  |         |                   |                 |                      |       |

| bit 4         |              | 2 Module Disa                       |         |                   |                 |                      |       |

| -             | 1 = SPI2 mod | lule is disabled                    |         |                   |                 |                      |       |

# REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** Once the PWM module is re-enabled (PWMMD is set to '1' and then set to '0'), all PWM registers must be re-initialized.

# 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

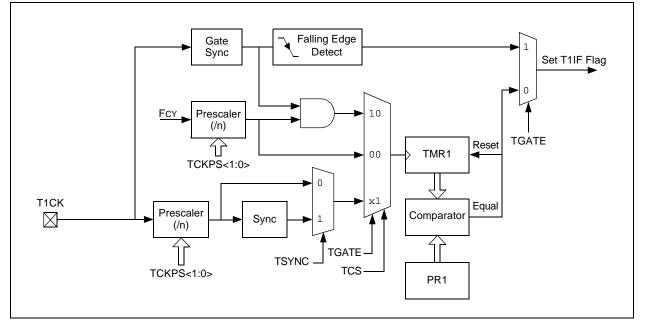

The Timer1 module is a 16-bit timer, which can serve as a time counter for the Real-Time Clock (RTC), or operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated from the low-power 32.767 kHz crystal oscillator available on the device.

- Can be operated in Asynchronous Counter mode from an external clock source.

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler.

The unique features of Timer1 allow it to be used for Real-Time Clock (RTC) applications. A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit: TCS (T1CON<1>)

- Timer Synchronization Control bit: TSYNC (T1CON<2>)

- Timer Gate Control bit: TGATE (T1CON<6>)

The timer control bit settings for different operating modes are given in the Table 12-1.

#### TABLE 12-1: TIMER MODE SETTINGS

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

NOTES:

# REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| DAAL                              | DAAL        | DAA                                                    | D AA/         | D ///                                    | D ///            | D ///    | D /// |

|-----------------------------------|-------------|--------------------------------------------------------|---------------|------------------------------------------|------------------|----------|-------|

| R/W-x                             | R/W-x       | R/W-x                                                  | R/W-x         | R/W-x                                    | R/W-x            | R/W-x    | R/W-x |

| SID10                             | SID9        | SID8                                                   | SID7          | SID6                                     | SID5             | SID4     | SID3  |

| bit 15                            |             |                                                        |               |                                          |                  |          | bit 8 |

|                                   |             |                                                        |               |                                          |                  |          |       |

| R/W-x                             | R/W-x       | R/W-x                                                  | U-0           | R/W-x                                    | U-0              | R/W-x    | R/W-x |

| SID2                              | SID1        | SID0                                                   | —             | EXIDE                                    | —                | EID17    | EID16 |

| bit 7                             |             |                                                        |               |                                          |                  |          | bit 0 |

|                                   |             |                                                        |               |                                          |                  |          |       |

| Legend:                           |             |                                                        |               |                                          |                  |          |       |

| R = Readable bit W = Writable bit |             |                                                        |               | U = Unimplen                             | nented bit, read | d as '0' |       |

| -n = Value at                     | POR         | '1' = Bit is set                                       |               | 0' = Bit is cleared $x = Bit is unknown$ |                  |          | nown  |

| bit 4                             | 0 = Message | address bit, SI<br>address bit, SI<br>ited: Read as '( | Dx, must be ' |                                          |                  |          |       |

| bit 3                             | •           | nded Identifier E                                      |               |                                          |                  |          |       |

| -                                 |             | only messages<br>only messages<br>:hen:                |               |                                          |                  |          |       |

| bit 2                             | Unimplemen  | ted: Read as '                                         | )'            |                                          |                  |          |       |

| bit 1-0                           | EID<17:16>: | Extended Ident                                         | ifier bits    |                                          |                  |          |       |

|                                   | •           | address bit, El<br>address bit, El                     |               |                                          |                  |          |       |

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

# BUFFER 21-5: ECANx MESSAGE BUFFER WORD 4

| R/W-x                              | R/W-x | R/W-x          | R/W-x            | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|------------------------------------|-------|----------------|------------------|--------------|------------------|----------|-------|

| _                                  |       |                | Ву               | te 3         |                  |          |       |

| bit 15                             |       |                |                  |              |                  |          | bit 8 |

| R/W-x                              | R/W-x | R/W-x          | R/W-x            | R/W-x        | R/W-x            | R/W-x    | R/W-x |

| _                                  |       |                | Ву               | te 2         |                  |          |       |

| bit 7                              |       |                |                  |              |                  |          | bit 0 |

| Legend:                            |       |                |                  |              |                  |          |       |

| R = Readable                       | bit   | W = Writable b | bit              | U = Unimpler | mented bit, read | d as '0' |       |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is cle | ared         | x = Bit is unkr  | nown     |       |

| bit 15-8 | Byte 3<15:8>: ECANx Message Byte 3 |

|----------|------------------------------------|

| bit 7-0  | Byte 2<7:0>: ECANx Message Byte 2  |

#### BUFFER 21-6: ECANx MESSAGE BUFFER WORD 5

| R/W-x                              | R/W-x | R/W-x            | R/W-x | R/W-x                | R/W-x           | R/W-x              | R/W-x |

|------------------------------------|-------|------------------|-------|----------------------|-----------------|--------------------|-------|

|                                    |       |                  | B     | /te 5                |                 |                    |       |

| bit 15                             |       |                  |       |                      |                 |                    | bit 8 |

| R/W-x                              | R/W-x | R/W-x            | R/W-x | R/W-x                | R/W-x           | R/W-x              | R/W-x |

|                                    |       |                  | B     | /te 4                |                 |                    |       |

| bit 7                              |       |                  |       |                      |                 |                    | bit 0 |

| Legend:                            |       |                  |       |                      |                 |                    |       |

| R = Readable bit                   |       | W = Writable b   | oit   | U = Unimplen         | nented bit, rea | id as '0'          |       |

| -n = Value at POR '1' = Bit is set |       | '1' = Bit is set |       | '0' = Bit is cleared |                 | x = Bit is unknown |       |

bit 15-8

Byte 5<15:8>: ECANx Message Byte 5

bit 7-0

Byte 4<7:0>: ECANx Message Byte 4

© 2009-2014 Microchip Technology Inc.

| R/W-0                                                                                                                                              | R/W-0                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PEND5                                                                                                                                              | SWTRG5                                                                                                                                                                    | TRGSRC54                                                                                                                                                                                                                                                                                                                                                                                                               | TRGSRC53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TRGSRC52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TRGSRC51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TRGSRC50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                    |                                                                                                                                                                           | •                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                    |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| R/W-0                                                                                                                                              | R/W-0                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PEND4                                                                                                                                              | SWTRG4                                                                                                                                                                    | TRGSRC44                                                                                                                                                                                                                                                                                                                                                                                                               | TRGSRC43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TRGSRC42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TRGSRC41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TRGSRC40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                    |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                    |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |