Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Detuns                     |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 50 MIPs                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, QEI, POR, PWM, WDT                                    |

| Number of I/O              | 74                                                                                 |

| Program Memory Size        | 64KB (64K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                |                                                                                    |

| RAM Size                   | 9K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 18x10b; D/A 1x10b                                                              |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 80-TQFP                                                                            |

| Supplier Device Package    | 80-TQFP (12x12)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs608t-50i-pt |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

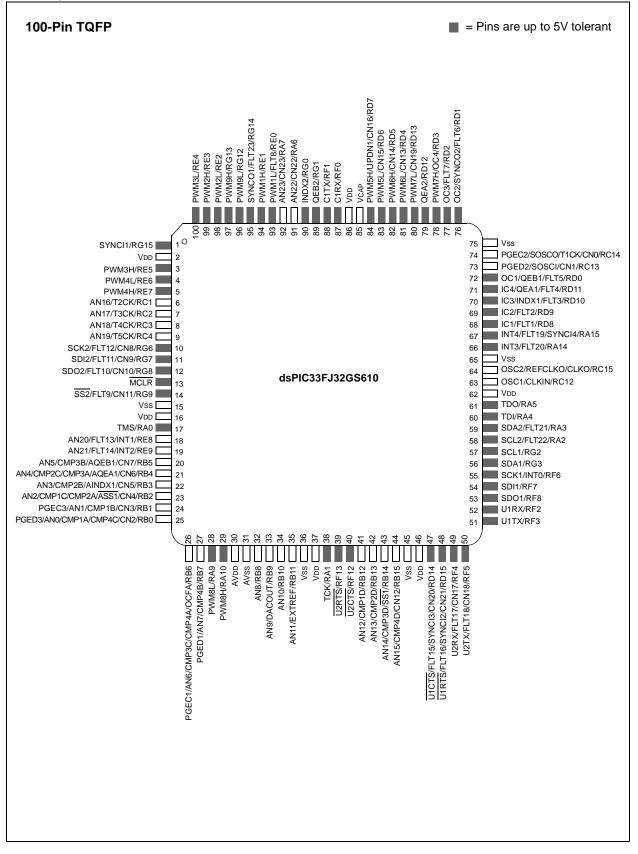

## Pin Diagrams (Continued)

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Pin Name             | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                        |

|----------------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN23             | I           | Analog         | Analog input channels.                                                                                                                                                                                                                                             |

| CLKI<br>CLKO         | I<br>O      | ST/CMOS<br>—   | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.<br>Always associated with OSC2 pin function. |

| OSC1                 | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                                                                                    |

| OSC2                 | I/O         | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                        |

| SOSCI                |             | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                                                                                     |

| SOSCO                | 0           |                | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                                                                                    |

| CN0-CN23             | Ι           | ST             | Change Notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                   |

| C1RX                 | I           | ST             | ECAN1 bus receive pin.                                                                                                                                                                                                                                             |

| C1TX                 | 0           | —              | ECAN1 bus transmit pin.                                                                                                                                                                                                                                            |

| IC1-IC4              | Ι           | ST             | Capture Inputs 1 through 4.                                                                                                                                                                                                                                        |

| INDX1, INDX2, AINDX1 | I           | ST             | Quadrature Encoder Index Pulse input.                                                                                                                                                                                                                              |

| QEA1, QEA2, AQEA1    | I           | ST             | Quadrature Encoder Phase A input in QEI mode.                                                                                                                                                                                                                      |

| QEB1, QEB2, AQEB1    | I           | ST             | Auxiliary Timer External Clock/Gate input in Timer mode.<br>Quadrature Encoder Phase A input in QEI mode.<br>Auxiliary Timer External Clock/Gate input in Timer mode.                                                                                              |

| UPDN1                | 0           | CMOS           | Position Up/Down Counter Direction State.                                                                                                                                                                                                                          |

| OCFA                 | I           | ST             | Compare Fault A input.                                                                                                                                                                                                                                             |

| OC1-OC4              | 0           | —              | Compare Outputs 1 through 4.                                                                                                                                                                                                                                       |

| INT0                 | I           | ST             | External Interrupt 0.                                                                                                                                                                                                                                              |

| INT1                 | I           | ST             | External Interrupt 1.                                                                                                                                                                                                                                              |

| INT2                 | I           | ST             | External Interrupt 2.                                                                                                                                                                                                                                              |

| INT3                 | I           | ST             | External Interrupt 3.                                                                                                                                                                                                                                              |

| INT4                 | 1           | ST             | External Interrupt 4.                                                                                                                                                                                                                                              |

| RA0-RA15             | I/O         | ST             | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| RB0-RB15<br>RC0-RC15 | I/O<br>I/O  | ST<br>ST       | PORTB is a bidirectional I/O port.<br>PORTC is a bidirectional I/O port.                                                                                                                                                                                           |

| RD0-RD15             | 1/0         | ST             | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| RE0-RE9              | I/O         | ST             | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| RF0-RF13             | I/O         | ST             | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| RG0-RG15             | I/O         | ST             | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| T1CK                 | 1/0         | ST             | Timer1 external clock input.                                                                                                                                                                                                                                       |

| T2CK                 | i i         | ST             | Timer2 external clock input.                                                                                                                                                                                                                                       |

| T3CK                 | ·           | ST             | Timer3 external clock input.                                                                                                                                                                                                                                       |

| T4CK                 | I           | ST             | Timer4 external clock input.                                                                                                                                                                                                                                       |

| T5CK                 | I           | ST             | Timer5 external clock input.                                                                                                                                                                                                                                       |

| Legend: CMOS = CMC   | )S.comp     | atible input   | or output Analog = Analog input I = Input                                                                                                                                                                                                                          |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-Transistor Logic

P = Power

0 = Output

## TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ32GS608/610 AND dsPIC33FJ64GS608/610 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3         | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------|---------|---------|---------------|---------|---------|---------|---------------|

| CNEN1        | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE         | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2        | 0062        | _       | _       | _       | _       | _       | _       | _      | _      | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE        | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1        | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | <b>CN3PUE</b> | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2        | 006A        | —       | _       | _       | _       | _       | _       | -      |        | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE       | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ32GS406/606 AND dsPIC33FJ64GS406/606 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------|--------|--------|--------|---------|---------|---------|---------------|

| CNEN1        | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE   | CN6IE   | CN5IE  | CN4IE  | CN3IE  | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2        | 0062        | _       | -       | _       | -       | -       |         |        | _      | CN23IE  | CN22IE  | _      |        | -      | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1        | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE  | CN6PUE  | CN5PUE | CN4PUE | CN3PUE | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2        | 006A        | —       | _       | _       | _       | _       | _       | _      | _      | CN23PUE | CN22PUE | _      | _      | _      | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|              | 4-9:        |         | TERRUI  | 1 0011   |         |         |          |          |          | 00.0010  |          |          |          |         |          |          |          | <u> </u>      |

|--------------|-------------|---------|---------|----------|---------|---------|----------|----------|----------|----------|----------|----------|----------|---------|----------|----------|----------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13   | Bit 12  | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| INTCON1      | 0080        | NSTDIS  | OVAERR  | OVBERR   | COVAERR | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  |          | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | —        | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI    | _        | _       | _       | _        | _        | _        | _        | _        | _        | INT4EP   | INT3EP  | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0         | 0084        | _       | _       | ADIF     | U1TXIF  | U1RXIF  | SPI1IF   | SPI1EIF  | T3IF     | T2IF     | OC2IF    | IC2IF    | —        | T1IF    | OC1IF    | IC1IF    | INTOIF   | 0000          |

| IFS1         | 0086        | U2TXIF  | U2RXIF  | INT2IF   | T5IF    | T4IF    | OC4IF    | OC3IF    | _        | _        | _        | _        | INT1IF   | CNIF    | AC1IF    | MI2C1IF  | SI2C1IF  | 0000          |

| IFS2         | 8800        | _       | _       | _        | _       | _       | _        | _        | _        | —        | IC4IF    | IC3IF    | _        | _       | _        | SPI2IF   | SPI2EIF  | 0000          |

| IFS3         | 008A        | _       | _       | _        | _       | _       | QEI1IF   | PSEMIF   | _        | —        | INT4IF   | INT3IF   | _        | _       | MI2C2IF  | SI2C2IF  | _        | 0000          |

| IFS4         | 008C        | _       | _       | _        | _       | QEI2IF  | _        | PSESMIF  | _        | —        | _        | _        | _        | _       | U2EIF    | U1EIF    | _        | 0000          |

| IFS5         | 008E        | PWM2IF  | PWM1IF  | ADCP12IF | _       | _       | _        | _        | _        | —        | _        | _        | _        | _       | _        | ADCP8IF  | _        | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF | _        | -       | _       |          | AC4IF    | AC3IF    | AC2IF    |          | PWM8IF   | PWM7IF   | PWM6IF  | PWM5IF   | PWM4IF   | PWM3IF   | 0000          |

| IFS7         | 0092        | _       | _       | _        | _       | _       | _        |          | _        | _        | _        | ADCP7IF  | ADCP6IF  | ADCP5IF | ADCP4IF  | ADCP3IF  | ADCP2IF  | 0000          |

| IEC0         | 0094        |         | _       | ADIE     | U1TXIE  | U1RXIE  | SPI1IE   | SPI1EIE  | T3IE     | T2IE     | OC2IE    | IC2IE    | _        | T1IE    | OC1IE    | IC1IE    | INTOIE   | 0000          |

| IEC1         | 0096        | U2TXIE  | U2RXIE  | INT2IE   | T5IE    | T4IE    | OC4IE    | OC3IE    | _        | _        | -        | _        | INT1IE   | CNIE    | _        | MI2C1IE  | SI2C1IE  | 0000          |

| IEC2         | 0098        | -       | _       | _        | _       | _       |          |          | _        | _        | IC4IE    | IC3IE    | _        |         | _        | SPI2IE   | SPI2EIE  | 0000          |

| IEC3         | 009A        |         | _       | _        | -       | _       | QEI1IE   | PSEMIE   | _        | _        | INT4IE   | INT3IE   | _        |         | MI2C2IE  | SI2C2IE  | _        | 0000          |

| IEC4         | 009C        |         | _       | _        | -       | QEI2IE  |          | PSESMIE  | _        | _        | -        | _        | _        |         | U2EIE    | U1EIE    | _        | 0000          |

| IEC5         | 009E        | PWM2IE  | PWM1IE  | ADCP12IE | -       | _       |          |          | _        | _        |          | _        | _        |         | _        | ADCP8IE  | _        | 0000          |

| IEC6         | 00A0        | ADCP1IE | ADCP0IE | _        | -       | _       |          | AC4IE    | AC3IE    | AC2IE    |          | PWM8IE   | PWM7IE   | PWM6IE  | PWM5IE   | PWM4IE   | PWM3IE   | 0000          |

| IEC7         | 00A2        | _       | _       | _        | _       | _       | _        | _        | _        | _        | _        | ADCP7IE  | ADCP6IE  | ADCP5IE | ADCP4IE  | ADCP3IE  | ADCP2IE  | 0000          |

| IPC0         | 00A4        |         | T1IP2   | T1IP1    | T1IP0   | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2   | IC1IP1   | IC1IP0   |         | INT0IP2  | INT0IP1  | INT0IP0  | 4444          |

| IPC1         | 00A6        |         | T2IP2   | T2IP1    | T2IP0   | _       | OC2IP2   | OC2IP1   | OC2IP0   | _        | IC2IP2   | IC2IP1   | IC2IP0   |         | _        | _        | _        | 4440          |

| IPC2         | 00A8        |         | U1RXIP2 | U1RXIP1  | U1RXIP0 | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 |         | T3IP2    | T3IP1    | T3IP0    | 4444          |

| IPC3         | 00AA        |         | _       | _        | _       | _       |          |          | _        | _        | ADIP2    | ADIP1    | ADIP0    |         | U1TXIP2  | U1TXIP1  | U1TXIP0  | 0044          |

| IPC4         | 00AC        |         | CNIP2   | CNIP1    | CNIP0   | _       | AC1IP2   | AC1IP1   | AC1IP0   | _        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 |         | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 | 4444          |

| IPC5         | 00AE        |         | _       | _        | _       | _       |          |          | _        | _        | -        | _        | _        |         | INT1IP2  | INT1IP1  | INT1IP0  | 0004          |

| IPC6         | 00B0        |         | T4IP2   | T4IP1    | T4IP0   | _       | OC4IP2   | OC4IP1   | OC4IP0   | _        | OC3IP2   | OC3IP1   | OC3IP0   |         | _        | _        | _        | 4440          |

| IPC7         | 00B2        | _       | U2TXIP2 | U2TXIP1  | U2TXIP0 | _       | U2RXIP2  | U2RXIP1  | U2RXIP0  | _        | INT2IP2  | INT2IP1  | INT2IP0  | _       | T5IP2    | T5IP1    | T5IP0    | 4444          |

| IPC8         | 00B4        |         | _       | _        | _       | _       |          |          | _        | _        | SPI2IP2  | SPI2IP1  | SPI2IP0  |         | SPI2EIP2 | SPI2EIP1 | SPI2EIP0 | 0044          |

| IPC9         | 00B6        |         | -       | _        | -       | _       | IC4IP2   | IC4IP1   | IC4IP0   | _        | IC3IP2   | IC3IP1   | IC3IP0   |         | _        | _        | _        | 0440          |

| IPC12        | 00BC        | _       | _       | _        | _       | _       | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 | _        | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 | _       | _        | _        | _        | 0440          |

| IPC13        | 00BE        | _       | _       | _        | _       | _       | INT4IP2  | INT4IP1  | INT4IP0  | —        | INT3IP2  | INT3IP1  | INT3IP0  | _       | —        | _        | —        | 0440          |

| IPC14        | 00C0        | _       | _       | _        | _       | _       | QEI1IP2  | QEI1IP1  | QEI1IP0  | _        | PSEMIP2  | PSEMIP1  | PSEMIP0  | _       | _        | _        | _        | 0440          |

| IPC16        | 00C4        | _       | _       | _        | _       | _       | U2EIP2   | U2EIP1   | U2EIP0   | _        | U1EIP2   | U1EIP1   | U1EIP0   | _       | _        | _        | _        | 0440          |

| IPC18        | 00C8        | _       | QEI2IP2 | QEI2IP1  | QEI2IP0 | _       | —        | —        | —        | _        | PSESMIP2 | PSESMIP1 | PSESMIP0 | _       | _        | _        | _        | 4040          |

| IPC20        | 00CC        |         |         |          |         |         |          | _        |          | _        | ADCP8IP2 | ADCP8IP1 | ADCP8IP0 | _       | _        | _        | _        | 0040          |

dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

## TABLE 4-9: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ32GS608

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-63: PMD REGISTER MAP FOR dsPIC33FJ64GS606 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|--------|--------|--------|-------|--------|-------|---------------|

| PMD1         | 0770        | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | -      | I2C1MD | U2MD  | U1MD   | SPI2MD | SPI1MD | —     | C1MD   | ADCMD | 0000          |

| PMD2         | 0772        | -      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _      |        | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3         | 0774        | _      | _      | _      | _      | -      | CMPMD  | _      | _      | _      | —     | QEI2MD | _      | _      | —     | I2C2MD | —     | 0000          |

| PMD4         | 0776        | -      |        | —      | -      |        | _      |        |        | _      | —     | _      | _      | REFOMD | _     |        | —     | 0000          |

| PMD6         | 077A        | -      |        | PWM6MD | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD | _      | —     | _      | _      | —      | _     |        | —     | 0000          |

| PMD7         | 077C        | _      | _      | _      | -      | CMP4MD | CMP3MD | CMP2MD | CMP1MD | _      | _     | _      | _      | _      | _     | _      | _     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-64: PMD REGISTER MAP FOR dsPIC33FJ32GS606 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|--------|--------|--------|-------|--------|-------|---------------|

| PMD1         | 0770        | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  |        | I2C1MD | U2MD  | U1MD   | SPI2MD | SPI1MD |       | _      | ADCMD | 0000          |

| PMD2         | 0772        | -      | -      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _      | _      | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3         | 0774        | -      | -      | _      | _      | _      | CMPMD  | _      | _      | _      | _     | QEI2MD | _      | _      | _     | I2C2MD | _     | 0000          |

| PMD4         | 0776        | -      | -      | _      | _      | _      | _      | _      | _      | _      | _     | _      | _      | REFOMD | _     | _      | _     | 0000          |

| PMD6         | 077A        | -      | -      | PWM6MD | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD | _      | _     | _      | _      | _      | _     | _      | _     | 0000          |

| PMD7         | 077C        | _      | _      |        | —      | CMP4MD | CMP3MD | CMP2MD | CMP1MD | _      | —     | —      | _      | _      | _     | _      |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-65: PMD REGISTER MAP FOR dsPIC33FJ32GS406 AND dsPIC33FJ64GS406 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|--------|--------|--------|-------|--------|-------|---------------|

| PMD1         | 0770        | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD   | SPI2MD | SPI1MD | _     | _      | ADCMD | 0000          |

| PMD2         | 0772        | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | —      | _     | —      | -      | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3         | 0774        | _      | _      | _      | _      | _      | _      | -      | _      | —      | _     | QEI2MD | -      | _      | _     | I2C2MD | _     | 0000          |

| PMD4         | 0776        | _      | _      | _      | _      | _      | _      | -      | _      | —      | _     | —      | -      | REFOMD | _     | _      | _     | 0000          |

| PMD6         | 077A        | _      |        | PWM6MD | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD | —      | _     | _      | _      |        | _     |        | _     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 4.4 Modulo Addressing

Modulo Addressing mode is a method used to provide an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

## 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Υ   | Space       | Modulo      | Addressing   | EA   |

|-------|-----|-------------|-------------|--------------|------|

|       | cal | culations   | assume      | word-sized   | data |

|       | (LS | Sb of every | / EA is alw | /ays clear). |      |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

## 4.4.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that will operate with Modulo Addressing:

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

#### MOV #0x1100, W0 Byte W0, XMODSRT MOV ;set modulo start address Address MOV #0x1163. W0 MOV W0, MODEND ;set modulo end address 0x1100 MOV #0x8001, W0 MOV W0, MODCON ;enable W1, X AGU for modulo MOV #0x0000, W0 ;W0 holds buffer fill value MOV #0x1110, W1 ;point W1 to buffer 0x1163 DO AGAIN, #0x31 ;fill the 50 buffer locations MOV WO, [W1++] ;fill the next location AGAIN: INC W0, W0 ; increment the fill value Start Addr = 0x1100End Addr = 0x1163Length = 0x0032 Words

### FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

## dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| 11.0          |                                                              |                                      |                 |                  |                  |                 |         |

|---------------|--------------------------------------------------------------|--------------------------------------|-----------------|------------------|------------------|-----------------|---------|

| U-0           | U-0                                                          | U-0                                  | U-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |

| _             | —                                                            | _                                    | —               | —                | INT4IP2          | INT4IP1         | INT4IP0 |

| bit 15        |                                                              |                                      |                 |                  |                  |                 | bit 8   |

|               |                                                              |                                      |                 |                  |                  |                 |         |

| U-0           | R/W-1                                                        | R/W-0                                | R/W-0           | U-0              | U-0              | U-0             | U-0     |

| —             | INT3IP2                                                      | INT3IP1                              | INT3IP0         | —                | _                | —               | —       |

| bit 7         |                                                              |                                      |                 |                  |                  |                 | bit (   |

|               |                                                              |                                      |                 |                  |                  |                 |         |

| Legend:       |                                                              |                                      |                 |                  |                  |                 |         |

| R = Readable  | e bit                                                        | W = Writable                         | bit             | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value at | POR                                                          | '1' = Bit is set                     |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 10-8      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup | ot source is dis                     | highest priorit |                  |                  |                 |         |

| bit 7         | =                                                            | ted: Read as '                       |                 |                  |                  |                 |         |

| bit 6-4       | 111 = Interru<br>•<br>•                                      | External Internot is Priority 7 (    |                 |                  |                  |                 |         |

|               | 001 = Interru<br>000 = Interru                               | ot is Priority 1<br>ot source is dis | abled           |                  |                  |                 |         |

## REGISTER 7-32: IPC13: INTERRUPT PRIORITY CONTROL REGISTER 13

## REGISTER 16-12: PDCx: PWM GENERATOR DUTY CYCLE x REGISTER<sup>(1,2,3)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | PDC   | x<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PDC   | x<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| •               | h:+   | W/ Writchlah     | :4    |                  | nantad hit raa  | d aa '0'        |       |

| R = Readable    |       | W = Writable b   | It    | •                | nented bit, rea |                 |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

### bit 15-0 PDCx<15:0>: PWM Generator # Duty Cycle Value bits

- **Note 1:** In Independent PWM mode, the PDCx register controls the PWMxH duty cycle only. In the Complementary, Redundant and Push-Pull PWM modes, the PDCx register controls the duty cycle of both the PWMxH and PWMxL.

- **2:** The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period 0x0009.

- **3:** As the duty cycle gets closer to 0% or 100% of the PWM period (0 to 40 ns, depending on the mode of operation), PWM duty cycle resolution will increase from 1 to 3 LSBs.

## REGISTER 16-13: SDCx: PWM SECONDARY DUTY CYCLE x REGISTER<sup>(1,2,3)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | SDC   | x<15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  |       | 5x<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimplem      | nented bit, rea | ıd as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 **SDCx<15:0>:** Secondary Duty Cycle bits for PWMxL Output Pin

- **Note 1:** The SDCx register is used in Independent PWM mode only. When used in Independent PWM mode, the SDCx register controls the PWMxL duty cycle.

- **2:** The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period 0x0009.

- **3:** As the duty cycle gets closer to 0% or 100% of the PWM period (0 to 40 ns, depending on the mode of operation), PWM duty cycle resolution will increase from 1 to 3 LSBs.

## REGISTER 16-23: LEBCONX: LEADING-EDGE BLANKING CONTROL x REGISTER (CONTINUED)

| bit 1 | BPLH: Blanking in PWMxL High Enable bit                                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> </ul> |

| bit 0 | BPLL: Blanking in PWMxL Low Enable bit                                                                                                                            |

|       | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is low</li> </ul>   |

**Note 1:** The blanking signal is selected via the BLANKSELx bits in the AUXCONx register.

## 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 dsPIC33FJ64GS406/606/608/610 and families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)" (DS70000195) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit ( $I^2C$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock.

- The SDAx pin is data.

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C Interface Supporting Both Master and Slave modes of Operation

- I<sup>2</sup>C Slave mode Supports 7-Bit and 10-Bit Addressing

- I<sup>2</sup>C Master mode Supports 7-Bit and 10-Bit Addressing

- I<sup>2</sup>C Port allows Bidirectional Transfers Between Master and Slaves

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control)

- I<sup>2</sup>C Supports Multi-Master Operation, Detects Bus Collision and Arbitrates Accordingly

## 19.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7-bit and 10-bit addressing.

The I<sup>2</sup>C module can operate either as a slave or a master on an I<sup>2</sup>C bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, refer to the "*dsPIC33/PIC24 Family Reference Manual*". Please see the Microchip web site (www.microchip.com) for the latest "*dsPIC33/PIC24 Family Reference Manual*" sections.

## 19.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write:

- I2CxRSR is the shift register used for shifting data internal to the module and the user application has no access to it.

- I2CxRCV is the receive buffer and the register to which data bytes are written or from which data bytes are read.

- I2CxTRN is the transmit register to which bytes are written during a transmit operation.

- The I2CxADD register holds the slave address.

- A status bit, ADD10, indicates 10-Bit Addressing mode.

- The I2CxBRG acts as the Baud Rate Generator (BRG) reload value.

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV and an interrupt pulse is generated.

## REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UxRX Idle state is '0'                                                                                                                                                         |

|         | 0 = UxRX Idle state is '1'                                                                                                                                                         |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | 11 = 9-bit data, no parity                                                                                                                                                         |

|         | 10 = 8-bit data, odd parity                                                                                                                                                        |

|         | 01 = 8-bit data, even parity                                                                                                                                                       |

|         | 00 = 8-bit data, no parity                                                                                                                                                         |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                      |

|         | 1 = Two Stop bits                                                                                                                                                                  |

|         | 0 = One Stop bit                                                                                                                                                                   |

| Note 1: | Refer to "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual" for information or                                                                                        |

- enabling the UART module for receive or transmit operation. That section of the manual is available on the Microchip web site: www.microchip.com.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

| REGISTER 21-20: | CxRXMnSID: ECANx ACCEPTANCE FILTER MASK n STANDARD IDENTIFIER |

|-----------------|---------------------------------------------------------------|

|                 | REGISTER (n = 0-2)                                            |

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| SID10  | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | —   | MIDE  | —   | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-5    | SID<10:0>: Standard Identifier bits<br>1 = Includes bit, SIDx, in filter comparison<br>CIDy bit is don't corr in filter comparison                                                                                                                                                                |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>h</b> :4 | 0 = SIDx bit is don't care in filter comparison                                                                                                                                                                                                                                                   |

| bit 4       | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                        |

| bit 3       | MIDE: Identifier Receive Mode bit                                                                                                                                                                                                                                                                 |

|             | <ul> <li>1 = Matches only message types (standard or extended address) that correspond to EXIDE bit in filter</li> <li>0 = Matches either standard or extended address message if filters match<br/>(i.e., if (Filter SID) = (Message SID) or if (Filter SID/EID) = (Message SID/EID))</li> </ul> |

| bit 2       | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                        |

| bit 1-0     | EID<17:16>: Extended Identifier bits                                                                                                                                                                                                                                                              |

|             | 1 = Includes bit, EIDx, in filter comparison                                                                                                                                                                                                                                                      |

|             | 0 = EIDx bit is don't care in filter comparison                                                                                                                                                                                                                                                   |

## REGISTER 21-21: CxRXMnEID: ECANx ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER REGISTER (n = 0-2)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

**EID<15:0>:** Extended Identifier bits 1 = Includes bit, EIDx, in filter comparison

- 0 = EIDx bit is don't care in filter comparison

- © 2009-2014 Microchip Technology Inc.

| U-0                  | U-0                                                        | U-0                                                                                 | R/C-0, HS             | R/C-0, HS             | R/C-0, HS             | R/C-0, HS            | R/C-0, HS            |  |  |

|----------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|----------------------|----------------------|--|--|

| _                    | —                                                          | —                                                                                   | P12RDY <sup>(1)</sup> | P11RDY <sup>(1)</sup> | P10RDY <sup>(1)</sup> | P9RDY <sup>(1)</sup> | P8RDY <sup>(1)</sup> |  |  |

| bit 15               |                                                            |                                                                                     |                       |                       |                       |                      | bit 8                |  |  |

|                      |                                                            |                                                                                     |                       |                       |                       |                      |                      |  |  |

| R/C-0, HS            | R/C-0, HS                                                  | R/C-0, HS                                                                           | R/C-0, HS             | R/C-0, HS             | R/C-0, HS             | R/C-0, HS            | R/C-0, HS            |  |  |

| P7RDY <sup>(1)</sup> | P6RDY <sup>(1)</sup>                                       | P5RDY <sup>(1)</sup>                                                                | P4RDY <sup>(1)</sup>  | P3RDY <sup>(1)</sup>  | P2RDY <sup>(1)</sup>  | P1RDY <sup>(1)</sup> | P0RDY <sup>(1)</sup> |  |  |

| bit 7                |                                                            | bit 0                                                                               |                       |                       |                       |                      |                      |  |  |

|                      |                                                            |                                                                                     |                       |                       |                       |                      |                      |  |  |

| Legend:              |                                                            | C = Clearable b                                                                     | oit                   | HS - Hardwa           | re Settable bit       |                      |                      |  |  |

| R = Readable         | e bit                                                      | W = Writable bi                                                                     | t                     | U = Unimpler          | mented bit, rea       | d as '0'             |                      |  |  |

| -n = Value at        | POR                                                        | '1' = Bit is set                                                                    |                       | '0' = Bit is cle      | ared                  | x = Bit is unk       | nown                 |  |  |

|                      |                                                            |                                                                                     |                       |                       |                       |                      | J                    |  |  |

| bit 15-13            | Unimplemen                                                 | ted: Read as '0                                                                     | ,                     |                       |                       |                      |                      |  |  |

| bit 6                | P12RDY: Co                                                 | nversion Data fo                                                                    | r Pair 12 Read        | y bit <b>(1)</b>      |                       |                      |                      |  |  |

|                      | Bit is set whe                                             | en data is ready i                                                                  | n buffer, cleare      | d when a '0' is       | written to this       | bit.                 |                      |  |  |

| bit 5                | P11RDY: Cor                                                | nversion Data fo                                                                    | r Pair 11 Read        | y bit <sup>(1)</sup>  |                       |                      |                      |  |  |

|                      | Bit is set whe                                             | en data is ready i                                                                  | n buffer, cleare      | d when a '0' is       | s written to this     | bit.                 |                      |  |  |

| bit 4                | P10RDY: Co                                                 | nversion Data fo                                                                    | r Pair 10 Read        | y bit <sup>(1)</sup>  |                       |                      |                      |  |  |

|                      | Bit is set whe                                             | en data is ready i                                                                  | n buffer, cleare      | ed when a '0' is      | s written to this     | bit.                 |                      |  |  |

| bit 3                | P9RDY: Con                                                 | version Data for                                                                    | Pair 9 Ready b        | oit <sup>(1)</sup>    |                       |                      |                      |  |  |

|                      |                                                            | en data is ready i                                                                  |                       |                       | s written to this     | bit.                 |                      |  |  |

| bit 2                | P8RDY: Con                                                 | version Data for                                                                    | Pair 8 Ready b        | <sub>oit</sub> (1)    |                       |                      |                      |  |  |

|                      |                                                            | en data is ready i                                                                  |                       |                       | s written to this     | bit.                 |                      |  |  |

| bit 1                |                                                            | version Data for                                                                    |                       |                       |                       |                      |                      |  |  |

|                      |                                                            | en data is ready i                                                                  |                       |                       | s written to this     | bit.                 |                      |  |  |

| bit 6                |                                                            | version Data for                                                                    |                       |                       |                       |                      |                      |  |  |

|                      |                                                            | en data is ready i                                                                  |                       |                       | s written to this     | bit.                 |                      |  |  |

| bit 5                |                                                            | version Data for                                                                    |                       |                       |                       |                      |                      |  |  |

|                      |                                                            | en data is ready i                                                                  |                       |                       | s written to this     | bit.                 |                      |  |  |

| bit 4                |                                                            | version Data for                                                                    |                       |                       |                       |                      |                      |  |  |

|                      |                                                            | Bit is set when data is ready in buffer, cleared when a '0' is written to this bit. |                       |                       |                       |                      |                      |  |  |

| bit 3                |                                                            | version Data for                                                                    |                       |                       |                       |                      |                      |  |  |

|                      |                                                            | en data is ready i                                                                  |                       |                       | s written to this     | bit.                 |                      |  |  |

| bit 2                |                                                            | version Data for                                                                    |                       |                       |                       |                      |                      |  |  |

|                      |                                                            | en data is ready i                                                                  |                       |                       | s written to this     | bit.                 |                      |  |  |

| bit 1                | P1RDY: Conversion Data for Pair 1 Ready bit <sup>(1)</sup> |                                                                                     |                       |                       |                       |                      |                      |  |  |

## **REGISTER 22-2: ADSTAT: ADC STATUS REGISTER**

Bit is set when data is ready in buffer, cleared when a '0' is written to this bit. PORDY: Conversion Data for Pair 0 Ready bit<sup>(1)</sup> bit 0 Bit is set when data is ready in buffer, cleared when a '0' is written to this bit.

Note 1: Not all PxRDY bits are available on all devices. See Figure 22-1, Figure 22-2, Figure 22-3 and Figure 22-4 for the available analog inputs.

| TABLE 24-2: | dsPIC33F CONFIGURATION BITS DESCRIPTION |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit Field   | Register                                | RTSP Effect                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| BWRP        | FBS                                     | Immediate                                                                                              | Boot Segment Program Flash Write Protection bit<br>1 = Boot segment can be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| BSS<2:0>    | FBS                                     | Immediate                                                                                              | <ul> <li>Boot Segment Program Flash Code Protection Size bits</li> <li>X11 = No boot program Flash segment</li> <li>Boot Space is 256 Instruction Words (except interrupt vectors):</li> <li>110 = Standard security; boot program Flash segment ends at 0x0003FE</li> <li>010 = High security; boot program Flash segment ends at 0x0003FE</li> <li>Boot Space is 768 Instruction Words (except interrupt vectors):</li> <li>101 = Standard security; boot program Flash segment ends at 0x0007FE</li> <li>001 = High security; boot program Flash segment ends at 0x0007FE</li> <li>Boot Space is 1792 Instruction Words (except interrupt vectors):</li> <li>100 = Standard security; boot program Flash segment ends at 0x0007FE</li> <li>Boot Space is 1792 Instruction Words (except interrupt vectors):</li> <li>100 = Standard security; boot program Flash segment ends at 0x000FFE</li> <li>000 = High security; boot program Flash segment ends at 0x000FFE</li> </ul> |  |  |

| GSS<1:0>    | FGS                                     | Immediate                                                                                              | General Segment Code-Protect bits<br>11 = User program memory is not code-protected<br>10 = Standard security<br>0x = High security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| GWRP        | FGS                                     | Immediate                                                                                              | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| IESO        | FOSCSEL                                 | Immediate                                                                                              | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start-up device with FRC, then automatically switch to the user selected oscillator source when ready</li> <li>0 = Start-up device with user selected oscillator source</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |