Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, QEI, POR, PWM, WDT                                 |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 9K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10b; D/A 1x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs610-e-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

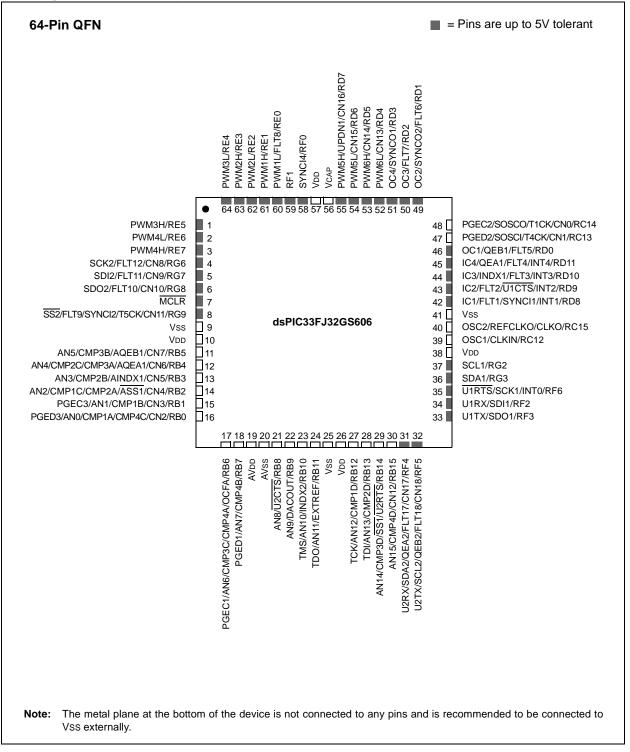

#### Pin Diagrams (Continued)

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>                                                                                                                                                                                                                                                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)</pre> |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                                                                                                                                                                                                                                                                                                                            |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                             |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                   |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = Result was negative</li> <li>0 = Result was non-negative (zero or positive)</li> </ul>                                                                                                                                                                                                                                                                                    |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                               |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of a magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                   |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                 |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                |

|         |                                                                                                                                                                                                                                                                                                                                                                                        |

- Note 1: This bit can be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

- 4: Clearing this bit will clear SA and SB.

| File<br>Name | SFR<br>Addr | Bit 15   | Bit 14              | Bit 13   | Bit 12   | Bit 11   | Bit 10    | Bit 9         | Bit 8         | Bit 7 | Bit 6   | Bit 5    | Bit 4         | Bit 3     | Bit    | 2 Bit 1   | 1 Bit 0 | All<br>Reset |

|--------------|-------------|----------|---------------------|----------|----------|----------|-----------|---------------|---------------|-------|---------|----------|---------------|-----------|--------|-----------|---------|--------------|

| WREG0        | 0000        |          | Working Register 0  |          |          |          |           |               |               |       |         |          | 0000          |           |        |           |         |              |

| WREG1        | 0002        |          |                     |          |          |          | V         | /orking Regis | ter 1         |       |         |          |               |           |        |           |         | 0000         |

| WREG2        | 0004        |          |                     |          |          |          | V         | /orking Regis | ter 2         |       |         |          |               |           |        |           |         | 0000         |

| WREG3        | 0006        |          |                     |          |          |          | V         | /orking Regis | ter 3         |       |         |          |               |           |        |           |         | 0000         |

| WREG4        | 8000        |          |                     |          |          |          | V         | /orking Regis | ter 4         |       |         |          |               |           |        |           |         | 0000         |

| WREG5        | 000A        |          |                     |          |          |          | V         | /orking Regis | ter 5         |       |         |          |               |           |        |           |         | 0000         |

| WREG6        | 000C        |          |                     |          |          |          | V         | /orking Regis | ter 6         |       |         |          |               |           |        |           |         | 0000         |

| WREG7        | 000E        |          |                     |          |          |          | V         | /orking Regis | ter 7         |       |         |          |               |           |        |           |         | 0000         |

| WREG8        | 0010        |          |                     |          |          |          | V         | /orking Regis | ter 8         |       |         |          |               |           |        |           |         | 0000         |

| WREG9        | 0012        |          |                     |          |          |          | V         | /orking Regis | ter 9         |       |         |          |               |           |        |           |         | 0000         |

| WREG10       | 0014        |          |                     |          |          |          | W         | orking Regist | er 10         |       |         |          |               |           |        |           |         | 0000         |

| WREG11       | 0016        |          |                     |          |          |          | W         | orking Regist | er 11         |       |         |          |               |           |        |           |         | 0000         |

| WREG12       | 0018        |          |                     |          |          |          | W         | orking Regist | er 12         |       |         |          |               |           |        |           |         | 0000         |

| WREG13       | 001A        |          |                     |          |          |          | W         | orking Regist | er 13         |       |         |          |               |           |        |           |         | 0000         |

| WREG14       | 001C        |          | Working Register 14 |          |          |          |           | 0000          |               |       |         |          |               |           |        |           |         |              |

| WREG15       | 001E        |          |                     |          |          |          | W         | orking Regist | er 15         |       |         |          |               |           |        |           |         | 0800         |

| SPLIM        | 0020        |          |                     |          |          |          | Stack     | Pointer Limit | Register      |       |         |          |               |           |        |           |         | xxxx         |

| ACCAL        | 0022        |          |                     |          |          |          |           | ACCAL         |               |       |         |          |               |           |        |           |         | xxxx         |

| ACCAH        | 0024        |          |                     |          |          |          |           | ACCAH         |               |       |         |          |               |           |        |           |         | xxxx         |

| ACCAU        | 0026        | ACCA<39> | ACCA<39>            | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39>  | ACCA<39>      | ACCA<39>      |       |         |          | ACCA          | U         |        |           |         | xxxx         |

| ACCBL        | 0028        |          |                     |          |          |          |           | ACCBL         |               |       |         |          |               |           |        |           |         | xxxx         |

| ACCBH        | 002A        |          |                     |          |          |          |           | ACCBH         |               |       |         |          |               |           |        |           |         | xxxx         |

| ACCBU        | 002C        | ACCB<39> | ACCB<39>            | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39>  | ACCB<39>      | ACCB<39>      |       |         |          | ACCB          | U         |        |           |         | xxxx         |

| PCL          | 002E        |          |                     |          |          |          | Program ( | Counter Low I | Byte Register |       |         |          |               |           |        |           |         | 0000         |

| PCH          | 0030        |          | —                   | —        |          | —        | —         |               | —             |       |         | Program  | Counter Hig   | gh Byte I | Regist | er        |         | 0000         |

| TBLPAG       | 0032        |          | —                   | —        |          | —        | —         |               | —             |       |         | Table Pa | ge Address    | Pointer I | Regist | .er       |         | 0000         |

| PSVPAG       | 0034        | —        | —                   | —        |          | —        | —         |               | _             | F     | Program | Memory V | isibility Pag | e Addres  | s Poi  | nter Regi | ster    | 0000         |

| RCOUNT       | 0036        |          |                     |          |          |          | REPEAT    | Loop Counter  | er Register   |       |         |          |               |           |        |           |         | xxxx         |

| DCOUNT       | 0038        |          |                     |          |          |          |           | DCOUNT<15     | :0>           |       |         |          |               |           |        |           |         | xxxx         |

| DOSTARTL     | 003A        |          |                     |          |          |          | DOS       | TARTL<15:1>   |               |       |         |          |               |           |        |           | 0       | xxxx         |

| DOSTARTH     | 003C        | _        | _                   | —        | _        | —        | —         | —             | —             | -     | —       |          | DC            | STARTH    | 1<5:0: | >         |         | 00xx         |

| DOENDL       | 003E        |          |                     |          |          |          | DOE       | NDL<15:1>     |               |       |         |          |               |           |        |           | 0       | xxxx         |

| DOENDH       | 0040        | _        | —                   | —        | —        | —        | _         | —             | _             | —     | —       |          |               | DOEN      | ЭН     |           |         | 00xx         |

| SR           | 0042        | OA       | OB                  | SA       | SB       | OAB      | SAB       | DA            | DC            | IPL2  | IPL1    | IPL0     | RA            | N         | OV     | / Z       | С       | 0000         |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.2 RTSP Operation

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 27-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the Table Write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

The programming time depends on the FRC accuracy (see Table 27-20) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time and Word Write Cycle Time parameters (see Table 27-12).

#### EQUATION 5-1: PROGRAMMING TIME

$\frac{T}{7.37 \text{ MHz} \times (FRC \text{ Accuracy})\% \times (FRC \text{ Tuning})\%}$

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 2\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `b000000, the minimum row write time is equal to Equation 5-2.

# EQUATION 5-2: MINIMUM ROW WRITE TIME

| $T_{RW} = \cdot$ | 11064 Cycles                                        | = 1.473 ms |

|------------------|-----------------------------------------------------|------------|

| IKW = 2          | $7.37  MHz \times (1 + 0.02) \times (1 - 0.000938)$ | -1.4/3 ms  |

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM ROW WRITE TIME

| $T_{RW} =$ | <u>— 11064 Cycles</u> = $1.533$ ms                                            |

|------------|-------------------------------------------------------------------------------|

| INW -      | $7.37 \text{ MHz} \times (1 - 0.02) \times (1 - 0.000938) = 1.555 \text{ ms}$ |

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

## dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                                                                                     | R/W-0 <sup>(1)</sup>                                                                | U-0             | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| WR                    | WREN                                                                                                     | WRERR                                                                               | —               | _                     | —                     | —                     | —                     |  |  |  |

| bit 15                |                                                                                                          | 1                                                                                   |                 | I.                    |                       |                       | bit 8                 |  |  |  |

|                       |                                                                                                          |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

| U-0                   | R/W-0 <sup>(1)</sup>                                                                                     | U-0                                                                                 | U-0             | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  |  |  |  |

| _                     | ERASE                                                                                                    |                                                                                     | —               | NVMOP3 <sup>(2)</sup> | NVMOP2 <sup>(2)</sup> | NVMOP1 <sup>(2)</sup> | NVMOP0 <sup>(2)</sup> |  |  |  |

| bit 7                 |                                                                                                          |                                                                                     |                 |                       |                       | •                     | bit 0                 |  |  |  |

|                       |                                                                                                          |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

| Legend:               |                                                                                                          | SO = Settal                                                                         | ole Only bit    |                       |                       |                       |                       |  |  |  |

| R = Readable          | bit                                                                                                      | W = Writabl                                                                         | e bit           | U = Unimpler          | mented bit, read      | l as '0'              |                       |  |  |  |

| -n = Value at F       | POR                                                                                                      | '1' = Bit is s                                                                      | et              | '0' = Bit is cle      | ared                  | x = Bit is unkr       | nown                  |  |  |  |

|                       |                                                                                                          |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

| bit 15                | WR: Write Con                                                                                            | trol bit <sup>(1)</sup>                                                             |                 |                       |                       |                       |                       |  |  |  |

|                       | 1 = Initiates a                                                                                          |                                                                                     |                 |                       | on; the operation     | on is self-timed      | and the bit is        |  |  |  |

|                       | cleared by<br>0 = Program of                                                                             | hardware one                                                                        |                 |                       | 2                     |                       |                       |  |  |  |

| bit 14                | -                                                                                                        | -                                                                                   |                 |                       | 5                     |                       |                       |  |  |  |

| DIL 14                |                                                                                                          | VREN: Write Enable bit <sup>(1)</sup><br>. = Enables Flash program/erase operations |                 |                       |                       |                       |                       |  |  |  |

|                       | 0 = Inhibits Fla                                                                                         |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

| bit 13                | WRERR: Write                                                                                             |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

|                       | 1 = An improper program or erase sequence attempt or termination has occurred (bit is set                |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

|                       | automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

|                       |                                                                                                          |                                                                                     |                 | pleted normally       | /                     |                       |                       |  |  |  |

| bit 12-7              | Unimplemente                                                                                             |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

| bit 6                 | ERASE: Erase                                                                                             | •                                                                                   |                 |                       |                       |                       |                       |  |  |  |

|                       | 1 = Performs tl<br>0 = Performs tl                                                                       |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

| bit 5-4               | Unimplemente                                                                                             |                                                                                     |                 |                       |                       | on the next w         | i communa             |  |  |  |

| bit 3-0               | NVMOP<3:0>:                                                                                              |                                                                                     |                 | s(1,2)                |                       |                       |                       |  |  |  |

|                       | If ERASE = 1:                                                                                            |                                                                                     |                 | ,                     |                       |                       |                       |  |  |  |

|                       | 1111 = Memor                                                                                             | y bulk erase o                                                                      | operation       |                       |                       |                       |                       |  |  |  |

|                       | 1101 = Erases                                                                                            |                                                                                     | ment (GS)       |                       |                       |                       |                       |  |  |  |

|                       | 0011 = No ope<br>0010 = Memory                                                                           |                                                                                     | oporation       |                       |                       |                       |                       |  |  |  |

|                       | 0001 = No ope                                                                                            |                                                                                     | operation       |                       |                       |                       |                       |  |  |  |

|                       | 0000 = Erases                                                                                            |                                                                                     | figuration regi | ister byte            |                       |                       |                       |  |  |  |

|                       | If ERASE = 0:                                                                                            | If ERASE = 0:                                                                       |                 |                       |                       |                       |                       |  |  |  |

|                       | 1111 = No ope                                                                                            |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

|                       | 1101 = No ope<br>0011 = Memory                                                                           |                                                                                     | m operation     |                       |                       |                       |                       |  |  |  |

|                       | 0010 = No ope                                                                                            |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

|                       | 0001 = Memor                                                                                             | y row progran                                                                       |                 |                       |                       |                       |                       |  |  |  |

|                       | 0000 = Program                                                                                           | ms a single C                                                                       | onfiguration r  | egister byte          |                       |                       |                       |  |  |  |

| Note 1: The           | ese bits can only                                                                                        | be reset on a                                                                       | Power-on Re     | eset.                 |                       |                       |                       |  |  |  |

|                       | -                                                                                                        |                                                                                     |                 |                       |                       |                       |                       |  |  |  |

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

2: All other combinations of NVMOP<3:0> are unimplemented.

NOTES:

| HS/HC-0       | HS/HC-0                                                      | HS/HC-0                                              | R/W-0                 | R/W-0            | R/W-0                           | R/W-0                         | R/W-0               |  |  |  |

|---------------|--------------------------------------------------------------|------------------------------------------------------|-----------------------|------------------|---------------------------------|-------------------------------|---------------------|--|--|--|

| FLTSTAT(      | <sup>1)</sup> CLSTAT <sup>(1)</sup>                          | TRGSTAT                                              | FLTIEN                | CLIEN            | TRGIEN                          | ITB <sup>(3)</sup>            | MDCS <sup>(3)</sup> |  |  |  |

| bit 15        |                                                              |                                                      |                       |                  |                                 |                               | bit 8               |  |  |  |

| DAMO          | DAM 0                                                        | D/M/ O                                               |                       | R/W-0            | DAMA                            | DAMO                          | DAMO                |  |  |  |

| R/W-0         | R/W-0                                                        | R/W-0<br>DTCP <sup>(4)</sup>                         | U-0                   |                  | R/W-0<br>CAM <sup>(2,3,5)</sup> | R/W-0<br>XPRES <sup>(6)</sup> | R/W-0               |  |  |  |

| DTC1<br>bit 7 | DTC0                                                         | DICPO                                                | —                     | MTBS             | CAM                             | APRES(*)                      | IUE<br>bit          |  |  |  |

|               |                                                              |                                                      |                       |                  |                                 |                               |                     |  |  |  |

| Legend:       |                                                              | HC = Hardware                                        | Clearable bit         | HS = Hardw       | are Settable bit                |                               |                     |  |  |  |

| R = Reada     | ble bit                                                      | W = Writable b                                       | it                    | U = Unimple      | mented bit, rea                 | d as '0'                      |                     |  |  |  |

| -n = Value    | at POR                                                       | '1' = Bit is set                                     |                       | '0' = Bit is cl  | eared                           | x = Bit is unk                | nown                |  |  |  |

| bit 15        | FLTSTAT: Fa                                                  | ult Interrupt Stat                                   | us bit <sup>(1)</sup> |                  |                                 |                               |                     |  |  |  |

|               |                                                              | rrupt is pending                                     |                       |                  |                                 |                               |                     |  |  |  |

|               |                                                              | nterrupt is pend                                     |                       |                  |                                 |                               |                     |  |  |  |

|               |                                                              | ared by setting F                                    |                       |                  |                                 |                               |                     |  |  |  |

| bit 14        |                                                              | rent-Limit Interru                                   | •                     |                  |                                 |                               |                     |  |  |  |

|               |                                                              | mit interrupt is pe<br>nt-limit interrupt is         |                       |                  |                                 |                               |                     |  |  |  |

|               |                                                              | ared by setting C                                    |                       |                  |                                 |                               |                     |  |  |  |

| bit 13        | TRGSTAT: Tr                                                  | igger Interrupt S                                    | tatus bit             |                  |                                 |                               |                     |  |  |  |

|               |                                                              | terrupt is pendin                                    | •                     |                  |                                 |                               |                     |  |  |  |

|               |                                                              | r interrupt is pen<br>ared by setting T              |                       |                  |                                 |                               |                     |  |  |  |

| bit 12        |                                                              |                                                      |                       |                  |                                 |                               |                     |  |  |  |

|               |                                                              | Fault Interrupt Enable bit<br>t interrupt is enabled |                       |                  |                                 |                               |                     |  |  |  |

|               |                                                              | rrupt is disabled                                    | and FLTSTAT b         | oit is cleared   |                                 |                               |                     |  |  |  |

| bit 11        | CLIEN: Curre                                                 | Current-Limit Interrupt Enable bit                   |                       |                  |                                 |                               |                     |  |  |  |

|               |                                                              | mit interrupt is e<br>mit interrupt is di            |                       | STAT bit is cle  | ared                            |                               |                     |  |  |  |

| bit 10        | TRGIEN: Trig                                                 | ger Interrupt En                                     | able bit              |                  |                                 |                               |                     |  |  |  |

|               |                                                              | event generates<br>/ent interrupts a                 |                       |                  | is cleared                      |                               |                     |  |  |  |

| bit 9         |                                                              | dent Time Base                                       |                       |                  |                                 |                               |                     |  |  |  |

|               | 1 = PHASEx/                                                  | SPHASEx regist                                       | ters provide tim      | •                | •                               | enerator                      |                     |  |  |  |

| bit 8         |                                                              | er Duty Cycle Re                                     | -                     |                  |                                 |                               |                     |  |  |  |

|               | 1 = MDC regi                                                 | ster provides du<br>d SDCx registers                 | ty cycle informa      | ation for this P |                                 | generator                     |                     |  |  |  |

| Note 1:       | Software must cle                                            | ear the interrupt                                    | status here and       | l in the corresp | oonding IFSx bit                | in the interrup               | t controller.       |  |  |  |

|               | The Independent<br>CAM bit is ignore                         |                                                      | e (ITB = 1) mus       | st be enabled t  | o use Center-A                  | igned mode. If                | TTB = 0, the        |  |  |  |

| 3:            | These bits should                                            | I not be changed                                     | after the PWM         | l is enabled by  | setting PTEN (                  | PTCON<15>)                    | = 1.                |  |  |  |

|               | For DTCP to be e                                             |                                                      |                       |                  |                                 |                               |                     |  |  |  |

|               | Center-Aligned m<br>registers. The hig<br>the fastest clock. |                                                      |                       |                  |                                 |                               |                     |  |  |  |

| 6:            | Configure CLMO<br>Reset mode.                                | D (FCLCONX<8                                         | 3>) = 0 and ITB       | (PWMCONx         | <9>) = 1 to ope                 | rate in Externa               | al Period           |  |  |  |

#### REGISTER 16-11: PWMCONX: PWM CONTROL x REGISTER

#### REGISTER 16-11: PWMCONx: PWM CONTROL x REGISTER (CONTINUED)

| bit 7- | 6  | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode<br>10 = Dead-time function is disabled                                                                  |

|--------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |    | <ul> <li>01 = Negative dead time is actively applied for Complementary Output mode</li> <li>00 = Positive dead time is actively applied for all output modes</li> </ul>                   |

| bit 5  |    | DTCP: Dead-Time Compensation Polarity bit <sup>(4)</sup>                                                                                                                                  |

|        |    | <ul> <li>1 = If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened;</li> <li>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened</li> </ul>                                     |

|        |    | <ul> <li>If DTCMPx = 0, PWMxH is shortened and PWMLx is lengthened;</li> <li>If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened</li> </ul>                                         |

| bit 4  |    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 3  |    | MTBS: Master Time Base Select bit                                                                                                                                                         |

|        |    | <ul> <li>1 = PWM generator uses the secondary master time base for synchronization and the clock source for<br/>the PWM generation logic (if secondary time base is available)</li> </ul> |

|        |    | <ul> <li>PWM generator uses the primary master time base for synchronization and the clock source for<br/>the PWM generation logic</li> </ul>                                             |

| bit 2  |    | CAM: Center-Aligned Mode Enable bit <sup>(2,3,5)</sup>                                                                                                                                    |

|        |    | <ul><li>1 = Center-Aligned mode is enabled</li><li>0 = Edge-Aligned mode is enabled</li></ul>                                                                                             |

| bit 1  |    | XPRES: External PWM Reset Control bit <sup>(6)</sup>                                                                                                                                      |

|        |    | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time<br/>Base mode</li> </ul>                                                       |

|        |    | 0 = External pins do not affect PWM time base                                                                                                                                             |

| bit 0  |    | IUE: Immediate Update Enable bit                                                                                                                                                          |

|        |    | <ul> <li>1 = Updates to the active MDC/PDCx/SDCx registers are immediate</li> <li>0 = Updates to the active PDCx registers are synchronized to the PWM time base</li> </ul>               |

| Note   | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                                                                              |

|        | 2: | The Independent Time Base mode (ITB = 1) must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.                                                                  |

|        |    |                                                                                                                                                                                           |

- **3:** These bits should not be changed after the PWM is enabled by setting PTEN (PTCON<15>) = 1.

- 4: For DTCP to be effective, DTC<1:0> must be set to '11'; otherwise, DTCP is ignored.

- 5: Center-Aligned mode ignores the Least Significant 3 bits of the Duty Cycle, Phase and Dead-Time registers. The highest Center-Aligned mode resolution available is 8.32 ns with the clock prescaler set to the fastest clock.

- 6: Configure CLMOD (FCLCONX<8>) = 0 and ITB (PWMCONx<9>) = 1 to operate in External Period Reset mode.

#### REGISTER 16-26: PWMCAPx: PRIMARY PWM TIME BASE CAPTURE x REGISTER

| R-0                                | R-0                               | R-0                        | R-0                                     | R-0                                | R-0 | R-0 | R-0   |

|------------------------------------|-----------------------------------|----------------------------|-----------------------------------------|------------------------------------|-----|-----|-------|

|                                    |                                   |                            | PWMCAP                                  | <12:5> <sup>(1,2,3,4)</sup>        |     |     |       |

| bit 15                             |                                   |                            |                                         |                                    |     |     | bit 8 |

|                                    |                                   |                            |                                         |                                    |     |     |       |

| R-0                                | R-0                               | R-0                        | R-0                                     | R-0                                | U-0 | U-0 | U-0   |

|                                    | PW                                | /MCAP<4:0> <sup>(1,2</sup> | ,3,4)                                   |                                    | —   | —   | —     |

| bit 7                              |                                   |                            |                                         |                                    |     |     | bit 0 |

|                                    |                                   |                            |                                         |                                    |     |     |       |

| Legend:                            |                                   |                            |                                         |                                    |     |     |       |

| R = Readable bit                   | R = Readable bit W = Writable bit |                            |                                         | U = Unimplemented bit, read as '0' |     |     |       |

| -n = Value at POR '1' = Bit is set |                                   |                            | '0' = Bit is cleared x = Bit is unknown |                                    |     |     |       |

bit 15-3 **PWMCAP<12:0>:** Captured PWM Time Base Value bits<sup>(1,2,3,4)</sup> The value in this register represents the captured PWM time base value when a leading edge is detected on the current-limit input.

#### bit 2-0 Unimplemented: Read as '0'

Note 1: The capture feature is only available on the primary output (PWMxH).

2: This feature is active only after LEB processing on the current-limit input signal is complete.

**3:** The minimum capture resolution is 8.32 ns.

4: This feature can be used when the XPRES bit (PWMCONx<1>) is set to '0'.

| U-0                           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                | R/W-0                                                                            | r-0                     | R/W-1            | R/W-0           | R/W-0  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------|------------------|-----------------|--------|

|                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                          | CSIDL                                                                                                                                | ABAT                                                                             | r                       | REQOP2           | REQOP1          | REQOP0 |

| bit 15                        |                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                      | ,,                                                                               |                         |                  |                 | bit 8  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                      |                                                                                  |                         |                  |                 |        |

| R-1                           | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                        | R-0                                                                                                                                  | U-0                                                                              | R/W-0                   | U-0              | U-0             | R/W-0  |

| OPMODE2                       | OPMODE1                                                                                                                                                                                                                                                                                                                                                                                                                                    | OPMODE0                                                                                                                              |                                                                                  | CANCAP                  |                  | —               | WIN    |

| bit 7                         |                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                      |                                                                                  |                         |                  |                 | bit 0  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                      |                                                                                  |                         |                  |                 |        |

| Legend:                       |                                                                                                                                                                                                                                                                                                                                                                                                                                            | r = Reserved                                                                                                                         | bit                                                                              |                         |                  |                 |        |

| R = Readable                  | bit                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable                                                                                                                         | bit                                                                              | U = Unimplei            | mented bit, read | l as '0'        |        |

| -n = Value at P               | OR                                                                                                                                                                                                                                                                                                                                                                                                                                         | '1' = Bit is set                                                                                                                     |                                                                                  | '0' = Bit is cle        | eared            | x = Bit is unkr | nown   |

| bit 15-14<br>bit 13<br>bit 12 | CSIDL: ECAN<br>1 = Discontinue<br>0 = Continues<br>ABAT: Abort A<br>1 = Signals al                                                                                                                                                                                                                                                                                                                                                         | ted: Read as '<br>Nx Stop in Idle l<br>ues module op<br>s module opera<br>All Pending Tra<br>Il transmit buffe<br>ill clear this bit | Mode bit<br>eration when<br>tion in Idle me<br>ansmissions b<br>ers to abort tra | ode<br>it<br>Insmission |                  |                 |        |

| bit 11                        | Reserved: Do                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                      |                                                                                  |                         | aboned           |                 |        |

| bit 10-8                      |                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>Request Ope</li> </ul>                                                                                                      | vation Mode I                                                                    | hits                    |                  |                 |        |

|                               | <pre>111 = Sets Listen All Messages mode 110 = Reserved 101 = Reserved 100 = Sets Configuration mode 011 = Sets Listen Only Mode 010 = Sets Loopback mode 001 = Sets Disable mode</pre>                                                                                                                                                                                                                                                    |                                                                                                                                      |                                                                                  |                         |                  |                 |        |

| bit 7-5                       | <ul> <li>000 = Sets Normal Operation mode</li> <li>OPMODE&lt;2:0&gt;: Operation Mode bits</li> <li>111 = Module is in Listen All Messages mode</li> <li>110 = Reserved</li> <li>101 = Reserved</li> <li>100 = Module is in Configuration mode</li> <li>011 = Module is in Listen Only mode</li> <li>010 = Module is in Loopback mode</li> <li>001 = Module is in Disable mode</li> <li>000 = Module is in Normal Operation mode</li> </ul> |                                                                                                                                      |                                                                                  |                         |                  |                 |        |

| bit 4                         |                                                                                                                                                                                                                                                                                                                                                                                                                                            | ted: Read as '                                                                                                                       | •                                                                                |                         |                  |                 |        |

| bit 3                         | <b>CANCAP:</b> EC<br>1 = Enables in                                                                                                                                                                                                                                                                                                                                                                                                        | CAN Message I<br>nput capture ba<br>ECAN capture                                                                                     | Receive Time                                                                     | -                       |                  |                 |        |

| bit 2-1                       | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                 | ted: Read as '                                                                                                                       | 0'                                                                               |                         |                  |                 |        |

| bit 0                         | WIN: SFR Ma                                                                                                                                                                                                                                                                                                                                                                                                                                | ap Window Sele                                                                                                                       | ect bit                                                                          |                         |                  |                 |        |

|                               | 1 = Uses filter<br>0 = Uses buff                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                      |                                                                                  |                         |                  |                 |        |

#### REGISTER 21-1: CxCTRL1: ECANx CONTROL REGISTER 1

| R/W-x                                                                                     | R/W-x                                | R/W-x             | R/W-x   | R/W-x                              | R/W-x | R/W-x              | R/W-x |

|-------------------------------------------------------------------------------------------|--------------------------------------|-------------------|---------|------------------------------------|-------|--------------------|-------|

| EID5                                                                                      | EID4                                 | EID3              | EID2    | EID1                               | EID0  | RTR                | RB1   |

| bit 15                                                                                    |                                      |                   | •       |                                    | •     |                    | bit 8 |

| U-x                                                                                       | U-x                                  | U-x               | R/W-x   | R/W-x                              | R/W-x | R/W-x              | R/W-x |

|                                                                                           | _                                    | _                 | RB0     | DLC3                               | DLC2  | DLC1               | DLC0  |

| bit 7                                                                                     |                                      |                   |         |                                    |       |                    | bit 0 |

|                                                                                           |                                      |                   |         |                                    |       |                    |       |

| Legend:                                                                                   |                                      |                   |         |                                    |       |                    |       |

| R = Readable                                                                              | e bit                                | W = Writable      | bit     | U = Unimplemented bit, read as '0' |       |                    |       |

| -n = Value at                                                                             | POR                                  | '1' = Bit is set  |         | '0' = Bit is cle                   | eared | x = Bit is unknown |       |

|                                                                                           |                                      |                   |         |                                    |       |                    |       |

| bit 15-10                                                                                 | EID<5:0>: E                          | xtended Identifie | er bits |                                    |       |                    |       |

| bit 9                                                                                     | RTR: Remote Transmission Request bit |                   |         |                                    |       |                    |       |

| <ul><li>1 = Message will request remote transmission</li><li>0 = Normal message</li></ul> |                                      |                   |         |                                    |       |                    |       |

#### BUFFER 21-3: ECANx MESSAGE BUFFER WORD 2

|         | 0 = Normal message                                |

|---------|---------------------------------------------------|

| bit 8   | RB1: Reserved Bit 1                               |

|         | User must set this bit to '0' per ECAN™ protocol. |

| bit 7-5 | Unimplemented: Read as '0'                        |

| bit 4   | RB0: Reserved Bit 0                               |

|         | User must set this bit to '0' per ECAN protocol.  |

| bit 3-0 | DLC<3:0>: Data Length Code bits                   |

#### BUFFER 21-4: ECANx MESSAGE BUFFER WORD 3

| R/W-x                              | R/W-x | R/W-x          | R/W-x             | R/W-x        | R/W-x           | R/W-x     | R/W-x |

|------------------------------------|-------|----------------|-------------------|--------------|-----------------|-----------|-------|

|                                    |       |                | В                 | yte 1        |                 |           |       |

| bit 15                             |       |                |                   |              |                 |           | bit 8 |

| R/W-x                              | R/W-x | R/W-x          | R/W-x             | R/W-x        | R/W-x           | R/W-x     | R/W-x |

|                                    |       |                | В                 | yte 0        |                 |           |       |

| bit 7                              |       |                |                   |              |                 |           | bit 0 |

| Legend:                            |       |                |                   |              |                 |           |       |

| R = Readable                       | bit   | W = Writable b | it                | U = Unimplem | nented bit, rea | ad as '0' |       |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is clea | ared         | x = Bit is unkr | nown      |       |

bit 7-0 Byte 0<7:0>: ECANx Message Byte 0

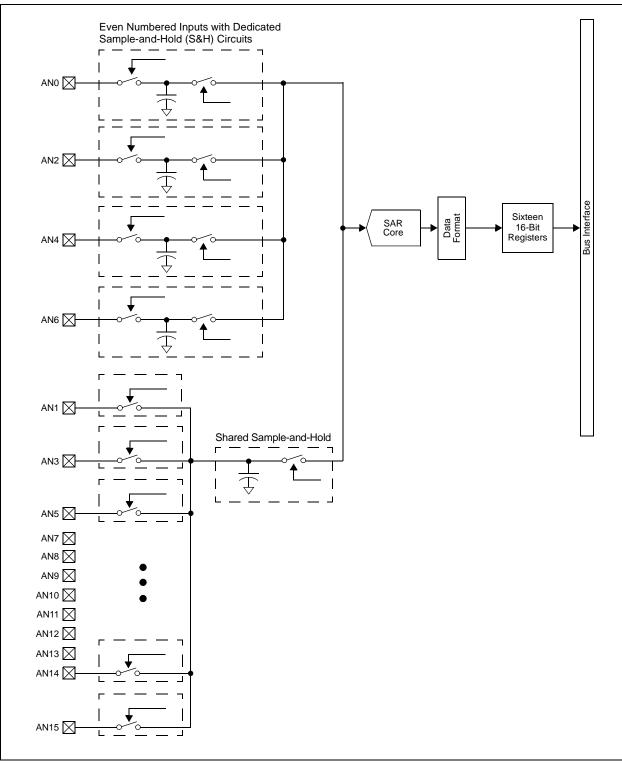

#### FIGURE 22-1: ADC BLOCK DIAGRAM FOR dsPIC33FJ32GS406 AND dsPIC33FJ64GS406 DEVICES WITH ONE SAR

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| R/W-0            | R/W-0                          | R/W-0                                  | R/W-0                     | R/W-0                              | R/W-0                           | R/W-0              | R/W-0        |  |

|------------------|--------------------------------|----------------------------------------|---------------------------|------------------------------------|---------------------------------|--------------------|--------------|--|

| IRQEN7           | PEND7                          | SWTRG7                                 | TRGSRC74                  | TRGSRC73                           | TRGSRC72                        | TRGSRC71           | TRGSRC70     |  |

| bit 15           |                                |                                        |                           |                                    |                                 |                    | bit 8        |  |