Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

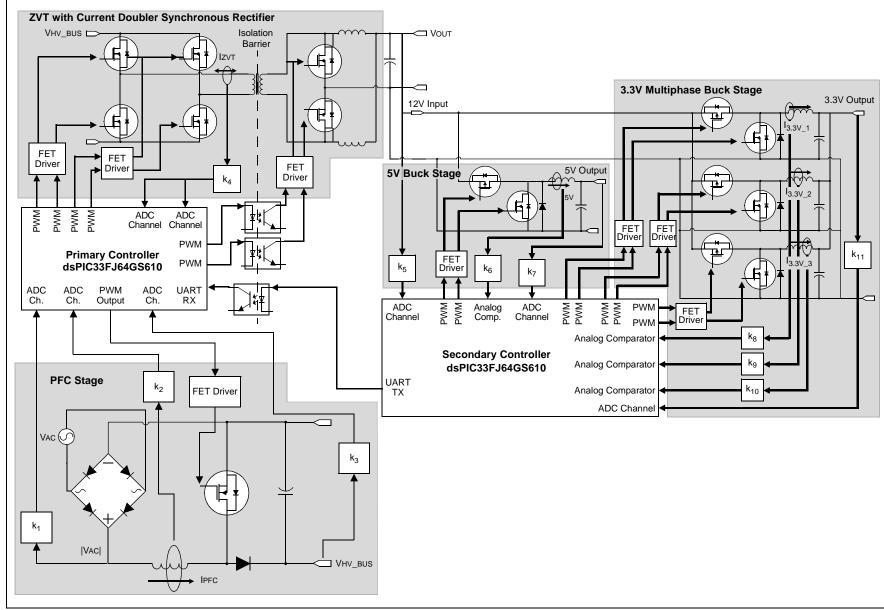

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, QEI, POR, PWM, WDT                                 |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 9K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10b; D/A 1x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs610-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ64GS606 DEVICES (CONTINUED)

| File    | SFR  |        |          |          |          |        |          |          |          |       |           |           |           |         |          |          |          | All    |

|---------|------|--------|----------|----------|----------|--------|----------|----------|----------|-------|-----------|-----------|-----------|---------|----------|----------|----------|--------|

| Name    | Addr | Bit 15 | Bit 14   | Bit 13   | Bit 12   | Bit 11 | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6     | Bit 5     | Bit 4     | Bit 3   | Bit 2    | Bit 1    | Bit 0    | Resets |

| IPC21   | 00CE | _      | —        | —        | —        | _      | _        |          | —        |       | ADCP12IP2 | ADCP12IP1 | ADCP12IP0 | _       | —        |          | —        | 0040   |

| IPC23   | 00D2 | —      | PWM2IP2  | PWM2IP1  | PWM2IP0  |        | PWM1IP2  | PWM1IP1  | PWM1IP0  |       | —         | -         | -         | —       | —        | -        | —        | 4400   |

| IPC24   | 00D4 | _      | PWM6IP2  | PWM6IP1  | PWM6IP0  |        | PWM5IP2  | PWM5IP1  | PWM5IP0  | _     | PWM4IP2   | PWM4IP1   | PWM4IP0   | _       | PWM3IP2  | PWM3IP1  | PWM3IP0  | 4444   |

| IPC25   | 00D6 | _      | AC2IP2   | AC2IP1   | AC2IP0   |        | PWM9IP2  | PWM9IP1  | PWM9IP0  | _     | PWM8IP2   | PWM8IP1   | PWM8IP0   | _       | PWM7IP2  | PWM7IP1  | PWM7IP0  | 4000   |

| IPC26   | 00D8 | _      | _        | _        | _        |        | _        | _        | _        | _     | AC4IP2    | AC4IP1    | AC4IP0    | _       | AC3IP2   | AC3IP1   | AC3IP0   | 0044   |

| IPC27   | 00DA | _      | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 |        | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | _     | _         | _         | _         | _       | _        | _        | _        | 4400   |

| IPC28   | 00DC | _      | ADCP5IP2 | ADCP5IP1 | ADCP5IP0 |        | ADCP4IP2 | ADCP4IP1 | ADCP4IP0 | _     | ADCP3IP2  | ADCP3IP1  | ADCP3IP0  | _       | ADCP2IP2 | ADCP2IP1 | ADCP2IP0 | 4444   |

| IPC29   | 00DE | _      | _        | _        | _        |        | _        | _        | _        | _     | ADCP7IP2  | ADCP7IP1  | ADCP7IP0  | _       | ADCP6IP2 | ADCP6IP1 | ADCP6IP0 | 0004   |

| INTTREG | 00E0 | _      | _        | _        | _        | ILR3   | ILR2     | ILR1     | ILR0     | _     | VECNUM6   | VECNUM5   | VECNUM4   | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000   |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14                                                                                                         | Bit 13         | Bit 12  | Bit 11   | Bit 10  | Bit 9     | Bit 8  | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|---------|----------------------------------------------------------------------------------------------------------------|----------------|---------|----------|---------|-----------|--------|----------|----------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON7      | 04E0        | FLTSTAT | CLSTAT                                                                                                         | TRGSTAT        | FLTIEN  | CLIEN    | TRGIEN  | ITB       | MDCS   | DTC1     | DTC0     | DTCP     | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON7       | 04E2        | PENH    | PENL                                                                                                           | POLH           | POLL    | PMOD1    | PMOD0   | OVRENH    | OVRENL | OVRDAT1  | OVRDAT0  | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON7      | 04E4        | IFLTMOD | CLSRC4                                                                                                         | CLSRC3         | CLSRC2  | CLSRC1   | CLSRC0  | CLPOL     | CLMOD  | FLTSRC4  | FLTSRC3  | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC7         | 04E6        |         |                                                                                                                | PDC7<15:0> 000 |         |          |         |           |        |          |          |          | 0000     |          |          |          |          |               |

| PHASE7       | 04E8        |         | PHASE7<15:0> 000                                                                                               |                |         |          |         |           |        |          |          | 0000     |          |          |          |          |          |               |

| DTR7         | 04EA        | _       |                                                                                                                |                |         |          |         |           |        |          |          | 0000     |          |          |          |          |          |               |

| ALTDTR7      | 04EA        | _       | _                                                                                                              |                |         |          |         |           |        | ALTDT    | R7<13:0> |          |          |          |          |          |          | 0000          |

| SDC7         | 04EE        |         |                                                                                                                |                |         |          |         |           | SDC.   | 7<15:0>  |          |          |          |          |          |          |          | 0000          |

| SPHASE7      | 04F0        |         |                                                                                                                |                |         |          |         |           | SPHAS  | E7<15:0> |          |          |          |          |          |          |          | 0000          |

| TRIG7        | 04F2        |         |                                                                                                                |                |         |          |         | TRGCMP<12 | ::0>   |          |          |          |          |          | -        | _        | _        | 0000          |

| TRGCON7      | 04F4        | TRGDIV3 | TRGDIV2                                                                                                        | TRGDIV1        | TRGDIV0 | _        | _       | _         | _      | DTM      | —        | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG7       | 04F6        |         |                                                                                                                |                |         |          | ;       | STRGCMP<1 | 2:0>   |          |          |          |          |          | _        | _        | —        | 0000          |

| PWMCAP7      | 04F8        |         | PWMCAP<12:0> 000                                                                                               |                |         |          |         |           |        |          |          | 0000     |          |          |          |          |          |               |

| LEBCON7      | 04FA        | PHR     | PHF                                                                                                            | PLR            | PLF     | FLTLEBEN | CLLEBEN | _         | —      | _        | _        | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY7      | 04FC        | _       | _                                                                                                              | _              | —       |          |         |           | L      | EB<8:0>  |          |          |          |          | —        | _        | —        | 0000          |

| AUXCON7      | 04FE        | HRPDIS  | PDIS HRDDIS BLANKSEL3 BLANKSEL2 BLANKSEL1 BLANKSEL0 - CHOPSEL3 CHOPSEL2 CHOPSEL1 CHOPSEL0 CHOPHEN CHOPHEN 0000 |                |         |          |         |           |        |          |          |          |          |          |          |          |          |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-63: PMD REGISTER MAP FOR dsPIC33FJ64GS606 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|--------|--------|--------|-------|--------|-------|---------------|

| PMD1         | 0770        | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | -      | I2C1MD | U2MD  | U1MD   | SPI2MD | SPI1MD | —     | C1MD   | ADCMD | 0000          |

| PMD2         | 0772        | -      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _      |        | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3         | 0774        | _      | _      | _      | _      | -      | CMPMD  | _      | _      | _      | —     | QEI2MD | _      | —      | —     | I2C2MD | —     | 0000          |

| PMD4         | 0776        | -      |        | —      | -      |        | _      |        |        | _      | —     | _      | _      | REFOMD | _     |        | —     | 0000          |

| PMD6         | 077A        | -      |        | PWM6MD | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD | _      | —     | _      | _      | —      | _     |        | —     | 0000          |

| PMD7         | 077C        | _      | _      | _      | -      | CMP4MD | CMP3MD | CMP2MD | CMP1MD | _      | _     | _      | _      | _      | _     | _      | _     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-64: PMD REGISTER MAP FOR dsPIC33FJ32GS606 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|--------|--------|--------|-------|--------|-------|---------------|

| PMD1         | 0770        | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  |        | I2C1MD | U2MD  | U1MD   | SPI2MD | SPI1MD |       | _      | ADCMD | 0000          |

| PMD2         | 0772        | -      | -      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _      | _      | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3         | 0774        | -      | -      | _      | _      | _      | CMPMD  | _      | _      | _      | _     | QEI2MD | _      | _      | _     | I2C2MD | _     | 0000          |

| PMD4         | 0776        | -      | -      | _      | _      | _      | _      | _      | _      | _      | _     | _      | _      | REFOMD | _     | _      | _     | 0000          |

| PMD6         | 077A        | -      | -      | PWM6MD | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD | _      | _     | _      | _      | _      | _     | _      | _     | 0000          |

| PMD7         | 077C        | _      | _      |        | —      | CMP4MD | CMP3MD | CMP2MD | CMP1MD | _      | —     | —      | _      | _      | _     | _      |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-65: PMD REGISTER MAP FOR dsPIC33FJ32GS406 AND dsPIC33FJ64GS406 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|--------|--------|--------|-------|--------|-------|---------------|

| PMD1         | 0770        | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD   | SPI2MD | SPI1MD | _     | _      | ADCMD | 0000          |

| PMD2         | 0772        | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | —      | _     | —      | -      | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3         | 0774        | _      | _      | _      | _      | _      | _      | -      | _      | —      | _     | QEI2MD | -      | _      | _     | I2C2MD | _     | 0000          |

| PMD4         | 0776        | _      | _      | _      | _      | _      | _      | -      | _      | —      | _     | —      | -      | REFOMD | _     | _      | _     | 0000          |

| PMD6         | 077A        | _      |        | PWM6MD | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD | —      | _     | _      | _      |        | _     |        | _     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 7-13: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | OC1IE: Output Compare Channel 1 Interrupt Enable bit |

|-------|------------------------------------------------------|

|       | 1 = Interrupt request is enabled                     |

|       | 0 = Interrupt request is not enabled                 |

| bit 1 | IC1IE: Input Capture Channel 1 Interrupt Enable bit  |

|       | 1 = Interrupt request is enabled                     |

|       | 0 = Interrupt request is not enabled                 |

| bit 0 | INTOIE: External Interrupt 0 Enable bit              |

|       | 1 = Interrupt request is enabled                     |

0 = Interrupt request is not enabled

© 2009-2014 Microchip Technology Inc.

| U-0              | R/W-1                          | R/W-0                                  | R/W-0            | U-0             | R/W-1           | R/W-0           | R/W-0   |

|------------------|--------------------------------|----------------------------------------|------------------|-----------------|-----------------|-----------------|---------|

| _                | U1RXIP2                        | U1RXIP1                                | U1RXIP0          | _               | SPI1IP2         | SPI1IP1         | SPI1IP0 |

| oit 15           |                                | -                                      |                  |                 | -               |                 | bit     |

|                  |                                |                                        |                  |                 |                 |                 |         |

| U-0              | R/W-1                          | R/W-0                                  | R/W-0            | U-0             | R/W-1           | R/W-0           | R/W-0   |

|                  | SPI1EIP2                       | SPI1EIP1                               | SPI1EIP0         | —               | T3IP2           | T3IP1           | T3IP0   |

| bit 7            |                                |                                        |                  |                 |                 |                 | bit     |

| Legend:          |                                |                                        |                  |                 |                 |                 |         |

| R = Readab       | le bit                         | W = Writable                           | bit              | U = Unimple     | mented bit, rea | d as '0'        |         |

| -n = Value a     | t POR                          | '1' = Bit is set                       |                  | '0' = Bit is cl | eared           | x = Bit is unkr | nown    |

|                  |                                |                                        |                  |                 |                 |                 |         |

| bit 15           | -                              | ted: Read as '                         |                  |                 |                 |                 |         |

| bit 14-12        |                                | -: UART1 Rece                          |                  |                 |                 |                 |         |

|                  | 111 = Interru                  | pt is Priority 7 (                     | nighest priorit  | y interrupt)    |                 |                 |         |

|                  | •                              |                                        |                  |                 |                 |                 |         |

|                  | •                              |                                        |                  |                 |                 |                 |         |

|                  | 001 = Interru<br>000 = Interru | pt is Priority 1<br>pt source is dis   | abled            |                 |                 |                 |         |

| bit 11           | Unimplemen                     | ted: Read as '                         | 0'               |                 |                 |                 |         |

| bit 10-8         | SPI1IP<2:0>:                   | SPI1 Event In                          | terrupt Priority | / bits          |                 |                 |         |

|                  |                                | pt is Priority 7 (                     |                  |                 |                 |                 |         |

|                  | •                              |                                        |                  |                 |                 |                 |         |

|                  | •                              |                                        |                  |                 |                 |                 |         |

|                  | 001 = Interru                  | pt is Priority 1<br>pt source is dis   | ablad            |                 |                 |                 |         |

| hit 7            |                                |                                        |                  |                 |                 |                 |         |

| bit 7<br>bit 6-4 | -                              | ted: Read as '<br>>: SPI1 Error li     |                  | v hite          |                 |                 |         |

| DIL 0-4          |                                | >: SPIT Error II<br>pt is Priority 7 ( | •                |                 |                 |                 |         |

|                  | •                              |                                        | ingriest priorit | y interrupt)    |                 |                 |         |

|                  | •                              |                                        |                  |                 |                 |                 |         |

|                  | •                              |                                        |                  |                 |                 |                 |         |

|                  | 001 = Interru                  | pt is Priority 1<br>pt source is dis   | ahled            |                 |                 |                 |         |

| bit 3            |                                | ted: Read as '                         |                  |                 |                 |                 |         |

| bit 2-0          | -                              | imer3 Interrupt                        |                  |                 |                 |                 |         |

|                  |                                | pt is Priority 7 (                     | -                | v interrunt)    |                 |                 |         |

|                  | •                              | prist nonty / (                        | ingricot priorit | y interrupty    |                 |                 |         |

|                  | •                              |                                        |                  |                 |                 |                 |         |

|                  | •                              | nt in Drinnits 4                       |                  |                 |                 |                 |         |

|                  | 001 = Interru                  | pt is Priority 1<br>pt source is dis   | ahled            |                 |                 |                 |         |

|                  |                                |                                        |                  |                 |                 |                 |         |

## REGISTER 7-23: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0          | R/W-1               | R/W-0                                | R/W-0             | U-0               | R/W-1             | R/W-0           | R/W-0    |

|--------------|---------------------|--------------------------------------|-------------------|-------------------|-------------------|-----------------|----------|

| _            | CNIP2               | CNIP1                                | CNIP0             | —                 | AC1IP2            | AC1IP1          | AC1IP0   |

| bit 15       |                     |                                      |                   |                   |                   |                 | bit      |

| U-0          | R/W-1               | R/W-0                                | R/W-0             | U-0               | R/W-1             | R/W-0           | R/W-0    |

| _            | MI2C1IP2            | MI2C1IP1                             | MI2C1IP0          | _                 | SI2C1IP2          | SI2C1IP1        | SI2C1IP0 |

| bit 7        |                     |                                      |                   |                   |                   |                 | bit      |

| Legend:      |                     |                                      |                   |                   |                   |                 |          |

| R = Readab   | le bit              | W = Writable                         | bit               | U = Unimple       | emented bit, read | t as '0'        |          |

| -n = Value a |                     | '1' = Bit is set                     |                   | '0' = Bit is cl   |                   | x = Bit is unkr | nown     |

|              |                     |                                      |                   |                   |                   |                 |          |

| bit 15       | Unimplemen          | ted: Read as '                       | 0'                |                   |                   |                 |          |

| bit 14-12    | CNIP<2:0>: (        | Change Notific                       | ation Interrupt   | Priority bits     |                   |                 |          |

|              | 111 = Interru       | pt is Priority 7                     | (highest priorit  | y interrupt)      |                   |                 |          |

|              | •                   |                                      |                   |                   |                   |                 |          |

|              | •                   |                                      |                   |                   |                   |                 |          |

|              | 001 = Interru       | pt is Priority 1                     |                   |                   |                   |                 |          |

|              | 000 = Interru       | pt source is dis                     | sabled            |                   |                   |                 |          |

| bit 11       | Unimplemen          | ted: Read as '                       | 0'                |                   |                   |                 |          |

| bit 10-8     | AC1IP<2:0>:         | Analog Comp                          | arator 1 Interro  | upt Priority bite | S                 |                 |          |

|              | 111 = Interru       | pt is Priority 7                     | (highest priorit  | y interrupt)      |                   |                 |          |

|              | •                   |                                      |                   |                   |                   |                 |          |

|              | •                   |                                      |                   |                   |                   |                 |          |

|              |                     | pt is Priority 1<br>pt source is dis | sabled            |                   |                   |                 |          |

| bit 7        | Unimplemen          | ted: Read as '                       | 0'                |                   |                   |                 |          |

| bit 6-4      | MI2C1IP<2:0         | >: I2C1 Maste                        | r Events Interr   | upt Priority bit  | ts                |                 |          |

|              | 111 = Interru       | pt is Priority 7                     | (highest priorit  | y interrupt)      |                   |                 |          |

|              | •                   |                                      |                   |                   |                   |                 |          |

|              | •                   |                                      |                   |                   |                   |                 |          |

|              |                     | pt is Priority 1<br>pt source is dis | sabled            |                   |                   |                 |          |

| bit 3        |                     | ited: Read as '                      |                   |                   |                   |                 |          |

| bit 2-0      | -                   | >: I2C1 Slave I                      |                   | ot Priority hits  |                   |                 |          |

|              |                     | pt is Priority 7                     |                   | -                 |                   |                 |          |

|              | •                   | prior nonty i                        | (ingriced priorit | y monuply         |                   |                 |          |

|              | •                   |                                      |                   |                   |                   |                 |          |

|              |                     |                                      |                   |                   |                   |                 |          |

|              | •<br>001 - Intorre: | pt is Priority 1                     |                   |                   |                   |                 |          |

## REGISTER 7-25: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

# REGISTER 8-5: DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|----------------------|-----------------|-----------------|-------|

|                 |       |                  | PAD<  | 15:8> <b>(2)</b>     |                 |                 |       |

| bit 15          |       |                  |       |                      |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  |       | <7:0> <sup>(2)</sup> |                 |                 |       |

| bit 7           |       |                  |       |                      |                 |                 | bit 0 |

| Legend:         |       |                  |       |                      |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimpler         | nented bit, rea | ıd as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle     | ared            | x = Bit is unkr | nown  |

bit 15-0 PAD<15:0>: Peripheral Address Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** See Table 8-1 for a complete list of peripheral addresses.

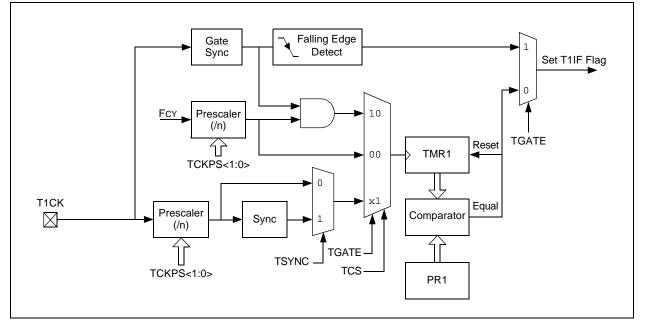

## 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as a time counter for the Real-Time Clock (RTC), or operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated from the low-power 32.767 kHz crystal oscillator available on the device.

- Can be operated in Asynchronous Counter mode from an external clock source.

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler.

The unique features of Timer1 allow it to be used for Real-Time Clock (RTC) applications. A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit: TCS (T1CON<1>)

- Timer Synchronization Control bit: TSYNC (T1CON<2>)

- Timer Gate Control bit: TGATE (T1CON<6>)

The timer control bit settings for different operating modes are given in the Table 12-1.

### TABLE 12-1: TIMER MODE SETTINGS

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

NOTES:

NOTES:

### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | $1 = U \mathbf{x} \mathbf{R} \mathbf{X}$ Idle state is '0'                                                                                                                         |

|         | 0 = UxRX Idle state is '1'                                                                                                                                                         |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | 11 = 9-bit data, no parity                                                                                                                                                         |

|         | 10 = 8-bit data, odd parity                                                                                                                                                        |

|         | 01 = 8-bit data, even parity                                                                                                                                                       |

|         | 00 = 8-bit data, no parity                                                                                                                                                         |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                      |

|         | 1 = Two Stop bits                                                                                                                                                                  |

|         | 0 = One Stop bit                                                                                                                                                                   |

| Note 1: | Refer to "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual" for information or                                                                                        |

- enabling the UART module for receive or transmit operation. That section of the manual is available on the Microchip web site: www.microchip.com.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

## REGISTER 21-17: CxRXFnEID: ECANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | EID<  | 15:8> |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|        |       |       | EID<  | <7:0> |       |       |       |

| bit 7  |       |       |       |       |       |       | bit ( |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

## REGISTER 21-18: CxFMSKSEL1: ECANx FILTER 7-0 MASK SELECTION REGISTER 1

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| F7MSK1 | F7MSK0 | F6MSK1 | F6MSK0 | F5MSK1 | F5MSK0 | F4MSK1 | F4MSK0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| F3MSK1 | F3MSK0 | F2MSK1 | F2MSK0 | F1MSK1 | F1MSK0 | F0MSK1 | F0MSK1 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | <b>F7MSK&lt;1:0&gt;:</b> Mask Source for Filter 7 bits<br>11 = Reserved<br>10 = Acceptance Mask 2 registers contain mask<br>01 = Acceptance Mask 1 registers contain mask<br>00 = Acceptance Mask 0 registers contain mask |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-12 | F6MSK<1:0>: Mask Source for Filter 6 bits (same values as bits<15:14>)                                                                                                                                                     |

| bit 11-10 | F5MSK<1:0>: Mask Source for Filter 5 bits (same values as bits<15:14>)                                                                                                                                                     |

| bit 9-8   | F4MSK<1:0>: Mask Source for Filter 4 bits (same values as bits<15:14>)                                                                                                                                                     |

| bit 7-6   | F3MSK<1:0>: Mask Source for Filter 3 bits (same values as bits<15:14>)                                                                                                                                                     |

| bit 5-4   | F2MSK<1:0>: Mask Source for Filter 2 bits (same values as bits<15:14>)                                                                                                                                                     |

| bit 3-2   | F1MSK<1:0>: Mask Source for Filter 1 bits (same values as bits<15:14>)                                                                                                                                                     |

| bit 1-0   | F0MSK<1:0>: Mask Source for Filter 0 bits (same values as bits<15:14>)                                                                                                                                                     |

© 2009-2014 Microchip Technology Inc.

# REGISTER 21-26: CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER (m = 0, 2, 4, 6; n = 1, 3, 5, 7)

|                 | (111 – 0                                                                     |                                       |                       |                         |                      |                 |                |  |  |

|-----------------|------------------------------------------------------------------------------|---------------------------------------|-----------------------|-------------------------|----------------------|-----------------|----------------|--|--|

| R/W-0           | R-0                                                                          | R-0                                   | R-0                   | R/W-0                   | R/W-0                | R/W-0           | R/W-0          |  |  |

| TXENn           | TXABTn                                                                       | TXLARBn                               | TXERRn                | TXREQn                  | RTRENn               | TXnPRI1         | TXnPRI0        |  |  |

| bit 15          |                                                                              |                                       |                       |                         |                      |                 | bit 8          |  |  |

| R/W-0           | R-0                                                                          | R-0                                   | R-0                   | R/W-0                   | R/W-0                | R/W-0           | R/W-0          |  |  |

| TXENm           | TXABTm <sup>(1)</sup>                                                        | TXLARBm <sup>(1)</sup>                | TXERRm <sup>(1)</sup> | TXREQm                  | RTRENm               | TXmPRI1         | TXmPRI0        |  |  |

| bit 7           |                                                                              |                                       |                       |                         |                      |                 | bit            |  |  |

| Legend:         |                                                                              |                                       |                       |                         |                      |                 |                |  |  |

| R = Readable    | bit                                                                          | W = Writable                          | bit                   | U = Unimpler            | mented bit, read     | d as '0'        |                |  |  |

| -n = Value at F | POR                                                                          | '1' = Bit is set                      |                       | '0' = Bit is cle        | ared                 | x = Bit is unkr | nown           |  |  |

|                 |                                                                              |                                       |                       |                         |                      |                 |                |  |  |

| bit 15-8        |                                                                              | n for bits<7:0>,                      |                       | er n                    |                      |                 |                |  |  |

| bit 7           | TXENm: TX/I                                                                  | RX Buffer Seleo                       | ction bit             |                         |                      |                 |                |  |  |

|                 |                                                                              | Bn is a transmi<br>Bn is a receive    |                       |                         |                      |                 |                |  |  |

| bit 6           |                                                                              |                                       |                       |                         |                      |                 |                |  |  |

| Sit 0           | <b>TXABTm:</b> Message Aborted bit <sup>(1)</sup><br>1 = Message was aborted |                                       |                       |                         |                      |                 |                |  |  |

|                 |                                                                              | completed tran                        | smission succ         | essfully                |                      |                 |                |  |  |

| bit 5           |                                                                              | Message Lost A                        |                       |                         |                      |                 |                |  |  |

|                 |                                                                              | lost arbitration did not lose arl     |                       |                         |                      |                 |                |  |  |

| bit 4           | TXERRm: Er                                                                   | ror Detected D                        | uring Transmis        | sion bit <sup>(1)</sup> |                      |                 |                |  |  |

|                 |                                                                              | or occurred whi<br>or did not occu    |                       |                         |                      |                 |                |  |  |

| bit 3           | TXREQm: M                                                                    | essage Send re                        | equest bit            |                         |                      |                 |                |  |  |

|                 |                                                                              | that a message<br>e bit to '0'; while |                       |                         | clears when the bort | e message is su | ccessfully ser |  |  |

| bit 2           | RTRENm: Au                                                                   | uto-Remote Tra                        | nsmit Enable l        | bit                     |                      |                 |                |  |  |

|                 |                                                                              | emote transmit<br>emote transmit      |                       |                         |                      |                 |                |  |  |

| bit 1-0         | TXmPRI<1:0                                                                   | >: Message Tra                        | ansmission Pri        | ority bits              |                      |                 |                |  |  |

|                 |                                                                              | message priori                        |                       |                         |                      |                 |                |  |  |

**Note 1:** This bit is cleared when TXREQm is set.

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

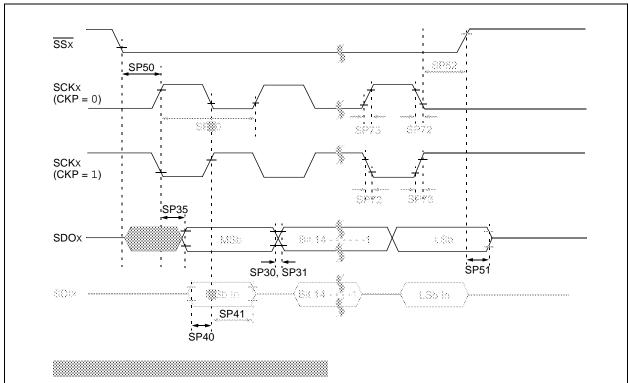

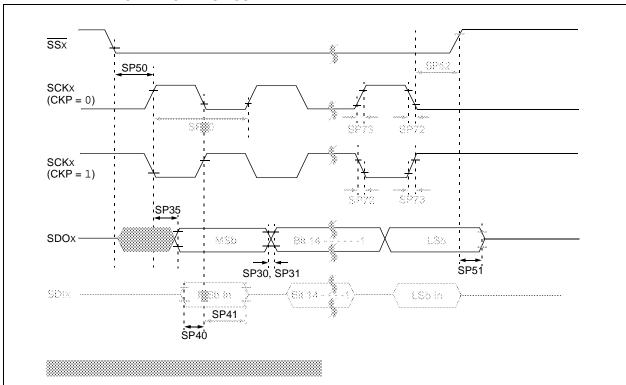

FIGURE 27-17: SPIx SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

FIGURE 27-18: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

# TABLE 27-37:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       |                       | Standard Op<br>(unless othe<br>Operating ter                 | erwise st    | t <b>ated)</b><br>e -40° | C ≤ TA ≤ | <b>IV to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |                                      |

|--------------|-----------------------|--------------------------------------------------------------|--------------|--------------------------|----------|------------------------------------------------------------------|--------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                | Min          | Тур <sup>(2)</sup>       | Max      | Units                                                            | Conditions                           |

| SP70         | TscP                  | Maximum SCKx Input Frequency                                 | —            | _                        | 11       | MHz                                                              | See Note 3                           |

| SP72         | TscF                  | SCKx Input Fall Time                                         | —            |                          |          | ns                                                               | See Parameter DO32 and <b>Note 4</b> |

| SP73         | TscR                  | SCKx Input Rise Time                                         | _            |                          |          | ns                                                               | See Parameter DO31 and <b>Note 4</b> |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                   | _            |                          |          | ns                                                               | See Parameter DO32 and <b>Note 4</b> |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                   | —            | _                        | _        | ns                                                               | See Parameter DO31 and <b>Note 4</b> |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —            | 6                        | 20       | ns                                                               |                                      |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30           |                          |          | ns                                                               |                                      |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30           |                          |          | ns                                                               |                                      |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30           |                          |          | ns                                                               |                                      |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120          | _                        | —        | ns                                                               |                                      |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10           | _                        | 50       | ns                                                               | See Note 4                           |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40 | —                        |          | ns                                                               | See Note 4                           |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock, generated by the master, must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | Ν        | <b>ILLIMETER</b> | S    |  |

|------------------------|------------------|----------|------------------|------|--|

| Dimensior              | Dimension Limits |          |                  |      |  |

| Number of Pins         | Ν                |          | 64               |      |  |

| Pitch                  | е                |          | 0.50 BSC         |      |  |

| Overall Height         | Α                | 0.80     | 0.90             | 1.00 |  |

| Standoff               | A1               | 0.00     | 0.02             | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF |                  |      |  |

| Overall Width          | E                |          | 9.00 BSC         |      |  |

| Exposed Pad Width      | E2               | 7.05     | 7.15             | 7.50 |  |

| Overall Length         | D                |          | 9.00 BSC         |      |  |

| Exposed Pad Length     | D2               | 7.05     | 7.15             | 7.50 |  |

| Contact Width          | b                | 0.18     | 0.25             | 0.30 |  |

| Contact Length         | L                | 0.30     | 0.40             | 0.50 |  |

| Contact-to-Exposed Pad | K                | 0.20     | -                | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-149C Sheet 2 of 2

NOTES: