Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                             |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 50 MIPs                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, QEI, POR, PWM, WDT                                    |

| Number of I/O              | 85                                                                                 |

| Program Memory Size        | 64KB (64K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 9K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 24x10b; D/A 1x10b                                                              |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-TQFP                                                                           |

| Supplier Device Package    | 100-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs610t-50i-pt |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

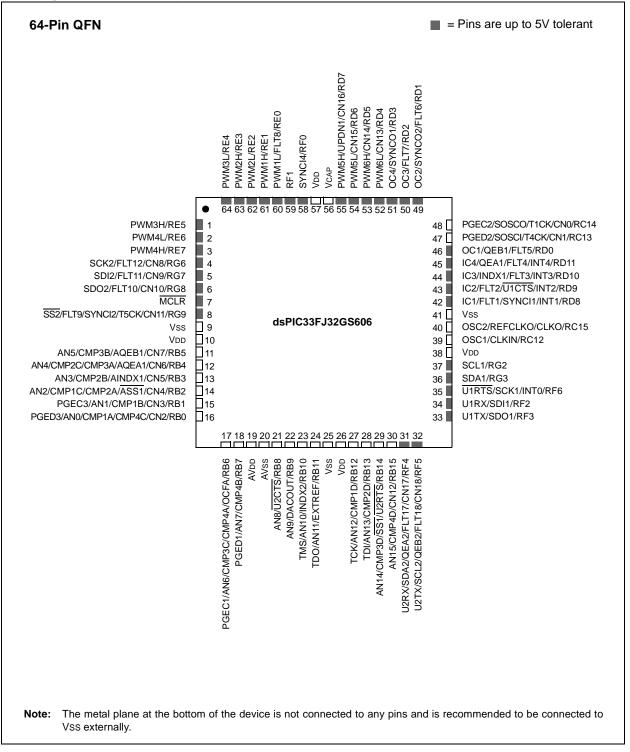

#### Pin Diagrams (Continued)

### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest sections in the "dsPIC33/PIC24 Family Reference Manual", which are available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

This document contains device-specific information for the following dsPIC33F Digital Signal Controller (DSC) devices:

- dsPIC33FJ32GS406

- dsPIC33FJ32GS606

- dsPIC33FJ32GS608

- dsPIC33FJ32GS610

- dsPIC33FJ64GS406

- dsPIC33FJ64GS606

- dsPIC33FJ64GS608

- dsPIC33FJ64GS610

The dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 families of devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance 16-bit microcontroller (MCU) architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the dsPIC33FJ32GS406/ 606/608/610 and dsPIC33FJ64GS406/606/608/610 devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

| File<br>Name | SFR<br>Addr | Bit 15   | Bit 14              | Bit 13   | Bit 12   | Bit 11   | Bit 10    | Bit 9         | Bit 8         | Bit 7 | Bit 6   | Bit 5    | Bit 4         | Bit 3     | Bit    | 2 Bit 1   | 1 Bit 0 | All<br>Reset |

|--------------|-------------|----------|---------------------|----------|----------|----------|-----------|---------------|---------------|-------|---------|----------|---------------|-----------|--------|-----------|---------|--------------|

| WREG0        | 0000        |          |                     |          |          |          | V         | /orking Regis | ter 0         |       |         |          |               |           |        |           |         | 0000         |

| WREG1        | 0002        |          |                     |          |          |          | V         | /orking Regis | ter 1         |       |         |          |               |           |        |           |         | 0000         |

| WREG2        | 0004        |          |                     |          |          |          | V         | /orking Regis | ter 2         |       |         |          |               |           |        |           |         | 0000         |

| WREG3        | 0006        |          |                     |          |          |          | V         | /orking Regis | ter 3         |       |         |          |               |           |        |           |         | 0000         |

| WREG4        | 8000        |          |                     |          |          |          | V         | /orking Regis | ter 4         |       |         |          |               |           |        |           |         | 0000         |

| WREG5        | 000A        |          |                     |          |          |          | V         | /orking Regis | ter 5         |       |         |          |               |           |        |           |         | 0000         |

| WREG6        | 000C        |          |                     |          |          |          | V         | /orking Regis | ter 6         |       |         |          |               |           |        |           |         | 0000         |

| WREG7        | 000E        |          |                     |          |          |          | V         | /orking Regis | ter 7         |       |         |          |               |           |        |           |         | 0000         |

| WREG8        | 0010        |          |                     |          |          |          | V         | /orking Regis | ter 8         |       |         |          |               |           |        |           |         | 0000         |

| WREG9        | 0012        |          |                     |          |          |          | V         | /orking Regis | ter 9         |       |         |          |               |           |        |           |         | 0000         |

| WREG10       | 0014        |          |                     |          |          |          | W         | orking Regist | er 10         |       |         |          |               |           |        |           |         | 0000         |

| WREG11       | 0016        |          |                     |          |          |          | W         | orking Regist | er 11         |       |         |          |               |           |        |           |         | 0000         |

| WREG12       | 0018        |          |                     |          |          |          | W         | orking Regist | er 12         |       |         |          |               |           |        |           |         | 0000         |

| WREG13       | 001A        |          | Working Register 13 |          |          |          |           |               |               |       |         |          |               | 0000      |        |           |         |              |

| WREG14       | 001C        |          | Working Register 14 |          |          |          |           |               |               |       |         |          |               |           | 0000   |           |         |              |

| WREG15       | 001E        |          |                     |          |          |          |           |               |               |       |         |          |               |           |        | 0800      |         |              |

| SPLIM        | 0020        |          |                     |          |          |          | Stack     | Pointer Limit | Register      |       |         |          |               |           |        |           |         | xxxx         |

| ACCAL        | 0022        |          |                     |          |          |          |           | ACCAL         |               |       |         |          |               |           |        |           |         | xxxx         |

| ACCAH        | 0024        |          |                     |          |          |          |           | ACCAH         |               |       |         |          |               |           |        |           |         | xxxx         |

| ACCAU        | 0026        | ACCA<39> | ACCA<39>            | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39>  | ACCA<39>      | ACCA<39>      |       |         |          | ACCA          | U         |        |           |         | xxxx         |

| ACCBL        | 0028        |          |                     |          |          |          |           | ACCBL         |               |       |         |          |               |           |        |           |         | xxxx         |

| ACCBH        | 002A        |          |                     |          |          |          |           | ACCBH         |               |       |         |          |               |           |        |           |         | xxxx         |

| ACCBU        | 002C        | ACCB<39> | ACCB<39>            | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39>  | ACCB<39>      | ACCB<39>      |       |         |          | ACCB          | U         |        |           |         | xxxx         |

| PCL          | 002E        |          |                     |          |          |          | Program ( | Counter Low I | Byte Register |       |         |          |               |           |        |           |         | 0000         |

| PCH          | 0030        |          | —                   | —        |          | —        | —         |               | —             |       |         | Program  | Counter Hig   | gh Byte I | Regist | er        |         | 0000         |

| TBLPAG       | 0032        |          | —                   | —        |          | —        | —         |               | —             |       |         | Table Pa | ge Address    | Pointer I | Regist | .er       |         | 0000         |

| PSVPAG       | 0034        | —        | —                   | —        |          | —        | —         |               | —             | F     | Program | Memory V | isibility Pag | e Addres  | s Poi  | nter Regi | ster    | 0000         |

| RCOUNT       | 0036        |          |                     |          |          |          | REPEAT    | Loop Counter  | er Register   |       |         |          |               |           |        |           |         | xxxx         |

| DCOUNT       | 0038        |          |                     |          |          |          |           | DCOUNT<15     | :0>           |       |         |          |               |           |        |           |         | xxxx         |

| DOSTARTL     | 003A        |          |                     |          |          |          | DOS       | TARTL<15:1>   |               |       |         |          |               |           |        |           | 0       | xxxx         |

| DOSTARTH     | 003C        | _        | _                   | —        | _        | —        | —         | —             | —             | -     | —       |          | DC            | STARTH    | 1<5:0: | >         |         | 00xx         |

| DOENDL       | 003E        |          |                     |          |          |          | DOE       | NDL<15:1>     |               |       |         |          |               |           |        |           | 0       | xxxx         |

| DOENDH       | 0040        | _        | —                   | —        | —        | —        | _         | —             | _             | —     | —       |          |               | DOEN      | ЭН     |           |         | 00xx         |

| SR           | 0042        | OA       | OB                  | SA       | SB       | OAB      | SAB       | DA            | DC            | IPL2  | IPL1    | IPL0     | RA            | N         | OV     | / Z       | С       | 0000         |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4-9: | INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ32GS608 (CONTINUED) |

|------------|--------------------------------------------------------------------|

|------------|--------------------------------------------------------------------|

|              |             |        |          |          |          |        |          |          |          |       | •         |           | -         |         |          |          |          |               |

|--------------|-------------|--------|----------|----------|----------|--------|----------|----------|----------|-------|-----------|-----------|-----------|---------|----------|----------|----------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14   | Bit 13   | Bit 12   | Bit 11 | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6     | Bit 5     | Bit 4     | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| IPC21        | 00CE        | _      | —        | —        | -        |        | —        | —        | -        | —     | ADCP12IP2 | ADCP12IP1 | ADCP12IP1 | —       | —        | _        | —        | 0040          |

| IPC23        | 00D2        | _      | PWM2IP2  | PWM2IP1  | PWM2IP0  | _      | PWM1IP2  | PWM1IP1  | PWM1IP0  | _     | _         | _         | _         | _       | _        | _        | _        | 4400          |

| IPC24        | 00D4        | _      | PWM6IP2  | PWM6IP1  | PWM6IP0  | -      | PWM5IP2  | PWM5IP1  | PWM5IP0  | _     | PWM4IP2   | PWM4IP1   | PWM4IP0   | —       | PWM3IP2  | PWM3IP1  | PWM3IP0  | 4444          |

| IPC25        | 00D6        | _      | AC2IP2   | AC2IP1   | AC2IP0   | -      | _        | _        | _        | _     | PWM8IP2   | PWM8IP1   | PWM8IP0   | —       | PWM7IP2  | PWM7IP1  | PWM7IP0  | 4044          |

| IPC26        | 00D8        | _      | —        | _        | _        | -      | _        | _        | _        | _     | AC4IP2    | AC4IP1    | AC4IP0    | —       | AC3IP2   | AC3IP1   | AC3IP0   | 0044          |

| IPC27        | 00DA        | _      | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | -      | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | _     | _         | _         | _         | —       | _        | _        | _        | 4400          |

| IPC28        | 00DC        | _      | ADCP5IP2 | ADCP5IP1 | ADCP5IP0 | -      | ADCP4IP2 | ADCP4IP1 | ADCP4IP0 | _     | ADCP3IP2  | ADCP3IP1  | ADCP3IP0  | —       | ADCP2IP2 | ADCP2IP1 | ADCP2IP0 | 4444          |

| IPC29        | 00DE        | _      |          | _        | _        | _      | _        | _        | _        | _     | ADCP7IP2  | ADCP7IP1  | ADCP7IP0  | _       | ADCP6IP2 | ADCP6IP1 | ADCP6IP0 | 0044          |

| INTTREG      | 00E0        | _      | _        | _        | _        | ILR3   | ILR2     | ILR1     | ILR0     | _     | VECNUM6   | VECNUM5   | VECNUM4   | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4      | 4-21        | : HIG             | SH-SPE       | ED PW   | /M GEI  | NERATO    | R 5 REG   | SISTER N  | IAP       |           |         |          |          |          |          |          |          |               |

|--------------|-------------|-------------------|--------------|---------|---------|-----------|-----------|-----------|-----------|-----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15            | Bit 14       | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7     | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| PWMCON5      | 04A0        | FLTSTAT           | CLSTAT       | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS      | DTC1      | DTC0    | DTCP     | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON5       | 04A2        | PENH              | PENL         | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL    | OVRDAT1   | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON5      | 04A4        | IFLTMOD           | CLSRC4       | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD     | FLTSRC4   | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC5         | 04A6        |                   |              |         |         |           |           |           | PDC       | 5<15:0>   |         |          |          |          |          |          |          | 0000          |

| PHASE5       | 04A8        |                   |              |         |         |           |           |           | PHAS      | E5<15:0>  |         |          |          |          |          |          |          | 0000          |

| DTR5         | 04AA        |                   | DTR5<13:0> 0 |         |         |           |           |           |           |           |         |          | 0000     |          |          |          |          |               |

| ALTDTR5      | 04AA        | — — ALTDTR5<13:0> |              |         |         |           |           |           |           |           |         |          | 0000     |          |          |          |          |               |

| SDC5         | 04AE        |                   |              |         |         |           |           |           | SDC       | 5<15:0>   |         |          |          |          |          |          |          | 0000          |

| SPHASE5      | 04B0        |                   |              |         |         |           |           |           | SPHAS     | SE5<15:0> |         |          |          |          |          |          |          | 0000          |

| TRIG5        | 04B2        |                   |              |         |         |           |           | TRGCMP<12 | 2:0>      |           |         |          |          |          | _        | _        | _        | 0000          |

| TRGCON5      | 04B4        | TRGDIV3           | TRGDIV2      | TRGDIV1 | TRGDIV0 |           | -         | _         | _         | DTM       | -       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG5       | 04B6        |                   |              |         |         |           |           | STRGCMP<1 | 2:0>      |           |         |          |          |          | _        | _        | _        | 0000          |

| PWMCAP5      | 04B8        |                   |              |         |         |           |           | PWMCAP<1  | 2:0>      |           |         |          |          |          | _        | _        | _        | 0000          |

| LEBCON5      | 04BA        | PHR               | PHF          | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | _         | _         | _         | _       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY5      | 04BC        |                   | _            | _       | —       |           |           |           | L         | EB<8:0>   |         |          |          |          | _        | _        | —        | 0000          |

| AUXCON5      | 04BE        | HRPDIS            | HRDDIS       | _       | —       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 | _         | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-28: UART1 REGISTER MAP

| File Name                                | SFR<br>Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7    | Bit 6    | Bit 5 | Bit 4       | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|------------------------------------------|--------------|----------|--------|----------|--------|--------|--------|-------|------------------------|----------|----------|-------|-------------|---------|--------|--------|-------|---------------|

| U1MODE                                   | 0220         | UARTEN   | —      | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0                   | WAKE     | LPBACK   | ABAUD | URXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA                                    | 0222         | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISEL1 | URXISEL0 | ADDEN | RIDLE       | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG                                  | 0224         | _        | —      | _        | _      | _      | —      | —     |                        |          |          | UART1 | Transmit Re | egister |        |        |       | xxxx          |

| U1RXREG                                  | 0226         | _        | —      | _        | _      | _      | —      | _     | UART1 Receive Register |          |          |       |             |         |        |        | 0000  |               |

| U1BRG 0228 Baud Rate Generator Prescaler |              |          |        |          |        |        |        |       |                        |          |          | 0000  |             |         |        |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-29: UART2 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15                        | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7    | Bit 6    | Bit 5 | Bit 4      | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|-------------------------------|--------|----------|--------|--------|--------|-------|------------------------|----------|----------|-------|------------|---------|--------|--------|-------|---------------|

| U2MODE       | 0230        | UARTEN                        | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                   | WAKE     | LPBACK   | ABAUD | URXINV     | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232        | UTXISEL1                      | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISEL1 | URXISEL0 | ADDEN | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234        | _                             | _      | _        | _      | —      | _      | _     |                        |          |          | UART2 | Transmit R | egister |        |        |       | xxxx          |

| U2RXREG      | 0236        | _                             | _      | _        | _      | —      | _      | _     | UART2 Receive Register |          |          |       |            |         |        | 0000   |       |               |

| U2BRG        | 0238        | Baud Rate Generator Prescaler |        |          |        |        |        |       |                        |          |          |       |            | 0000    |        |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | SFR<br>Addr | Bit 15             | Bit 14 | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6  | Bit 5   | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     | All<br>Resets |

|--------------|-------------|--------------------|--------|--------|----------|----------|----------|----------|----------|-------------|--------|---------|-----------|-----------|-----------|-----------|-----------|---------------|

| ADCON        | 0300        | ADON               | _      | ADSIDL | SLOWCLK  | _        | GSWTRG   | -        | FORM     | EIE         | ORDER  | SEQSAMP | ASYNCSAMP | —         | ADCS2     | ADCS1     | ADCS0     | 0003          |

| ADPCFG       | 0302        |                    |        |        |          |          |          |          | P        | CFG<15:0    | >      |         |           | •         | •         |           | •         | 0000          |

| ADPCFG2      | 0304        | _                  | _      | —      | _        | _        | _        | _        | _        | —           | _      | —       | _         | _         | _         | PCFG      | <17:16>   | 0000          |

| ADSTAT       | 0306        | —                  | —      | _      | P12RDY   | _        | _        | _        | P8RDY    | P7RDY       | P6RDY  | P5RDY   | P4RDY     | P3RDY     | P2RDY     | P1RDY     | PORDY     | 0000          |

| ADBASE       | 0308        |                    |        |        |          |          |          |          | ADBASE<  | :15:1>      |        |         |           |           |           |           | _         | 0000          |

| ADCPC0       | 030A        | IRQEN1             | PEND1  | SWTRG1 | TRGSRC14 | TRGSRC13 | TRGSRC12 | TRGSRC11 | TRGSRC10 | IRQEN0      | PEND0  | SWTRG0  | TRGSRC04  | TRGSRC03  | TRGSRC02  | TRGSRC01  | TRGSRC00  | 0000          |

| ADCPC1       | 030C        | IRQEN3             | PEND3  | SWTRG3 | TRGSRC34 | TRGSRC33 | TRGSRC32 | TRGSRC31 | TRGSRC30 | IRQEN2      | PEND2  | SWTRG2  | TRGSRC24  | TRGSRC23  | TRGSRC22  | TRGSRC21  | TRGSRC20  | 0000          |

| ADCPC2       | 030E        | IRQEN5             | PEND5  | SWTRG5 | TRGSRC54 | TRGSRC53 | TRGSRC52 | TRGSRC51 | TRGSRC50 | IRQEN4      | PEND4  | SWTRG4  | TRGSRC44  | TRGSRC43  | TRGSRC42  | TRGSRC41  | TRGSRC40  | 0000          |

| ADCPC3       | 0310        | IRQEN7             | PEND7  | SWTRG7 | TRGSRC74 | TRGSRC73 | TRGSRC72 | TRGSRC71 | TRGSRC70 | IRQEN6      | PEND6  | SWTRG6  | TRGSRC64  | TRGSRC63  | TRGSRC62  | TRGSRC61  | TRGSRC640 | 0000          |

| ADCPC4       | 0312        | -                  |        |        | _        | _        | -        | _        | _        | IRQEN8      | PEND8  | SWTRG8  | TRGSRC84  | TRGSRC83  | TRGSRC82  | TRGSRC81  | TRGSRC80  | 0000          |

| ADCPC6       | 0316        | -                  |        |        | _        | _        | -        | _        | _        | IRQEN12     | PEND12 | SWTRG12 | TRGSRC124 | TRGSRC123 | TRGSRC122 | TRGSRC121 | TRGSRC120 | 0000          |

| ADCBUF0      | 0340        |                    |        |        |          |          |          |          | ADO      | C Data Buff | er 0   |         |           |           |           |           |           | xxxx          |

| ADCBUF1      | 0342        |                    |        |        |          |          |          |          | ADO      | C Data Buff | er 1   |         |           |           |           |           |           | xxxx          |

| ADCBUF2      | 0344        |                    |        |        |          |          |          |          | ADO      | C Data Buff | er 2   |         |           |           |           |           |           | xxxx          |

| ADCBUF3      | 0346        |                    |        |        |          |          |          |          | ADO      | C Data Buff | er 3   |         |           |           |           |           |           | xxxx          |

| ADCBUF4      | 0348        |                    |        |        |          |          |          |          | ADO      | C Data Buff | er 4   |         |           |           |           |           |           | xxxx          |

| ADCBUF5      | 034A        |                    |        |        |          |          |          |          | ADO      | C Data Buff | er 5   |         |           |           |           |           |           | xxxx          |

| ADCBUF6      | 034C        |                    |        |        |          |          |          |          | ADO      | C Data Buff | er 6   |         |           |           |           |           |           | xxxx          |

| ADCBUF7      | 034E        |                    |        |        |          |          |          |          | ADO      | C Data Buff | er 7   |         |           |           |           |           |           | xxxx          |

| ADCBUF8      | 0350        |                    |        |        |          |          |          |          | ADO      | C Data Buff | er 8   |         |           |           |           |           |           | xxxx          |

| ADCBUF9      | 0352        |                    |        |        |          |          |          |          | ADO      | C Data Buff | er 9   |         |           |           |           |           |           | xxxx          |

| ADCBUF10     | 0354        |                    |        |        |          |          |          |          | ADC      | Data Buffe  | er 10  |         |           |           |           |           |           | xxxx          |

| ADCBUF11     | 0356        |                    |        |        |          |          |          |          | ADC      | Data Buffe  | er 11  |         |           |           |           |           |           | xxxx          |

| ADCBUF12     | 0358        |                    |        |        |          |          |          |          | ADC      | Data Buffe  | er 12  |         |           |           |           |           |           | xxxx          |

| ADCBUF13     | 035A        |                    |        |        |          |          |          |          | ADC      | Data Buffe  | er 13  |         |           |           |           |           |           | xxxx          |

| ADCBUF14     | 035C        | ADC Data Buffer 14 |        |        |          |          |          |          |          |             |        |         | xxxx      |           |           |           |           |               |

| ADCBUF15     | 035E        |                    |        |        |          |          |          |          | ADC      | Data Buffe  | er 15  |         |           |           |           |           |           | xxxx          |

| ADCBUF16     | 0360        |                    |        |        |          |          |          |          | ADC      | Data Buffe  | er 16  |         |           |           |           |           |           | xxxx          |

| ADCBUF17     | 0362        |                    |        |        |          |          |          |          | ADC      | Data Buffe  | er 17  |         |           |           |           |           |           | xxxx          |

| ADCBUF24     | 0370        |                    |        |        |          |          |          |          | ADC      | Data Buffe  | er 24  |         |           |           |           |           |           | xxxx          |

| ADCBUF25     | 0372        |                    |        |        |          |          |          |          | ADC      | Data Buffe  | er 25  |         |           |           |           |           |           | xxxx          |

#### TABLE 4-33: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ32GS608 AND dsPIC33FJ64GS608 DEVICES

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| U-0          | U-0           | U-0                              | U-0           | U-0              | U-0              | U-0             | U-0     |

|--------------|---------------|----------------------------------|---------------|------------------|------------------|-----------------|---------|

| _            | —             | —                                | —             | _                | _                | _               | _       |

| bit 15       | ÷             |                                  |               |                  |                  |                 | bit 8   |

|              |               |                                  |               |                  |                  |                 |         |

| U-0          | U-0           | R/W-0                            | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| —            | —             | ADCP7IF                          | ADCP6IF       | ADCP5IF          | ADCP4IF          | ADCP3IF         | ADCP2IF |

| bit 7        |               |                                  |               |                  |                  |                 | bit C   |

|              |               |                                  |               |                  |                  |                 |         |

| Legend:      | 1 1 2         |                                  | 1.14          |                  |                  |                 |         |

| R = Readab   |               | W = Writable                     |               | •                | mented bit, read |                 |         |

| -n = Value a | t POR         | '1' = Bit is set                 |               | '0' = Bit is cle | ared             | x = Bit is unkr | iown    |

| bit 15-6     | Unimplomor    | nted: Read as '                  | 0'            |                  |                  |                 |         |

| bit 5        | -             |                                  |               | ntorrupt Elog S  | Yotuo hit        |                 |         |

| DIL D        |               | DC Pair 7 Conv<br>request has oc |               | nterrupt Flag S  |                  |                 |         |

|              |               | request has no                   |               |                  |                  |                 |         |

| bit 4        | ADCP6IF: A    | DC Pair 6 Conv                   | ersion Done I | nterrupt Flag S  | Status bit       |                 |         |

|              |               | request has oc                   |               |                  |                  |                 |         |

|              | •             | request has no                   |               |                  |                  |                 |         |

| bit 3        |               | DC Pair 5 Conv                   |               | nterrupt Flag S  | Status bit       |                 |         |

|              |               | request has oc<br>request has no |               |                  |                  |                 |         |

| bit 2        |               | DC Pair 4 Conv                   |               | nterrupt Flag S  | status bit       |                 |         |

|              |               | request has oc                   |               |                  |                  |                 |         |

|              |               | request has no                   |               |                  |                  |                 |         |

| bit 1        | ADCP3IF: AD   | DC Pair 3 Conv                   | ersion Done I | nterrupt Flag S  | status bit       |                 |         |

|              |               | request has oc                   |               |                  |                  |                 |         |

|              | -             | request has no                   |               |                  |                  |                 |         |

| bit 0        |               | DC Pair 2 Conv                   |               | nterrupt Flag S  | Status bit       |                 |         |

|              | •             | request has oc                   |               |                  |                  |                 |         |

|              | 0 = interrupt | request has no                   | loccurrea     |                  |                  |                 |         |

#### REGISTER 7-12: IFS7: INTERRUPT FLAG STATUS REGISTER 7

## dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| U-0          | U-0           | U-0                                 | U-0          | U-0              | R/W-0            | R/W-0            | U-0 |

|--------------|---------------|-------------------------------------|--------------|------------------|------------------|------------------|-----|

| _            | —             | _                                   | _            |                  | QEI1IE           | PSEMIE           | _   |

| bit 15       | ·             |                                     |              |                  |                  |                  | bit |

|              |               |                                     |              |                  |                  |                  |     |

| U-0          | R/W-0         | R/W-0                               | U-0          | U-0              | R/W-0            | R/W-0            | U-0 |

|              | INT4IE        | INT3IE                              |              | —                | MI2C2IE          | SI2C2IE          |     |

| bit 7        |               |                                     |              |                  |                  |                  | bit |

| Legend:      |               |                                     |              |                  |                  |                  |     |

| R = Readab   | le bit        | W = Writable                        | bit          | U = Unimpler     | mented bit, read | l as '0'         |     |

| -n = Value a | t POR         | '1' = Bit is set                    |              | '0' = Bit is cle |                  | x = Bit is unkno | own |

|              |               |                                     |              |                  |                  |                  |     |

| bit 15-11    | Unimplemen    | ted: Read as '                      | כ'           |                  |                  |                  |     |

| bit 10       | QEI1IE: QEI1  | 1 Event Interrup                    | t Enable bit |                  |                  |                  |     |

|              |               | request is enab                     |              |                  |                  |                  |     |

|              | •             | request is not e                    |              |                  |                  |                  |     |

| bit 9        |               | /M Special Ever                     |              | rupt Enable bit  | t                |                  |     |

|              |               | request is enab<br>request is not e |              |                  |                  |                  |     |

| bit 8-7      |               | ited: Read as '                     |              |                  |                  |                  |     |

| bit 6        | -             | rnal Interrupt 4                    |              |                  |                  |                  |     |

|              |               | request is enab                     |              |                  |                  |                  |     |

|              |               | request is not e                    |              |                  |                  |                  |     |

| bit 6        | INT3IE: Exte  | rnal Interrupt 3                    | Enable bit   |                  |                  |                  |     |

|              |               | request is enab                     |              |                  |                  |                  |     |

|              |               | request is not e                    |              |                  |                  |                  |     |

| bit 4-3      | -             | ted: Read as '                      |              |                  |                  |                  |     |

| bit 2        |               | 2 Master Even                       |              | nable bit        |                  |                  |     |

|              |               | request is enab<br>request is not e |              |                  |                  |                  |     |

| bit 1        | -             | 2 Slave Events                      |              | able bit         |                  |                  |     |

|              |               | request is enab                     | •            |                  |                  |                  |     |

|              | 0 = Interrupt |                                     |              |                  |                  |                  |     |

|              | 1             |                                     | liablea      |                  |                  |                  |     |

#### REGISTER 7-16: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

## dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

#### REGISTER 7-26: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| Legend: |     |     |     |     |         |         |         |

|---------|-----|-----|-----|-----|---------|---------|---------|

| bit 7   |     |     |     |     |         |         | bit C   |

| _       | —   | —   | _   | —   | INT1IP2 | INT1IP1 | INT1IP0 |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| bit 15  |     |     |     |     |         |         | bit 8   |

|         | —   | —   | —   | —   | —       | —       | —       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

#### bit 15-3 Unimplemented: Read as '0'

INT1IP<2:0>: External Interrupt 1 Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

bit 2-0

.

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### 7.4 Interrupt Setup Procedures

#### 7.4.1 INITIALIZATION

Complete the following steps to configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

| Note: | At a devic                                | e Rese | et, the | PC  | Cx reg | isters are |  |  |  |  |  |

|-------|-------------------------------------------|--------|---------|-----|--------|------------|--|--|--|--|--|

|       | initialized                               | such   | that    | all | user   | interrupt  |  |  |  |  |  |

|       | sources are assigned to Priority Level 4. |        |         |     |        |            |  |  |  |  |  |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 7.4.2 INTERRUPT SERVICE ROUTINE

The method used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (C or assembler) and the language development toolsuite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, program will re-enter the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.4.4 INTERRUPT DISABLE

The following steps outline the procedure to disable all user interrupts:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, EOh, with SRL.

To enable user interrupts, the POP instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of |

|-------|-----------------------------------------------|

|       | 7 or lower can be disabled. Trap sources      |

|       | (Level 8-Level 15) cannot be disabled.        |

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

| R/W-0           | U-0                                                                                                                                                                                              | R/W-0                                                                                                                                              | R/W-1, HC                   | R/W-0                     | R/W-0                          | R/W-0             | R/W-0           |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------|--------------------------------|-------------------|-----------------|--|--|--|

| I2CEN           | —                                                                                                                                                                                                | I2CSIDL                                                                                                                                            | SCLREL                      | IPMIEN                    | A10M                           | DISSLW            | SMEN            |  |  |  |

| bit 15          |                                                                                                                                                                                                  |                                                                                                                                                    |                             | I                         | •                              |                   | bit 8           |  |  |  |

|                 |                                                                                                                                                                                                  |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                                                            | R/W-0                                                                                                                                              | R/W-0, HC                   | R/W-0, HC                 | R/W-0, HC                      | R/W-0, HC         | R/W-0, HC       |  |  |  |

| GCEN            | STREN                                                                                                                                                                                            | ACKDT                                                                                                                                              | ACKEN                       | RCEN                      | PEN                            | RSEN              | SEN             |  |  |  |

| bit 7           |                                                                                                                                                                                                  |                                                                                                                                                    |                             |                           |                                | ·                 | bit (           |  |  |  |

|                 |                                                                                                                                                                                                  |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

| Legend:         |                                                                                                                                                                                                  | HC = Hardw                                                                                                                                         | are Clearable               | bit                       |                                |                   |                 |  |  |  |

| R = Readable    | bit                                                                                                                                                                                              | W = Writable                                                                                                                                       | e bit                       | U = Unimplem              | ented bit, read a              | is '0'            |                 |  |  |  |

| -n = Value at F | POR                                                                                                                                                                                              | '1' = Bit is se                                                                                                                                    | et                          | '0' = Bit is clea         | ared                           | x = Bit is unkno  | own             |  |  |  |

|                 |                                                                                                                                                                                                  |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

| bit 15          |                                                                                                                                                                                                  | Cx Enable bit                                                                                                                                      |                             |                           |                                |                   |                 |  |  |  |

|                 |                                                                                                                                                                                                  |                                                                                                                                                    |                             |                           | Ax and SCLx pin                |                   | bins            |  |  |  |

|                 |                                                                                                                                                                                                  |                                                                                                                                                    |                             | pins are contro           | lled by port funct             | ions              |                 |  |  |  |

| bit 14          | -                                                                                                                                                                                                | ented: Read                                                                                                                                        |                             |                           |                                |                   |                 |  |  |  |

| bit 13          |                                                                                                                                                                                                  | 2Cx Stop in Ic                                                                                                                                     |                             | an davias ante            |                                |                   |                 |  |  |  |

|                 |                                                                                                                                                                                                  |                                                                                                                                                    |                             | nen device ente<br>e mode | ers Idle mode                  |                   |                 |  |  |  |

| bit 12          |                                                                                                                                                                                                  | <ul> <li>0 = Continues module operation in Idle mode</li> <li>SCLREL: SCLx Release Control bit (when operating as I<sup>2</sup>C slave)</li> </ul> |                             |                           |                                |                   |                 |  |  |  |

|                 | 1 = Releases SCLx clock                                                                                                                                                                          |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

|                 | 0 = Holds SCLx clock low (clock stretch)                                                                                                                                                         |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

|                 | <u>If STREN = 1:</u>                                                                                                                                                                             |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

|                 | Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware is clear at beginning of slave transmission. Hardware is clear at end of slave reception. |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

|                 | If STREN =                                                                                                                                                                                       | -                                                                                                                                                  | 15111551011. 116            | iluwale is clear          | at end of slave                | eception.         |                 |  |  |  |

|                 |                                                                                                                                                                                                  |                                                                                                                                                    | can only write              | e '1' to release          | clock). Hardwar                | e is clear at beg | inning of slave |  |  |  |

|                 | transmissio                                                                                                                                                                                      | on.                                                                                                                                                | -                           |                           |                                | -                 | _               |  |  |  |

| bit 11          |                                                                                                                                                                                                  | • •                                                                                                                                                | •                           |                           | e (IPMI) Enable b              | it                |                 |  |  |  |

|                 |                                                                                                                                                                                                  |                                                                                                                                                    |                             | es are Acknow             | ledged                         |                   |                 |  |  |  |

|                 |                                                                                                                                                                                                  | ode is disable                                                                                                                                     |                             |                           |                                |                   |                 |  |  |  |

| bit 10          | A10M: 10-Bit Slave Address bit                                                                                                                                                                   |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

|                 | 1 = I2CxADD is a 10-bit slave address<br>0 = I2CxADD is a 7-bit slave address                                                                                                                    |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

| bit 9           | 0 = 12CXADD is a 7-bit slave address<br>DISSLW: Disable Slew Rate Control bit                                                                                                                    |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

|                 | 1 = Slew rate control is disabled                                                                                                                                                                |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

|                 | 0 = Slew ra                                                                                                                                                                                      | ate control is e                                                                                                                                   | enabled                     |                           |                                |                   |                 |  |  |  |

| bit 8           | SMEN: SMBus Input Levels bit                                                                                                                                                                     |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

|                 | 1 = Enables I/O pin thresholds compliant with SMBus specification                                                                                                                                |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

|                 | <ul> <li>0 = Disables SMBus input thresholds</li> <li>GCEN: General Call Enable bit (when operating as I<sup>2</sup>C<sup>™</sup> slave)</li> </ul>                                              |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

| bit 7           |                                                                                                                                                                                                  |                                                                                                                                                    | -                           |                           | -                              |                   |                 |  |  |  |

|                 | 1 = Enable<br>recept                                                                                                                                                                             |                                                                                                                                                    | ien a general               | call address is           | received in the la             | 2CXRSR (module    | e is enabled to |  |  |  |

|                 |                                                                                                                                                                                                  | al call addres                                                                                                                                     | s is disabled               |                           |                                |                   |                 |  |  |  |

|                 |                                                                                                                                                                                                  |                                                                                                                                                    |                             | it (when operat           | ting as I <sup>2</sup> C slave | )                 |                 |  |  |  |

| bit 6           | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as $I^2C$ slave)                                                                                                                     |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

| bit 6           | Used in conjunction with the SCLREL bit.                                                                                                                                                         |                                                                                                                                                    |                             |                           |                                |                   |                 |  |  |  |

| bit 6           | Used in co<br>1 = Enable                                                                                                                                                                         |                                                                                                                                                    | the SCLREL<br>receives cloc | bit.<br>k stretching      |                                |                   |                 |  |  |  |

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

NOTES:

| R/W-0                   | R/W-0        | R/W-0            | R/W-0           | R/W-0                                    | R/W-0            | R/W-0    | R/W-0   |

|-------------------------|--------------|------------------|-----------------|------------------------------------------|------------------|----------|---------|

| F15MSK1                 | F15MSK0      | F14MSK1          | F14MSK0         | F13MSK1                                  | F13MSK0          | F12MSK1  | F12MSK0 |

| bit 15                  |              |                  |                 |                                          |                  |          | bit 8   |

|                         |              |                  |                 |                                          |                  |          |         |

| R/W-0                   | R/W-0        | R/W-0            | R/W-0           | R/W-0                                    | R/W-0            | R/W-0    | R/W-0   |

| F11MSK1                 | F11MSK0      | F10MSK1          | F10MSK0         | F9MSK1                                   | F9MSK0           | F8MSK1   | F8MSK0  |

| bit 7                   |              |                  |                 |                                          |                  |          | bit 0   |

|                         |              |                  |                 |                                          |                  |          |         |

| Legend:                 |              |                  |                 |                                          |                  |          |         |

| R = Readable            | bit          | W = Writable     | bit             | U = Unimpler                             | mented bit, read | l as '0' |         |

| -n = Value at POR '1' = |              | '1' = Bit is set |                 | 0' = Bit is cleared $x = Bit is unknown$ |                  |          | nown    |

|                         |              |                  |                 |                                          |                  |          |         |

| bit 15-14               | F15MSK<1:0   | >: Mask Sourc    | e for Filter 15 | bits                                     |                  |          |         |

|                         | 11 = Reserve | ed               |                 |                                          |                  |          |         |

|                         |              | nce Mask 2 reg   |                 |                                          |                  |          |         |

|                         | 01 = Accepta | nce Mask 1 reg   | gisters contain | mask                                     |                  |          |         |

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| bit 13-12 | F14MSK<1:0>: Mask Source for Filter 14 bits (same values as bits<15:14>) |

|-----------|--------------------------------------------------------------------------|

00 = Acceptance Mask 0 registers contain mask

bit 11-10 F13MSK<1:0>: Mask Source for Filter 13 bits (same values as bits<15:14>)

bit 9-8 F12MSK<1:0>: Mask Source for Filter 12 bits (same values as bits<15:14>)

bit 7-6 **F11MSK<1:0>:** Mask Source for Filter 11 bits (same values as bits<15:14>)

bit 5-4 **F10MSK<1:0>:** Mask Source for Filter 10 bits (same values as bits<15:14>)

bit 3-2 **F9MSK<1:0>:** Mask Source for Filter 9 bits (same values as bits<15:14>)

bit 1-0 F8MSK<1:0>: Mask Source for Filter 8 bits (same values as bits<15:14>)

| R/W-x         | R/W-x                       | R/W-x                         | R/W-x        | R/W-x                                   | R/W-x           | R/W-x    | R/W-x |

|---------------|-----------------------------|-------------------------------|--------------|-----------------------------------------|-----------------|----------|-------|

| EID5          | EID4                        | EID3                          | EID2         | EID1                                    | EID0            | RTR      | RB1   |

| bit 15        |                             |                               | •            |                                         | •               |          | bit 8 |

| U-x           | U-x                         | U-x                           | R/W-x        | R/W-x                                   | R/W-x           | R/W-x    | R/W-x |

|               | _                           | _                             | RB0          | DLC3                                    | DLC2            | DLC1     | DLC0  |

| bit 7         |                             |                               |              |                                         | •               |          | bit 0 |

|               |                             |                               |              |                                         |                 |          |       |

| Legend:       |                             |                               |              |                                         |                 |          |       |

| R = Readable  | e bit                       | W = Writable                  | bit          | U = Unimplei                            | mented bit, rea | d as '0' |       |

| -n = Value at | POR                         | '1' = Bit is set              |              | '0' = Bit is cleared x = Bit is unknown |                 |          |       |

|               |                             |                               |              |                                         |                 |          |       |

| bit 15-10     | EID<5:0>: E                 | xtended Identifie             | er bits      |                                         |                 |          |       |

| bit 9         | RTR: Remot                  | e Transmission                | Request bit  |                                         |                 |          |       |

|               | 1 = Message<br>0 = Normal r | e will request rer<br>nessage | note transmi | ssion                                   |                 |          |       |

#### BUFFER 21-3: ECANx MESSAGE BUFFER WORD 2

|         | 0 = Normal message                                |

|---------|---------------------------------------------------|

| bit 8   | RB1: Reserved Bit 1                               |

|         | User must set this bit to '0' per ECAN™ protocol. |

| bit 7-5 | Unimplemented: Read as '0'                        |

| bit 4   | RB0: Reserved Bit 0                               |

|         | User must set this bit to '0' per ECAN protocol.  |

| bit 3-0 | DLC<3:0>: Data Length Code bits                   |

#### BUFFER 21-4: ECANx MESSAGE BUFFER WORD 3

| R/W-x                              | R/W-x | R/W-x          | R/W-x                | R/W-x        | R/W-x              | R/W-x     | R/W-x |

|------------------------------------|-------|----------------|----------------------|--------------|--------------------|-----------|-------|

|                                    |       |                | В                    | yte 1        |                    |           |       |

| bit 15                             |       |                |                      |              |                    |           | bit 8 |

| R/W-x                              | R/W-x | R/W-x          | R/W-x                | R/W-x        | R/W-x              | R/W-x     | R/W-x |

|                                    |       |                | В                    | yte 0        |                    |           |       |

| bit 7                              |       |                |                      |              |                    |           | bit 0 |

| Legend:                            |       |                |                      |              |                    |           |       |

| R = Readable                       | bit   | W = Writable b | it                   | U = Unimplem | nented bit, rea    | ad as '0' |       |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is cleared |              | x = Bit is unknown |           |       |

bit 7-0 Byte 0<7:0>: ECANx Message Byte 0

| U-0             | U-0                                                                                                                                                                                                                                                        | U-0              | U-0             | U-0                                     | U-0                | U-0                | U-0         |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-----------------------------------------|--------------------|--------------------|-------------|--|