Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

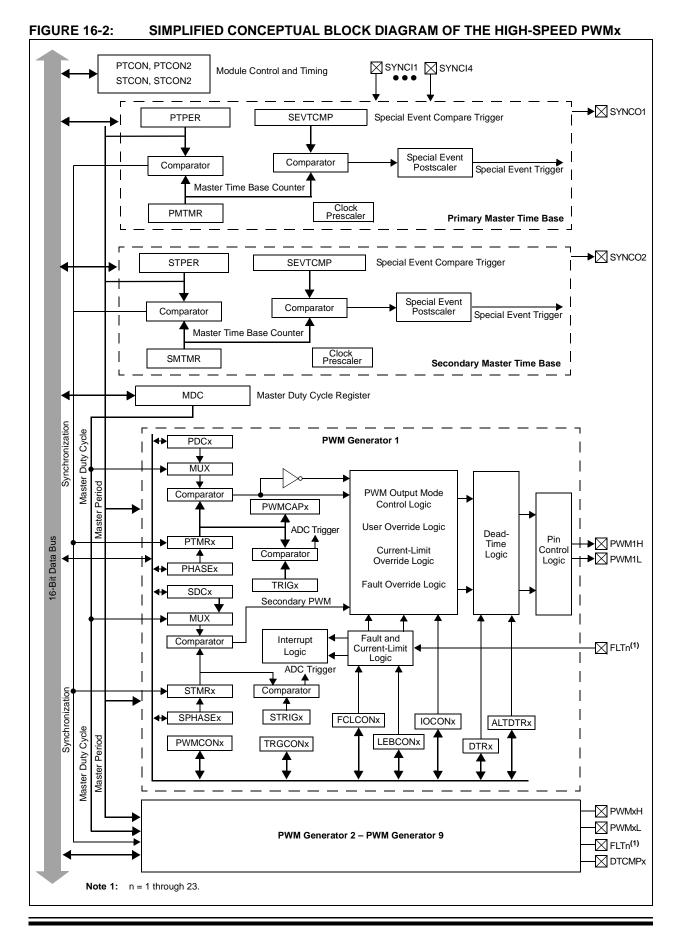

| Peripherals                | Brown-out Detect/Reset, DMA, QEI, POR, PWM, WDT                                  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 9K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10b; D/A 1x10b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gs610t-i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

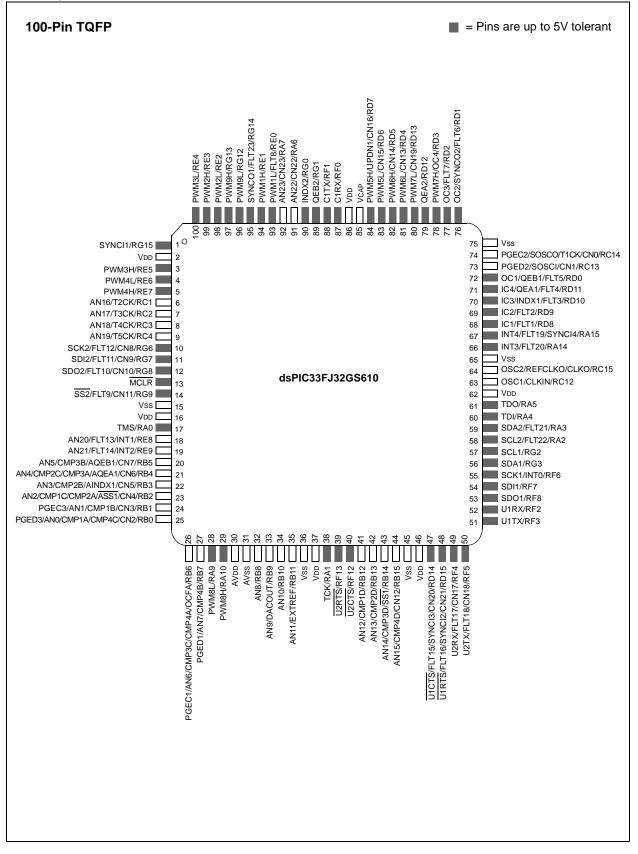

## Pin Diagrams (Continued)

| TABLE 1-1: PI |                 | ESCRIPT        |                                                                      |

|---------------|-----------------|----------------|----------------------------------------------------------------------|

| Pin Name      | Pin<br>Type     | Buffer<br>Type | Description                                                          |

| U1CTS         | I               | ST             | UART1 Clear-to-Send.                                                 |

| U1RTS         | 0               | _              | UART1 Request-to-Send.                                               |

| U1RX          | I               | ST             | UART1 receive.                                                       |

| U1TX          | 0               | _              | UART1 transmit.                                                      |

| U2CTS         | I               | ST             | UART2 Clear-to-Send.                                                 |

| U2RTS         | 0               | _              | UART2 Request-to-Send.                                               |

| U2RX          | I               | ST             | UART2 receive.                                                       |

| U2TX          | 0               | _              | UART2 transmit.                                                      |

| SCK1          | I/O             | ST             | Synchronous serial clock input/output for SPI1.                      |

| SDI1          | I               | ST             | SPI1 data in.                                                        |

| SDO1          | 0               | _              | SPI1 data out.                                                       |

| SS1, ASS1     | I/O             | ST             | SPI1 slave synchronization or frame pulse I/O.                       |

| SCK2          | I/O             | ST             | Synchronous serial clock input/output for SPI2.                      |

| SDI2          | I               | ST             | SPI2 data in.                                                        |

| SDO2          | 0               | _              | SPI2 data out.                                                       |

| SS2           | I/O             | ST             | SPI2 slave synchronization or frame pulse I/O.                       |

| SCL1          | I/O             | ST             | Synchronous serial clock input/output for I2C1.                      |

| SDA1          | I/O             | ST             | Synchronous serial data input/output for I2C1.                       |

| SCL2          | I/O             | ST             | Synchronous serial clock input/output for I2C2.                      |

| SDA2          | I/O             | ST             | Synchronous serial data input/output for I2C2.                       |

| TMS           | I               | TTL            | JTAG Test mode select pin.                                           |

| TCK           | I               | TTL            | JTAG test clock input pin.                                           |

| TDI           | I               | TTL            | JTAG test data input pin.                                            |

| TDO           | 0               | _              | JTAG test data output pin.                                           |

| CMP1A         | Ι               | Analog         | Comparator 1 Channel A.                                              |

| CMP1B         | I               | Analog         | Comparator 1 Channel B.                                              |

| CMP1C         | I               | Analog         | Comparator 1 Channel C.                                              |

| CMP1D         | I               | Analog         | Comparator 1 Channel D.                                              |

| CMP2A         | I               | Analog         | Comparator 2 Channel A                                               |

| CMP2B         | I               | Analog         | Comparator 2 Channel B.                                              |

| CMP2C         | I               | Analog         | Comparator 2 Channel C.                                              |

| CMP2D         | I               | Analog         | Comparator 2 Channel D.                                              |

| CMP3A         | I               | Analog         | Comparator 3 Channel A.                                              |

| CMP3B         | I               | Analog         | Comparator 3 Channel B.                                              |

| CMP3C         | I               | Analog         | Comparator 3 Channel C.                                              |

| CMP3D         | I               | Analog         | Comparator 3 Channel D.                                              |

| CMP4A         | I               | Analog         | Comparator 4 Channel A.                                              |

| CMP4B         | I               | Analog         | Comparator 4 Channel B.                                              |

| CMP4C         | I               | Analog         | Comparator 4 Channel C.                                              |

| CMP4D         | Ι               | Analog         | Comparator 4 Channel D.                                              |

| DACOUT        | 0               | _              | DAC output voltage.                                                  |

| EXTREF        | I               | Analog         | External voltage reference input for the reference DACs.             |

| REFCLK        | 0               |                | REFCLK output signal is a postscaled derivative of the system clock. |

|               | CMOS compa      | atible input   |                                                                      |

| •             | mitt Triggor in |                |                                                                      |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:CMOS = CMOS compatible input or output<br/>ST = Schmitt Trigger input with CMOS levels<br/>TTL = Transistor-Transistor LogicAnalog = Analog input<br/>P = PowerI = Input<br/>O = Output

## 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space. All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All Effective Addresses (EAs) are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

#### 4.2.6 DMA RAM

Some devices contain 1 Kbyte of dual ported DMA RAM, which is located at the end of Y data space. Memory locations that are part of Y data RAM and are in the DMA RAM space are accessible simultaneously by the CPU and the DMA Controller module. DMA RAM is utilized by the DMA Controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA Controller without having to steal cycles from the CPU.

When the CPU and the DMA Controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14         | Bit 13   Bit 17   Bit 11   Bit 10   Bit 9   Bit 8   Bit 7   Bit 6   Bit 5   Bit 4   Bit 3   Bit 7   Bit 1   Bit 0 |         |           |           |           |           |          |         |          | All<br>Resets |          |          |          |          |      |

|--------------|-------------|---------|----------------|-------------------------------------------------------------------------------------------------------------------|---------|-----------|-----------|-----------|-----------|----------|---------|----------|---------------|----------|----------|----------|----------|------|

| PWMCON7      | 04E0        | FLTSTAT | CLSTAT         | TRGSTAT                                                                                                           | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS      | DTC1     | DTC0    | DTCP     | _             | MTBS     | CAM      | XPRES    | IUE      | 0000 |

| IOCON7       | 04E2        | PENH    | PENL           | POLH                                                                                                              | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL    | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0       | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000 |

| FCLCON7      | 04E4        | IFLTMOD | CLSRC4         | CLSRC3                                                                                                            | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD     | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1       | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000 |

| PDC7         | 04E6        |         | PDC7<15:0> 01  |                                                                                                                   |         |           |           |           |           |          |         | 0000     |               |          |          |          |          |      |

| PHASE7       | 04E8        |         |                |                                                                                                                   |         |           |           |           | PHAS      | E7<15:0> |         |          |               |          |          |          |          | 0000 |

| DTR7         | 04EA        | _       | — — DTR7<13:0> |                                                                                                                   |         |           |           |           |           |          |         | 0000     |               |          |          |          |          |      |

| ALTDTR7      | 04EA        | _       | ALTDTR7<13:0>  |                                                                                                                   |         |           |           |           |           |          |         | 0000     |               |          |          |          |          |      |

| SDC7         | 04EE        |         |                |                                                                                                                   |         |           |           |           | SDC.      | 7<15:0>  |         |          |               |          |          |          |          | 0000 |

| SPHASE7      | 04F0        |         |                |                                                                                                                   |         |           |           |           | SPHAS     | E7<15:0> |         |          |               |          |          |          |          | 0000 |

| TRIG7        | 04F2        |         |                |                                                                                                                   |         |           |           | TRGCMP<12 | :0>       |          |         |          |               |          | -        | _        | _        | 0000 |

| TRGCON7      | 04F4        | TRGDIV3 | TRGDIV2        | TRGDIV1                                                                                                           | TRGDIV0 | _         | _         | _         | _         | DTM      | —       | TRGSTRT5 | TRGSTRT4      | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000 |

| STRIG7       | 04F6        |         |                |                                                                                                                   |         |           | ;         | STRGCMP<1 | 2:0>      |          |         |          |               |          | _        | _        | —        | 0000 |

| PWMCAP7      | 04F8        |         |                |                                                                                                                   |         |           |           | PWMCAP<12 | 2:0>      |          |         |          |               |          | _        | _        | —        | 0000 |

| LEBCON7      | 04FA        | PHR     | PHF            | PLR                                                                                                               | PLF     | FLTLEBEN  | CLLEBEN   | _         | —         | —        | _       | BCH      | BCL           | BPHH     | BPHL     | BPLH     | BPLL     | 0000 |

| LEBDLY7      | 04FC        | _       | _              | _                                                                                                                 | —       |           |           |           | L         | EB<8:0>  |         |          |               |          | —        | _        | —        | 0000 |

| AUXCON7      | 04FE        | HRPDIS  | HRDDIS         | _                                                                                                                 | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 | _        | _       | CHOPSEL3 | CHOPSEL2      | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000 |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-36: DMA REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|                | . 00.       |                             |             |        |        |        |        |        |        |            |         |         |         |         |         |         |         |               |

|----------------|-------------|-----------------------------|-------------|--------|--------|--------|--------|--------|--------|------------|---------|---------|---------|---------|---------|---------|---------|---------------|

| File<br>Name   | SFR<br>Addr | Bit 15                      | Bit 14      | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7      | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

| DMA0CON        | 0380        | CHEN                        | SIZE        | DIR    | HALF   | NULLW  | —      | _      | —      | —          | —       | AMODE1  | AMODE0  | _       | —       | MODE1   | MODE0   | 0000          |

| DMA0REQ        | 0382        | FORCE                       | _           | _      | _      | —      | _      |        | _      | —          | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | 007F          |

| DMA0STA        | 0384        |                             |             |        |        |        |        |        |        | STA<15:0>  |         |         |         |         |         |         |         | 0000          |

| <b>DMA0STB</b> | 0386        |                             |             |        |        |        |        |        |        | STB<15:0>  |         |         |         |         |         |         |         | 0000          |

| DMA0PAD        | 0388        |                             |             |        |        |        |        |        |        | PAD<15:0>  |         |         |         |         |         |         |         | 0000          |

| DMA0CNT        | 038A        | <u>− − − − − −</u> CNT<9:0> |             |        |        |        |        |        |        |            | 0000    |         |         |         |         |         |         |               |

| DMA1CON        | 038C        | CHEN                        | SIZE        | DIR    | HALF   | NULLW  |        |        | —      | _          | —       | AMODE1  | AMODE0  | _       |         | MODE1   | MODE0   | 0000          |

| DMA1REQ        | 038E        | FORCE                       | _           |        | —      | —      |        |        | —      | _          | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | 007F          |

| DMA1STA        | 0390        |                             | STA<15:0> 0 |        |        |        |        |        |        | 0000       |         |         |         |         |         |         |         |               |

| DMA1STB        | 0392        |                             | STB<15:0>   |        |        |        |        |        |        |            |         | 0000    |         |         |         |         |         |               |

| DMA1PAD        | 0394        | PAD<15:0>                   |             |        |        |        |        |        |        |            | 0000    |         |         |         |         |         |         |               |

| DMA1CNT        | 0396        |                             |             | _      | _      | _      | _      |        |        |            |         | CNT<    | :9:0>   |         |         |         |         | 0000          |

| DMA2CON        | 0398        | CHEN                        | SIZE        | DIR    | HALF   | NULLW  | _      | _      | _      | _          | _       | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA2REQ        | 039A        | FORCE                       | _           |        | —      | —      |        |        | _      | —          | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | 007F          |

| DMA2STA        | 039C        |                             |             |        |        |        |        |        |        | STA<15:0>  |         |         |         |         |         |         |         | 0000          |

| DMA2STB        | 039E        |                             |             |        |        |        |        |        |        | STB<15:0>  |         |         |         |         |         |         |         | 0000          |

| DMA2PAD        | 03A0        |                             |             |        |        |        |        |        |        | PAD<15:0>  |         |         |         |         |         |         |         | 0000          |

| DMA2CNT        | 03A2        | _                           | _           |        | —      | —      |        |        |        |            |         | CNT<    | :9:0>   |         |         |         |         | 0000          |

| <b>DMA3CON</b> | 03A4        | CHEN                        | SIZE        | DIR    | HALF   | NULLW  |        |        | _      | —          | _       | AMODE1  | AMODE0  | —       |         | MODE1   | MODE0   | 0000          |

| <b>DMA3REQ</b> | 03A6        | FORCE                       |             | _      | _      | _      | _      | _      | _      | _          | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | 007F          |

| <b>DMA3STA</b> | 03A8        |                             |             |        |        |        |        |        |        | STA<15:0>  |         |         |         |         |         |         |         | 0000          |

| <b>DMA3STB</b> | 03AA        |                             |             |        |        |        |        |        |        | STB<15:0>  |         |         |         |         |         |         |         | 0000          |

| <b>DMA3PAD</b> | 03AC        |                             |             |        |        |        |        |        |        | PAD<15:0>  |         |         |         |         |         |         |         | 0000          |

| <b>DMA3CNT</b> | 03AE        | _                           | _           | _      | —      | —      | _      |        |        |            |         | CNT<    | :9:0>   |         |         |         |         | 0000          |

| DMACS0         | 03E0        | _                           | _           |        | —      | PWCOL3 | PWCOL2 | PWCOL1 | PWCOL0 | —          | _       | —       | _       | XWCOL3  | XWCOL2  | XWCOL1  | XWCOL0  | 0000          |

| DMACS1         | 03E2        | _                           | _           | -      | _      | LSTCH3 | LSTCH2 | LSTCH1 | LSTCH0 | —          | —       | _       | _       | PPST3   | PPST2   | PPST1   | PPST0   | 0F00          |

| DSADR          | 03E4        |                             |             |        |        |        |        |        | D      | SADR<15:0> |         |         |         |         |         |         |         | 0000          |

DS7000591F-page 88

#### 6.2 Power-on Reset (POR)

A Power-on Reset (POR) circuit ensures the device is reset from power-on. The POR circuit is active until VDD crosses the VPOR threshold and the delay, TPOR, has elapsed. The delay, TPOR, ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 27.0 "Electrical Characteristics" for details.

The Power-on Reset (POR) status bit in the Reset Control (RCON<0>) register is set to indicate the Power-on Reset.

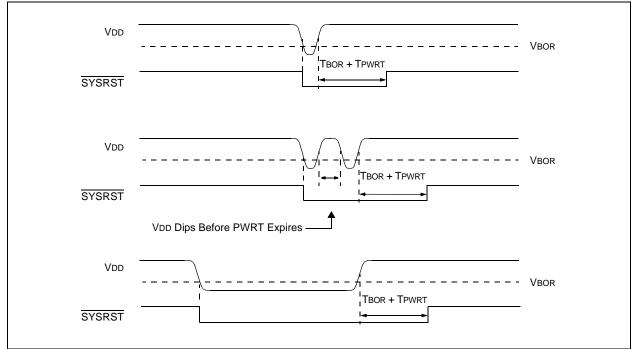

#### 6.3 Brown-out Reset (BOR) and Power-up Timer (PWRT)

The on-chip regulator has a Brown-out Reset (BOR) circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses the

VBOR threshold and the delay, TBOR, has elapsed. The delay, TBOR, ensures the voltage regulator output becomes stable.

The Brown-out Reset (BOR) status bit in the Reset Control (RCON<1>) register is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides a Power-up Time Delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The Power-up Timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select (FPWRT<2:0>) bits in the FPOR Configuration (FPOR<2:0>) register, which provides eight settings (from 0 ms to 128 ms). Refer to **Section 24.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The Reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point

#### FIGURE 6-3: BROWN-OUT SITUATIONS

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| U-0          | U-0           | U-0                                 | U-0           | U-0              | U-0              | U-0             | U-0     |  |  |  |  |  |

|--------------|---------------|-------------------------------------|---------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| —            | —             | —                                   | —             | —                | —                | —               | —       |  |  |  |  |  |

| bit 15       |               |                                     |               |                  |                  |                 | bit 8   |  |  |  |  |  |

|              |               |                                     |               |                  |                  |                 |         |  |  |  |  |  |

| U-0          | U-0           | R/W-0                               | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |

| _            |               | ADCP7IE                             | ADCP6IE       | ADCP5IE          | ADCP4IE          | ADCP3IE         | ADCP2IE |  |  |  |  |  |

| bit 7        |               |                                     |               |                  |                  |                 | bit C   |  |  |  |  |  |

|              |               |                                     |               |                  |                  |                 |         |  |  |  |  |  |

| Legend:      |               |                                     |               |                  |                  |                 |         |  |  |  |  |  |

| R = Readab   | ole bit       | W = Writable                        | bit           | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value a | at POR        | '1' = Bit is set                    |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

|              |               |                                     |               |                  |                  |                 |         |  |  |  |  |  |

| bit 15-6     | •             | nted: Read as '                     |               |                  |                  |                 |         |  |  |  |  |  |

| bit 5        |               | DC Pair 7 Conv                      |               | nterrupt Enable  | e bit            |                 |         |  |  |  |  |  |

|              |               | request is enab                     |               |                  |                  |                 |         |  |  |  |  |  |

| 1.1.4        | •             | request is not e                    |               |                  | 1.5              |                 |         |  |  |  |  |  |

| bit 4        |               | DC Pair 6 Conv                      |               | nterrupt Enable  | e Dit            |                 |         |  |  |  |  |  |

|              |               | request is enab<br>request is not e |               |                  |                  |                 |         |  |  |  |  |  |

| bit 3        | •             | DC Pair 5 Conv                      |               | nterrupt Enable  | e bit            |                 |         |  |  |  |  |  |

| Sit 0        |               | request is enab                     |               |                  |                  |                 |         |  |  |  |  |  |

|              | •             | request is not e                    |               |                  |                  |                 |         |  |  |  |  |  |

| bit 2        | ADCP4IE: A    | DC Pair 4 Conv                      | ersion Done I | nterrupt Enable  | e bit            |                 |         |  |  |  |  |  |

|              | 1 = Interrupt | request is enab                     | led           |                  |                  |                 |         |  |  |  |  |  |

|              | 0 = Interrupt | request is not e                    | enabled       |                  |                  |                 |         |  |  |  |  |  |

| bit 1        | ADCP3IE: A    | DC Pair 3 Conv                      | ersion Done I | nterrupt Enable  | e bit            |                 |         |  |  |  |  |  |

|              |               | 1 = Interrupt request is enabled    |               |                  |                  |                 |         |  |  |  |  |  |

|              | 0 = Interrupt | request is not e                    | enabled       |                  |                  |                 |         |  |  |  |  |  |

| bit 0        |               | DC Pair 2 Conv                      |               | nterrupt Enable  | e bit            |                 |         |  |  |  |  |  |

|              |               | request is enab                     |               |                  |                  |                 |         |  |  |  |  |  |

|              | 0 = Interrupt | request is not e                    | enabled       |                  |                  |                 |         |  |  |  |  |  |

#### REGISTER 7-20: IEC7: INTERRUPT ENABLE CONTROL REGISTER 7

| U-0           | R/W-1         | R/W-0                    | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0    |

|---------------|---------------|--------------------------|------------------|------------------|------------------|-----------------|----------|

| _             | ADCP1IP2      | ADCP1IP1                 | ADCP1IP0         | —                | ADCP0IP2         | ADCP0IP1        | ADCP0IP0 |

| oit 15        | ·             |                          |                  |                  | ·                | ·               | bit 8    |

|               |               |                          |                  |                  |                  |                 |          |

| U-0           | U-0           | U-0                      | U-0              | U-0              | U-0              | U-0             | U-0      |

| _             | —             | —                        | —                | —                | —                | —               | -        |

| bit 7         |               |                          |                  |                  | ·                | •               | bit (    |

|               |               |                          |                  |                  |                  |                 |          |

| Legend:       |               |                          |                  |                  |                  |                 |          |

| R = Readabl   | le bit        | W = Writable             | bit              | U = Unimple      | mented bit, read | d as '0'        |          |

| -n = Value at | t POR         | '1' = Bit is set         | t                | '0' = Bit is cle | eared            | x = Bit is unki | nown     |

|               |               |                          |                  |                  |                  |                 |          |

| bit 15        | Unimplemen    | ted: Read as '           | 0'               |                  |                  |                 |          |

| bit 14-12     | ADCP1IP<2:    | <b>0&gt;:</b> ADC Pair 1 | Conversion       | Done Interrupt   | Priority bits    |                 |          |

|               | 111 = Interru | pt is Priority 7         | (highest priorit | y interrupt)     |                  |                 |          |

|               | •             |                          |                  |                  |                  |                 |          |

|               | •             |                          |                  |                  |                  |                 |          |

|               | 001 = Interru | pt is Priority 1         |                  |                  |                  |                 |          |

|               | 000 = Interru | pt source is dis         | sabled           |                  |                  |                 |          |

| bit 11        | Unimplemen    | ted: Read as '           | 0'               |                  |                  |                 |          |

| bit 10-8      | ADCP0IP<2:    | <b>0&gt;:</b> ADC Pair ( | ) Conversion [   | Done Interrupt   | Priority bits    |                 |          |

|               | 111 = Interru | pt is Priority 7         | (highest priorit | y interrupt)     |                  |                 |          |

|               | •             |                          |                  |                  |                  |                 |          |

|               | •             |                          |                  |                  |                  |                 |          |

|               | 001 = Interru | pt is Priority 1         |                  |                  |                  |                 |          |

|               | 000 = Interru | pt source is dis         | sabled           |                  |                  |                 |          |

| bit 7-0       | Unimplemen    | ted: Read as '           | 0'               |                  |                  |                 |          |

|               |               |                          |                  |                  |                  |                 |          |

#### REGISTER 7-43: IPC27: INTERRUPT PRIORITY CONTROL REGISTER 27

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70182) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., the UART Receive register and Input Capture 1 buffer) and buffers, or variables stored in RAM, with minimal CPU intervention. The DMA Controller (DMAC) can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA Controller uses a dedicated bus for data transfers and, therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

Note: The DMA module is not available on dsIPC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406 devices.

The peripherals that can utilize DMA are listed in Table 8-1 along with their associated Interrupt Request (IRQ) numbers.

## TABLE 8-1: DMA CONTROLLER CHANNEL TO PERIPHERAL ASSOCIATIONS

| Peripheral to DMA Association         | DMAxREQ Register<br>IRQSEL<6:0> Bits | DMAxPAD Register<br>Values to Read from<br>Peripheral | DMAxPAD Register<br>Values to Write to<br>Peripheral |

|---------------------------------------|--------------------------------------|-------------------------------------------------------|------------------------------------------------------|

| INT0 – External Interrupt 0           | 0000000                              | —                                                     | —                                                    |

| IC1 – Input Capture 1                 | 0000001                              | 0x0140 (IC1BUF)                                       | —                                                    |

| IC2 – Input Capture 2                 | 0000101                              | 0x0144 (IC2BUF)                                       | —                                                    |

| IC3 – Input Capture 3                 | 0100101                              | 0x0148 (IC3BUF)                                       | —                                                    |

| IC4 – Input Capture 4                 | 0100110                              | 0x014C (IC4BUF)                                       | —                                                    |

| OC1 – Output Compare 1 Data           | 0000010                              | —                                                     | 0x0182 (OC1R)                                        |

| OC1 – Output Compare 1 Secondary Data | 0000010                              | —                                                     | 0x0180 (OC1RS)                                       |

| OC2 – Output Compare 2 Data           | 0000110                              | —                                                     | 0x0188 (OC2R)                                        |

| OC2 – Output Compare 2 Secondary Data | 0000110                              | —                                                     | 0x0186 (OC2RS)                                       |

| OC3 – Output Compare 3 Data           | 0011001                              | —                                                     | 0x018E (OC3R)                                        |

| OC3 – Output Compare 3 Secondary Data | 0011001                              | —                                                     | 0x018C (OC3RS)                                       |

| OC4 – Output Compare 4 Data           | 0011010                              | —                                                     | 0x0194 (OC4R)                                        |

| OC4 – Output Compare 4 Secondary Data | 0011010                              | —                                                     | 0x0192 (OC4RS)                                       |

| TMR2 – Timer2                         | 0000111                              | —                                                     | —                                                    |

| TMR3 – Timer3                         | 0001000                              | —                                                     | —                                                    |

| TMR4 – Timer4                         | 0011011                              | —                                                     | —                                                    |

| TMR5 – Timer5                         | 0011100                              | —                                                     | —                                                    |

| SPI1 – Transfer Done                  | 0001010                              | 0x0248 (SPI1BUF)                                      | 0x0248 (SPI1BUF)                                     |

| SPI2 – Transfer Done                  | 0100001                              | 0x0268 (SPI2BUF)                                      | 0x0268 (SPI2BUF)                                     |

| UART1RX – UART1 Receiver              | 0001011                              | 0x0226 (U1RXREG)                                      | —                                                    |

| UART1TX – UART1 Transmitter           | 0001100                              | —                                                     | 0x0224 (U1TXREG)                                     |

| UART2RX – UART2 Receiver              | 0011110                              | 0x0236 (U2RXREG)                                      | —                                                    |

| UART2TX – UART2 Transmitter           | 0011111                              | —                                                     | 0x0234 (U2TXREG)                                     |

| ECAN1 – RX Data Ready                 | 0100010                              | 0x0640 (C1RXD)                                        | _                                                    |

| ECAN1 – TX Data Request               | 1000110                              | —                                                     | 0x0642 (C1TXD)                                       |

© 2009-2014 Microchip Technology Inc.

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator (Part IV)" (DS70307) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

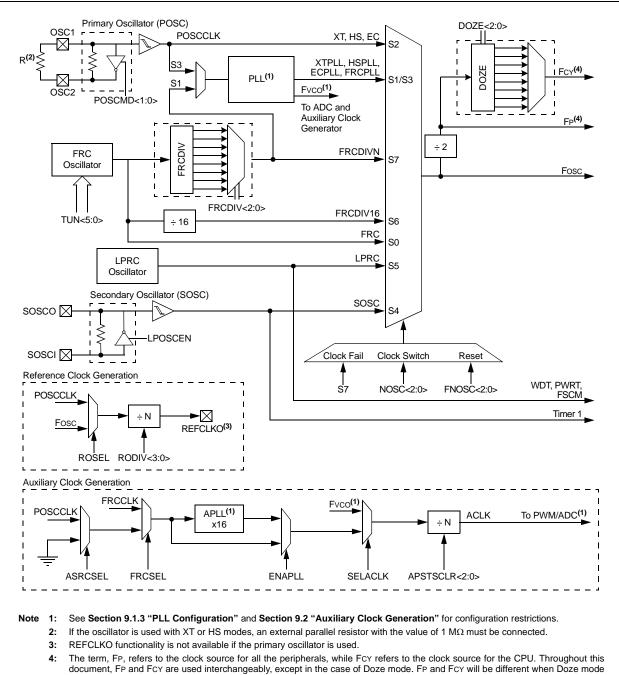

The oscillator system provides:

- External and Internal Oscillator Options as Clock

Sources

- An On-Chip Phase-Locked Loop (PLL) to Scale the Internal Operating frequency to the Required System Clock Frequency

- An Internal FRC Oscillator that can also be used with the PLL, thereby allowing Full-Speed Operation without any External Clock Generation Hardware

- Clock Switching Between Various Clock Sources

- Programmable Clock Postscaler for System

Power Savings

- A Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and takes Fail-Safe Measures

- A Clock Control Register (OSCCON)

- Nonvolatile Configuration bits for Main Oscillator Selection

- Auxiliary PLL for ADC and PWM

A simplified diagram of the oscillator system is shown in Figure 9-1.

#### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

is used in any ratio other than 1:1, which is the default.

## 9.5 Clock Switching Operation

Applications are free to switch among any of the four clock sources (primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects of this flexibility, dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610 devices have a safeguard lock built into the switch process.

Note: Primary oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from primary oscillator mode in software, it cannot switch among the different primary submodes without reprogramming the device.

## 9.5.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 24.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled; this is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC<2:0> Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.5.2 OSCILLATOR SWITCHING SEQUENCE

To perform a clock switch, the following basic sequence is required:

- 1. If desired, read the COSCx bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSCx control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit (OSCCON<0>) to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

The clock switching hardware compares the COSCx status bits with the new value of the NOSCx control bits. If they are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and the CF (OSCCON<3>) status bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bit values are transferred to the COSCx status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to "Oscillator (Part IV)" (DS70307) in the "dsPIC33/PIC24 Family Reference Manual" for details.

## 9.6 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then, the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a Warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

#### © 2009-2014 Microchip Technology Inc.

# REGISTER 16-14: PHASEx: PWM PRIMARY PHASE-SHIFT x REGISTER<sup>(1,2)</sup>

| R/W-0   | R/W-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0 | R/W-0   | R/W-0 |

|---------|-------|---------|---------|---------|-------|---------|-------|

|         |       | 11/00-0 | 11/00-0 | 10/00-0 |       | 10/00-0 |       |

|         |       |         | PHASE   | x<15:8> |       |         |       |

| bit 15  |       |         |         |         |       |         | bit 8 |

| R/W-0   | R/W-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0 | R/W-0   | R/W-0 |

|         |       |         | PHASE   | X<7:0>  |       |         |       |

| bit 7   |       |         |         |         |       |         | bit ( |

|         |       |         |         |         |       |         |       |

| Logondi |       |         |         |         |       |         |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 PHASEx<15:0>: PWM Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

- **Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<10:8> = 00, 01 or 10), PHASEx<15:0> = Phase-Shift Value for PWMxH and PWMxL outputs.

- True Independent Output mode (IOCONx<10:8> = 11), PHASEx<15:0> = Phase-Shift Value for PWMxH only.

- The PHASEx/SPHASEx registers provide the phase shift with respect to the master time base; therefore, the valid range is 0x0000 through period.

- **2:** If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<10:8> = 00, 01 or 10), PHASEx<15:0> = Independent Time Base Period Value for PWMxH and PWMxL.

- True Independent Output mode (IOCONx<10:8> = 11). PHASEx<15:0> = Independent Time Base Period Value for PWMxH only.

- When the PHASEx/SPHASEx registers provide the local period, the valid range is 0x0000 through 0xFFF8.

## REGISTER 16-16: DTRx: PWM DEAD-TIME x REGISTER

| U-0    | U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|--------|-------|-------|

| —      | —     |       |       | DTR×  | <13:8> |       |       |

| bit 15 |       |       |       |       |        |       | bit 8 |

|        |       |       |       |       |        |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|        |       |       | DTRx  | <7:0> |        |       |       |

| bit 7  |       |       |       |       |        |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Value for PWMx Dead-Time Unit bits

#### REGISTER 16-17: ALTDTRx: PWM ALTERNATE DEAD-TIME x REGISTER

| U-0                                                                        | U-0   | R/W-0          | R/W-0         | R/W-0        | R/W-0           | R/W-0    | R/W-0 |  |  |  |

|----------------------------------------------------------------------------|-------|----------------|---------------|--------------|-----------------|----------|-------|--|--|--|

| —                                                                          | —     |                | ALTDTRx<13:8> |              |                 |          |       |  |  |  |

| bit 15                                                                     |       |                |               |              |                 |          | bit 8 |  |  |  |

|                                                                            |       |                |               |              |                 |          |       |  |  |  |

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0         | R/W-0        | R/W-0           | R/W-0    | R/W-0 |  |  |  |

|                                                                            |       |                | ALTDT         | Rx<7:0>      |                 |          |       |  |  |  |

| bit 7                                                                      |       |                |               |              |                 |          | bit 0 |  |  |  |

|                                                                            |       |                |               |              |                 |          |       |  |  |  |

| Legend:                                                                    |       |                |               |              |                 |          |       |  |  |  |

| R = Readable                                                               | bit   | W = Writable b | bit           | U = Unimplem | ented bit, read | d as '0' |       |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |                |               |              |                 | nown     |       |  |  |  |

| h                                                                          |       |                |               |              |                 |          |       |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Value for PWMx Dead-Time Unit bits

## 21.3 Modes of Operation

The ECANTM module can operate in one of several operation modes selected by the user. These modes include:

- Initialization mode

- Disable mode

- Normal Operation mode

- · Listen Only mode

- Listen All Messages mode

- Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

## 21.3.1 INITIALIZATION MODE

In the Initialization mode, the module does not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The user application has access to Configuration registers that are access restricted in other modes. The module protects the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The ECAN module is not allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

## 21.3.2 DISABLE MODE

In Disable mode, the module does not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts remain and the error counters retains their value.

If the REQOP<2:0> bits (CxCTRL1<10:8>) = 001, the module enters the Module Disable mode. If the module is active, the module waits for 11 recessive bits on the CAN bus, detects that condition as an Idle bus, then accepts the module disable command. When the OPMODE<2:0> bits (CxCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CxRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CxCFG2<14>) enables or disables the filter.

| Note: | Typically, if the ECAN module is allowed to   |

|-------|-----------------------------------------------|

| Note. |                                               |

|       | transmit in a particular mode of operation,   |

|       | and a transmission is requested immedi-       |

|       | ately after the ECAN module has been          |

|       | placed in that mode of operation, the         |

|       | module waits for 11 consecutive recessive     |

|       | bits on the bus before starting transmission. |

|       | If the user switches to Disable mode within   |

|       | this 11-bit period, then this transmission is |

|       | aborted and the corresponding TXABTmn         |

|       | bit is set and the TXREQmn bit is cleared.    |

## 21.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins assume the CAN bus functions. The module transmits and receives CAN bus messages via the CxTX and CxRX pins.

#### 21.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

## 21.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = 111. In this mode, the data, which is in the message assembly buffer until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

## 21.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module connects the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

# dsPIC33FJ32GS406/606/608/610 and dsPIC33FJ64GS406/606/608/610

| R/W-0            | R/W-0                                                                                     | R/W-0            | R/W-0                                | R/W-0                              | R/W-0    | R/W-0              | R/W-0    |  |  |

|------------------|-------------------------------------------------------------------------------------------|------------------|--------------------------------------|------------------------------------|----------|--------------------|----------|--|--|

| IRQEN3           | PEND3                                                                                     | SWTRG3           | TRGSRC34                             | TRGSRC33                           | TRGSRC32 | TRGSRC31           | TRGSRC30 |  |  |

| bit 15           | •                                                                                         |                  |                                      |                                    |          |                    | bit 8    |  |  |

|                  |                                                                                           |                  |                                      |                                    |          |                    |          |  |  |

| R/W-0            | R/W-0                                                                                     | R/W-0            | R/W-0                                | R/W-0                              | R/W-0    | R/W-0              | R/W-0    |  |  |

| IRQEN2           | PEND2                                                                                     | SWTRG2           | TRGSRC24                             | TRGSRC23                           | TRGSRC22 | TRGSRC21           | TRGSRC20 |  |  |

| bit 7            |                                                                                           |                  |                                      |                                    |          |                    | bit 0    |  |  |

|                  |                                                                                           |                  |                                      |                                    |          |                    |          |  |  |

| Legend:          |                                                                                           |                  |                                      |                                    |          |                    |          |  |  |

| R = Readable bit |                                                                                           | W = Writable bit |                                      | U = Unimplemented bit, read as '0' |          |                    |          |  |  |

| -n = Value at    | POR                                                                                       | '1' = Bit is set |                                      | '0' = Bit is cleared               |          | x = Bit is unknown |          |  |  |

|                  |                                                                                           |                  |                                      |                                    |          |                    |          |  |  |

| bit 15           | IRQEN3: Interrupt Request Enable 3 bit                                                    |                  |                                      |                                    |          |                    |          |  |  |

|                  | 1 = Enables IRQ generation when requested conversion of Channels AN7 and AN6 is completed |                  |                                      |                                    |          |                    |          |  |  |

|                  | 0 = IRQ is not generated                                                                  |                  |                                      |                                    |          |                    |          |  |  |

| bit 14           | PEND3: Pending Conversion Status 3 bit                                                    |                  |                                      |                                    |          |                    |          |  |  |

|                  | 1 = Conversion of Channels AN7 and AN6 is pending; set when selected trigger is asserted  |                  |                                      |                                    |          |                    |          |  |  |

|                  | 0 = Conversi                                                                              | on is complete   |                                      |                                    |          |                    |          |  |  |

|                  | SWTRG3: Software Trigger 3 bit                                                            |                  |                                      |                                    |          |                    |          |  |  |

| bit 13           | SWTRG3: So                                                                                | Jitwale mggel    |                                      |                                    |          |                    |          |  |  |

| bit 13           | 1 = Starts co                                                                             | nversion of AN   | N7 and AN6 (if s                     | selected by the                    |          |                    |          |  |  |

| bit 13           | 1 = Starts co<br>This bit i                                                               | nversion of AN   | N7 and AN6 (if s<br>/ cleared by hai | selected by the<br>rdware when th  |          |                    |          |  |  |

## REGISTER 22-7: ADCPC1: ADC CONVERT PAIR CONTROL REGISTER 1

**Note 1:** The trigger source must be set as an individual software trigger prior to setting this bit to '1'. If other conversions are in progress, the conversion is performed when the conversion resources are available.

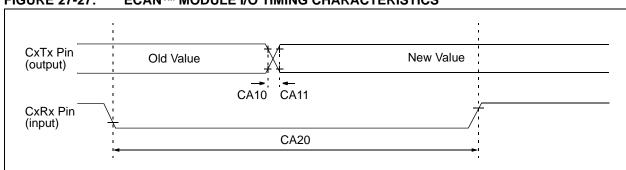

## FIGURE 27-27: ECAN™ MODULE I/O TIMING CHARACTERISTICS

#### TABLE 27-48: ECAN™ MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |       |                    |

|--------------------|--------|----------------------------------------------|-------------------------------------------------------|-----|-----|-------|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                | Min                                                   | Тур | Max | Units | Conditions         |

| CA10               | TioF   | Port Output Fall Time                        | _                                                     | —   | —   | ns    | See Parameter DO32 |

| CA11               | TioR   | Port Output Rise Time                        | —                                                     | —   | —   | ns    | See Parameter DO31 |

| CA20               | Tcwf   | Pulse Width to Trigger<br>CAN Wake-up Filter | 120                                                   | —   | —   | ns    |                    |

Note 1: These parameters are characterized but not tested in manufacturing.

## TABLE 27-49: DMA READ/WRITE TIMING REQUIREMENTS

| AC CHARACTERISTICS |                           | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |       |       |            |  |

|--------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|------------|--|

| Param<br>No.       | Characteristic            | Min.                                                                                                                                                                                                 | Тур | Max.  | Units | Conditions |  |

| DM1                | DMA Read/Write Cycle Time | —                                                                                                                                                                                                    | —   | 1 Tcy | ns    |            |  |

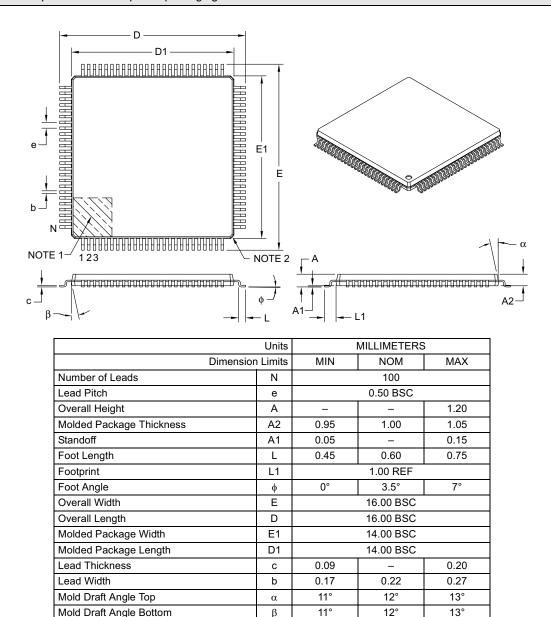

#### 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B