Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 50                                                                          |

| Program Memory Size        | 48KB (24K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65j15t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                        | Pin Number            | Pin                       | Buffer           | Description                                                                                                                                                                          |  |

|---------------------------------------------------------------------------------|-----------------------|---------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                 | TQFP                  | Туре                      | Туре             | Description                                                                                                                                                                          |  |

| RE0/AD8/RD/P2D<br>RE0<br>AD8<br>RD                                              | 4                     | I/O<br>I/O<br>I           | ST<br>TTL<br>TTL | PORTE is a bidirectional I/O port.<br>Digital I/O.<br>External memory address/data 8.<br>Read control for Parallel Slave Port.                                                       |  |

| P2D<br>RE1/AD9/WR/P2C<br>RE1<br>AD9<br>WR<br>P2C                                | 3                     | 0<br> /0<br> /0<br> <br>0 | ST<br>TTL<br>TTL | Digital I/O.<br>External memory address/data 9.<br>Write control for Parallel Slave Port.<br>ECCP2 PWM output C.                                                                     |  |

| RE2/AD10/CS/P2B<br>RE2<br>AD10<br>CS<br>P2B                                     | 78                    | I/O<br>I/O<br>I<br>O      | ST<br>TTL<br>TTL | Digital I/O.<br>External memory address/data 10.<br>Chip select control for Parallel Slave Port.<br>ECCP2 PWM output B.                                                              |  |

| RE3/AD11/P3C<br>RE3<br>AD11<br>P3C <sup>(3)</sup>                               | 77                    | I/O<br>I/O<br>O           | ST<br>TTL        | Digital I/O.<br>External memory address/data 11.<br>ECCP3 PWM output C.                                                                                                              |  |

| RE4/AD12/P3B<br>RE4<br>AD12<br>P3B <sup>(3)</sup>                               | 76                    | I/O<br>I/O<br>O           | ST<br>TTL        | Digital I/O.<br>External memory address/data 12.<br>ECCP3 PWM output B.                                                                                                              |  |

| RE5/AD13/P1C<br>RE5<br>AD13<br>P1C <sup>(3)</sup>                               | 75                    | I/O<br>I/O<br>O           | ST<br>TTL        | Digital I/O.<br>External memory address/data 13.<br>ECCP1 PWM output C.                                                                                                              |  |

| RE6/AD14/P1B<br>RE6<br>AD14<br>P1B <sup>(3)</sup>                               | 74                    | I/O<br>I/O<br>O           | ST<br>TTL        | Digital I/O.<br>External memory address/data 14.<br>ECCP1 PWM output B.                                                                                                              |  |

| RE7/AD15/ECCP2/P2A<br>RE7<br>AD15<br>ECCP2 <sup>(4)</sup><br>P2A <sup>(4)</sup> | 73                    | I/O<br>I/O<br>I/O<br>O    | ST<br>TTL<br>ST  | Digital I/O.<br>External memory address/data 15.<br>Capture 2 input/Compare 2 output/PWM 2 output.<br>ECCP2 PWM output A.                                                            |  |

| $ST = Sc$ $I = Inj$ $P = Pc$ $I^2C/SMB = I^2C$                                  | ower<br>C™/SMBus inpu | ut with Cl                |                  | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)<br>uration bit, CCP2MX, is cleared (Extended Microcontroller mo |  |

### TABLE 1-4: PIC18F8XJ10/8XJ15 PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Default assignment for ECCP2/P2A for all devices in all operating modes (CCP2MX is set).

3: Default assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is set).

4: Alternate assignment for ECCP2/P2A when CCP2MX is cleared (Microcontroller mode).

5: Alternate assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is cleared).

| Pin Name                   | Pin Number         | Pin Buffer | Description  |                                                   |  |

|----------------------------|--------------------|------------|--------------|---------------------------------------------------|--|

| Pin Name                   | TQFP               | Туре Туре  |              |                                                   |  |

|                            |                    |            |              | PORTH is a bidirectional I/O port.                |  |

| RH0/A16                    | 79                 |            |              |                                                   |  |

| RH0<br>A16                 |                    | 1/0<br>1/0 | ST<br>TTL    | Digital I/O.<br>External memory address/data 16.  |  |

| RH1/A17                    | 80                 |            |              |                                                   |  |

| RH1<br>A17                 |                    | I/O<br>I/O | ST<br>TTL    | Digital I/O.<br>External memory address/data 17.  |  |

| RH2/A18                    | 1                  |            |              |                                                   |  |

| RH2                        |                    | I/O        | ST           | Digital I/O.                                      |  |

| A18                        |                    | I/O        | TTL          | External memory address/data 18.                  |  |

| RH3/A19                    | 2                  | 10         | OT           |                                                   |  |

| RH3<br>A19                 |                    | 1/O<br>1/O | ST<br>TTL    | Digital I/O.<br>External memory address/data 19.  |  |

| RH4/AN12/P3C               | 22                 |            |              |                                                   |  |

| RH4                        |                    | I/O        | ST           | Digital I/O.                                      |  |

| AN12<br>P3C <sup>(5)</sup> |                    | <br>0      | Analog<br>—  | Analog input 12.<br>ECCP3 PWM output C.           |  |

| RH5/AN13/P3B               | 21                 |            |              |                                                   |  |

| RH5                        |                    | I/O        | ST           | Digital I/O.                                      |  |

| AN13<br><sub>P3B</sub> (5) |                    |            | Analog       | Analog input 13.<br>ECCP3 PWM output B.           |  |

| RH6/AN14/P1C               | 20                 | 0          | _            |                                                   |  |

| RH6                        | 20                 | I/O        | ST           | Digital I/O.                                      |  |

| AN14                       |                    | I          | Analog       | Analog input 14.                                  |  |

| P1C <sup>(5)</sup>         |                    | 0          | —            | ECCP1 PWM output C.                               |  |

| RH7/AN15/P1B               | 19                 |            | 07           |                                                   |  |

| RH7<br>AN15                |                    | I/O<br>I   | ST<br>Analog | Digital I/O.<br>Analog input 15.                  |  |

| P1B <sup>(5)</sup>         |                    | 0          |              | ECCP1 PWM output B.                               |  |

| -                          | L compatible inp   |            | 1            | CMOS = CMOS compatible input or output            |  |

|                            | hmitt Trigger inpu | ut with C  | MOS levels   |                                                   |  |

| I = Ing<br>P = Po          |                    |            |              | O = Output<br>OD = Open-Drain (no P diode to VDD) |  |

#### TABLE 1-4: PIC18F8XJ10/8XJ15 PINOUT I/O DESCRIPTIONS (CONTINUED)

P = Power I<sup>2</sup>C/SMB = I<sup>2</sup>C™/SMBus input buffer

**Note 1:** Alternate assignment for ECCP2/P2A when Configuration bit, CCP2MX, is cleared (Extended Microcontroller mode).

2: Default assignment for ECCP2/P2A for all devices in all operating modes (CCP2MX is set).

3: Default assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is set).

4: Alternate assignment for ECCP2/P2A when CCP2MX is cleared (Microcontroller mode).

5: Alternate assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is cleared).

### 6.4 Data Addressing Modes

| Note: | The execution of some instructions in the  |

|-------|--------------------------------------------|

|       | core PIC18 instruction set are changed     |

|       | when the PIC18 extended instruction set is |

|       | enabled. See Section 6.6 "Data Memory      |

|       | and the Extended Instruction Set" for      |

|       | more information.                          |

While the program memory can be addressed in only one way – through the program counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 6.6.1 "Indexed Addressing with Literal Offset**".

# 6.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device, or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way, but require an additional explicit argument in the opcode. This is known as Literal Addressing mode, because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

### 6.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byte-oriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit Literal Address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 6.3.3 "General **Purpose Register File**"), or a location in the Access Bank (Section 6.3.2 "Access Bank") as the data source for the instruction.

The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.3.1 "Bank Select Register") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit, 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

# 6.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code using loops, such as the example of clearing an entire RAM bank in Example 6-5. It also enables users to perform Indexed Addressing and other Stack Pointer operations for program memory in data memory.

#### EXAMPLE 6-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 100h | ;                |

|---------|-------|------------|------------------|

| NEXT    | CLRF  | POSTINC0   | ; Clear INDF     |

|         |       |            | ; register then  |

|         |       |            | ; inc pointer    |

|         | BTFSS | FSROH, 1   | ; All done with  |

|         |       |            | ; Bank1?         |

|         | BRA   | NEXT       | ; NO, clear next |

| CONTINU | JE    |            | ; YES, continue  |

|         |       |            |                  |

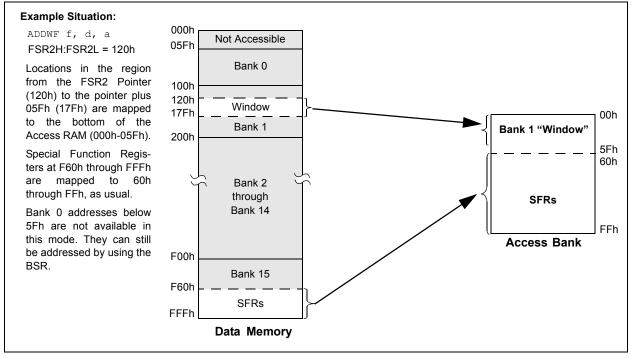

### 6.6.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the lower part of Access RAM (00h to 5Fh) is mapped. Rather than containing just the contents of the bottom part of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see Section 6.3.2 "Access Bank"). An example of Access Bank remapping in this addressing mode is shown in Figure 6-12.

Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use Direct Addressing as before. Any Indirect or Indexed Addressing operation that explicitly uses any of the indirect file operands (including FSR2) will continue to operate as standard Indirect Addressing. Any instruction that uses the Access Bank, but includes a register address of greater than 05Fh, will use Direct Addressing and the normal Access Bank map.

#### 6.6.4 BSR IN INDEXED LITERAL OFFSET MODE

Although the Access Bank is remapped when the extended instruction set is enabled, the operation of the BSR remains unchanged. Direct Addressing, using the BSR to select the data memory bank, operates in the same manner as previously described.

# FIGURE 6-12: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

#### 8.7.1 **8-BIT MODE TIMING**

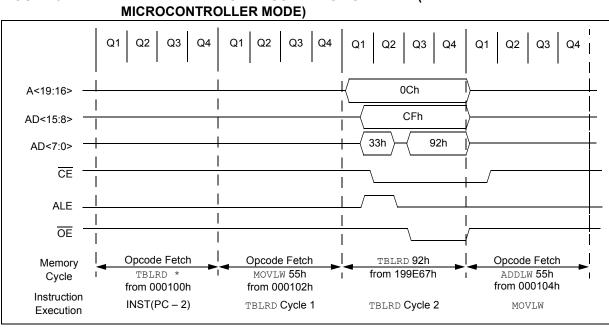

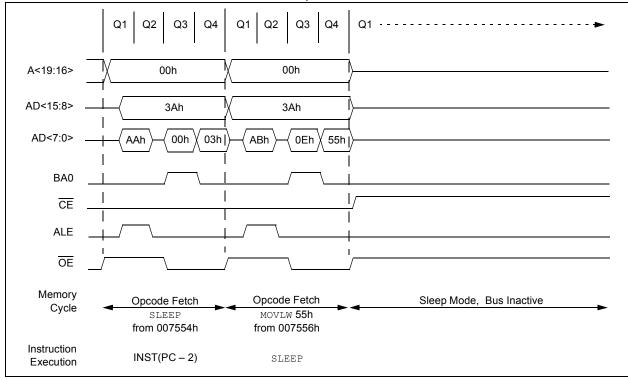

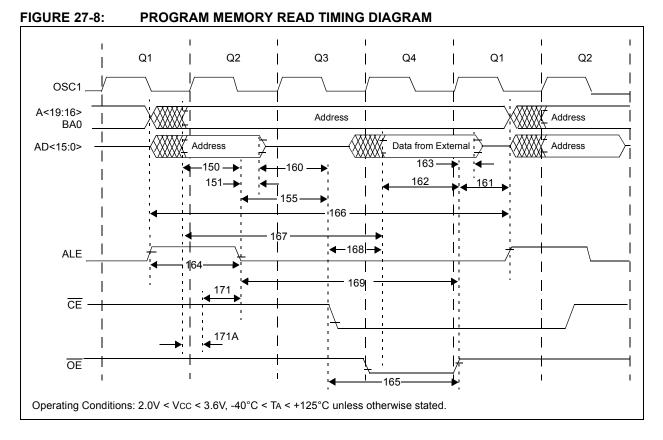

The presentation of control signals on the external memory bus is different for the various operating modes. Typical signal timing diagrams are shown in Figure 8-7 and Figure 8-8.

#### **FIGURE 8-7:** EXTERNAL MEMORY BUS TIMING FOR TBLRD (EXTENDED

#### **EXTERNAL MEMORY BUS TIMING FOR SLEEP (EXTENDED FIGURE 8-8: MICROCONTROLLER MODE)**

# 9.0 8 x 8 HARDWARE MULTIPLIER

## 9.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 9-1.

# 9.2 Operation

Example 9-1 shows the instruction sequence for an  $8 \times 8$  unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 9-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

### EXAMPLE 9-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ; |                |

|-------|-------|---|---|----------------|

| MULWF | ARG2  |   | ; | ARG1 * ARG2 -> |

|       |       |   | ; | PRODH: PRODL   |

|       |       |   |   |                |

#### EXAMPLE 9-2: 8 x 8 SIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, W  |   |                |

|-------|----------|---|----------------|

| MULWF | ARG2     | ; | ARG1 * ARG2 -> |

|       |          | ; | PRODH:PRODL    |

| BTFSC | ARG2, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG1         |

| MOVF  | ARG2, W  |   |                |

| BTFSC | ARG1, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG2         |

|       |          |   |                |

|                  |                           | Program           | Cycles | Time     |          |         |  |

|------------------|---------------------------|-------------------|--------|----------|----------|---------|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

|                  | Without Hardware Multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 μs   |  |

| 8 x 8 unsigned   | Hardware Multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs    |  |

| 8 x 8 signed     | Without Hardware Multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs   |  |

|                  | Hardware Multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 μs    |  |

| 16 x 16 uppigned | Without Hardware Multiply | 21                | 242    | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| 16 x 16 unsigned | Hardware Multiply         | 28                | 28     | 2.8 μs   | 11.2 μs  | 28 μs   |  |

| 16 x 16 signed   | Without Hardware Multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs  |  |

|                  | Hardware Multiply         | 35                | 40     | 4.0 μs   | 16.0 μs  | 40 μs   |  |

### TABLE 9-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

# 11.3 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin). All pins on PORTB are digital only and tolerate voltages up to 5.5V.

The Output Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

### EXAMPLE 11-2: INITIALIZING PORTB

| CLRF  | PORTB | ; Initialize PORTB by<br>; clearing output<br>: data latches |

|-------|-------|--------------------------------------------------------------|

| CLRF  | LATB  | ; data fattines<br>: Alternate method                        |

| OLIG  | DITE  | ; to clear output                                            |

|       |       | ; data latches                                               |

| MOVLW | OCFh  | ; Value used to                                              |

|       |       | ; initialize data                                            |

|       |       | ; direction                                                  |

| MOVWF | TRISB | ; Set RB<3:0> as inputs                                      |

|       |       | ; RB<5:4> as outputs                                         |

|       |       | ; RB<7:6> as inputs                                          |

|       |       |                                                              |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn <u>on all</u> the pull-ups. This is performed by clearing bit, RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB<7:4>) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from power-managed modes. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF (ANY), PORTB instruction). This will end the mismatch condition.

- b) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit, RBIF, to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

For 80-pin devices, RB3 can be configured as the alternate peripheral pin for the ECCP2 module and Enhanced PWM Output 2A by clearing the CCP2MX Configuration bit. This applies only to 80-pin devices operating in Extended Microcontroller mode. If the device is in Microcontroller mode, the alternate assignment for ECCP2 is RE7. As with other ECCP2 configurations, the user must ensure that the TRISB<3> bit is set appropriately for the intended operation.

| Pin Name     | Function           | TRIS<br>Setting | I/O | I/О Туре             | Description                                                                              |

|--------------|--------------------|-----------------|-----|----------------------|------------------------------------------------------------------------------------------|

| RD0/AD0/PSP0 | RD0                | 0               | 0   | DIG                  | LATD<0> data output.                                                                     |

|              |                    | 1               | I   | ST                   | PORTD<0> data input.                                                                     |

|              | AD0 <sup>(2)</sup> | x               | 0   | DIG                  | External memory interface, address/data bit 0 output. <sup>(1)</sup>                     |

|              |                    | x               | I   | TTL                  | External memory interface, data bit 0 input. <sup>(1)</sup>                              |

|              | PSP0               |                 | 0   | DIG                  | PSP read output data (LATD<0>); takes priority over port data.                           |

|              |                    |                 | Ι   | TTL                  | PSP write data input.                                                                    |

| RD1/AD1/PSP1 | RD1                | 0               | 0   | DIG                  | LATD<1> data output.                                                                     |

|              |                    | 1               | Ι   | ST                   | PORTD<1> data input.                                                                     |

|              | AD1 <sup>(2)</sup> | x               | 0   | DIG                  | External memory interface, address/data bit 1 output. <sup>(1)</sup>                     |

|              |                    | x               | I   | TTL                  | External memory interface, data bit 1 input. <sup>(1)</sup>                              |

|              | PSP1               | x               | 0   | DIG                  | PSP read output data (LATD<1>); takes priority over port data.                           |

|              |                    | x               | I   | TTL                  | PSP write data input.                                                                    |

| RD2/AD2/PSP2 | RD2                | 0               | 0   | DIG                  | LATD<2> data output.                                                                     |

|              |                    | 1               | Ι   | ST                   | PORTD<2> data input.                                                                     |

|              | AD2 <sup>(2)</sup> | х               | 0   | DIG                  | External memory interface, address/data bit 2 output. <sup>(1)</sup>                     |

|              |                    | х               | I   | TTL                  | External memory interface, data bit 2 input. <sup>(1)</sup>                              |

|              | PSP2               | x               | 0   | DIG                  | PSP read output data (LATD<2>); takes priority over port data.                           |

|              |                    | х               | I   | TTL                  | PSP write data input.                                                                    |

| RD3/AD3/PSP3 | RD3                | 0               | 0   | DIG                  | LATD<3> data output.                                                                     |

|              |                    | 1               | I   | ST                   | PORTD<3> data input.                                                                     |

|              | AD3 <sup>(2)</sup> | x               | 0   | DIG                  | External memory interface, address/data bit 3 output. <sup>(1)</sup>                     |

|              |                    | х               | I   | TTL                  | External memory interface, data bit 3 input. <sup>(1)</sup>                              |

|              | PSP3               | x               | 0   | DIG                  | PSP read output data (LATD<3>); takes priority over port data.                           |

|              |                    | х               | I   | TTL                  | PSP write data input.                                                                    |

| RD4/AD4/     | RD4                | 0               | 0   | DIG                  | LATD<4> data output.                                                                     |

| PSP4/SDO2    |                    | 1               | I   | ST                   | PORTD<4> data input.                                                                     |

|              | AD4 <sup>(2)</sup> | х               | 0   | DIG                  | External memory interface, address/data bit 4 output. <sup>(1)</sup>                     |

|              |                    | х               | I   | TTL                  | External memory interface, data bit 4 input. <sup>(1)</sup>                              |

|              | PSP4               | х               | 0   | DIG                  | PSP read output data (LATD<4>); takes priority over port data.                           |

|              |                    | х               | I   | TTL                  | PSP write data input.                                                                    |

|              | SDO2               | 0               | 0   | DIG                  | SPI data output (MSSP2 module); takes priority over port data.                           |

| RD5/AD5/     | RD5                | 0               | 0   | DIG                  | LATD<5> data output.                                                                     |

| PSP5/SDI2/   |                    | 1               | I   | ST                   | PORTD<5> data input.                                                                     |

| SDA2         | AD5 <sup>(2)</sup> | х               | 0   | DIG                  | External memory interface, address/data bit 5 output. <sup>(1)</sup>                     |

|              |                    | х               | I   | TTL                  | External memory interface, data bit 5 input. <sup>(1)</sup>                              |

|              | PSP5               | х               | 0   | DIG                  | PSP read output data (LATD<5>); takes priority over port data.                           |

|              |                    | х               | Ι   | TTL                  | PSP write data input.                                                                    |

|              | SDI2               | 1               | Ι   | ST                   | SPI data input (MSSP2 module).                                                           |

|              | SDA2               | 1               | 0   | DIG                  | I <sup>2</sup> C <sup>™</sup> data output (MSSP2 module); takes priority over port data. |

|              |                    | 1               | I   | I <sup>2</sup> C/SMB | I <sup>2</sup> C data input (MSSP2 module); input type depends on module setting.        |

TABLE 11-9: PORTD FUNCTIONS

Legend: PWR = Power Supply, O = Output, I = Input, I<sup>2</sup>C<sup>™</sup>/SMB = I<sup>2</sup>C/SMBus input buffer, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: External memory interface I/O takes priority over all other digital and PSP I/O.

2: Available on 80-pin devices only.

# 19.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCKx is the clock output)

- Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

Each MSSP module consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full detect bit, BF (SSPxSTAT<0>), and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL (SSPxCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPxBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF (SSPxSTAT<0>), indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 19-1 shows the loading of the SSPxBUF (SSPxSR) for data transmission.

The SSPxSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various status conditions.

| LOOP | BRA           | LOOP                 | ;Has data been received (transmit complete)?<br>;No<br>;WREG reg = contents of SSP1BUF |

|------|---------------|----------------------|----------------------------------------------------------------------------------------|

|      | MOVWF         | RXDATA               | ;Save in user RAM, if data is meaningful                                               |

|      | MOVF<br>MOVWF | TXDATA, W<br>SSP1BUF | ;W reg = contents of TXDATA<br>;New data to xmit                                       |

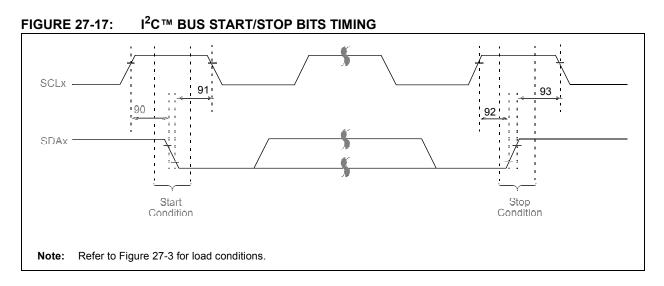

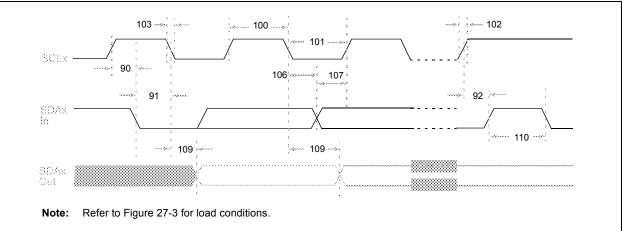

# 19.4 I<sup>2</sup>C Mode

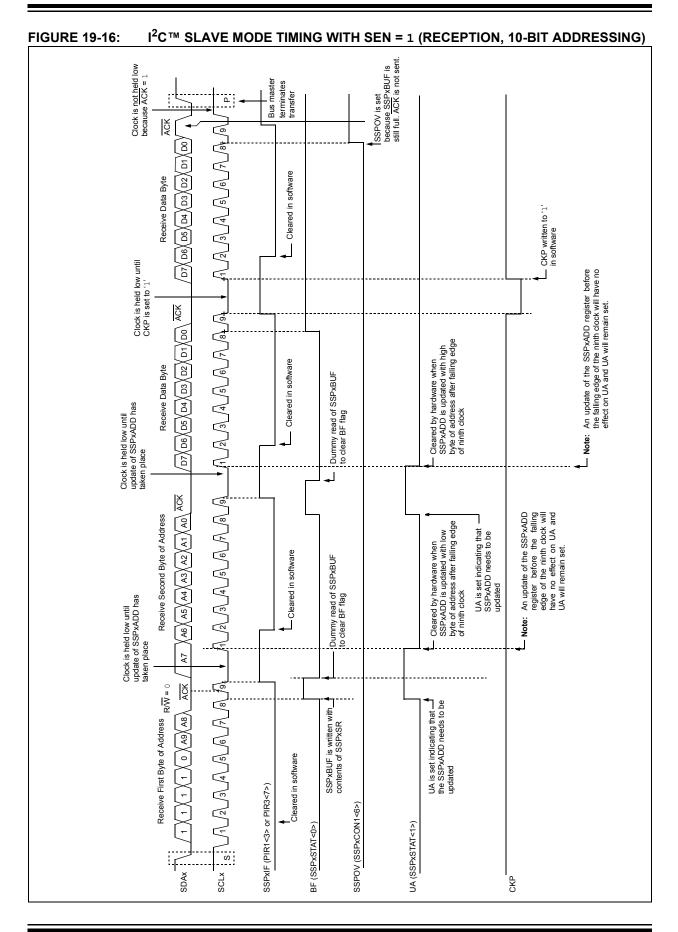

The MSSP module in I<sup>2</sup>C mode fully implements all master and slave functions (including general call support) and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial clock (SCLx) RC3/SCK1/SCL1 or RD6/SCK2/SCL2

- Serial data (SDAx) RC4/SDI1/SDA1 or RD5/SDI2/SDA2

The user must configure these pins as inputs by setting the associated TRIS bits.

#### **FIGURE 19-7: MSSP BLOCK DIAGRAM** (I<sup>2</sup>C<sup>™</sup> MODE) Internal Data Bus Read Write SSPxBUF reg SCLx $\mathbb{X}$ Shift Clock imesSSPxSR reg SDAx LSb MSb Match Detect Addr Match Address Mask SSPxADD reg Set. Reset Start and S. P bits Stop bit Detect (SSPxSTAT reg) Note: Only port I/O names are used in this diagram for the sake of brevity. Refer to the text for a full list of multiplexed functions.

### 19.4.1 REGISTERS

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are:

- MSSP Control Register 1 (SSPxCON1)

- MSSP Control Register 2 (SSPxCON2)

- MSSP Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSP Shift Register (SSPxSR) Not directly accessible

- MSSP Address Register (SSPxADD)

SSPxCON1, SSPxCON2 and SSPxSTAT are the control and status registers in I<sup>2</sup>C mode operation. The SSPxCON1 and SSPxCON2 registers are readable and writable. The lower 6 bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

SSPxADD register holds the slave device address when the MSSP is configured in I<sup>2</sup>C Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPxADD act as the Baud Rate Generator reload value.

In receive operations, SSPxSR and SSPxBUF together create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

# REGISTER 19-4: SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | WCOL: Write Collision Detect bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | In Master Transmit mode:<br>1 = A write to the SSPxBUF register was attempted while the I <sup>2</sup> C conditions were not valid for a<br>transmission to be started (must be cleared in software)                                                                                                                                                                                                                                                                                                                                               |

|         | 0 = No collision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>In Slave Transmit mode:</li> <li>1 = The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in software)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |

|         | 0 = No collision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | In Receive mode (Master or Slave modes):<br>This is a "don't care" bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 6   | SSPOV: Receive Overflow Indicator bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | <ul> <li>In Receive mode:</li> <li>1 = A byte is received while the SSPxBUF register is still holding the previous byte (must be cleared in software)</li> <li>0 = No overflow</li> </ul>                                                                                                                                                                                                                                                                                                                                                          |

|         | <u>In Transmit mode:</u><br>This is a "don't care" bit in Transmit mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 5   | SSPEN: Master Synchronous Serial Port Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = Enables the serial port and configures the SDAx and SCLx pins as the serial port pins<sup>(1)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins<sup>(1)</sup></li> </ul>                                                                                                                                                                                                                                                                                                                             |

| bit 4   | CKP: SCKx Release Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | In Slave mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Release clock</li> <li>0 = Holds clock low (clock stretch); used to ensure data setup time</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | In Master mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | Unused in this mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 3-0 | SSPM<3:0>: Master Synchronous Serial Port Mode Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | 1111 = I <sup>2</sup> C Slave mode, 10-bit address with Start and Stop bit interrupts enabled <sup>(2)</sup><br>1110 = I <sup>2</sup> C Slave mode, 7-bit address with Start and Stop bit interrupts enabled <sup>(2)</sup><br>1011 = I <sup>2</sup> C Firmware Controlled Master mode (slave Idle) <sup>(2)</sup><br>1000 = I <sup>2</sup> C Master mode, clock = Fosc/(4 * (SSPADD + 1)) <sup>(2)</sup><br>0111 = I <sup>2</sup> C Slave mode, 10-bit address <sup>(2)</sup><br>0110 = I <sup>2</sup> C Slave mode, 7-bit address <sup>(2)</sup> |

| Note 1: | When enabled, the SDAx and SCLx pins must be properly configured as input or output.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| •       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

2: Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.

### REGISTER 20-2: RCSTAX: RECEIVE STATUS AND CONTROL REGISTER

| R/W-0         | R/W-0                                     | R/W-0                                                          | R/W-0            | R/W-0            | R-0              | R-0               | R-x             |  |  |

|---------------|-------------------------------------------|----------------------------------------------------------------|------------------|------------------|------------------|-------------------|-----------------|--|--|

| SPEN          | RX9                                       | SREN                                                           | CREN             | ADDEN            | FERR             | OERR              | RX9D            |  |  |

| bit 7         |                                           |                                                                |                  |                  |                  |                   | bit (           |  |  |

|               |                                           |                                                                |                  |                  |                  |                   |                 |  |  |

| Legend:       |                                           |                                                                |                  |                  |                  |                   |                 |  |  |

| R = Readabl   | e bit                                     |                                                                | W = Writable bit |                  | mented bit, rea  |                   |                 |  |  |

| -n = Value at | POR                                       | '1' = Bit is set                                               | :                | '0' = Bit is cle | ared             | x = Bit is unki   | nown            |  |  |

| bit 7         | SPEN: Seria                               | SPEN: Serial Port Enable bit                                   |                  |                  |                  |                   |                 |  |  |

|               |                                           | ort enabled (con<br>ort disabled (hel                          |                  | Tx and TXx/C     | Kx pins as seria | al port pins)     |                 |  |  |

| bit 6         | <b>RX9:</b> 9-Bit F                       | Receive Enable I                                               | oit              |                  |                  |                   |                 |  |  |

|               |                                           | 9-bit reception<br>8-bit reception                             |                  |                  |                  |                   |                 |  |  |

| bit 5         | SREN: Sing                                | le Receive Enal                                                | ole bit          |                  |                  |                   |                 |  |  |

|               | <u>Asynchrono</u><br>Don't care.          | us mode:                                                       |                  |                  |                  |                   |                 |  |  |

|               | 1 = Enable<br>0 = Disable                 | <u>is mode – Maste</u><br>s single receive<br>s single receive |                  | - 4-             |                  |                   |                 |  |  |

|               |                                           | eared after rece<br>is mode – Slave                            |                  | ete.             |                  |                   |                 |  |  |

| bit 4         | CREN: Con                                 | CREN: Continuous Receive Enable bit                            |                  |                  |                  |                   |                 |  |  |

|               | Asynchrono<br>1 = Enables<br>0 = Disables | receiver                                                       |                  |                  |                  |                   |                 |  |  |

|               |                                           | <u>is mode:</u><br>continuous rece<br>s continuous rec         |                  | ole bit, CREN, i | s cleared (CRE   | EN overrides SF   | REN)            |  |  |

| bit 3         | ADDEN: Ad                                 | Idress Detect Er                                               | able bit         |                  |                  |                   |                 |  |  |

|               | 1 = Enable                                | us mode 9-bit (F<br>s address detect<br>s address detect       | tion, enables i  |                  |                  |                   |                 |  |  |

|               | <u>Asynchrono</u><br>Don't care.          | us mode 8-bit (F                                               | <u>RX9 = 0):</u> |                  |                  |                   |                 |  |  |

| bit 2         | FERR: Fran                                | ning Error bit                                                 |                  |                  |                  |                   |                 |  |  |

|               | 1 = Framing<br>0 = No fram                | ı error (can be uı<br>ing error                                | odated by read   | ding the RCRE    | Gx register and  | I receiving the r | next valid byte |  |  |

| bit 1         | OERR: Ove                                 | errun Error bit                                                |                  |                  |                  |                   |                 |  |  |

|               | 1 = Overrun<br>0 = No over                | n error (can be cl<br>rrun error                               | eared by clea    | ring bit, CREN   | )                |                   |                 |  |  |

| bit 0         | <b>RX9D:</b> 9th b                        | bit of Received D                                              | Data             |                  |                  |                   |                 |  |  |

|               | This can be                               | address/data bi                                                | t or a parity bi | t and must be    | calculated by u  | ser firmware.     |                 |  |  |

|               |                                           |                                                                |                  |                  |                  |                   |                 |  |  |

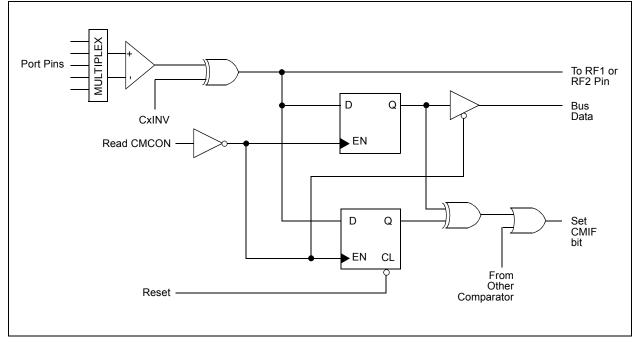

### FIGURE 22-3: COMPARATOR OUTPUT BLOCK DIAGRAM

# 22.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that occurred. The CMIF bit (PIR2<6>) is the Comparator Interrupt Flag. The CMIF bit must be reset by clearing it. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

Both the CMIE bit (PIE2<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit (INTCON<7>) must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | If a change in the CMCON register          |

|-------|--------------------------------------------|

|       | (C1OUT or C2OUT) should occur when a       |

|       | read operation is being executed (start of |

|       | the Q2 cycle), then the CMIF (PIR2         |

|       | register) interrupt flag may not get set.  |

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON will end the mismatch condition.

- b) Clear flag bit, CMIF.

A mismatch condition will continue to set flag bit, CMIF. Reading CMCON will end the mismatch condition and allow flag bit, CMIF, to be cleared.

# 22.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional, if enabled. This interrupt will wake-up the device from Sleep mode, when enabled. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators (CM<2:0> = 111) before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

# 22.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator modules to be turned off (CM<2:0> = 111). However, the input pins (RF3 through RF6) are configured as analog inputs by default on device Reset. The I/O configuration for these pins is determined by the setting of the PCFG<3:0> bits (ADCON1<3:0>). Therefore, device current is minimized when analog inputs are present at Reset time.

| XORWF                        | KORWF Exclusive OR W with f                                                                                                                                                                                                                                                         |                                                                                                                                                           |                      |  |  |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Syntax:                      | XORWF                                                                                                                                                                                                                                                                               | f {,d {,a}}                                                                                                                                               |                      |  |  |  |

| Operands:                    | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                               |                                                                                                                                                           |                      |  |  |  |

| Operation:                   | (W) .XOR.                                                                                                                                                                                                                                                                           | (f) $\rightarrow$ dest                                                                                                                                    |                      |  |  |  |

| Status Affected:             | N, Z                                                                                                                                                                                                                                                                                |                                                                                                                                                           |                      |  |  |  |

| Encoding:                    | 0001                                                                                                                                                                                                                                                                                | 10da ffi                                                                                                                                                  | ff ffff              |  |  |  |

| Description:                 | register 'f'. I<br>in W. If 'd' is                                                                                                                                                                                                                                                  | Exclusive OR the contents of W with register 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in the register 'f'. |                      |  |  |  |

|                              |                                                                                                                                                                                                                                                                                     | he Access Bar<br>he BSR is use                                                                                                                            |                      |  |  |  |

|                              | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operate<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                                                                                                                           |                      |  |  |  |

| Words:                       | 1                                                                                                                                                                                                                                                                                   |                                                                                                                                                           |                      |  |  |  |

| Cycles:                      | 1                                                                                                                                                                                                                                                                                   |                                                                                                                                                           |                      |  |  |  |

| Q Cycle Activity:            |                                                                                                                                                                                                                                                                                     |                                                                                                                                                           |                      |  |  |  |

| Q1                           | Q2                                                                                                                                                                                                                                                                                  | Q3                                                                                                                                                        | Q4                   |  |  |  |

| Decode                       | Read<br>register 'f'                                                                                                                                                                                                                                                                | Process<br>Data                                                                                                                                           | Write to destination |  |  |  |

| Example:                     | XORWF 1                                                                                                                                                                                                                                                                             | REG, 1, 0                                                                                                                                                 |                      |  |  |  |

| Before Instruc               |                                                                                                                                                                                                                                                                                     |                                                                                                                                                           |                      |  |  |  |

| REG<br>W                     | = AFh<br>= B5h                                                                                                                                                                                                                                                                      |                                                                                                                                                           |                      |  |  |  |

| After Instructic<br>REG<br>W | on<br>= 1Ah<br>= B5h                                                                                                                                                                                                                                                                |                                                                                                                                                           |                      |  |  |  |

# 25.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, the PIC18F87J10 family of devices also provide an optional extension to the core CPU functionality. The added features include eight additional instructions that augment Indirect and Indexed Addressing operations and the implementation of Indexed Literal Offset Addressing for many of the standard PIC18 instructions.

The additional features of the extended instruction set are disabled by default on unprogrammed devices. Users must properly set or clear the XINST Configuration bit during programming to enable or disable these features.

The instructions in the extended set can all be classified as literal operations, which either manipulate the File Select Registers, or use them for Indexed Addressing. Two of the instructions, ADDFSR and SUBFSR, each have an additional special instantiation for using FSR2. These versions (ADDULNK and SUBULNK) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- dynamic allocation and deallocation of software stack space when entering and leaving subroutines

- function pointer invocation

- software Stack Pointer manipulation

- manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 25-3. Detailed descriptions are provided in **Section 25.2.2 "Extended Instruction Set"**. The opcode field descriptions in Table 25-1 (page 294) apply to both the standard and extended PIC18 instruction sets.

Note: The instruction set extension and the Indexed Literal Offset Addressing mode were designed for optimizing applications written in C; the user may likely never use these instructions directly in assembler. The syntax for these commands is provided as a reference for users who may be reviewing code that has been generated by a compiler.

# 25.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of Indexed Addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. The MPASM<sup>™</sup> Assembler will flag an error if it determines that an index or offset value is not bracketed.

When the extended instruction set is enabled, brackets are also used to indicate index arguments in byte-oriented and bit-oriented instructions. This is in addition to other changes in their syntax. For more details, see Section 25.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands".

Note: In the past, square brackets have been used to denote optional arguments in the PIC18 and earlier instruction sets. In this text and going forward, optional arguments are denoted by braces ("{ }").

| Mnemonic,<br>Operands |                                 | Description                              | Cycles | 16-Bit Instruction Word |      |         |      | Status   |

|-----------------------|---------------------------------|------------------------------------------|--------|-------------------------|------|---------|------|----------|

|                       |                                 | Description                              | Cycles | MSb                     |      |         | LSb  | Affected |

| ADDFSR                | f, k                            | Add Literal to FSR                       | 1      | 1110                    | 1000 | ffkk    | kkkk | None     |

| ADDULNK               | k                               | Add Literal to FSR2 and Return           | 2      | 1110                    | 1000 | 11kk    | kkkk | None     |

| CALLW                 |                                 | Call Subroutine using WREG               | 2      | 0000                    | 0000 | 0001    | 0100 | None     |

| MOVSF                 | z <sub>s</sub> , f <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110                    | 1011 | 0 z z z | ZZZZ | None     |

|                       |                                 | f <sub>d</sub> (destination) 2nd word    |        | 1111                    | ffff | ffff    | ffff |          |

| MOVSS                 | z <sub>s</sub> , z <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110                    | 1011 | 1zzz    | ZZZZ | None     |

|                       |                                 | z <sub>d</sub> (destination) 2nd word    |        | 1111                    | XXXX | XZZZ    | ZZZZ |          |

| PUSHL                 | k                               | Store Literal at FSR2,                   | 1      | 1110                    | 1010 | kkkk    | kkkk | None     |

|                       |                                 | Decrement FSR2                           |        |                         |      |         |      |          |

| SUBFSR                | f, k                            | Subtract Literal from FSR                | 1      | 1110                    | 1001 | ffkk    | kkkk | None     |

| SUBULNK               | k                               | Subtract Literal from FSR2 and           | 2      | 1110                    | 1001 | 11kk    | kkkk | None     |

|                       |                                 | Return                                   |        |                         |      |         |      |          |

### TABLE 25-3: EXTENSIONS TO THE PIC18 INSTRUCTION SET

| Param.<br>No | Symbol   | Characteristics                                                           | Min            | Тур       | Мах            | Units |

|--------------|----------|---------------------------------------------------------------------------|----------------|-----------|----------------|-------|

| 150          | TadV2alL | Address Out Valid to ALE ↓<br>(address setup time)                        | 0.25 Tcy – 10  | _         | _              | ns    |

| 151          | TalL2adl | ALE $\downarrow$ to Address Out Invalid (address hold time)               | 5              | _         | —              | ns    |

| 155          | TalL2oeL | ALE $\downarrow$ to $\overline{OE} \downarrow$                            | 10             | 0.125 TCY | _              | ns    |

| 160          | TadZ2oeL | AD High-Z to $\overline{OE} \downarrow$ (bus release to $\overline{OE}$ ) | 0              | _         | —              | ns    |

| 161          | ToeH2adD | OE ↑ to AD Driven                                                         | 0.125 Tcy – 5  | _         | —              | ns    |

| 162          | TadV2oeH | LS Data Valid before $\overline{OE}$ $\uparrow$ (data setup time)         | 20             | _         | —              | ns    |

| 163          | ToeH2adl | OE ↑ to Data In Invalid (data hold time)                                  | 0              | _         | _              | ns    |

| 164          | TalH2alL | ALE Pulse Width                                                           | —              | 0.25 TCY  | —              | ns    |

| 165          | ToeL2oeH | OE Pulse Width                                                            | 0.5 Tcy – 5    | 0.5 TCY   | _              | ns    |