Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f66j10-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6.1.5 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register or writable. Updates to the PCU register are performed through the PCU register are performed through the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.8.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

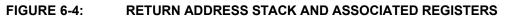

#### 6.1.6 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed, or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction (and on ADDULNK and SUBULNK instructions if the extended instruction set is enabled). PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions. The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack. The Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack. The contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full, has overflowed or has underflowed.

#### 6.1.6.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-4). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt (and ADDULNK and SUBULNK instructions if the extended instruction set is enabled), the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

#### FIGURE 6-7: DATA MEMORY MAP FOR PIC18FX5J10/X5J15/X6J10 DEVICES

| R/W-0         | R/W-0                            | R-0                               | R-0            | R/W-0          | R/W-0            | R/W-0          | R/W-0  |

|---------------|----------------------------------|-----------------------------------|----------------|----------------|------------------|----------------|--------|

| SSP2IF        | BCL2IF                           | RC2IF                             | TX2IF          | TMR4IF         | CCP5IF           | CCP4IF         | CCP3IF |

| bit 7         | •                                | ·                                 |                |                | ·                | •              | bit    |

| Legend:       |                                  |                                   |                |                |                  |                |        |

| R = Readable  | e bit                            | W = Writable                      | bit            | U = Unimple    | emented bit, rea | d as '0'       |        |

| -n = Value at | POR                              | '1' = Bit is se                   | t              | '0' = Bit is c | leared           | x = Bit is unk | nown   |

|               |                                  |                                   |                |                |                  |                |        |

| bit 7         |                                  | ster Synchrond                    |                | •              | •                |                |        |

|               |                                  | nsmission/recepto to transmit/rec |                | ete (must be c | leared in softwa | re)            |        |

| bit 6         |                                  | s Collision Inter                 |                |                |                  |                |        |

|               |                                  | ollision occurre                  | •              | ared in softwa | are)             |                |        |

| L:1 F         |                                  | collision occurr                  |                | L:4            |                  |                |        |

| bit 5         |                                  | ART2 Receive                      |                |                | eared when RC    | RECy is read)  |        |

|               |                                  | SART2 Receiv                      |                |                |                  |                |        |

| bit 4         | TX2IF: EUS                       | ART2 Transmit                     | Interrupt Flag | bit            |                  |                |        |

|               |                                  |                                   |                |                | (cleared when    | TXREGx is writ | ten)   |

|               |                                  | SART2 Transm                      |                |                |                  |                |        |

| bit 3         |                                  | IR4 to PR4 Ma                     |                | •              | <i>.</i>         |                |        |

|               |                                  | o PR4 match o<br>R4 to PR4 matc   | •              | be cleared in  | software)        |                |        |

| bit 2         |                                  | P5 Interrupt Fl                   |                |                |                  |                |        |

| 5112          | Capture mod                      |                                   | ag on          |                |                  |                |        |

|               | 1 = A TMR1                       |                                   |                |                | cleared in softw | vare)          |        |

|               | Compare mo<br>1 = A TMR1         |                                   | r compare ma   | tch occurred ( | must be cleared  | l in software) |        |

|               |                                  | R1/TMR3 regist                    |                |                |                  |                |        |

|               | PWM mode:                        |                                   |                |                |                  |                |        |

| <b>L:1</b>    | Unused in th                     |                                   | aa hit         |                |                  |                |        |

| bit 1         | Capture mod                      | P4 Interrupt Fl                   | ag bit         |                |                  |                |        |

|               | 1 = A TMR1                       |                                   |                |                | cleared in softw | vare)          |        |

|               | Compare mo                       |                                   |                |                |                  |                |        |

|               |                                  | /TMR3 registe<br>R1/TMR3 regist   |                |                | must be cleared  | l in software) |        |

|               | <u>PWM mode:</u><br>Unused in th |                                   |                |                |                  |                |        |

| bit 0         | CCP3IF: EC                       | CP3 Interrupt I                   | -lag bit       |                |                  |                |        |

|               |                                  | /TMR3 registe                     | •              | •              | cleared in softw | vare)          |        |

|               |                                  | R1/TMR3 regist                    | er capture occ | curred         |                  |                |        |

|               |                                  |                                   |                |                | must be cleared  | l in software) |        |

|               | <u>PWM mode:</u>                 | -                                 |                |                |                  |                |        |

|               |                                  | is mode.                          |                |                |                  |                |        |

## REGISTER 10-6: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

NOTES:

PIC18F87J10 FAMILY

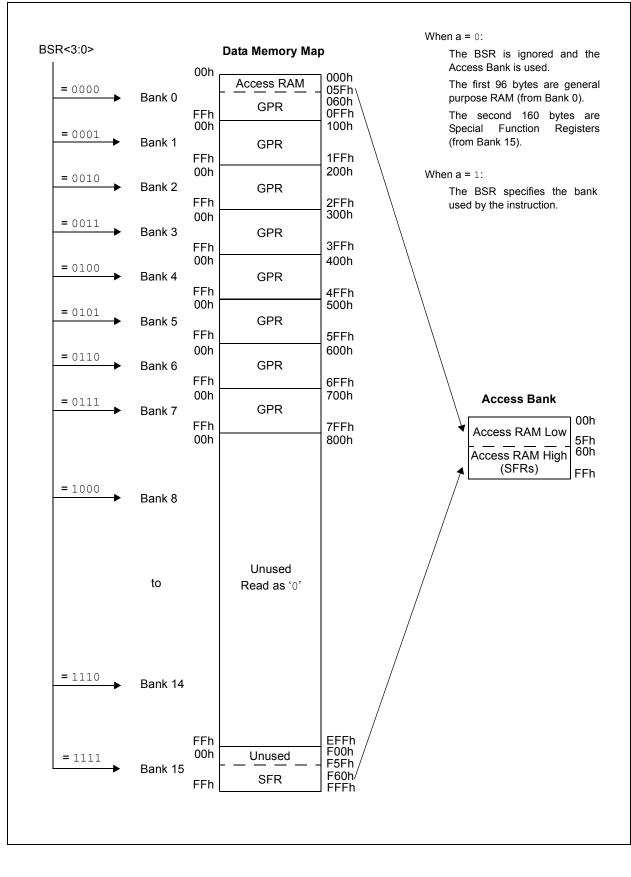

## 19.4.4 CLOCK STRETCHING

Both 7-Bit and 10-Bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPxCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCLx pin to be held low at the end of each data receive sequence.

#### 19.4.4.1 Clock Stretching for 7-Bit Slave Receive Mode (SEN = 1)

In 7-Bit Slave Receive mode, on the falling edge of the ninth clock at the end of the ACK sequence, if the BF bit is set, the CKP bit in the SSPxCON1 register is automatically cleared, forcing the SCLx output to be held low. The CKP being cleared to '0' will assert the SCLx line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCLx line low, the user has time to service the ISR and read the contents of the SSPxBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 19-15).

- Note 1: If the user reads the contents of the SSPxBUF before the falling edge of the ninth clock, the BF bit will be cleared. The CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

#### 19.4.4.2 Clock Stretching for 10-Bit Slave Receive Mode (SEN = 1)

In 10-Bit Slave Receive mode during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPxADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

Note: If the user polls the UA bit and clears it by updating the SSPxADD register before the falling edge of the ninth clock occurs, and if the user hasn't cleared the BF bit by reading the SSPxBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

#### 19.4.4.3 Clock Stretching for 7-Bit Slave Transmit Mode

The 7-Bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock if the BF bit is clear. This occurs regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCLx line low, the user has time to service the ISR and load the contents of the SSPxBUF before the master device can initiate another transmit sequence (see Figure 19-10).

- Note 1: If the user loads the contents of SSPxBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit.

#### 19.4.4.4 Clock Stretching for 10-Bit Slave Transmit Mode

In 10-Bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-Bit Slave Receive mode. The first two addresses are followed by a third address sequence which contains the high-order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is controlled by the BF flag as in 7-Bit Slave Transmit mode (see Figure 19-13).

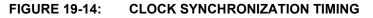

## 19.4.4.5 Clock Synchronization and the CKP Bit

When the CKP bit is cleared, the SCLx output is forced to '0'. However, clearing the CKP bit will not assert the SCLx output low until the SCLx output is already sampled low. Therefore, the CKP bit will not assert the SCLx line until an external  $I^2C$  master device has

already asserted the SCLx line. The SCLx output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have deasserted SCLx. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCLx (see Figure 19-14).

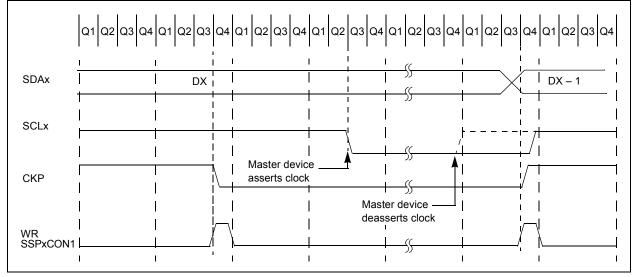

#### 19.4.7 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPxADD register (Figure 19-19). When a write occurs to SSPxBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TcY) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCLx pin will remain in its last state.

Table 19-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPxADD.

#### 19.4.7.1 Baud Rate and Module Interdependence

Because MSSP1 and MSSP2 are independent, they can operate simultaneously in I<sup>2</sup>C Master mode at different baud rates. This is done by using different BRG reload values for each module.

Because this mode derives its basic clock source from the system clock, any changes to the clock will affect both modules in the same proportion. It may be possible to change one or both baud rates back to a previous value by changing the BRG reload value.

| TABLE 19-3: | I <sup>2</sup> C™ CLOCK RATE w/BRG |

|-------------|------------------------------------|

|-------------|------------------------------------|

| Fosc   | Fcy    | Fcy * 2 | BRG Value | FscL<br>(2 Rollovers of BRG) |

|--------|--------|---------|-----------|------------------------------|

| 40 MHz | 10 MHz | 20 MHz  | 18h       | 400 kHz                      |

| 40 MHz | 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                    |

| 40 MHz | 10 MHz | 20 MHz  | 63h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 09h       | 400 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 02h       | 333 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 00h       | 1 MHz                        |

#### 20.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTAx<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CKx pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

#### 20.4.1 EUSART SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode.

If two words are written to the TXREGx and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREGx register.

- c) Flag bit, TXxIF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREGx register will transfer the second word to the TSR and flag bit, TXxIF, will now be set.

- e) If enable bit, TXxIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting enable bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name     | Bit 7                                               | Bit 6                                 | Bit 5      | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------|-----------------------------------------------------|---------------------------------------|------------|-------------|--------|--------|--------|--------|----------------------------|

| INTCON   | GIE/GIEH                                            | PEIE/GIEL                             | TMR0IE     | INT0IE      | RBIE   | TMR0IF | INT0IF | RBIF   | 53                         |

| PIR1     | PSPIF                                               | ADIF                                  | RC1IF      | TX1IF       | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 55                         |

| PIE1     | PSPIE                                               | ADIE                                  | RC1IE      | TX1IE       | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 55                         |

| IPR1     | PSPIP                                               | ADIP                                  | RC1IP      | TX1IP       | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 55                         |

| PIR3     | SSP2IF                                              | BCL2IF                                | RC2IF      | TX2IF       | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 55                         |

| PIE3     | SSP2IE                                              | BCL2IE                                | RC2IE      | TX2IE       | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 55                         |

| IPR3     | SSP2IP                                              | BCL2IP                                | RC2IP      | TX2IP       | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 55                         |

| RCSTAx   | SPEN                                                | RX9                                   | SREN       | CREN        | ADDEN  | FERR   | OERR   | RX9D   | 55                         |

| TXREGx   | EUSARTx                                             | Transmit Reo                          | gister     |             |        |        |        |        | 55                         |

| TXSTAx   | CSRC                                                | TX9                                   | TXEN       | SYNC        | SENDB  | BRGH   | TRMT   | TX9D   | 55                         |

| BAUDCONx | ABDOVF                                              | ABDOVF RCIDL - SCKP BRG16 - WUE ABDEN |            |             |        |        |        |        |                            |

| SPBRGHx  | RGHx EUSARTx Baud Rate Generator Register High Byte |                                       |            |             |        |        |        |        | 56                         |

| SPBRGx   | EUSARTx                                             | Baud Rate G                           | enerator R | egister Low | Byte   |        |        |        | 56                         |

## TABLE 20-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

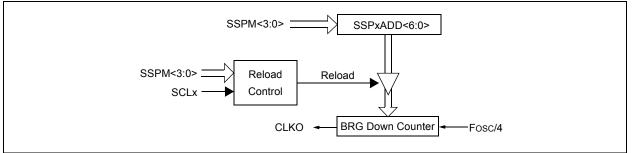

## 22.1 Comparator Configuration

There are eight modes of operation for the comparators, shown in Figure 22-1. Bits, CM<2:0>, of the CMCON register are used to select these modes. The TRISF register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in **Section 27.0 "Electrical Characteristics"**.

Note: Comparator interrupts should be disabled during a Comparator mode change; otherwise, a false interrupt may occur.

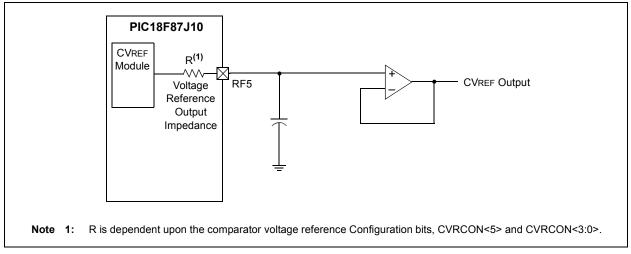

#### FIGURE 23-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |

|--------|--------|--------|--------|--------|--------|--------|--------|-------|----------------------------|

| CVRCON | CVREN  | CVROE  | CVRR   | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0  | 55                         |

| CMCON  | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0   | 55                         |

| TRISF  | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 |       | 56                         |

#### TABLE 23-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

Legend: — = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

NOTES:

#### REGISTER 24-1: CONFIG1L: CONFIGURATION REGISTER 1 LOW (BYTE ADDRESS 300000h)

| R/WO-1        | R/WO-1                         | R/WO-1                                                                    | U-0                         | U-0                | U-0              | U-0              | R/WO-1 |

|---------------|--------------------------------|---------------------------------------------------------------------------|-----------------------------|--------------------|------------------|------------------|--------|

| DEBUG         | XINST                          | STVREN                                                                    | _                           | _                  | _                | _                | WDTEN  |

| bit 7         |                                |                                                                           |                             |                    |                  |                  | bit 0  |

| Legend:       |                                |                                                                           |                             |                    |                  |                  |        |

| R = Readable  | e bit                          | WO = Write-O                                                              | nce bit                     | U = Unimpler       | mented bit, read | d as '0'         |        |

| -n = Value wh | en device is unp               | programmed                                                                |                             | '1' = Bit is se    | t                | '0' = Bit is cle | eared  |

| bit 6         | XINST: Exten<br>1 = Instructio | Ind debugger e<br>ded Instruction<br>In set extension<br>In set extension | Set Enable b<br>and Indexed | it<br>Addressing m | ode enabled      | ·                |        |

| bit 5         | 1 = Reset on                   | ck Overflow/Ur<br>stack overflow,<br>stack overflow,                      | /underflow en               | abled              |                  |                  |        |

| bit 4-1       | Unimplemen                     | ted: Read as '                                                            | )'                          |                    |                  |                  |        |

| bit 0         | 1 = WDT ena                    | chdog Timer Ei<br>abled<br>abled (control is                              |                             | WDTEN bit)         |                  |                  |        |

## REGISTER 24-2: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/WO-1 | U-0 | U-0   |

|-------|-----|-----|-----|-----|--------|-----|-------|

| —     | —   | —   | _   | (1) | CP0    | —   | —     |

| bit 7 |     |     |     |     |        |     | bit 0 |

| Legend:                |                     |                     |                      |

|------------------------|---------------------|---------------------|----------------------|

| R = Readable bit       | WO = Write-Once bit | U = Unimplemented I | oit, read as '0'     |

| -n = Value when device | e is unprogrammed   | '1' = Bit is set    | '0' = Bit is cleared |

bit 7-3 Unimplemented: Read as '0'

bit 2 CP0: Code Protection bit

- 1 = Program memory is not code-protected

- 0 = Program memory is code-protected

- bit 1-0 Unimplemented: Read as '0'

**Note 1:** This bit should always be maintained as '0'.

#### REGISTER 24-3: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |                                                                                                                                                                                             |                                                       |               |                 | -      |                  | -      |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------|-----------------|--------|------------------|--------|--|

| bit 7       bit 0         bit 7       bit 0         Legend:       WO = Write-Once bit       U = Unimplemented bit, read as '0'         -n = Value when device is unprogrammed       '1' = Bit is set       '0' = Bit is cleared         bit 7       IESO: Two-Speed Start-up (Internal/External Oscillator Switchover) Control bit       1 = Two-Speed Start-up enabled         bit 6       FCMEN: Fail-Safe Clock Monitor Enable bit       1 = Fail-Safe Clock Monitor enabled         bit 5-3       Unimplemented: Read as '0'         bit 2       FOSC2: Default/Reset System Clock Select bit         1 = Clock selected by FOSC<1:0> as a system clock is enabled when OSCCON<1:0> = 00         bit 1-0       FOSC+1:0>: Oscillator Selection bits         11 = EC oscillator, PLL enabled and under software control, CLKO function on OSC2         10 = EC oscillator, PLL enabled and under software control                                                                                                                                                 | R/WO-1                                                                                                                                          | R/WO-1                                                                                                                                                                                      | U-0                                                   | U-0           | U-0             | R/WO-1 | R/WO-1           | R/WO-1 |  |

| Legend:         R = Readable bit       WO = Write-Once bit       U = Unimplemented bit, read as '0'         -n = Value when device is unprogrammed       '1' = Bit is set       '0' = Bit is cleared         bit 7       IESO: Two-Speed Start-up (Internal/External Oscillator Switchover) Control bit         1 = Two-Speed Start-up enabled       0 = Two-Speed Start-up disabled         bit 6       FCMEN: Fail-Safe Clock Monitor Enable bit         1 = Fail-Safe Clock Monitor enabled       0 = Fail-Safe Clock Monitor enabled         0 = Fail-Safe Clock Monitor enabled       0 = Fail-Safe Clock Monitor disabled         bit 5-3       Unimplemented: Read as '0'         bit 2       FOSC2: Default/Reset System Clock Select bit         1 = Clock selected by FOSC<1:0> as a system clock is enabled when OSCCON<1:0> = 00         bit 1-0       FOSC<1:0>: Oscillator Selection bits         11 = EC oscillator, PLL enabled and under software control, CLKO function on OSC2         10 = EC oscillator, PLL enabled and under software control | IESO                                                                                                                                            | FCMEN                                                                                                                                                                                       | —                                                     | _             | —               | FOSC2  | FOSC1            | FOSC0  |  |

| R = Readable bit       WO = Write-Once bit       U = Unimplemented bit, read as '0'         -n = Value when device is unprogrammed       '1' = Bit is set       '0' = Bit is cleared         bit 7       IESO: Two-Speed Start-up (Internal/External Oscillator Switchover) Control bit         1 = Two-Speed Start-up enabled       0 = Two-Speed Start-up disabled         bit 6       FCMEN: Fail-Safe Clock Monitor Enable bit         1 = Fail-Safe Clock Monitor enabled       0 = Fail-Safe Clock Monitor disabled         bit 5-3       Unimplemented: Read as '0'         bit 2       FOSC2: Default/Reset System Clock Select bit         1 = Clock selected by FOSC<1:0> as a system clock is enabled when OSCCON<1:0> = 00         0 = INTRC enabled as a system clock when OSCCON<1:0> = 00         bit 1-0       FOSC<1:0>: Oscillator Selection bits         11 = EC oscillator, PLL enabled and under software control, CLKO function on OSC2         01 = HS oscillator, PLL enabled and under software control                                     | bit 7                                                                                                                                           |                                                                                                                                                                                             |                                                       |               |                 |        |                  | bit 0  |  |

| R = Readable bit       WO = Write-Once bit       U = Unimplemented bit, read as '0'         -n = Value when device is unprogrammed       '1' = Bit is set       '0' = Bit is cleared         bit 7       IESO: Two-Speed Start-up (Internal/External Oscillator Switchover) Control bit         1 = Two-Speed Start-up enabled       0 = Two-Speed Start-up disabled         bit 6       FCMEN: Fail-Safe Clock Monitor Enable bit         1 = Fail-Safe Clock Monitor enabled       0 = Fail-Safe Clock Monitor disabled         bit 5-3       Unimplemented: Read as '0'         bit 2       FOSC2: Default/Reset System Clock Select bit         1 = Clock selected by FOSC<1:0> as a system clock is enabled when OSCCON<1:0> = 00         0 = INTRC enabled as a system clock when OSCCON<1:0> = 00         bit 1-0       FOSC<1:0>: Oscillator Selection bits         11 = EC oscillator, PLL enabled and under software control, CLKO function on OSC2         01 = HS oscillator, PLL enabled and under software control                                     | Legend:                                                                                                                                         |                                                                                                                                                                                             |                                                       |               |                 |        |                  |        |  |

| bit 7 IESO: Two-Speed Start-up (Internal/External Oscillator Switchover) Control bit<br>1 = Two-Speed Start-up enabled<br>0 = Two-Speed Start-up disabled<br>bit 6 FCMEN: Fail-Safe Clock Monitor Enable bit<br>1 = Fail-Safe Clock Monitor enabled<br>0 = Fail-Safe Clock Monitor disabled<br>bit 5-3 Unimplemented: Read as '0'<br>bit 2 FOSC2: Default/Reset System Clock Select bit<br>1 = Clock selected by FOSC<1:0> as a system clock is enabled when OSCCON<1:0> = 00<br>0 = INTRC enabled as a system clock when OSCCON<1:0> = 00<br>bit 1-0 FOSC<1:0>: Oscillator Selection bits<br>11 = EC oscillator, PLL enabled and under software control, CLKO function on OSC2<br>01 = HS oscillator, PLL enabled and under software control                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |                                                                                                                                                                                             |                                                       |               |                 |        |                  |        |  |

| <ul> <li>1 = Two-Speed Start-up enabled</li> <li>0 = Two-Speed Start-up disabled</li> <li>bit 6</li> <li>FCMEN: Fail-Safe Clock Monitor Enable bit</li> <li>1 = Fail-Safe Clock Monitor enabled</li> <li>0 = Fail-Safe Clock Monitor disabled</li> <li>bit 5-3</li> <li>Unimplemented: Read as '0'</li> <li>bit 2</li> <li>FOSC2: Default/Reset System Clock Select bit</li> <li>1 = Clock selected by FOSC&lt;1:0&gt; as a system clock is enabled when OSCCON&lt;1:0&gt; = 00</li> <li>0 = INTRC enabled as a system clock when OSCCON&lt;1:0&gt; = 00</li> <li>bit 1-0</li> <li>FOSC&lt;1:0&gt;: Oscillator Selection bits</li> <li>11 = EC oscillator, PLL enabled and under software control, CLKO function on OSC2</li> <li>01 = HS oscillator, PLL enabled and under software control</li> </ul>                                                                                                                                                                                                                                                              | -n = Value w                                                                                                                                    | vhen device is unp                                                                                                                                                                          | programmed                                            |               | '1' = Bit is se | t      | '0' = Bit is cle | ared   |  |

| bit 2       FOSC2: Default/Reset System Clock Select bit         1 = Clock selected by FOSC<1:0> as a system clock is enabled when OSCCON<1:0> = 00         0 = INTRC enabled as a system clock when OSCCON<1:0> = 00         bit 1-0       FOSC<1:0>: Oscillator Selection bits         11 = EC oscillator, PLL enabled and under software control, CLKO function on OSC2         10 = EC oscillator, CLKO function on OSC2         01 = HS oscillator, PLL enabled and under software control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 6                                                                                                                                           | <ul> <li>1 = Two-Speed Start-up enabled</li> <li>0 = Two-Speed Start-up disabled</li> <li>FCMEN: Fail-Safe Clock Monitor Enable bit</li> <li>1 = Fail-Safe Clock Monitor enabled</li> </ul> |                                                       |               |                 |        |                  |        |  |

| <ul> <li>1 = Clock selected by FOSC&lt;1:0&gt; as a system clock is enabled when OSCCON&lt;1:0&gt; = 00</li> <li>0 = INTRC enabled as a system clock when OSCCON&lt;1:0&gt; = 00</li> <li>bit 1-0</li> <li>FOSC&lt;1:0&gt;: Oscillator Selection bits</li> <li>11 = EC oscillator, PLL enabled and under software control, CLKO function on OSC2</li> <li>10 = EC oscillator, CLKO function on OSC2</li> <li>01 = HS oscillator, PLL enabled and under software control</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 5-3                                                                                                                                         | Unimplemen                                                                                                                                                                                  | ted: Read as '                                        | כ'            |                 |        |                  |        |  |

| <ul> <li>11 = EC oscillator, PLL enabled and under software control, CLKO function on OSC2</li> <li>10 = EC oscillator, CLKO function on OSC2</li> <li>01 = HS oscillator, PLL enabled and under software control</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 2 <b>FOSC2:</b> Default/Reset System Clock Select bit<br>1 = Clock selected by FOSC<1:0> as a system clock is enabled when OSCCON<1:0> = 00 |                                                                                                                                                                                             |                                                       |               |                 |        |                  |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 1-0                                                                                                                                         | 11 = EC osci<br>10 = EC osci<br>01 = HS osci                                                                                                                                                | llator, PLL ena<br>llator, CLKO fu<br>llator, PLL ena | bled and unde | C2              |        | ction on OSC2    |        |  |

## REGISTER 24-4: CONFIG2H: CONFIGURATION REGISTER 2 HIGH (BYTE ADDRESS 300003h)

| U-0   | U-0 | U-0 | U-0 | R/WO-1 | R/WO-1 | R/WO-1 | R/WO-1 |

|-------|-----|-----|-----|--------|--------|--------|--------|

| —     | _   | _   | _   | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 |

| bit 7 |     |     |     |        |        |        | bit 0  |

| Legend:                     |                     |                     |                      |

|-----------------------------|---------------------|---------------------|----------------------|

| R = Readable bit            | WO = Write-Once bit | U = Unimplemented b | it, read as '0'      |

| -n = Value when device is u | inprogrammed        | '1' = Bit is set    | '0' = Bit is cleared |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDTPS<3:0>: Watchdog Timer Postscale Select bits

#### TABLE 25-2: PIC18F87J10 FAMILY INSTRUCTION SET

| Mnemonic,<br>Operands |                                 | C, Description                           |            | 16-bit Instruction Word |      |      |          | Status          |            |

|-----------------------|---------------------------------|------------------------------------------|------------|-------------------------|------|------|----------|-----------------|------------|

|                       |                                 | Description                              | Cycles     | MSb LSI                 |      | LSb  | Affected | Notes           |            |

| BYTE-OR               | ENTED                           | OPERATIONS                               |            |                         |      |      |          |                 |            |

| ADDWF                 | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da | ffff | ffff     | C, DC, Z, OV, N | 1, 2       |

| ADDWFC                | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da | ffff | ffff     | C, DC, Z, OV, N | 1, 2       |

| ANDWF                 | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da | ffff | ffff     | Z, N            | 1,2        |

| CLRF                  | f, a                            | Clear f                                  | 1          | 0110                    | 101a | ffff | ffff     | Z               | 2          |

| COMF                  | f, d, a                         | Complement f                             | 1          | 0001                    | 11da | ffff | ffff     | Z, N            | 1, 2       |

| CPFSEQ                | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a | ffff | ffff     | None            | 4          |

| CPFSGT                | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a | ffff | ffff     | None            | 4          |

| CPFSLT                | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a | ffff | ffff     | None            | 1, 2       |

| DECF                  | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da | ffff | ffff     | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ                | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da | ffff | ffff     | None            | 1, 2, 3, 4 |

| DCFSNZ                | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da | ffff | ffff     | None            | 1, 2       |

| INCF                  | f, d, a                         | Increment f                              | 1          | 0010                    | 10da | ffff | ffff     | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ                | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da | ffff | ffff     | None            | 4          |

| INFSNZ                | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da | ffff | ffff     | None            | 1, 2       |

| IORWF                 | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da | ffff | ffff     | Z, N            | 1, 2       |

| MOVF                  | f, d, a                         | Move f                                   | 1          | 0101                    | 00da | ffff | ffff     | Z, N            | 1          |

| MOVFF                 | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100                    | ffff | ffff | ffff     | None            |            |

|                       | 0 u                             | f <sub>d</sub> (destination) 2nd word    |            | 1111                    | ffff | ffff | ffff     |                 |            |

| MOVWF                 | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a | ffff | ffff     | None            |            |

| MULWF                 | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a | ffff | ffff     | None            | 1, 2       |

| NEGF                  | f, a                            | Negate f                                 | 1          | 0110                    | 110a | ffff | ffff     | C, DC, Z, OV, N |            |

| RLCF                  | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da | ffff | ffff     | C, Z, N         | 1, 2       |

| RLNCF                 | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da | ffff | ffff     | Z, N            |            |

| RRCF                  | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da | ffff | ffff     | C, Z, N         |            |

| RRNCF                 | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da | ffff | ffff     | Z, N            |            |

| SETF                  | f, a                            | Set f                                    | 1          | 0110                    | 100a | ffff | ffff     | None            | 1, 2       |

| SUBFWB                | f, d, a                         | Subtract f from WREG with                | 1          | 0101                    | 01da | ffff | ffff     | C, DC, Z, OV, N |            |

|                       |                                 | Borrow                                   |            |                         |      |      |          |                 |            |

| SUBWF                 | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da | ffff | ffff     | C, DC, Z, OV, N | 1, 2       |

| SUBWFB                |                                 | Subtract WREG from f with                | 1          | 0101                    | 10da | ffff | ffff     | C, DC, Z, OV, N |            |

|                       | . ,                             | Borrow                                   |            |                         |      |      |          |                 |            |

| SWAPF                 | f, d, a                         | Swap Nibbles in f                        | 1          | 0011                    | 10da | ffff | ffff     | None            | 4          |

| TSTFSZ                | f. a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110                    | 011a | ffff | ffff     | None            | 1, 2       |

| XORWF                 | , -                             | Exclusive OR WREG with f                 | 1          |                         | 10da | ffff | ffff     |                 | ,          |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

| SLE   | EP                                | Enter Slee                                                     | ep Mode                                                         |                | SUBF     | WB                      | Subtract f fr                                  | om W with Bo                                                                | orrow                      |

|-------|-----------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------|----------------|----------|-------------------------|------------------------------------------------|-----------------------------------------------------------------------------|----------------------------|

| Synta | ax:                               | SLEEP                                                          |                                                                 |                | Syntax   |                         | SUBFWB f                                       | {,d {,a}}                                                                   |                            |

| Oper  | ands:                             | None                                                           |                                                                 |                | Opera    | nds:                    | $0 \leq f \leq 255$                            |                                                                             |                            |

| Oper  | ation:                            | $00h \rightarrow WE$                                           | DT,                                                             |                |          |                         | $d \in [0, 1]$                                 |                                                                             |                            |

|       |                                   |                                                                | postscaler,                                                     |                | Onered   | Han                     | $a \in [0, 1]$<br>(W) - (f) - ( $\overline{C}$ | ) deat                                                                      |                            |

|       |                                   | $1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD}$ |                                                                 |                | Operat   | Affected:               |                                                |                                                                             |                            |

| Statu | s Affected:                       | TO, PD                                                         |                                                                 |                |          |                         | N, OV, C, DC                                   |                                                                             | c                          |

| Enco  | oding:                            | 0000                                                           | 0000 000                                                        | 0 0011         | Encod    | •                       |                                                | 01da fff                                                                    |                            |

| Desc  | cription:                         | cleared. Th<br>is set. The                                     | r-Down status<br>he Time-out st<br>Watchdog Tir<br>are cleared. | atus bit (TO)  | Descri   | ριιοπ.                  | (borrow) from<br>method). If 'd                | ster 'f' and Ca<br>n W (2's compl<br>' is '0', the res<br>, the result is s | lement<br>ult is stored in |

| Word  | le.                               | •                                                              | ssor is put into<br>scillator stoppe                            | •              |          |                         |                                                | e Access Bank<br>BSR is used to                                             | is selected. If select the |

| Cycle |                                   | 1                                                              |                                                                 |                |          |                         | lf 'a' is '0' and                              | d the extended                                                              | d instruction              |

|       | ycle Activity:                    | I                                                              |                                                                 |                |          |                         |                                                |                                                                             | on operates in             |

| QU    | Q1                                | Q2                                                             | Q3                                                              | Q4             |          |                         |                                                | al Offset Addr<br>95 (5Fh). See                                             | 0                          |

|       | Decode                            | No<br>operation                                                | Process<br>Data                                                 | Go to<br>Sleep |          |                         | Section 25.2<br>Bit-Oriented                   | .3 "Byte-Orie<br>Instructions<br>t Mode" for d                              | nted and<br>in Indexed     |

| Exan  | nnlo:                             | SLEEP                                                          |                                                                 |                | Words    | :                       | 1                                              |                                                                             |                            |

|       | Before Instruc                    |                                                                |                                                                 |                | Cycles   | :                       | 1                                              |                                                                             |                            |

|       | $\overline{TO} =$                 | ?                                                              |                                                                 |                | Q Cyc    | cle Activity:           |                                                |                                                                             |                            |

|       | PD =                              | ?                                                              |                                                                 |                |          | Q1                      | Q2                                             | Q3                                                                          | Q4                         |

|       | After Instruction<br>TO =<br>PD = | on<br>1†<br>0                                                  |                                                                 |                |          | Decode                  | Read<br>register 'f'                           | Process<br>Data                                                             | Write to destination       |

|       |                                   | 0                                                              |                                                                 |                | Examp    | <u>ole 1:</u>           | SUBFWB                                         | REG, 1, 0                                                                   |                            |

| † If  | WDT causes                        | wake-up, this b                                                | oit is cleared.                                                 |                | В        | efore Instruc           |                                                |                                                                             |                            |

|       |                                   |                                                                |                                                                 |                |          | REG<br>W                | = 3<br>= 2                                     |                                                                             |                            |

|       |                                   |                                                                |                                                                 |                | Δ        | C<br>fter Instructio    | = 1                                            |                                                                             |                            |

|       |                                   |                                                                |                                                                 |                |          | REG                     | = FF                                           |                                                                             |                            |

|       |                                   |                                                                |                                                                 |                |          | W<br>C                  | = 2<br>= 0                                     |                                                                             |                            |

|       |                                   |                                                                |                                                                 |                |          | Z<br>N                  | = 0                                            | sult is negative                                                            | ۵                          |

|       |                                   |                                                                |                                                                 |                | Examp    |                         | SUBFWB                                         |                                                                             |                            |

|       |                                   |                                                                |                                                                 |                | •        | efore Instruc           |                                                | -, -, -                                                                     |                            |

|       |                                   |                                                                |                                                                 |                |          | REG<br>W                | = 2<br>= 5                                     |                                                                             |                            |

|       |                                   |                                                                |                                                                 |                |          | С                       | = 1                                            |                                                                             |                            |

|       |                                   |                                                                |                                                                 |                | A        | fter Instruction<br>REG | on<br>= 2                                      |                                                                             |                            |

|       |                                   |                                                                |                                                                 |                |          | W                       | = 3                                            |                                                                             |                            |

|       |                                   |                                                                |                                                                 |                |          | C<br>Z                  | = 1<br>= 0                                     |                                                                             |                            |

|       |                                   |                                                                |                                                                 |                | <b>F</b> | N                       | = 0 ; re                                       | sult is positive                                                            |                            |

1 2 0 = =

SUBFWB

Example 3:

Before Instruction REG W C

After Instruction

REG W C Z N

; result is zero

REG, 1, 0

## 26.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK™ Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit<sup>™</sup> 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

## 26.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

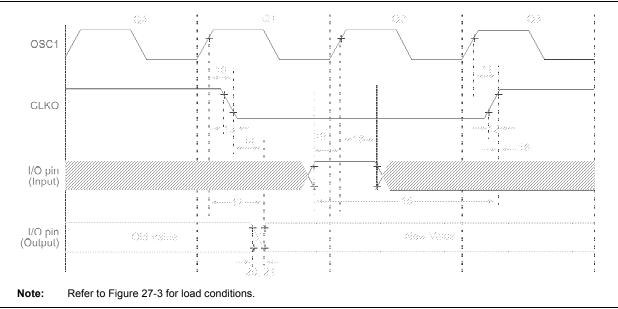

| Param<br>No. | Symbol   | Characteristic                                    | Min           | Тур | Мах          | Units | Conditions |

|--------------|----------|---------------------------------------------------|---------------|-----|--------------|-------|------------|

| 10           | TosH2ckL | OSC1 ↑ to CLKO ↓                                  | —             | 75  | 200          | ns    | (Note 1)   |

| 11           | TosH2ckH | OSC1 ↑ to CLKO ↑                                  | —             | 75  | 200          | ns    | (Note 1)   |

| 12           | TCKR     | CLKO Rise Time                                    | —             | 15  | 30           | ns    | (Note 1)   |

| 13           | ТскF     | CLKO Fall Time                                    | —             | 15  | 30           | ns    | (Note 1)   |

| 14           | TCKL2IOV | CLKO $\downarrow$ to Port Out Valid               | —             | _   | 0.5 Tcy + 20 | ns    |            |

| 15           | ТюV2скН  | Port In Valid before CLKO $\uparrow$              | 0.25 Tcy + 25 | _   | —            | ns    |            |

| 16           | TckH2iol | Port In Hold after CLKO ↑                         | 0             | _   | —            | ns    |            |

| 17           | TosH2IoV | OSC1 $\uparrow$ (Q1 cycle) to Port Out Valid      | —             | 50  | 150          | ns    |            |

| 18           | TosH2iol | OSC1 $\uparrow$ (Q2 cycle) to Port Input Invalid  | 100           | _   | —            | ns    |            |

| 18A          |          | (I/O in hold time)                                | 200           | _   | —            | ns    | VDD = 2.0V |

| 19           | TioV2osH | Port Input Valid to OSC1 ↑<br>(I/O in setup time) | 0             |     | —            | ns    |            |

| 20           | TIOR     | Port Output Rise Time                             | —             | _   | 6            | ns    |            |

| 20A          |          |                                                   | _             | _   | —            | _     |            |

| 21           | TIOF     | Port Output Fall Time                             | —             | _   | 5            | ns    |            |

| 21A          |          |                                                   |               |     | _            |       |            |

| 22†          | TINP     | INTx Pin High or Low Time                         | Тсү           | _   | —            | ns    |            |

| 23†          | Trbp     | RB<7:4> Change INTx High or Low Time              | Тсү           | _   | —            | ns    |            |

**Legend:** TBD = To Be Determined

† These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC mode, where CLKO output is 4 x Tosc.

| Memory Maps                          |   |

|--------------------------------------|---|

| PIC18FX5J10/X5J15/X6J10 Devices69    | 9 |

| PIC18FX6J15/X7J10 Devices70          | 0 |

| Special Function Registers72         | 2 |

| Special Function Registers72         | 2 |

| DAW                                  | 2 |

| DC Characteristics                   | 8 |

| Power-Down and Supply Current        | 1 |

| Supply Voltage                       | 0 |

| DCFSNZ                               | 3 |

| DECF                                 | 2 |

| DECFSZ                               | 3 |

| Development Support                  | 3 |

| Device Overview                      | 5 |

| Details on Individual Family Members | 6 |

| Features (64-Pin Devices)            | 7 |

| Features (80-Pin Devices)            | 7 |

| Direct Addressing                    |   |

### Е

| ECCP                                                 |     |

|------------------------------------------------------|-----|

| Associated Registers                                 | 192 |

| Capture and Compare Modes1                           |     |

| Enhanced PWM Mode1                                   | 81  |

| Standard PWM Mode1                                   |     |

| Effect on Standard PIC MCU Instructions              | 340 |

| Effects of Power-Managed Modes on                    |     |

| Various Clock Sources                                | 37  |

| Electrical Characteristics                           |     |

| Enhanced Capture/Compare/PWM (ECCP)1                 | 177 |

| Capture Mode. See Capture (ECCP Module).             |     |

| ECCP1/ECCP3 Outputs and                              |     |