Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 50                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f66j10t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18F87J10 FAMILY

## 3.0 OSCILLATOR CONFIGURATIONS

## 3.1 Oscillator Types

The PIC18F87J10 family of devices can be operated in five different oscillator modes:

- 1. HS High-Speed Crystal/Resonator

- 2. HSPLL High-Speed Crystal/Resonator with Software PLL Control

- 3. EC External Clock with Fosc/4 Output

- 4. ECPLL External Clock with Software PLL Control

- 5. INTRC Internal 31 kHz Oscillator

Four of these are selected by the user by programming the FOSC<2:0> Configuration bits. The fifth mode (INTRC) may be invoked under software control; it can also be configured as the default mode on device Resets.

## 3.2 Crystal Oscillator/Ceramic Resonators (HS Modes)

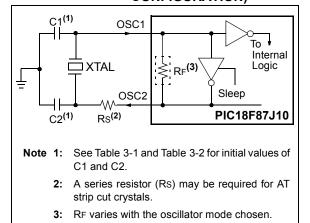

In HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 3-1 shows the pin connections.

The oscillator design requires the use of a parallel cut crystal.

Note: Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

## FIGURE 3-1:

#### CRYSTAL/CERAMIC RESONATOR OPERATION (HS OR HSPLL CONFIGURATION)

## TABLE 3-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Typical Capacitor Values Used: |                     |                |                |  |  |

|--------------------------------|---------------------|----------------|----------------|--|--|

| Mode                           | Freq.               | OSC1           | OSC2           |  |  |

| HS                             | 8.0 MHz<br>16.0 MHz | 27 pF<br>22 pF | 27 pF<br>22 pF |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. **These values are not optimized**.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following Table 3-2 for additional information.

| Resonators Used: |  |  |  |  |  |

|------------------|--|--|--|--|--|

| 4.0 MHz          |  |  |  |  |  |

| 8.0 MHz          |  |  |  |  |  |

| 16.0 MHz         |  |  |  |  |  |

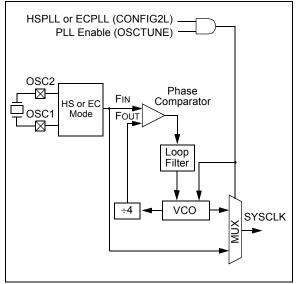

## 3.4 PLL Frequency Multiplier

A Phase Locked Loop (PLL) circuit is provided as an option for users who want to use a lower frequency oscillator circuit, or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals, or users who require higher clock speeds from an internal oscillator. For these reasons, the HSPLL and ECPLL modes are available.

The HSPLL and ECPLL modes provide the ability to selectively run the device at 4 times the external oscillating source to produce frequencies up to 40 MHz. The PLL is enabled by setting the PLLEN bit in the OSCTUNE register (Register 3-1).

#### FIGURE 3-4: PLL BLOCK DIAGRAM

#### REGISTER 3-1: OSCTUNE: PLL CONTROL REGISTER

| U-0   | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|----------------------|-----|-----|-----|-----|-----|-------|

| —     | PLLEN <sup>(1)</sup> |     | —   | —   | —   | —   | —     |

| bit 7 |                      |     |     |     |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 6 PLLEN: Frequency Multiplier PLL Enable bit<sup>(1)</sup>

```

1 = PLL enabled

```

0 = PLL disabled

bit 5-0 Unimplemented: Read as '0'

**Note 1:** Available only for ECPLL and HSPLL oscillator configurations; otherwise, this bit is unavailable and read as '0'.

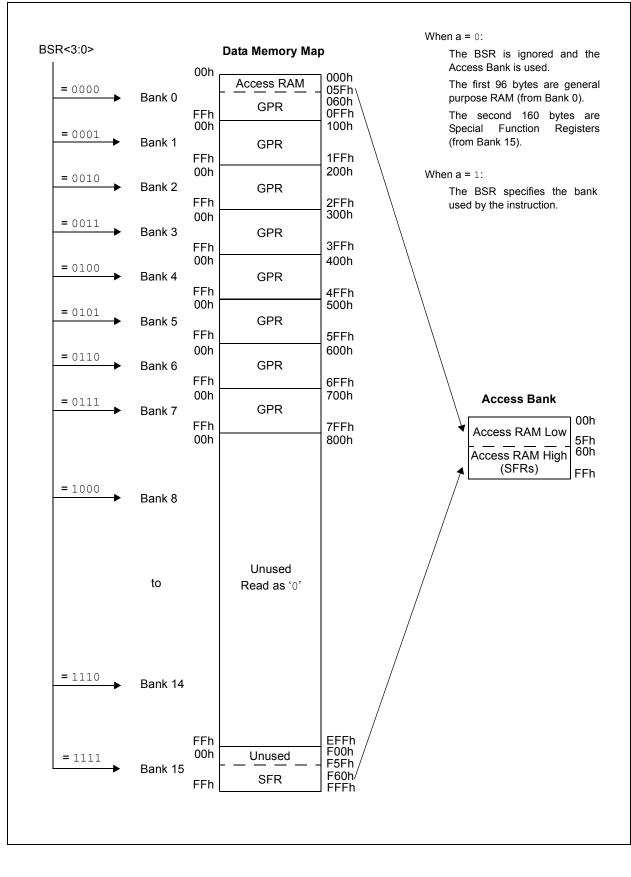

#### FIGURE 6-7: DATA MEMORY MAP FOR PIC18FX5J10/X5J15/X6J10 DEVICES

| File Name             | Bit 7       | Bit 6                | Bit 5               | Bit 4          | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Details<br>on page: |

|-----------------------|-------------|----------------------|---------------------|----------------|--------|--------|--------|--------|----------------------|---------------------|

| TXREG1                | EUSART1 Tr  | ansmit Regist        | er                  |                |        |        | •      |        | XXXX XXXX            | 55, 249,<br>250     |

| TXSTA1                | CSRC        | TX9                  | TXEN                | SYNC           | SENDB  | BRGH   | TRMT   | TX9D   | 0000 0010            | 55, 240             |

| RCSTA1                | SPEN        | RX9                  | SREN                | CREN           | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 55, 241             |

| EECON2                | Program Mer | mory Control F       | Register 2 (not     | a physical reg | ister) |        |        |        |                      | 55                  |

| EECON1                | —           | —                    | —                   | FREE           | WRERR  | WREN   | WR     | —      | 0 x00-               | 55                  |

| IPR3                  | SSP2IP      | BCL2IP               | RC2IP               | TX2IP          | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 1111 1111            | 55, 123             |

| PIR3                  | SSP2IF      | BCL2IF               | RC2IF               | TX2IF          | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 0000 0000            | 55, 117             |

| PIE3                  | SSP2IE      | BCL2IE               | RC2IE               | TX2IE          | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 0000 0000            | 55, 120             |

| IPR2                  | OSCFIP      | CMIP                 |                     | _              | BCL1IP |        | TMR3IP | CCP2IP | 11 1-11              | 55, 121             |

| PIR2                  | OSCFIF      | CMIF                 | _                   | _              | BCL1IF | _      | TMR3IF | CCP2IF | 00 0-00              | 55, 115             |

| PIE2                  | OSCFIE      | CMIE                 | _                   | _              | BCL1IE | _      | TMR3IE | CCP2IE | 00 0-00              | 55, 120             |

| IPR1                  | PSPIP       | ADIP                 | RC1IP               | TX1IP          | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 1111 1111            | 55, 120             |

| PIR1                  | PSPIF       | ADIF                 | RC1IF               | TX1IF          | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 55, 114             |

| PIE1                  | PSPIE       | ADIE                 | RC1IE               | TX1IE          | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 55, 117             |

| MEMCON <sup>(3)</sup> | EBDIS       | _                    | WAIT1               | WAIT0          | -      |        | WM1    | WM0    | 0-0000               | 55, 96              |

| OSCTUNE               | _           | PLLEN <sup>(4)</sup> | _                   | —              | -      | -      | —      | —      | -0                   | 33, 55              |

| TRISJ <sup>(2)</sup>  | TRISJ7      | TRISJ6               | TRISJ5              | TRISJ4         | TRISJ3 | TRISJ2 | TRISJ1 | TRISJ0 | 1111 1111            | 56, 147             |

| TRISH <sup>(2)</sup>  | TRISH7      | TRISH6               | TRISH5              | TRISH4         | TRISH3 | TRISH2 | TRISH1 | TRISH0 | 1111 1111            | 56, 145             |

| TRISG                 | _           | _                    | _                   | TRISG4         | TRISG3 | TRISG2 | TRISG1 | TRISG0 | 1 1111               | 56, 143             |

| TRISF                 | TRISF7      | TRISF6               | TRISF5              | TRISF4         | TRISF3 | TRISF2 | TRISF1 | _      | 1111 111-            | 56, 141             |

| TRISE                 | TRISE7      | TRISE6               | TRISE5              | TRISE4         | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 1111 1111            | 56, 139             |

| TRISD                 | TRISD7      | TRISD6               | TRISD5              | TRISD4         | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 1111 1111            | 56, 136             |

| TRISC                 | TRISC7      | TRISC6               | TRISC5              | TRISC4         | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 56, 133             |

| TRISB                 | TRISB7      | TRISB6               | TRISB5              | TRISB4         | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111            | 56, 130             |

| TRISA                 | _           | _                    | TRISA5              | TRISA4         | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111              | 56, 127             |

| LATJ <sup>(2)</sup>   | LATJ7       | LATJ6                | LATJ5               | LATJ4          | LATJ3  | LATJ2  | LATJ1  | LATJ0  | XXXX XXXX            | 56, 147             |

| LATH <sup>(2)</sup>   | LATH7       | LATH6                | LATH5               | LATH4          | LATH3  | LATH2  | LATH1  | LATH0  | XXXX XXXX            | 56, 145             |

| LATG                  | _           | _                    | _                   | LATG4          | LATG3  | LATG2  | LATG1  | LATG0  | x xxxx               | 56, 143             |

| LATF                  | LATF7       | LATF6                | LATF5               | LATF4          | LATF3  | LATF2  | LATF1  | _      | xxxx xxx-            | 56, 141             |

| LATE                  | LATE7       | LATE6                | LATE5               | LATE4          | LATE3  | LATE2  | LATE1  | LATE0  | xxxx xxxx            | 56, 139             |

| LATD                  | LATD7       | LATD6                | LATD5               | LATD4          | LATD3  | LATD2  | LATD1  | LATD0  | XXXX XXXX            | 56, 136             |

| LATC                  | LATC7       | LATC6                | LATC5               | LATC4          | LATC3  | LATC2  | LATC1  | LATC0  | XXXX XXXX            | 56, 133             |

| LATB                  | LATB7       | LATB6                | LATB5               | LATB4          | LATB3  | LATB2  | LATB1  | LATB0  | XXXX XXXX            | 56, 130             |

| LATA                  | _           | _                    | LATA5               | LATA4          | LATA3  | LATA2  | LATA1  | LATA0  | xx xxxx              | 56, 127             |

| PORTJ <sup>(2)</sup>  | RJ7         | RJ6                  | RJ5                 | RJ4            | RJ3    | RJ2    | RJ1    | RJ0    | XXXX XXXX            | 56, 147             |

| PORTH <sup>(2)</sup>  | RH7         | RH6                  | RH5                 | RH4            | RH3    | RH2    | RH1    | RH0    | 0000 xxxx            | 56, 145             |

| PORTG                 | RDPU        | REPU                 | RJPU <sup>(2)</sup> | RG4            | RG3    | RG2    | RG1    | RG0    | 111x xxxx            | 56, 143             |

| PORTF                 | RF7         | RF6                  | RF5                 | RF4            | RF3    | RF2    | RF1    | _      | x000 000-            | 56, 141             |

| PORTE                 | RE7         | RE6                  | RE5                 | RE4            | RE3    | RE2    | RE1    | RE0    | XXXX XXXX            | 56, 139             |

| PORTD                 | RD7         | RD6                  | RD5                 | RD4            | RD3    | RD2    | RD1    | RD0    | XXXX XXXX            | 56, 136             |

| PORTC                 | RC7         | RC6                  | RC5                 | RC4            | RC3    | RC2    | RC1    | RC0    | xxxx xxxx            | 56, 133             |

| PORTB                 | RB7         | RB6                  | RB5                 | RB4            | RB3    | RB2    | RB1    | RB0    | XXXX XXXX            | 56, 130             |

| PORTA                 |             | _                    | RA5                 | RA4            | RA3    | RA2    | RA1    | RA0    | 0x 0000              | 56, 127             |

|                       | × = unknown |                      |                     |                |        |        | 1      | 1      |                      | , . <b>_</b> .      |

## TABLE 6-4: REGISTER FILE SUMMARY (PIC18F87J10 FAMILY) (CONTINUED)

$\label{eq:logend: Legend: Legend: a generative state of the state of$

**Note 1:** Bit 21 of the PC is only available in Serial Programming modes.

2: These bits and/or registers are only available in 80-pin devices; otherwise, they are unimplemented and read as '0'. Reset values are shown for 80-pin devices.

3: This register and its bits are not implemented in 64-pin devices. In 80-pin devices, the bits are unwritable and read as '0' in Microcontroller mode.

4: The PLLEN bit is available only when either ECPLL or HSPLL Oscillator modes are selected; otherwise, the bit is read as '0'.

5: Reset value is '0' when Two-Speed Start-up is enabled and '1' if disabled.

## REGISTER 7-1: EECON1: EEPROM CONTROL REGISTER 1

| U-0         | U-0 | U-0 | R/W-0 | R/W-x | R/W-0 | R/S-0 | U-0 |

|-------------|-----|-----|-------|-------|-------|-------|-----|

| —           | —   | —   | FREE  | WRERR | WREN  | WR    | —   |

| bit 7 bit 0 |     |     |       |       |       |       |     |

| Legend:           | S = Settable bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | FREE: Flash Erase Enable bit                                                                                                                                                                                                                                                          |

|         | <ul> <li>1 = Erase the program memory block addressed by TBLPTR on the next WR command (cleared by completion of erase operation)</li> <li>0 = Perform write-only</li> </ul>                                                                                                          |

| bit 3   | WRERR: Flash Program Error Flag bit                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal operation or an improper write attempt)</li> <li>0 = The write operation completed</li> </ul>                                                                             |

| bit 2   | WREN: Flash Program Write Enable bit                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Allows write cycles to Flash program memory</li> <li>0 = Inhibits write cycles to Flash program memory</li> </ul>                                                                                                                                                        |

| bit 1   | WR: Write Control bit                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Initiates a program memory erase cycle or write cycle         (The operation is self-timed and the bit is cleared by hardware once the write is complete.         The WR bit can only be set (not cleared) in software.)</li> <li>0 = Write cycle is complete</li> </ul> |

| bit 0   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                            |

## 7.4 Erasing Flash Program Memory

The minimum erase block is 512 words or 1024 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 1024 bytes of program memory is erased. The Most Significant 12 bits of the TBLPTR<21:10> point to the block being erased. TBLPTR<9:0> are ignored.

The EECON1 register commands the erase operation. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation. For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

#### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with the address of the block being erased.

- 2. Set the WREN and FREE bits (EECON1<2,4>) to enable the erase operation.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the erase cycle.

- The CPU will stall for duration of the erase for TIE (see parameter D133B).

- 8. Re-enable interrupts.

| EXAMPLE 7-2: ERASING FLASH PROGRAM MEMO | RY |

|-----------------------------------------|----|

|-----------------------------------------|----|

|             | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | ; load TBLPTR with the base<br>; address of the memory block |

|-------------|----------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|

| ERASE_BLOCK |                                                    |                                                                                     |                                                              |

|             | BSF                                                | EECON1, WREN                                                                        | ; enable write to memory                                     |

|             | BSF                                                | EECON1, FREE                                                                        | ; enable Erase operation                                     |

|             | BCF                                                | INTCON, GIE                                                                         | ; disable interrupts                                         |

| Required    | MOVLW                                              | 55h                                                                                 |                                                              |

| Sequence    | MOVWF                                              | EECON2                                                                              | ; write 55h                                                  |

|             | MOVLW                                              | 0AAh                                                                                |                                                              |

|             | MOVWF                                              | EECON2                                                                              | ; write OAAh                                                 |

|             | BSF                                                | EECON1, WR                                                                          | ; start erase (CPU stall)                                    |

|             | BSF                                                | INTCON, GIE                                                                         | ; re-enable interrupts                                       |

|             |                                                    |                                                                                     |                                                              |

## 8.1 External Memory Bus Control

The operation of the interface is controlled by the MEMCON register (Register 8-1). This register is available in all program memory operating modes except Microcontroller mode. In this mode, the register is disabled and cannot be written to.

The EBDIS bit (MEMCON<7>) controls the operation of the bus and related port functions. Clearing EBDIS enables the interface and disables the I/O functions of the ports, as well as any other functions multiplexed to those pins. Setting the bit enables the I/O ports and other functions, but allows the interface to override everything else on the pins when an external memory operation is required. By default, the external bus is always enabled and disables all other I/O. The operation of the EBDIS bit is also influenced by the program memory mode being used. This is discussed in more detail in Section 8.5 "Program Memory Modes and the External Memory Bus".

The WAIT bits allow for the addition of wait states to external memory operations. The use of these bits is discussed in **Section 8.3 "Wait States"**.

The WM bits select the particular operating mode used when the bus is operating in 16-Bit Data Width mode. These are discussed in more detail in **Section 8.6 "16-Bit Data Width Modes"**. These bits have no effect when an 8-Bit Data Width mode is selected.

## REGISTER 8-1: MEMCON: EXTERNAL MEMORY BUS CONTROL REGISTER

| R/W-0 | U-0 | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-----|-----|-------|-------|

| EBDIS | —   | WAIT1 | WAIT0 | —   | —   | WM1   | WM0   |

| bit 7 |     |       |       |     |     |       | bit 0 |

|       |     |       |       |     |     |       |       |

| Legend:           | S = Settable bit |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | EBDIS: External Bus Disable bit                                                                                                                                                           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = External bus enabled when microcontroller accesses external memory; otherwise, all external bus<br/>drivers are mapped as I/O ports</li> </ul>                               |

|         | 0 = External bus always enabled, I/O ports are disabled                                                                                                                                   |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 5-4 | WAIT<1:0>: Table Reads and Writes Bus Cycle Wait Count bits                                                                                                                               |

|         | 11 = Table reads and writes will wait 0 TCY                                                                                                                                               |

|         | 10 = Table reads and writes will wait 1 Tcy                                                                                                                                               |

|         | 01 = Table reads and writes will wait 2 TCY                                                                                                                                               |

|         | 00 = Table reads and writes will wait 3 TCY                                                                                                                                               |

| bit 3-2 | Unimplemented: Read as '0                                                                                                                                                                 |

| bit 1-0 | WM<1:0>: TBLWT Operation with 16-Bit Data Bus Width Select bits                                                                                                                           |

|         | 1x = Word Write mode: TABLAT0 and TABLAT1 word output; WRH active when TABLAT1 written<br>01 = Byte Select mode: TABLAT data copied on both MSB and LSB; WRH and (UB or LB) will activate |

|         | 00 = Byte Write mode: TABLAT data copied on both MSB and LSB; WRT and (OB of LB) will activate                                                                                            |

|         |                                                                                                                                                                                           |

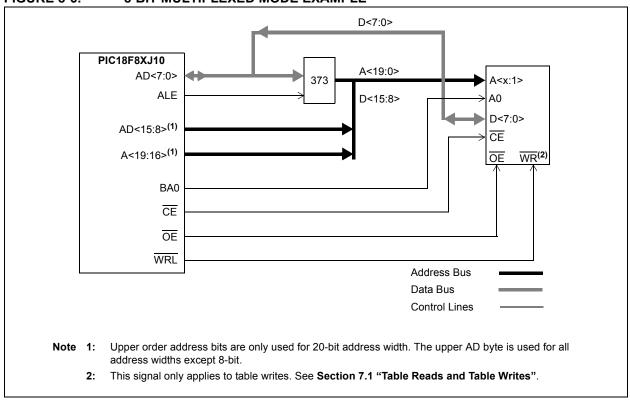

## 8.7 8-Bit Mode

In 8-Bit Data Width mode, the external memory bus operates only in Multiplexed mode; that is, data shares the 8 Least Significant bits of the address bus.

Figure 8-6 shows an example of 8-Bit Multiplexed mode for 80-pin devices. This mode is used for a single 8-bit memory connected for 16-bit operation. The instructions will be fetched as two 8-bit bytes on a shared data/address bus. The two bytes are sequentially fetched within one instruction cycle (TCY). Therefore, the designer must choose external memory devices according to timing calculations based on 1/2 TCY (2 times the instruction rate). For proper memory speed selection, glue logic propagation delay times must be considered, along with setup and hold times.

The Address Latch Enable (ALE) pin indicates that the address bits, AD<15:0>, are available on the external memory interface bus. The Output Enable signal (OE)

will enable one byte of program memory for a portion of the instruction cycle, then BA0 will change and the second byte will be enabled to form the 16-bit instruction word. The Least Significant bit of the address, BA0, must be connected to the memory devices in this mode. The Chip Enable signal ( $\overline{CE}$ ) is active at any time that the microcontroller accesses external memory, whether reading or writing. It is inactive (asserted high) whenever the device is in Sleep mode.

This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories.

During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate level of the BA0 control line is strobed on the LSb of the TBLPTR.

FIGURE 8-6: 8-BIT MULTIPLEXED MODE EXAMPLE

| Name                                           | Bit 7    | Bit 6        | Bit 5       | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|------------------------------------------------|----------|--------------|-------------|---------|--------|--------|--------|--------|----------------------------|

| INTCON                                         | GIE/GIEH | PEIE/GIEL    | TMR0IE      | INT0IE  | RBIE   | TMR0IF | INT0IF | RBIF   | 53                         |

| PIR1                                           | PSPIF    | ADIF         | RC1IF       | TX1IF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 55                         |

| PIE1                                           | PSPIE    | ADIE         | RC1IE       | TX1IE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 55                         |

| IPR1                                           | PSPIP    | ADIP         | RC1IP       | TX1IP   | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 55                         |

| PIR3                                           | SSP2IF   | BCL2IF       | RC2IF       | TX2IF   | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 55                         |

| PIE3                                           | SSP2IE   | BCL2IE       | RC2IE       | TX2IE   | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 55                         |

| IPR3                                           | SSP2IP   | BCL2IP       | RC2IP       | TX2IP   | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 55                         |

| TRISC                                          | TRISC7   | TRISC6       | TRISC5      | TRISC4  | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 56                         |

| TRISD                                          | TRISD7   | TRISD6       | TRISD5      | TRISD4  | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 56                         |

| TRISF                                          | TRISF7   | TRISF6       | TRISF5      | TRISF4  | TRISF3 | TRISF2 | TRISF1 | _      | 56                         |

| SSP1BUF                                        | MSSP1 Re | ceive Buffer | /Transmit R | egister |        |        |        |        | 54                         |

| SSPxCON1                                       | WCOL     | SSPOV        | SSPEN       | CKP     | SSPM3  | SSPM2  | SSPM1  | SSPM0  | 54, 57                     |

| SSPxSTAT                                       | SMP      | CKE          | D/Ā         | Р       | S      | R/W    | UA     | BF     | 54, 57                     |

| SSP2BUF MSSP2 Receive Buffer/Transmit Register |          |              |             |         |        |        | 57     |        |                            |

#### TABLE 19-2: REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: Shaded cells are not used by the MSSP module in SPI mode.

## 20.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of two serial I/O modules. (Generically, the EUSART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN bus) systems.

All members of the PIC18F87J10 family are equipped with two independent EUSART modules, referred to as EUSART1 and EUSART2. They can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-Wake-up on character reception

- Auto-Baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The pins of EUSART1 and EUSART2 are multiplexed with the functions of PORTC (RC6/TX1/CK1 and RC7/RX1/DT1) and PORTG (RG1/TX2/CK2 and RG2/RX2/DT2), respectively. In order to configure these pins as an EUSART:

- For EUSART1:

- bit, SPEN (RCSTA1<7>), must be set (= 1)

- bit, TRISC<7>, must be set (= 1)

- bit, TRISC<6>, must be cleared (= 0) for Asynchronous and Synchronous Master modes

- bit, TRISC<6>, must be set (= 1) for Synchronous Slave mode

- For EUSART2:

- bit, SPEN (RCSTA2<7>), must be set (= 1)

- bit, TRISG<2>, must be set (= 1)

- bit, TRISG<1>, must be cleared (= 0) for Asynchronous and Synchronous Master modes

- bit, TRISC<6> must be set (= 1) for Synchronous Slave mode

Note: The EUSART control will automatically reconfigure the pin from input to output as needed.

The operation of each Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTAx)

- Receive Status and Control (RCSTAx)

- Baud Rate Control (BAUDCONx)

These are detailed on the following pages in Register 20-1, Register 20-2 and Register 20-3, respectively.

Note: Throughout this section, references to register and bit names that may be associated with a specific EUSART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "RCSTAx" might refer to the Receive Status register for either EUSART1 or EUSART2.

## 21.2 Selecting and Configuring Automatic Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the  $GO/\overline{DONE}$  bit is set.

When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit. This occurs when the ACQT<2:0> bits (ADCON2<5:3>) remain in their Reset state ('000') and is compatible with devices that do not offer programmable acquisition times.

If desired, the ACQT bits can be set to select a programmable acquisition time for the A/D module. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

## 21.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 11 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable.

There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible but greater than the minimum TAD (see parameter 130 in Table 27-27 for more information).

Table 21-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

#### TABLE 21-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock S        | Maximum   |                         |

|-------------------|-----------|-------------------------|

| Operation         | ADCS<2:0> | Device<br>Frequency     |

| 2 Tosc            | 000       | 2.86 MHz                |

| 4 Tosc            | 100       | 5.71 MHz                |

| 8 Tosc            | 001       | 11.43 MHz               |

| 16 Tosc           | 101       | 22.86 MHz               |

| 32 Tosc           | 010       | 40.0 MHz                |

| 64 Tosc           | 110       | 40.0 MHz                |

| RC <sup>(2)</sup> | x11       | 1.00 MHz <sup>(1)</sup> |

Note 1: The RC source has a typical TAD time of  $4 \ \mu s$ .

2: For device frequencies above 1 MHz, the device must be in Sleep mode for the entire conversion or the A/D accuracy may be out of specification.

## 21.4 Configuring Analog Port Pins

The ADCON1, TRISA, TRISF and TRISH registers control the operation of the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<3:0> bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will be accurately converted.

- 2: Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

# PIC18F87J10 FAMILY

| CPFS        | SGT                                                                                                                                                                                                                                                                                 | Compare f                                   | with W, Skip                                                                                                                                                                | if f > W  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|

| Synta       | ax:                                                                                                                                                                                                                                                                                 | CPFSGT                                      | CPFSGT f {,a}                                                                                                                                                               |           |  |  |  |  |

| -           | ands:                                                                                                                                                                                                                                                                               | 0 ≤ f ≤ 255                                 | • •                                                                                                                                                                         |           |  |  |  |  |

|             |                                                                                                                                                                                                                                                                                     | a ∈ [0,1]                                   |                                                                                                                                                                             |           |  |  |  |  |

| Oper        | ation:                                                                                                                                                                                                                                                                              | (f) – (W),                                  |                                                                                                                                                                             |           |  |  |  |  |

|             |                                                                                                                                                                                                                                                                                     | skip if (f) > (                             | (W)                                                                                                                                                                         |           |  |  |  |  |

|             |                                                                                                                                                                                                                                                                                     | (unsigned c                                 | omparison)                                                                                                                                                                  |           |  |  |  |  |

| Statu       | s Affected:                                                                                                                                                                                                                                                                         | None                                        |                                                                                                                                                                             |           |  |  |  |  |

| Enco        | ding:                                                                                                                                                                                                                                                                               | 0110                                        | 010a fff                                                                                                                                                                    | f ffff    |  |  |  |  |

| Desc        | ription:                                                                                                                                                                                                                                                                            | location 'f' t                              | Compares the contents of data memory<br>location 'f' to the contents of the W by<br>performing an unsigned subtraction.                                                     |           |  |  |  |  |

|             |                                                                                                                                                                                                                                                                                     | contents of<br>instruction i<br>executed in | If the contents of 'f' are greater than the contents of WREG, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. |           |  |  |  |  |

|             |                                                                                                                                                                                                                                                                                     | ,                                           | he Access Bar<br>he BSR is use                                                                                                                                              |           |  |  |  |  |

|             | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operate<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                             |                                                                                                                                                                             |           |  |  |  |  |

| Word        | s:                                                                                                                                                                                                                                                                                  | 1                                           | 1                                                                                                                                                                           |           |  |  |  |  |

| Cycle       | es:                                                                                                                                                                                                                                                                                 |                                             |                                                                                                                                                                             |           |  |  |  |  |

| QC          | cle Activity:                                                                                                                                                                                                                                                                       |                                             |                                                                                                                                                                             |           |  |  |  |  |

|             | Q1                                                                                                                                                                                                                                                                                  | Q2                                          | Q3                                                                                                                                                                          | Q4        |  |  |  |  |

|             | Decode                                                                                                                                                                                                                                                                              | Read                                        | Process                                                                                                                                                                     | No        |  |  |  |  |

| الم ال      |                                                                                                                                                                                                                                                                                     | register 'f'                                | Data                                                                                                                                                                        | operation |  |  |  |  |

| lf sk       | ip:                                                                                                                                                                                                                                                                                 | 02                                          | 03                                                                                                                                                                          | 04        |  |  |  |  |

|             | No                                                                                                                                                                                                                                                                                  | Q2<br>No                                    | Q3<br>No                                                                                                                                                                    | Q4<br>No  |  |  |  |  |

|             | operation                                                                                                                                                                                                                                                                           | operation                                   | operation                                                                                                                                                                   | operation |  |  |  |  |

| lf sk       |                                                                                                                                                                                                                                                                                     | d by 2-word in                              | •                                                                                                                                                                           |           |  |  |  |  |

|             | Q1                                                                                                                                                                                                                                                                                  | Q2                                          | Q3                                                                                                                                                                          | Q4        |  |  |  |  |

|             | No                                                                                                                                                                                                                                                                                  | No                                          | No                                                                                                                                                                          | No        |  |  |  |  |

|             | operation                                                                                                                                                                                                                                                                           | operation                                   | operation                                                                                                                                                                   | operation |  |  |  |  |

|             | No                                                                                                                                                                                                                                                                                  | No                                          | No                                                                                                                                                                          | No        |  |  |  |  |

|             | operation                                                                                                                                                                                                                                                                           | operation                                   | operation                                                                                                                                                                   | operation |  |  |  |  |

| <u>Exam</u> | nple:                                                                                                                                                                                                                                                                               | HERE<br>NGREATER<br>GREATER                 | CPFSGT RE<br>:<br>:                                                                                                                                                         | G, 0      |  |  |  |  |

|             | Before Instruc                                                                                                                                                                                                                                                                      | tion                                        |                                                                                                                                                                             |           |  |  |  |  |

|             | PC<br>W                                                                                                                                                                                                                                                                             | = Ad<br>= ?                                 | dress (HERE)                                                                                                                                                                | )         |  |  |  |  |

|             | After Instructic                                                                                                                                                                                                                                                                    | •                                           |                                                                                                                                                                             |           |  |  |  |  |

|             | PC                                                                                                                                                                                                                                                                                  | = Ad                                        | dress (GREAT                                                                                                                                                                | TER)      |  |  |  |  |

|             | If REG<br>PC                                                                                                                                                                                                                                                                        |                                             | dress (NGREA                                                                                                                                                                | ATER)     |  |  |  |  |

| CPF                                                                             | SLT              | Compare f                                 | with W, Ski                                                                                                                                                           | ip if f < W                                   |  |  |  |

|---------------------------------------------------------------------------------|------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|--|--|

| Synt                                                                            | ax:              | CPFSLT                                    | f {,a}                                                                                                                                                                |                                               |  |  |  |

| Oper                                                                            | rands:           | 0≤f≤255<br>a∈[0,1]                        |                                                                                                                                                                       |                                               |  |  |  |

| Oper                                                                            | ration:          | (f) – (W),<br>skip if (f) <               |                                                                                                                                                                       |                                               |  |  |  |

| Statu                                                                           | is Affected:     | None                                      |                                                                                                                                                                       |                                               |  |  |  |

| Enco                                                                            | oding:           | 0110                                      | 000a f                                                                                                                                                                | fff ffff                                      |  |  |  |

| Desc                                                                            | cription:        | location 'f'                              | to the conter                                                                                                                                                         | of data memory<br>hts of W by<br>subtraction. |  |  |  |

|                                                                                 |                  | contents of<br>instruction<br>executed ir | If the contents of 'f' are less than the contents of W, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. |                                               |  |  |  |

|                                                                                 |                  |                                           | the BSR is us                                                                                                                                                         | ank is selected.<br>sed to select the         |  |  |  |

| Word                                                                            | ds:              | 1                                         |                                                                                                                                                                       |                                               |  |  |  |

| Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction. |                  |                                           |                                                                                                                                                                       |                                               |  |  |  |

| QC                                                                              | cycle Activity:  | 00                                        | 00                                                                                                                                                                    | 04                                            |  |  |  |

|                                                                                 | Q1<br>Decode     | Q2<br>Read                                | Q3<br>Process                                                                                                                                                         | Q4<br>No                                      |  |  |  |

|                                                                                 | Decoue           | register 'f'                              | Data                                                                                                                                                                  | operation                                     |  |  |  |

| lf sk                                                                           | kip:             | <u> </u>                                  |                                                                                                                                                                       |                                               |  |  |  |

|                                                                                 | Q1               | Q2                                        | Q3                                                                                                                                                                    | Q4                                            |  |  |  |

|                                                                                 | No               | No                                        | No                                                                                                                                                                    | No                                            |  |  |  |

|                                                                                 | operation        | operation                                 | operation                                                                                                                                                             | operation                                     |  |  |  |

| lf sk                                                                           | tip and followed | 3                                         |                                                                                                                                                                       | _                                             |  |  |  |

|                                                                                 | Q1               | Q2                                        | Q3                                                                                                                                                                    | Q4                                            |  |  |  |

|                                                                                 | No<br>operation  | No<br>operation                           | No<br>operation                                                                                                                                                       | No<br>operation                               |  |  |  |

|                                                                                 | No               | No                                        | No                                                                                                                                                                    | No                                            |  |  |  |

|                                                                                 | operation        | operation                                 | operation                                                                                                                                                             | operation                                     |  |  |  |

| <u>Exar</u>                                                                     | nple:            |                                           | CPFSLT RE                                                                                                                                                             | G, 1                                          |  |  |  |

| Before Instruction                                                              |                  |                                           |                                                                                                                                                                       |                                               |  |  |  |

|                                                                                 | PC               |                                           | dress (HEF                                                                                                                                                            | RE)                                           |  |  |  |

| W = ?                                                                           |                  |                                           |                                                                                                                                                                       |                                               |  |  |  |

| After Instruction<br>If REG < W;                                                |                  |                                           |                                                                                                                                                                       |                                               |  |  |  |

|                                                                                 | PC               | = Ac                                      | dress (LES                                                                                                                                                            | SS)                                           |  |  |  |

|                                                                                 | If REG<br>PC     | ≥ W<br>= Ac                               | ;<br><b>dress</b> (NLE                                                                                                                                                | SS)                                           |  |  |  |

|                                                                                 |                  | 7.0                                       |                                                                                                                                                                       | ,                                             |  |  |  |

## 25.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, the PIC18F87J10 family of devices also provide an optional extension to the core CPU functionality. The added features include eight additional instructions that augment Indirect and Indexed Addressing operations and the implementation of Indexed Literal Offset Addressing for many of the standard PIC18 instructions.

The additional features of the extended instruction set are disabled by default on unprogrammed devices. Users must properly set or clear the XINST Configuration bit during programming to enable or disable these features.

The instructions in the extended set can all be classified as literal operations, which either manipulate the File Select Registers, or use them for Indexed Addressing. Two of the instructions, ADDFSR and SUBFSR, each have an additional special instantiation for using FSR2. These versions (ADDULNK and SUBULNK) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- dynamic allocation and deallocation of software stack space when entering and leaving subroutines

- function pointer invocation

- software Stack Pointer manipulation

- manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 25-3. Detailed descriptions are provided in **Section 25.2.2 "Extended Instruction Set"**. The opcode field descriptions in Table 25-1 (page 294) apply to both the standard and extended PIC18 instruction sets.

Note: The instruction set extension and the Indexed Literal Offset Addressing mode were designed for optimizing applications written in C; the user may likely never use these instructions directly in assembler. The syntax for these commands is provided as a reference for users who may be reviewing code that has been generated by a compiler.

## 25.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of Indexed Addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. The MPASM<sup>™</sup> Assembler will flag an error if it determines that an index or offset value is not bracketed.

When the extended instruction set is enabled, brackets are also used to indicate index arguments in byte-oriented and bit-oriented instructions. This is in addition to other changes in their syntax. For more details, see Section 25.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands".

Note: In the past, square brackets have been used to denote optional arguments in the PIC18 and earlier instruction sets. In this text and going forward, optional arguments are denoted by braces ("{ }").

| Mnemonic, |                                 | Description                              | Cycles | 16-Bit Instruction Word |      |         |      | Status   |

|-----------|---------------------------------|------------------------------------------|--------|-------------------------|------|---------|------|----------|

| Opera     | nds                             | Description                              | Cycles | MSb                     |      |         | LSb  | Affected |

| ADDFSR    | f, k                            | Add Literal to FSR                       | 1      | 1110                    | 1000 | ffkk    | kkkk | None     |

| ADDULNK   | k                               | Add Literal to FSR2 and Return           | 2      | 1110                    | 1000 | 11kk    | kkkk | None     |

| CALLW     |                                 | Call Subroutine using WREG               | 2      | 0000                    | 0000 | 0001    | 0100 | None     |

| MOVSF     | z <sub>s</sub> , f <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110                    | 1011 | 0 z z z | ZZZZ | None     |

|           |                                 | f <sub>d</sub> (destination) 2nd word    |        | 1111                    | ffff | ffff    | ffff |          |

| MOVSS     | z <sub>s</sub> , z <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110                    | 1011 | 1zzz    | ZZZZ | None     |

|           |                                 | z <sub>d</sub> (destination) 2nd word    |        | 1111                    | XXXX | XZZZ    | ZZZZ |          |

| PUSHL     | k                               | Store Literal at FSR2,                   | 1      | 1110                    | 1010 | kkkk    | kkkk | None     |

|           |                                 | Decrement FSR2                           |        |                         |      |         |      |          |

| SUBFSR    | f, k                            | Subtract Literal from FSR                | 1      | 1110                    | 1001 | ffkk    | kkkk | None     |

| SUBULNK   | k                               | Subtract Literal from FSR2 and           | 2      | 1110                    | 1001 | 11kk    | kkkk | None     |

|           |                                 | Return                                   |        |                         |      |         |      |          |

#### TABLE 25-3: EXTENSIONS TO THE PIC18 INSTRUCTION SET

# PIC18F87J10 FAMILY

| MOVSS                                                             | Move Indexed to Indexed                                                                                                                                                                                                                                                                           |  |  |  |  |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|