Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 66                                                                         |

| Program Memory Size        | 48KB (24K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 15x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f85j15-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.0 RESET

The PIC18F87J10 family of devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR and covers the operation of the various start-up timers. Stack Reset events are covered in Section 6.1.6.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 24.2 "Watchdog Timer (WDT)".

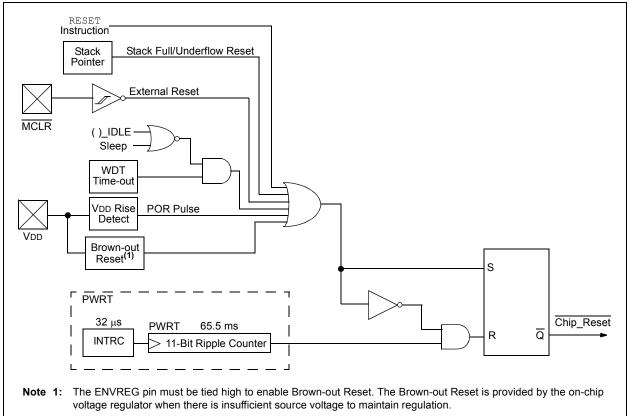

A simplified block diagram of the on-chip Reset circuit is shown in Figure 5-1.

## 5.1 RCON Register

Device Reset events are tracked through the RCON register (Register ). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be set by the event and must be cleared by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 5.6 "Reset State of Registers"**.

The RCON register also has a control bit for setting interrupt priority (IPEN). Interrupt priority is discussed in **Section 10.0 "Interrupts"**.

### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# 9.0 8 x 8 HARDWARE MULTIPLIER

### 9.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 9-1.

## 9.2 Operation

Example 9-1 shows the instruction sequence for an 8 x 8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 9-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

### EXAMPLE 9-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ; |                |

|-------|-------|---|---|----------------|

| MULWF | ARG2  |   | ; | ARG1 * ARG2 -> |

|       |       |   | ; | PRODH: PRODL   |

|       |       |   |   |                |

#### EXAMPLE 9-2: 8 x 8 SIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, W  |   |                |

|-------|----------|---|----------------|

| MULWF | ARG2     | ; | ARG1 * ARG2 -> |

|       |          | ; | PRODH:PRODL    |

| BTFSC | ARG2, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG1         |

| MOVF  | ARG2, W  |   |                |

| BTFSC | ARG1, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG2         |

|       |          |   |                |

|                  |                           | Program           | Cycles | Time     |          |         |  |

|------------------|---------------------------|-------------------|--------|----------|----------|---------|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

|                  | Without Hardware Multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 μs   |  |

| 8 x 8 unsigned   | Hardware Multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs    |  |

|                  | Without Hardware Multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs   |  |

| 8 x 8 signed     | Hardware Multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 μs    |  |

| 16 x 16 uppigned | Without Hardware Multiply | 21                | 242    | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| 16 x 16 unsigned | Hardware Multiply         | 28                | 28     | 2.8 μs   | 11.2 μs  | 28 μs   |  |

| 16 x 16 signed   | Without Hardware Multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs  |  |

| 16 x 16 signed   | Hardware Multiply         | 35                | 40     | 4.0 μs   | 16.0 μs  | 40 μs   |  |

### TABLE 9-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

## REGISTER 10-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| R/W-0         | R/W-0        | U-0                | U-0              | R/W-0                             | U-0             | R/W-0            | R/W-0  |

|---------------|--------------|--------------------|------------------|-----------------------------------|-----------------|------------------|--------|

| OSCFIF        | CMIF         |                    | _                | BCL1IF                            | _               | TMR3IF           | CCP2IF |

| bit 7         |              |                    |                  |                                   |                 |                  | bit (  |

|               |              |                    |                  |                                   |                 |                  |        |

| Legend:       |              |                    |                  |                                   |                 |                  |        |

| R = Readabl   |              | W = Writable       |                  | •                                 | nented bit, rea |                  |        |

| -n = Value at | POR          | '1' = Bit is set   |                  | '0' = Bit is cle                  | ared            | x = Bit is unkr  | nown   |

| bit 7         |              | cillator Fail Inte | rrunt Elag hit   |                                   |                 |                  |        |

|               |              |                    |                  | as changed to I                   | NTRC (must b    | e cleared in sof | tware) |

|               |              | clock operating    | ·                | 0                                 | ,               |                  | ,      |

| bit 6         | CMIF: Comp   | arator Interrupt   | Flag bit         |                                   |                 |                  |        |

|               |              |                    |                  | t be cleared in s                 | software)       |                  |        |

|               | 0 = Compar   | ator input has r   | ot changed       |                                   |                 |                  |        |

| bit 5-4       | •            | nted: Read as '    |                  |                                   |                 |                  |        |

| bit 3         | BCL1IF: Bus  | Collision Inter    | rupt Flag bit (I | MSSP1 module                      | )               |                  |        |

|               |              | ollision occurred  | •                | ared in software                  | e)              |                  |        |

| bit 2         | Unimpleme    | nted: Read as '    | 0'               |                                   |                 |                  |        |

| bit 1         | TMR3IF: TM   | R3 Overflow In     | terrupt Flag b   | it                                |                 |                  |        |

|               |              | egister overflow   |                  | cleared in softwa                 | are)            |                  |        |

| bit 0         |              | CP2 Interrupt F    |                  |                                   |                 |                  |        |

|               | Capture mod  | •                  |                  |                                   |                 |                  |        |

|               | 1 = A TMR1   |                    | •                | rred (must be c<br>:urred         | leared in softv | vare)            |        |

|               | Compare mo   | ode:               |                  |                                   |                 |                  |        |

|               |              |                    |                  | tch occurred (m<br>match occurred |                 | l in software)   |        |

|               | PWM mode:    |                    |                  |                                   |                 |                  |        |

|               | Unused in th | ic modo            |                  |                                   |                 |                  |        |

| Pin Name   | Function           | TRIS<br>Setting | I/O | I/O Type             | Description                                                                               |

|------------|--------------------|-----------------|-----|----------------------|-------------------------------------------------------------------------------------------|

| RD6/AD6/   | RD6                | 0               | 0   | DIG                  | LATD<6> data output.                                                                      |

| PSP6/SCK2/ |                    | 1               | Ι   | ST                   | PORTD<6> data input.                                                                      |

| SCL2       | AD6 <sup>(2)</sup> | x               | 0   | DIG-3                | External memory interface, address/data bit 6 output. <sup>(1)</sup>                      |

|            |                    | х               | Ι   | TTL                  | External memory interface, data bit 6 input. <sup>(1)</sup>                               |

|            | PSP6               | х               | 0   | DIG                  | PSP read output data (LATD<6>); takes priority over port data.                            |

|            |                    | x               | Ι   | TTL                  | PSP write data input.                                                                     |

|            | SCK2               | 0               | 0   | DIG                  | SPI clock output (MSSP2 module); takes priority over port data.                           |

|            |                    | 1               | I   | ST                   | SPI clock input (MSSP2 module).                                                           |

|            | SCL2               | 0               | 0   | DIG                  | I <sup>2</sup> C <sup>™</sup> clock output (MSSP2 module); takes priority over port data. |

|            |                    | 1               | Ι   | I <sup>2</sup> C/SMB | I <sup>2</sup> C clock input (MSSP2 module); input type depends on module setting.        |

| RD7/AD7/   | RD7                | 0               | 0   | DIG                  | LATD<7> data output.                                                                      |

| PSP7/SS2   |                    | 1               | I   | ST                   | PORTD<7> data input.                                                                      |

|            | AD7 <sup>(2)</sup> | x               | 0   | DIG                  | External memory interface, address/data bit 7 output. <sup>(1)</sup>                      |

|            |                    | x               | Ι   | TTL                  | External memory interface, data bit 7 input. <sup>(1)</sup>                               |

|            | PSP7               | х               | 0   | DIG                  | PSP read output data (LATD<7>); takes priority over port data.                            |

|            |                    | х               | I   | TTL                  | PSP write data input.                                                                     |

|            | SS2                | х               | I   | TTL                  | Slave select input for MSSP (MSSP2 module).                                               |

### TABLE 11-9: PORTD FUNCTIONS (CONTINUED)

Legend: PWR = Power Supply, O = Output, I = Input, I<sup>2</sup>C™/SMB = I<sup>2</sup>C/SMBus input buffer, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: External memory interface I/O takes priority over all other digital and PSP I/O.

2: Available on 80-pin devices only.

### TABLE 11-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Name  | Bit 7  | Bit 6  | Bit 5               | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|-------|--------|--------|---------------------|--------|--------|--------|--------|--------|----------------------------|

| PORTD | RD7    | RD6    | RD5                 | RD4    | RD3    | RD2    | RD1    | RD0    | 56                         |

| LATD  | LATD7  | LATD6  | LATD5               | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | 56                         |

| TRISD | TRISD7 | TRISD6 | TRISD5              | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 56                         |

| PORTG | RDPU   | REPU   | RJPU <sup>(1)</sup> | RG4    | RG3    | RG2    | RG1    | RG0    | 56                         |

**Legend:** Shaded cells are not used by PORTD.

**Note 1:** Unimplemented on 64-pin devices, read as '0'.

# 11.7 PORTF, LATF and TRISF Registers

PORTF is a 7-bit wide, bidirectional port. The corresponding Data Direction register is TRISF. Setting a TRISF bit (= 1) will make the corresponding PORTF pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISF bit (= 0) will make the corresponding PORTF pin an output (i.e., put the contents of the output latch on the selected pin). Only pin 7 of PORTF has no analog input; it is the only pin that can tolerate voltages up to 5.5V.

The Output Latch register (LATF) is also memory mapped. Read-modify-write operations on the LATF register read and write the latched output value for PORTF.

All pins on PORTF are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

PORTF is multiplexed with several analog peripheral functions, including the A/D Converter and comparator inputs, as well as the comparator outputs. Pins, RF2 through RF6, may be used as comparator inputs or outputs by setting the appropriate bits in the CMCON register. To use RF<6:3> as digital inputs, it is also necessary to turn off the comparators.

- Note 1: On device Resets, pins, RF<6:1>, are configured as analog inputs and are read as '0'.

- **2:** To configure PORTF as digital I/O, turn off comparators and set ADCON1 value.

#### EXAMPLE 11-6: INITIALIZING PORTF

| CLRF PORTF   | ; Initialize FORTF by<br>; clearing output<br>: data latches   |

|--------------|----------------------------------------------------------------|

| CLRF LATF    | <pre>; Alternate method ; to clear output ; data latches</pre> |

| MOVLW 07h    | ;                                                              |

| MOVWF CMCON  | ; Turn off comparators                                         |

| MOVLW OFh;   |                                                                |

| MOVWF ADCON1 | ; Set PORTF as digital I/O                                     |

| MOVLW OCEh   | ; Value used to                                                |

|              | ; initialize data                                              |

|              | ; direction                                                    |

| MOVWF TRISF  | ; Set RF3:RF1 as inputs                                        |

|              | ; RF5:RF4 as outputs                                           |

|              | ; RF7:RF6 as inputs                                            |

|              |                                                                |

# 11.9 PORTH, LATH and TRISH Registers

| ſ | Note: | PORTH    | is | available | only | on | 80-pin |

|---|-------|----------|----|-----------|------|----|--------|

|   |       | devices. |    |           |      |    |        |

PORTH is an 8-bit wide, bidirectional I/O port. The corresponding Data Direction register is TRISH. Setting a TRISH bit (= 1) will make the corresponding PORTH pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISH bit (= 0) will make the corresponding PORTH pin an output (i.e., put the contents of the output latch on the selected pin). PORTH<3:0> pins are digital only and tolerate voltages up to 5.5V.

The Output Latch register (LATH) is also memory mapped. Read-modify-write operations on the LATH register read and write the latched output value for PORTH.

All pins on PORTH are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output. When the external memory interface is enabled, four of the PORTH pins function as the high-order address lines for the interface. The address output from the interface takes priority over other digital I/O. The corresponding TRISH bits are also overridden.

PORTH pins, RH4 through RH7, are multiplexed with analog converter inputs. The operation of these pins as analog inputs is selected by clearing or setting the PCFG<3:0> control bits in the ADCON1 register.

PORTH can also be configured as the alternate Enhanced PWM output Channels B and C for the ECCP1 and ECCP3 modules. This is done by clearing the ECCPMX Configuration bit.

| EXAMP | LE 11-8: | INITIALIZING PORTH      |

|-------|----------|-------------------------|

| CLRF  | PORTH    | ; Initialize PORTH by   |

|       |          | ; clearing output       |

|       |          | ; data latches          |

| CLRF  | LATH     | ; Alternate method      |

|       |          | ; to clear output       |

|       |          | ; data latches          |

| MOVLW | OFh      | ; Configure PORTH as    |

| MOVWF | ADCON1   | ; digital I/O           |

| MOVLW | OCFh     | ; Value used to         |

|       |          | ; initialize data       |

|       |          | ; direction             |

| MOVWF | TRISH    | ; Set RH3:RH0 as inputs |

|       |          | ; RH5:RH4 as outputs    |

|       |          | ; RH7:RH6 as inputs     |

|       |          |                         |

# 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 13-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 13-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 13-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

## REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:      |                                          |                                                                                     |                                                              |                    |

|--------------|------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|

| R = Readal   | ble bit                                  | W = Writable bit                                                                    | U = Unimplemented bit,                                       | read as '0'        |

| -n = Value a | at POR                                   | '1' = Bit is set                                                                    | '0' = Bit is cleared                                         | x = Bit is unknowr |

| bit 7        | <b>RD16:</b> 16                          | -Bit Read/Write Mode Enal                                                           | ble bit                                                      |                    |

|              |                                          | -                                                                                   | mer1 in one 16-bit operation<br>mer1 in two 8-bit operations |                    |

| bit 6        | T1RUN:                                   | Fimer1 System Clock Status                                                          | s bit                                                        |                    |

|              |                                          | ce clock is derived from Tim<br>ce clock is derived from and                        |                                                              |                    |

| bit 5-4      | T1CKPS                                   | <1:0>: Timer1 Input Clock F                                                         | Prescale Select bits                                         |                    |

|              | 10 = 1:4<br>01 = 1:2                     | Prescale value<br>Prescale value<br>Prescale value<br>Prescale value                |                                                              |                    |

| bit 3        |                                          | N: Timer1 Oscillator Enable                                                         | bit                                                          |                    |

|              | 0 = Time                                 | r1 oscillator is enabled<br>r1 oscillator is shut off<br>ator inverter and feedback | resistor are turned off to elimin                            | ate power drain    |

| bit 2        |                                          |                                                                                     | ut Synchronization Select bit                                |                    |

|              | <u>When TN</u><br>1 = Do no<br>0 = Syncl | I <u>R1CS = 1:</u><br>ot synchronize external cloc<br>nronize external clock input  | k input                                                      |                    |

|              |                                          | I <u>R1CS = 0:</u><br>ignored. Timer1 uses the i                                    | nternal clock when TMR1CS =                                  | 0.                 |

| bit 1        | TMR1CS                                   | : Timer1 Clock Source Sele                                                          | ect bit                                                      |                    |

|              |                                          | nal clock from the RC0/T10<br>nal clock (Fosc/4)                                    | DSO/T13CKI pin (on the rising                                | edge)              |

| bit 0        | TMR10N                                   | : Timer1 On bit                                                                     |                                                              |                    |

|              | 1 = Enat<br>0 = Stops                    | les Timer1<br>s Timer1                                                              |                                                              |                    |

## REGISTER 19-2: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

| R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|----------------------|-------|-------|-------|-------|-------|-------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit 7 |                      |       |       | •     |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | WCOL: Write Collision Detect bit                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = The SSPxBUF register is written while it is still transmitting the previous word<br/>(must be cleared in software)</li> </ul>                                                                                                                                                                                                                                                                                 |

|         | 0 = No collision                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 6   | SSPOV: Receive Overflow Indicator bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>SPI Slave mode:</li> <li>1 = A new byte is received while the SSPxBUF register is still holding the previous data. In case of overflow, the data in SSPxSR is lost. Overflow can only occur in Slave mode. The user must read the SSPxBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software).</li> <li>0 = No overflow</li> </ul>                                           |

| bit 5   | SSPEN: Master Synchronous Serial Port Enable bit                                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Enables serial port and configures SCKx, SDOx, SDIx and SSx as serial port pins<sup>(2)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins<sup>(2)</sup></li> </ul>                                                                                                                                                                                                           |

| bit 4   | CKP: Clock Polarity Select bit                                                                                                                                                                                                                                                                                                                                                                                             |

|         | <ul> <li>1 = Idle state for clock is a high level</li> <li>0 = Idle state for clock is a low level</li> </ul>                                                                                                                                                                                                                                                                                                              |

| bit 3-0 | SSPM<3:0>: Master Synchronous Serial Port Mode Select bits                                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>0101 = SPI Slave mode, clock = SCKx pin, SSx pin control disabled, SSx can be used as I/O pin<sup>(3)</sup></li> <li>0100 = SPI Slave mode, clock = SCKx pin, SSx pin control enabled<sup>(3)</sup></li> <li>0011 = SPI Master mode, clock = TMR2 output/2<sup>(3)</sup></li> <li>0010 = SPI Master mode, clock = Fosc/64<sup>(3)</sup></li> <li>0001 = SPI Master mode, clock = Fosc/16<sup>(3)</sup></li> </ul> |

|         | 0001 = SPI Master mode, clock = FOSC/16(3)0000 = SPI Master mode, clock = FOSC/4(3)                                                                                                                                                                                                                                                                                                                                        |

|         | In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPxBUF register.                                                                                                                                                                                                                                                                                   |

- 2: When enabled, these pins must be properly configured as input or output.

- **3:** Bit combinations not specifically listed here are either reserved or implemented in I<sup>2</sup>C mode only.

### 19.3.5 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCKx. The master determines when the slave (Processor 1, Figure 19-2) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDOx output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDIx pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode.

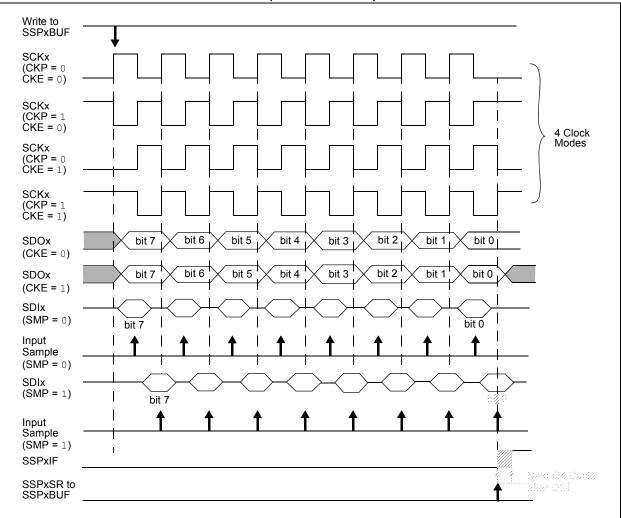

The clock polarity is selected by appropriately programming the CKP bit (SSPxCON1<4>). This then, would give waveforms for SPI communication as

shown in Figure 19-3, Figure 19-5 and Figure 19-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

Figure 19-3 shows the waveforms for Master mode. When the CKE bit is set, the SDOx data is valid before there is a clock edge on SCKx. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

### FIGURE 19-3: SPI MODE WAVEFORM (MASTER MODE)

PIC18F87J10 FAMILY

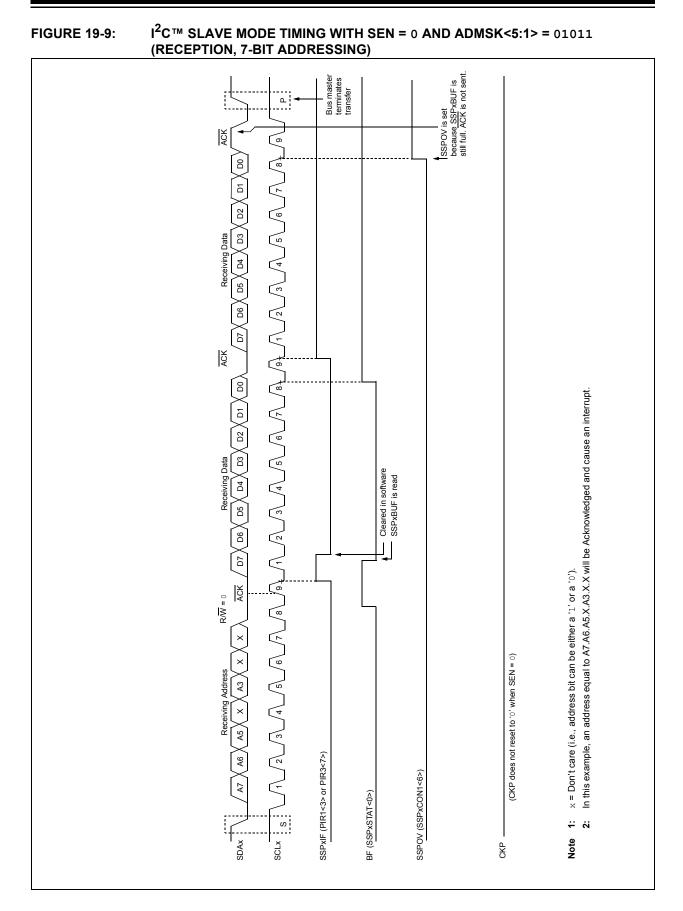

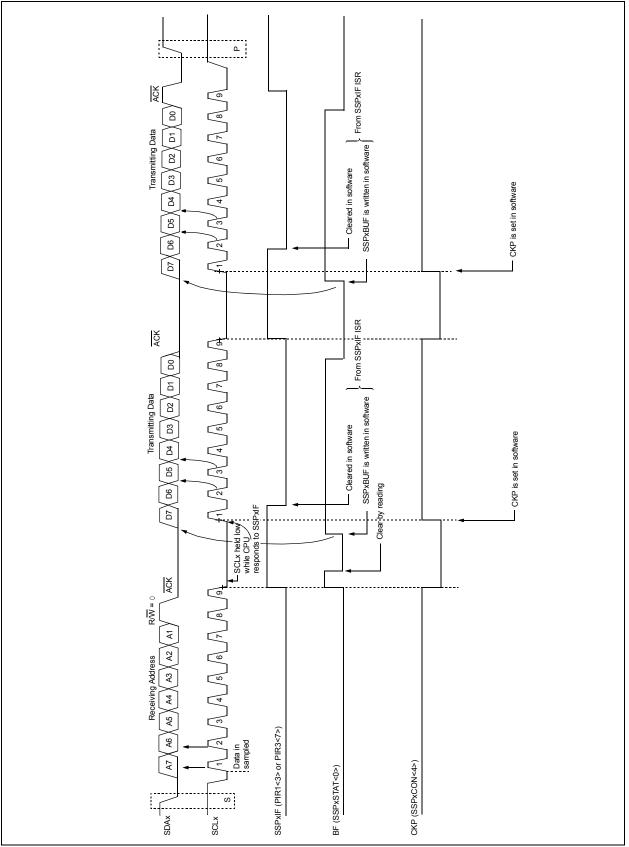

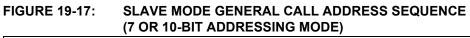

### 19.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit, GCEN, is enabled (SSPxCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPxSR and the address is compared against the SSPxADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPxSR is transferred to the SSPxBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPxIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPxBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPxADD is required to be updated for the second half of the address to match and the UA bit is set (SSPxSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-Bit Addressing mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 19-17).

### 20.1 Baud Rate Generator (BRG)

The BRG is a dedicated 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode; setting the BRG16 bit (BAUDCONx<3>) selects 16-bit mode.

The SPBRGHx:SPBRGx register pair controls the period of a free-running timer. In Asynchronous mode, bits BRGH (TXSTAx<2>) and BRG16 (BAUDCONx<3>) also control the baud rate. In Synchronous mode, BRGH is ignored. Table 20-1 shows the formula for computation of the baud rate for different EUSART modes which only apply in Master mode (internally generated clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRGHx:SPBRGx registers can be calculated using the formulas in Table 20-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 20-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 20-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGHx:SPBRGx registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

### 20.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRGx register pair.

### 20.1.2 SAMPLING

The data on the RXx pin (either RC7/RX1/DT1 or RG2/RX2/DT2) is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RXx pin.

| Configuration Bits |       | its  |                     |                   |  |

|--------------------|-------|------|---------------------|-------------------|--|

| SYNC               | BRG16 | BRGH | BRG/EUSART Mode     | Baud Rate Formula |  |

| 0                  | 0     | 0    | 8-Bit/Asynchronous  | Fosc/[64 (n + 1)] |  |

| 0                  | 0     | 1    | 8-Bit/Asynchronous  |                   |  |

| 0                  | 1     | 0    | 16-Bit/Asynchronous | Fosc/[16 (n + 1)] |  |

| 0                  | 1     | 1    | 16-Bit/Asynchronous |                   |  |

| 1                  | 0     | х    | 8-Bit/Synchronous   | Fosc/[4 (n + 1)]  |  |

| 1                  | 1     | х    | 16-Bit/Synchronous  |                   |  |

#### TABLE 20-1: BAUD RATE FORMULAS

**Legend:** x = Don't care, n = value of SPBRGHx:SPBRGx register pair

## 25.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, the PIC18F87J10 family of devices also provide an optional extension to the core CPU functionality. The added features include eight additional instructions that augment Indirect and Indexed Addressing operations and the implementation of Indexed Literal Offset Addressing for many of the standard PIC18 instructions.

The additional features of the extended instruction set are disabled by default on unprogrammed devices. Users must properly set or clear the XINST Configuration bit during programming to enable or disable these features.

The instructions in the extended set can all be classified as literal operations, which either manipulate the File Select Registers, or use them for Indexed Addressing. Two of the instructions, ADDFSR and SUBFSR, each have an additional special instantiation for using FSR2. These versions (ADDULNK and SUBULNK) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- dynamic allocation and deallocation of software stack space when entering and leaving subroutines

- function pointer invocation

- software Stack Pointer manipulation

- manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 25-3. Detailed descriptions are provided in **Section 25.2.2 "Extended Instruction Set"**. The opcode field descriptions in Table 25-1 (page 294) apply to both the standard and extended PIC18 instruction sets.

Note: The instruction set extension and the Indexed Literal Offset Addressing mode were designed for optimizing applications written in C; the user may likely never use these instructions directly in assembler. The syntax for these commands is provided as a reference for users who may be reviewing code that has been generated by a compiler.

## 25.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of Indexed Addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. The MPASM<sup>™</sup> Assembler will flag an error if it determines that an index or offset value is not bracketed.

When the extended instruction set is enabled, brackets are also used to indicate index arguments in byte-oriented and bit-oriented instructions. This is in addition to other changes in their syntax. For more details, see Section 25.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands".

Note: In the past, square brackets have been used to denote optional arguments in the PIC18 and earlier instruction sets. In this text and going forward, optional arguments are denoted by braces ("{ }").

| Mnemonic, Description |                                 | Description                              | 16-Bit Instruction Word |      |      | /ord    | Status |          |

|-----------------------|---------------------------------|------------------------------------------|-------------------------|------|------|---------|--------|----------|

| Opera                 | nds                             | Description                              | Cycles                  | MSb  |      |         | LSb    | Affected |

| ADDFSR                | f, k                            | Add Literal to FSR                       | 1                       | 1110 | 1000 | ffkk    | kkkk   | None     |

| ADDULNK               | k                               | Add Literal to FSR2 and Return           | 2                       | 1110 | 1000 | 11kk    | kkkk   | None     |

| CALLW                 |                                 | Call Subroutine using WREG               | 2                       | 0000 | 0000 | 0001    | 0100   | None     |

| MOVSF                 | z <sub>s</sub> , f <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2                       | 1110 | 1011 | 0 z z z | ZZZZ   | None     |

|                       |                                 | f <sub>d</sub> (destination) 2nd word    |                         | 1111 | ffff | ffff    | ffff   |          |

| MOVSS                 | z <sub>s</sub> , z <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2                       | 1110 | 1011 | 1zzz    | ZZZZ   | None     |

|                       |                                 | z <sub>d</sub> (destination) 2nd word    |                         | 1111 | XXXX | XZZZ    | ZZZZ   |          |

| PUSHL                 | k                               | Store Literal at FSR2,                   | 1                       | 1110 | 1010 | kkkk    | kkkk   | None     |

|                       |                                 | Decrement FSR2                           |                         |      |      |         |        |          |

| SUBFSR                | f, k                            | Subtract Literal from FSR                | 1                       | 1110 | 1001 | ffkk    | kkkk   | None     |

| SUBULNK               | k                               | Subtract Literal from FSR2 and           | 2                       | 1110 | 1001 | 11kk    | kkkk   | None     |

|                       |                                 | Return                                   |                         |      |      |         |        |          |

### TABLE 25-3: EXTENSIONS TO THE PIC18 INSTRUCTION SET

# 27.3 DC Characteristics: PIC18F87J10 Family (Industrial)

| DC CHA       | RACTE  | RISTICS                                              | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |          |       |                                                       |  |

|--------------|--------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                                       | Min                                                                                                                                    | Мах      | Units | Conditions                                            |  |

|              | VIL    | Input Low Voltage                                    |                                                                                                                                        |          |       |                                                       |  |

|              |        | All I/O Ports:                                       |                                                                                                                                        |          |       |                                                       |  |

| D030         |        | with TTL buffer                                      | Vss                                                                                                                                    | 0.15 Vdd | V     | Vdd < 3.3V                                            |  |

| D030A        |        |                                                      | —                                                                                                                                      | 0.8      | V     | $3.3V \leq V\text{DD} \leq 3.6V$                      |  |

| D031         |        | with Schmitt Trigger Buffer                          | Vss                                                                                                                                    | 0.2 VDD  | V     |                                                       |  |

| D031A        |        | RC3 and RC4                                          | Vss                                                                                                                                    | 0.3 VDD  | V     | I <sup>2</sup> C™ enabled                             |  |

| D031B        |        |                                                      | Vss                                                                                                                                    | 0.8      | V     | SMBus enabled                                         |  |

| D032         |        | MCLR                                                 | Vss                                                                                                                                    | 0.2 VDD  | V     |                                                       |  |

| D033         |        | OSC1                                                 | Vss                                                                                                                                    | 0.3 VDD  | V     | HS, HSPLL modes                                       |  |

| D033A        |        | OSC1                                                 | Vss                                                                                                                                    | 0.2 VDD  | V     | EC, ECPLL modes <sup>(1)</sup>                        |  |

| D034         |        | T1CKI                                                | Vss                                                                                                                                    | 0.3      | V     |                                                       |  |

|              | Vih    | Input High Voltage                                   |                                                                                                                                        |          |       |                                                       |  |

|              |        | I/O Ports with non 5.5V<br>Tolerance: <sup>(4)</sup> |                                                                                                                                        |          |       |                                                       |  |

| D040         |        | with TTL Buffer                                      | 0.25 VDD + 0.8V                                                                                                                        | Vdd      | V     | Vdd < 3.3V                                            |  |

| D040A        |        |                                                      | 2.0                                                                                                                                    | Vdd      | V     | $3.3V \leq V\text{DD} \leq 3.6V$                      |  |

| D041         |        | with Schmitt Trigger Buffer                          | 0.8 Vdd                                                                                                                                | Vdd      | V     |                                                       |  |

|              |        | I/O Ports with 5.5V<br>Tolerance: <sup>(4)</sup>     |                                                                                                                                        |          |       |                                                       |  |

| D041A        |        | RC3 and RC4                                          | 0.7 Vdd                                                                                                                                | Vdd      | V     | I <sup>2</sup> C enabled                              |  |

| D041B        |        |                                                      | 2.1                                                                                                                                    | Vdd      | V     | SMBus enabled                                         |  |

| Dxxx         |        | with TTL Buffer                                      | 0.25 VDD + 0.8V                                                                                                                        | 5.5      | V     | Vdd < 3.3V                                            |  |

| DxxxA        |        |                                                      | 2.0                                                                                                                                    | 5.5      | V     | $3.3V \leq V\text{DD} \leq 3.6V$                      |  |

| Dxxx         |        | with Schmitt Trigger Buffer                          | 0.8 Vdd                                                                                                                                | 5.5      | V     |                                                       |  |

| D042         |        | MCLR                                                 | 0.8 VDD                                                                                                                                | Vdd      | V     |                                                       |  |

| D043         |        | OSC1                                                 | 0.7 Vdd                                                                                                                                | Vdd      | V     | HS, HSPLL modes                                       |  |

| D043A        |        | OSC1                                                 | 0.8 Vdd                                                                                                                                | Vdd      | V     | EC, ECPLL modes                                       |  |

| D044         |        | T1CKI                                                | 1.6                                                                                                                                    | Vdd      | V     |                                                       |  |

|              | lı∟    | Input Leakage Current <sup>(2,3)</sup>               |                                                                                                                                        |          |       |                                                       |  |

| D060         |        | I/O Ports with non 5.5V<br>Tolerance: <sup>(4)</sup> | _                                                                                                                                      | ±1       | μA    | $Vss \le VPIN \le VDD,$ Pin at high-impedance         |  |

| D060A        |        | I/O Ports with 5.5V<br>Tolerance: <sup>(4)</sup>     | _                                                                                                                                      | ±1       | μA    | Vss $\leq$ VPIN $\leq$ 5.5V.<br>Pin at high-impedance |  |

| D061         |        | MCLR                                                 | _                                                                                                                                      | ±1       | μA    | $Vss \le VPIN \le VDD$                                |  |

| D063         |        | OSC1                                                 |                                                                                                                                        | ±5       | μA    | $Vss \le VPIN \le VDD$                                |  |

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC<sup>®</sup> device be driven with an external clock while in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as current sourced by the pin.

4: Refer to Table 11-2 for the pins that have corresponding tolerance limits.

| DC CH4       |       |                                       | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature -40°C $\leq$ TA $\leq$ +85°C for industrial |      |     |       |                                               |

|--------------|-------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-----------------------------------------------|

| Param<br>No. | Sym   | Characteristic                        | Min                                                                                                                          | Тур† | Max | Units | Conditions                                    |

|              |       | Program Flash Memory                  |                                                                                                                              |      |     |       |                                               |

| D130         | Eр    | Cell Endurance                        | 100                                                                                                                          | 1K   | —   | E/W   | -40°C to +85°C                                |

| D131         | Vpr   | VDD for Read                          | VMIN                                                                                                                         | —    | 3.6 | V     | VMIN = Minimum operating<br>voltage           |

| D132         | Vpew  | Voltage for Self-Timed Erase or Write |                                                                                                                              |      |     |       |                                               |

|              |       | VDD                                   | 2.35                                                                                                                         | _    | 3.6 | V     | ENVREG = 0                                    |

|              |       | VDDCORE                               | 2.25                                                                                                                         | _    | 2.7 | V     | ENVREG = 1                                    |

| D133A        | Tiw   | Self-Timed Write Cycle Time           |                                                                                                                              | 2.8  | _   | ms    |                                               |

| D133B        | TIE   | Self-Timed Page Erase Cycle<br>Time   | _                                                                                                                            | 33.0 | —   | ms    |                                               |

| D134         | TRETD | Characteristic Retention              | 20                                                                                                                           | _    | —   | Year  | Provided no other specifications are violated |

| D135         | IDDP  | Supply Current during<br>Programming  | _                                                                                                                            | 10   | —   | mA    |                                               |

| D140         | TWE   | Writes per Erase Cycle                |                                                                                                                              |      | 1   |       | For each physical address                     |

### TABLE 27-1:MEMORY PROGRAMMING REQUIREMENTS

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Param.<br>No. | Symbol  | Characteris               | tic          | Min         | Max  | Units | Conditions                                 |

|---------------|---------|---------------------------|--------------|-------------|------|-------|--------------------------------------------|

| 100           | Тнідн   | Clock High Time           | 100 kHz mode | 4.0         | _    | μs    |                                            |

|               |         |                           | 400 kHz mode | 0.6         | _    | μS    |                                            |

|               |         |                           | MSSP Module  | 1.5 TCY     | _    |       |                                            |

| 101           | TLOW    | Clock Low Time            | 100 kHz mode | 4.7         | _    | μs    |                                            |

|               |         |                           | 400 kHz mode | 1.3         | _    | μs    |                                            |

|               |         |                           | MSSP Module  | 1.5 TCY     | —    |       |                                            |

| 102           | TR      | SDAx and SCLx Rise Time   | 100 kHz mode | —           | 1000 | ns    |                                            |

|               |         |                           | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from<br>10 to 400 pF |

| 103           | TF      | SDAx and SCLx Fall Time   | 100 kHz mode | _           | 300  | ns    |                                            |

|               |         |                           | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from<br>10 to 400 pF |

| 90 Tsu:s      | TSU:STA |                           | 100 kHz mode | 4.7         |      | μS    | Only relevant for Repeated                 |

|               |         |                           | 400 kHz mode | 0.6         | _    | μs    | Start condition                            |

| 91            | THD:STA | Start Condition Hold Time | 100 kHz mode | 4.0         | —    | μs    | After this period, the first clock         |

|               |         |                           | 400 kHz mode | 0.6         | —    | μs    | pulse is generated                         |

| 106           | THD:DAT | Data Input Hold Time      | 100 kHz mode | 0           | —    | ns    |                                            |

|               |         |                           | 400 kHz mode | —           | 0.9  | μS    |                                            |

| 107           | TSU:DAT | Data Input Setup Time     | 100 kHz mode | 250         | —    | ns    | (Note 2)                                   |

|               |         |                           | 400 kHz mode | —           | —    | ns    |                                            |

| 92            | Tsu:sto | Stop Condition Setup Time | 100 kHz mode | 4.7         | _    | μS    |                                            |

|               |         |                           | 400 kHz mode | 0.6         | —    | μS    |                                            |

| 109           | ΤΑΑ     | Output Valid from Clock   | 100 kHz mode | —           | 3500 | ns    | (Note 1)                                   |

|               |         |                           | 400 kHz mode | —           | —    | ns    |                                            |

| 110           | TBUF    | Bus Free Time             | 100 kHz mode | 4.7         | —    | μS    | Time the bus must be free                  |

|               |         |                           | 400 kHz mode | —           | —    | μS    | before a new transmission can start        |

| D102          | Св      | Bus Capacitive Loading    |              | —           | 400  | pF    |                                            |

## TABLE 27-21: I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS (SLAVE MODE)

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCLx to avoid unintended generation of Start or Stop conditions.

2: A Fast mode I<sup>2</sup>C<sup>™</sup> bus device can be used in a Standard mode I<sup>2</sup>C bus system, but the requirement, TSU:DAT ≥ 250 ns, must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCLx signal. If such a device does stretch the LOW period of the SCLx signal, it must output the next data bit to the SDAx line, TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCLx line is released.

NOTES:

# INDEX

| Α                                                 |     |

|---------------------------------------------------|-----|

| A/D                                               | 261 |

| A/D Converter Interrupt, Configuring              |     |

| Acquisition Requirements                          |     |

| ADCAL Bit                                         | 269 |

| ADCON0 Register                                   |     |

| ADCON1 Register                                   | 261 |

| ADCON2 Register                                   | 261 |

| ADRESH Register261,                               |     |

| ADRESL Register                                   |     |

| Analog Port Pins                                  |     |

| Analog Port Pins, Configuring                     |     |

| Associated Registers                              |     |

| Automatic Acquisition Time                        | 267 |

| Calculating the Minimum Required                  | 000 |

| Acquisition Time                                  |     |

| Calibration                                       |     |

| Configuring the Module                            |     |

| Conversion Clock (TAD)<br>Conversion Requirements |     |

| Conversion Status (GO/DONE Bit)                   |     |

| Conversions                                       |     |

| Converter Characteristics                         |     |

| Operation in Power-Managed Modes                  |     |

| Special Event Trigger (ECCP)                      | 268 |

| Use of the ECCP2 Trigger                          |     |

| Absolute Maximum Ratings                          |     |

| AC (Timing) Characteristics                       |     |

| Load Conditions for Device Timing                 |     |

| Specifications                                    | 363 |

| Parameter Symbology                               |     |

| Temperature and Voltage Specifications            |     |

| Timing Conditions                                 |     |

| ACKSTAT                                           |     |

| ACKSTAT Status Flag                               | 229 |

| ADCAL Bit                                         | 269 |

| ADCON0 Register                                   | 261 |

| GO/DONE Bit                                       | 264 |

| ADCON1 Register                                   | 261 |

| ADCON2 Register                                   | 261 |

| ADDFSR                                            | 336 |

| ADDLW                                             | 299 |

| ADDULNK                                           |     |

| ADDWF                                             | 299 |

| ADDWFC                                            |     |

| ADRESH Register                                   |     |

| ADRESL Register                                   | 264 |

| Analog-to-Digital Converter. See A/D.             |     |

| ANDLW                                             |     |

| ANDWF                                             | 301 |

| Assembler                                         | 244 |

| MPASM Assembler                                   |     |

| Auto-Wake-up on Sync Break Character              | 252 |

| В                                                 |     |

| Basic Connection Requirements                     | 27  |

| Baud Rate Generator                               |     |

| BC                                                | 301 |

| BCF                                               | 302 |

| BF                                                |     |

| BF Status Flag                                    | 229 |

| <b>PIC18F87J1</b> | <b>0 FAMILY</b> |

|-------------------|-----------------|

|-------------------|-----------------|

| Bloc | k Diagrams                                              |     |

|------|---------------------------------------------------------|-----|

|      | 16-Bit Byte Select Mode                                 |     |

|      | 16-Bit Byte Write Mode                                  |     |

|      | 16-Bit Word Write Mode                                  |     |

|      | 8-Bit Multiplexed Modes                                 |     |

|      | A/D                                                     |     |

|      | Analog Input Model                                      |     |

|      | Baud Rate Generator                                     |     |

|      | Capture Mode Operation<br>Comparator Analog Input Model |     |

|      | Comparator I/O Operating Modes                          |     |

|      | Comparator Output                                       |     |

|      | Comparator Voltage Reference                            |     |

|      | Comparator Voltage Reference Output                     | 270 |

|      | Buffer Example                                          | 279 |

|      | Compare Mode Operation                                  |     |

|      | Connections for On-Chip Voltage Regulator               |     |

|      | Device Clock                                            |     |

|      | Enhanced PWM Simplified                                 |     |

|      | EUSART Receive                                          |     |

|      | EUSART Transmit                                         |     |

|      | External Power-on Reset Circuit                         |     |

|      | (Slow VDD Power-up)                                     | 49  |

|      | Fail-Safe Clock Monitor                                 |     |

|      | Generic I/O Port Operation                              | 125 |

|      | Interrupt Logic                                         | 110 |

|      | MSSP (I <sup>2</sup> C Master Mode)                     | 223 |

|      | MSSP (I <sup>2</sup> C Mode)                            | 203 |

|      | MSSP (SPI Mode)                                         |     |

|      | On-Chip Reset Circuit                                   | 47  |

|      | PIC18F6XJ10/6XJ15                                       |     |

|      | PIC18F8XJ10/8XJ15                                       |     |

|      | PLL                                                     |     |

|      | PORTD and PORTE (Parallel Slave Port)                   |     |

|      | PWM Operation (Simplified)                              |     |

|      | Reads from Flash Program Memory                         |     |

|      | Recommended Minimum Connections                         |     |

|      | Single Comparator                                       |     |

|      | Table Read Operation           Table Write Operation    |     |

|      | Table Writes to Flash Program Memory                    |     |

|      | Timer0 in 16-Bit Mode                                   |     |

|      | Timer0 in 8-Bit Mode                                    |     |

|      | Timer1                                                  |     |

|      | Timer1 (16-Bit Read/Write Mode)                         |     |

|      | Timer2                                                  |     |

|      | Timer3                                                  |     |

|      | Timer3 (16-Bit Read/Write Mode)                         | 164 |

|      | Timer4                                                  |     |

|      | Watchdog Timer                                          | 287 |

| BN.  | -                                                       | 302 |

| BNC  | :                                                       | 303 |

| BNN  | l                                                       | 303 |

| BNO  | V                                                       | 304 |

|      |                                                         | 304 |

|      | R. See Brown-out Reset.                                 |     |

|      | ·                                                       |     |

|      |                                                         |     |

|      | k Character (12-Bit) Transmit and Receive               | 254 |

|      | 6. See Baud Rate Generator.                             | 40  |

| RLOW | vn-out Reset (BOR)                                      |     |

|      | and On-Chip Voltage Regulator                           |     |

|      | Detecting                                               | 49  |