Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 66                                                                          |

| Program Memory Size        | 48KB (24K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 15x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f85j15t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                               | Pin Number | Pin                      | Buffer                                  | Description                                                                                                                                                          |  |  |  |

|--------------------------------------------------------|------------|--------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                               | TQFP       | Туре Туре                |                                         | Description                                                                                                                                                          |  |  |  |

|                                                        |            |                          |                                         | PORTD is a bidirectional I/O port.                                                                                                                                   |  |  |  |

| RD0/PSP0<br>RD0<br>PSP0                                | 58         | I/O<br>I/O               | ST<br>TTL                               | Digital I/O.<br>Parallel Slave Port data.                                                                                                                            |  |  |  |

| RD1/PSP1<br>RD1<br>PSP1                                | 55         | I/O<br>I/O               | ST<br>TTL                               | Digital I/O.<br>Parallel Slave Port data.                                                                                                                            |  |  |  |

| RD2/PSP2<br>RD2<br>PSP2                                | 54         | 1/0<br>1/0               | ST<br>TTL                               | Digital I/O.<br>Parallel Slave Port data.                                                                                                                            |  |  |  |

| RD3/PSP3<br>RD3<br>PSP3                                | 53         | I/O<br>I/O               | ST<br>TTL                               | Digital I/O.<br>Parallel Slave Port data.                                                                                                                            |  |  |  |

| RD4/PSP4/SDO2<br>RD4<br>PSP4<br>SDO2                   | 52         | I/O<br>I/O<br>O          | ST<br>TTL                               | Digital I/O.<br>Parallel Slave Port data.<br>SPI data out.                                                                                                           |  |  |  |

| RD5/PSP5/SDI2/SDA2<br>RD5<br>PSP5<br>SDI2<br>SDA2      | 51         | I/O<br>I/O<br>I<br>I/O   | ST<br>TTL<br>ST<br>I <sup>2</sup> C/SMB | Digital I/O.<br>Parallel Slave Port data.<br>SPI data in.<br>I <sup>2</sup> C™ data I/O.                                                                             |  |  |  |

| RD6/PSP6/SCK2/SCL2<br>RD6<br>PSP6<br>SCK2<br>SCL2      | 50         | I/O<br>I/O<br>I/O<br>I/O | ST<br>TTL<br>ST<br>I <sup>2</sup> C/SMB | Digital I/O.<br>Parallel Slave Port data.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |  |  |

| RD7/PSP7/ <del>SS2</del><br>RD7<br><u>PSP</u> 7<br>SS2 | 49         | 1/0<br>1/0<br>1          | ST<br>TTL<br>TTL                        | Digital I/O.<br>Parallel Slave Port data.<br>SPI slave select input.                                                                                                 |  |  |  |

| ST = Sc<br>I = Inj<br>P = Pc                           |            | out with (<br>ut buffer  | CMOS leve                               | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)                                                 |  |  |  |

#### TABLE 1-3: PIC18F6XJ10/6XJ15 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for ECCP2/P2A when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2/P2A when Configuration bit, CCP2MX, is cleared.

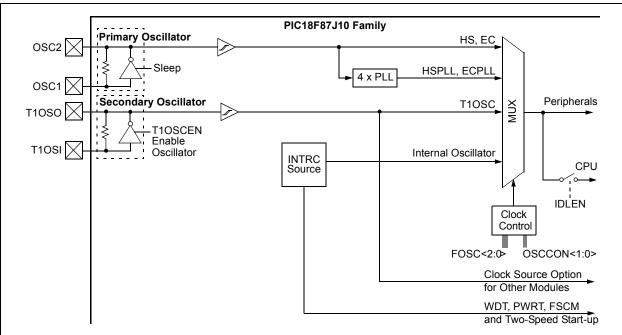

### 3.5 Internal Oscillator Block

The PIC18F87J10 family of devices includes an internal oscillator source (INTRC) which provides a nominal 31 kHz output. The INTRC is enabled on device power-up and clocks the device during its configuration cycle until it enters operating mode. INTRC is also enabled if it is selected as the device clock source or if any of the following are enabled:

- · Fail-Safe Clock Monitor

- Watchdog Timer

- Two-Speed Start-up

These features are discussed in greater detail in Section 24.0 "Special Features of the CPU".

The INTRC can also be optionally configured as the default clock source on device start-up by setting the FOSC2 Configuration bit. This is discussed in **Section 3.6.1 "Oscillator Control Register"**.

#### 3.6 Clock Sources and Oscillator Switching

The PIC18F87J10 family includes a feature that allows the device clock source to be switched from the main oscillator to an alternate clock source. PIC18F87J10 family devices offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- · Primary oscillators

- · Secondary oscillators

- · Internal oscillator

The **primary oscillators** include the External Crystal and Resonator modes and the External Clock modes. The particular mode is defined by the FOSC<2:0> Configuration bits. The details of these modes are covered earlier in this chapter.

The **secondary oscillators** are those external sources not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

PIC18F87J10 family devices offer the Timer1 oscillator as a secondary oscillator. This oscillator, in all power-managed modes, is often the time base for functions such as a real-time clock.

Most often, a 32.768 kHz watch crystal is connected between the RC0/T10S0/T13CKI and RC1/T10SI pins. Loading capacitors are also connected from each pin to ground.

The Timer1 oscillator is discussed in greater detail in **Section 13.3 "Timer1 Oscillator"**.

In addition to being a primary clock source, the **internal oscillator** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor.

The clock sources for the PIC18F87J10 family devices are shown in Figure 3-5. See **Section 24.0 "Special Features of the CPU"** for Configuration register details.

### FIGURE 3-5: PIC18F87J10 FAMILY CLOCK DIAGRAM

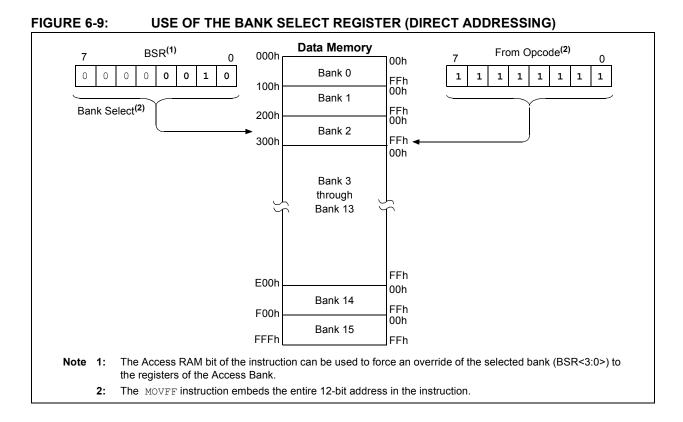

#### 6.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h-5Fh) in Bank 0 and the last 160 bytes of memory (60h-FFh) in Bank 15. The lower half is known as the "Access RAM" and is composed of GPRs. The upper half is where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 6-7).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0', however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 6.6.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 6.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

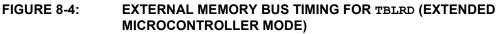

#### 8.6.4 16-BIT MODE TIMING

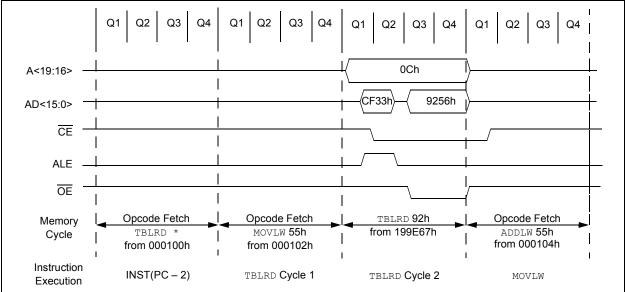

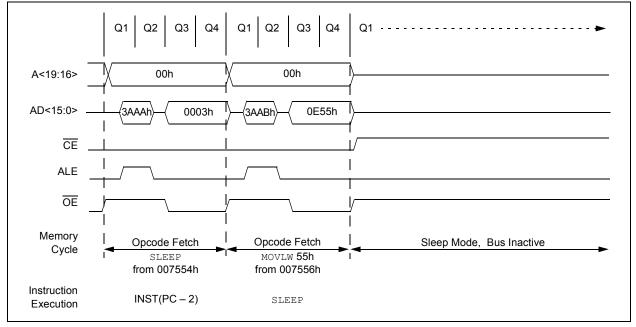

The presentation of control signals on the external memory bus is different for the various operating modes. Typical signal timing diagrams are shown in Figure 8-4 and Figure 8-5.

# FIGURE 8-5: EXTERNAL MEMORY BUS TIMING FOR SLEEP (EXTENDED MICROCONTROLLER MODE)

## 10.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Enable registers (PIE1, PIE2, PIE3). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

#### REGISTER 10-7: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| PSPIE | ADIE  | RC1IE | TX1IE | SSP1IE | CCP1IE | TMR2IE | TMR1IE |

| bit 7 |       |       |       |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | <b>PSPIE:</b> Parallel Slave Port Read/Write Interrupt Enable bit<br>1 = Enables the PSP read/write interrupt<br>0 = Disables the PSP read/write interrupt        |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIE: A/D Converter Interrupt Enable bit<br>1 = Enables the A/D interrupt<br>0 = Disables the A/D interrupt                                                       |

| bit 5 | <b>RC1IE:</b> EUSART1 Receive Interrupt Enable bit<br>1 = Enables the EUSART1 receive interrupt<br>0 = Disables the EUSART1 receive interrupt                     |

| bit 4 | <b>TX1IE:</b> EUSART1 Transmit Interrupt Enable bit<br>1 = Enables the EUSART1 transmit interrupt<br>0 = Disables the EUSART1 transmit interrupt                  |

| bit 3 | <b>SSP1IE:</b> Master Synchronous Serial Port 1 Interrupt Enable bit<br>1 = Enables the MSSP1 interrupt<br>0 = Disables the MSSP1 interrupt                       |

| bit 2 | <b>CCP1IE:</b> ECCP1 Interrupt Enable bit<br>1 = Enables the ECCP1 interrupt<br>0 = Disables the ECCP1 interrupt                                                  |

| bit 1 | <b>TMR2IE:</b> TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt              |

| bit 0 | <ul> <li>TMR1IE: TMR1 Overflow Interrupt Enable bit</li> <li>1 = Enables the TMR1 overflow interrupt</li> <li>0 = Disables the TMR1 overflow interrupt</li> </ul> |

# 11.0 I/O PORTS

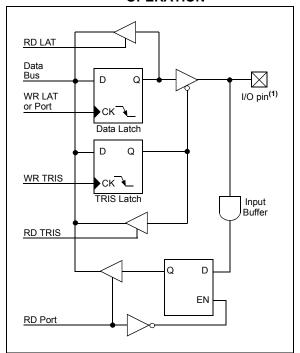

Depending on the device selected and features enabled, there are up to nine ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Output Latch register)

The Output Latch (LAT register) is useful for read-modify-write operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

FIGURE 11-1: GENERIC I/O PORT OPERATION

### 11.1 I/O Port Pin Capabilities

When developing an application, the capabilities of the port pins must be considered. Outputs on some pins have higher output drive strength than others. Similarly, some pins can tolerate higher than VDD input levels.

#### 11.1.1 PIN OUTPUT DRIVE

The output pin drive strengths vary for groups of pins intended to meet the needs for a variety of applications. PORTB and PORTC are designed to drive higher loads, such as LEDs. The external memory interface ports (PORTD, PORTE and PORTJ) are designed to drive medium loads. All other ports are designed for small loads, typically indication only. Table 11-1 summarizes the output capabilities. Refer to **Section 27.0 "Electrical Characteristics"** for more details.

| Port                 | Drive   | Description                   |

|----------------------|---------|-------------------------------|

| PORTA                | Minimum | Intended for indication.      |

| PORTF                |         |                               |

| PORTG                |         |                               |

| PORTH <sup>(1)</sup> |         |                               |

| PORTD                | Medium  | Sufficient drive levels for   |

| PORTE                |         | external memory interfacing   |

| PORTJ <sup>(1)</sup> |         | as well as indication.        |

| PORTB                | High    | Suitable for direct LED drive |

| PORTC                |         | levels.                       |

**Note 1:** These ports are not available on 64-pin devices.

| Pin Name      | Function | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                      |

|---------------|----------|-----------------|-----|-------------|------------------------------------------------------------------------------------------------------------------|

| RA0/AN0       | RA0      | 0               | 0   | DIG         | LATA<0> data output; not affected by analog input.                                                               |

|               |          | 1               | I   | TTL         | PORTA<0> data input; disabled when analog input enabled.                                                         |

|               | AN0      | 1               | Ι   | ANA         | A/D Input Channel 0. Default input configuration on POR; does not affect digital output.                         |

| RA1/AN1       | RA1      | 0               | 0   | DIG         | LATA<1> data output; not affected by analog input.                                                               |

|               |          | 1               | Ι   | TTL         | PORTA<1> data input; disabled when analog input enabled.                                                         |

|               | AN1      | 1               | I   | ANA         | A/D Input Channel 1. Default input configuration on POR; does not affect digital output.                         |

| RA2/AN2/VREF- | RA2      | 0               | 0   | DIG         | LATA<2> data output; not affected by analog input. Disabled when CVREF output enabled.                           |

|               |          | 1               | Ι   | TTL         | PORTA<2> data input. Disabled when analog functions enabled; disabled when CVREF output enabled.                 |

|               | AN2      | 1               | Ι   | ANA         | A/D Input Channel 2 and Comparator C2+ input. Default input configuration on POR; not affected by analog output. |

|               | VREF-    | 1               | I   | ANA         | A/D and Comparator low reference voltage input.                                                                  |

| RA3/AN3/VREF+ | RA3      | 0               | 0   | DIG         | LATA<3> data output; not affected by analog input.                                                               |

|               |          | 1               | Ι   | TTL         | PORTA<3> data input; disabled when analog input enabled.                                                         |

|               | AN3      | 1               | I   | ANA         | A/D Input Channel 3. Default input configuration on POR.                                                         |

|               | VREF+    | 1               | Ι   | ANA         | A/D high reference voltage input.                                                                                |

| RA4/T0CKI     | RA4      | 0               | 0   | DIG         | LATA<4> data output.                                                                                             |

|               |          | 1               | Ι   | ST          | PORTA<4> data input; default configuration on POR.                                                               |

|               | TOCKI    | х               | Ι   | ST          | Timer0 clock input.                                                                                              |

| RA5/AN4       | RA5      | 0               | 0   | DIG         | LATA<5> data output; not affected by analog input.                                                               |

|               |          | 1               | Ι   | TTL         | PORTA<5> data input; disabled when analog input enabled.                                                         |

|               | AN4      | 1               | Ι   | ANA         | A/D Input Channel 4. Default configuration on POR.                                                               |

TABLE 11-3: PORTA FUNCTIONS

**Legend:** PWR = Power Supply, O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|-------|--------|--------|--------|--------|--------|--------|----------------------------|

| PORTA  | _     | _     | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | 56                         |

| LATA   | —     | _     | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | 56                         |

| TRISA  | _     | _     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 56                         |

| ADCON1 | _     | _     | VCFG1  | VCFG0  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 54                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

# 11.3 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin). All pins on PORTB are digital only and tolerate voltages up to 5.5V.

The Output Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

#### EXAMPLE 11-2: INITIALIZING PORTB

| CLRF  | PORTB | ; Initialize PORTB by<br>; clearing output<br>: data latches |

|-------|-------|--------------------------------------------------------------|

| CLRF  | LATB  | ; data fattines<br>: Alternate method                        |

| OLIG  | DITE  | ; to clear output                                            |

|       |       | ; data latches                                               |

| MOVLW | OCFh  | ; Value used to                                              |

|       |       | ; initialize data                                            |

|       |       | ; direction                                                  |

| MOVWF | TRISB | ; Set RB<3:0> as inputs                                      |

|       |       | ; RB<5:4> as outputs                                         |

|       |       | ; RB<7:6> as inputs                                          |

|       |       |                                                              |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn <u>on all</u> the pull-ups. This is performed by clearing bit, RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB<7:4>) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from power-managed modes. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF (ANY), PORTB instruction). This will end the mismatch condition.

- b) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit, RBIF, to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

For 80-pin devices, RB3 can be configured as the alternate peripheral pin for the ECCP2 module and Enhanced PWM Output 2A by clearing the CCP2MX Configuration bit. This applies only to 80-pin devices operating in Extended Microcontroller mode. If the device is in Microcontroller mode, the alternate assignment for ECCP2 is RE7. As with other ECCP2 configurations, the user must ensure that the TRISB<3> bit is set appropriately for the intended operation.

## 11.7 PORTF, LATF and TRISF Registers

PORTF is a 7-bit wide, bidirectional port. The corresponding Data Direction register is TRISF. Setting a TRISF bit (= 1) will make the corresponding PORTF pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISF bit (= 0) will make the corresponding PORTF pin an output (i.e., put the contents of the output latch on the selected pin). Only pin 7 of PORTF has no analog input; it is the only pin that can tolerate voltages up to 5.5V.

The Output Latch register (LATF) is also memory mapped. Read-modify-write operations on the LATF register read and write the latched output value for PORTF.

All pins on PORTF are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

PORTF is multiplexed with several analog peripheral functions, including the A/D Converter and comparator inputs, as well as the comparator outputs. Pins, RF2 through RF6, may be used as comparator inputs or outputs by setting the appropriate bits in the CMCON register. To use RF<6:3> as digital inputs, it is also necessary to turn off the comparators.

- Note 1: On device Resets, pins, RF<6:1>, are configured as analog inputs and are read as '0'.

- **2:** To configure PORTF as digital I/O, turn off comparators and set ADCON1 value.

#### EXAMPLE 11-6: INITIALIZING PORTF

| CLRF PORTF   | ; Initialize FORTF by<br>; clearing output<br>: data latches   |

|--------------|----------------------------------------------------------------|

| CLRF LATF    | <pre>; Alternate method ; to clear output ; data latches</pre> |

| MOVLW 07h    | ;                                                              |

| MOVWF CMCON  | ; Turn off comparators                                         |

| MOVLW OFh;   |                                                                |

| MOVWF ADCON1 | ; Set PORTF as digital I/O                                     |

| MOVLW OCEh   | ; Value used to                                                |

|              | ; initialize data                                              |

|              | ; direction                                                    |

| MOVWF TRISF  | ; Set RF3:RF1 as inputs                                        |

|              | ; RF5:RF4 as outputs                                           |

|              | ; RF7:RF6 as inputs                                            |

|              |                                                                |

#### 15.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 15-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

#### 15.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 13.0 "Timer1 Module".

### 15.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

#### 15.5 Resetting Timer3 Using the ECCP Special Event Trigger

If ECCP1 or ECCP2 is configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer3. The trigger from ECCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 18.2.1** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from an ECCP module, the write will take precedence.

Note: The Special Event Triggers from the ECCPx module will not set the TMR3IF interrupt flag bit (PIR1<0>).

| Bit 7                     | Bit 6                                                                              | Bit 5                                                                                                                                            | Bit 4                                                                                                                                   | Bit 3                                                                                                                                                                 | Bit 2                                                                                                                                                                                                 | Bit 1                                                                                                                                                                                                                                | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reset<br>Values<br>on page                                                                                                                                                                                                                                                                                        |

|---------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIE/GIEH                  | PEIE/GIEL                                                                          | TMR0IE                                                                                                                                           | INT0IE                                                                                                                                  | RBIE                                                                                                                                                                  | TMR0IF                                                                                                                                                                                                | INT0IF                                                                                                                                                                                                                               | RBIF                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53                                                                                                                                                                                                                                                                                                                |

| OSCFIF                    | CMIF                                                                               | —                                                                                                                                                | _                                                                                                                                       | BCL1IF                                                                                                                                                                | _                                                                                                                                                                                                     | TMR3IF                                                                                                                                                                                                                               | CCP2IF                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55                                                                                                                                                                                                                                                                                                                |

| OSCFIE                    | CMIE                                                                               | —                                                                                                                                                | _                                                                                                                                       | BCL1IE                                                                                                                                                                | _                                                                                                                                                                                                     | TMR3IE                                                                                                                                                                                                                               | CCP2IE                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55                                                                                                                                                                                                                                                                                                                |

| OSCFIP                    | CMIP                                                                               | _                                                                                                                                                | _                                                                                                                                       | BCL1IP                                                                                                                                                                | _                                                                                                                                                                                                     | TMR3IP                                                                                                                                                                                                                               | CCP2IP                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55                                                                                                                                                                                                                                                                                                                |

| Timer3 Reg                | jister Low By                                                                      | /te                                                                                                                                              |                                                                                                                                         |                                                                                                                                                                       |                                                                                                                                                                                                       |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55                                                                                                                                                                                                                                                                                                                |

| Timer3 Register High Byte |                                                                                    |                                                                                                                                                  |                                                                                                                                         |                                                                                                                                                                       | 55                                                                                                                                                                                                    |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                   |

| RD16                      | T1RUN                                                                              | T1CKPS1                                                                                                                                          | T1CKPS0                                                                                                                                 | T1OSCEN                                                                                                                                                               | T1SYNC                                                                                                                                                                                                | TMR1CS                                                                                                                                                                                                                               | TMR10N                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54                                                                                                                                                                                                                                                                                                                |

| RD16                      | T3CCP2                                                                             | T3CKPS1                                                                                                                                          | T3CKPS0                                                                                                                                 | T3CCP1                                                                                                                                                                | <b>T3SYNC</b>                                                                                                                                                                                         | TMR3CS                                                                                                                                                                                                                               | TMR3ON                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55                                                                                                                                                                                                                                                                                                                |

|                           | GIE/GIEH<br>OSCFIF<br>OSCFIE<br>OSCFIP<br>Timer3 Reg<br>Timer3 Reg<br>RD16<br>RD16 | GIE/GIEH PEIE/GIEL<br>OSCFIF CMIF<br>OSCFIE CMIE<br>OSCFIP CMIP<br>Timer3 Register Low By<br>Timer3 Register High B<br>RD16 T1RUN<br>RD16 T3CCP2 | GIE/GIEHPEIE/GIELTMR0IEOSCFIFCMIFOSCFIECMIEOSCFIPCMIPTimer3 Register Low ByteTimer3 Register High ByteRD16T1RUNT1CKPS1RD16T3CCP2T3CKPS1 | GIE/GIEHPEIE/GIELTMR0IEINT0IEOSCFIFCMIFOSCFIECMIEOSCFIPCMIPOSCFIPCMIPTimer3 Register Low ByteTimer3 Register High ByteRD16T1RUNT1CKPS1T1CKPS0RD16T3CCP2T3CKPS1T3CKPS0 | GIE/GIEHPEIE/GIELTMR0IEINT0IERBIEOSCFIFCMIF——BCL1IFOSCFIECMIE——BCL1IEOSCFIPCMIP——BCL1IEOSCFIPCMIP——BCL1IPTimer3 Register Low ByteTimer3 Register High ByteT1CKPS1T1CKPS0RD16T1RUNT1CKPS1T3CKPS0T3CCP1 | GIE/GIEHPEIE/GIELTMR0IEINT0IERBIETMR0IFOSCFIFCMIFBCL1IF-OSCFIECMIEBCL1IE-OSCFIPCMIPBCL1IP-OSCFIPCMIPBCL1IP-OSCFIPCMIPBCL1IP-Timer3 Register Low ByteBCL1IP-Timer3 Register High ByteT10SCENT1SYNCRD16T1RUNT1CKPS1T3CKPS0T3CCP1T3SYNC | GIE/GIEH       PEIE/GIEL       TMR0IE       INTOIE       RBIE       TMR0IF       INTOIF         OSCFIF       CMIF       —       —       BCL1IF       —       TMR3IF         OSCFIE       CMIE       —       —       BCL1IF       —       TMR3IF         OSCFIP       CMIE       —       —       BCL1IE       —       TMR3IE         OSCFIP       CMIP       —       —       BCL1IP       —       TMR3IP         Timer3 Register Low Byte | GIE/GIEHPEIE/GIELTMROIEINTOIERBIETMROIFINTOIFRBIFOSCFIFCMIFBCL1IF-TMR3IFCCP2IFOSCFIECMIEBCL1IE-TMR3IECCP2IEOSCFIPCMIPBCL1IP-TMR3IPCCP2IPOSCFIPCMIPBCL1IP-TMR3IPCCP2IPTimer3 Register Low ByteBCL1IP-TMR3IPCCP2IPTimer3 Register High ByteT1OSCENT1SYNCTMR1CSTMR1ONRD16T1RUNT1CKPS1T3CKPS0T3CCP1T3SYNCTMR3CSTMR3ON |

TABLE 15-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

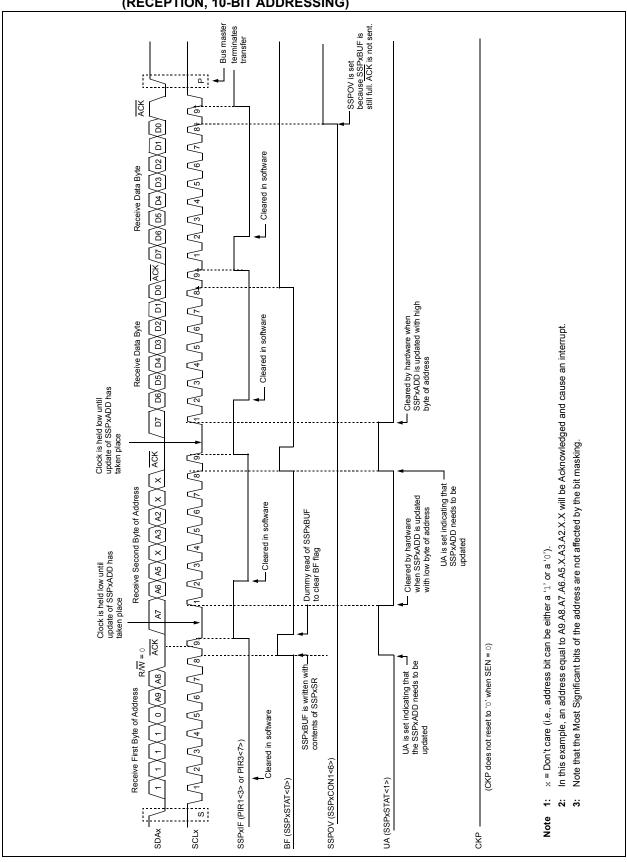

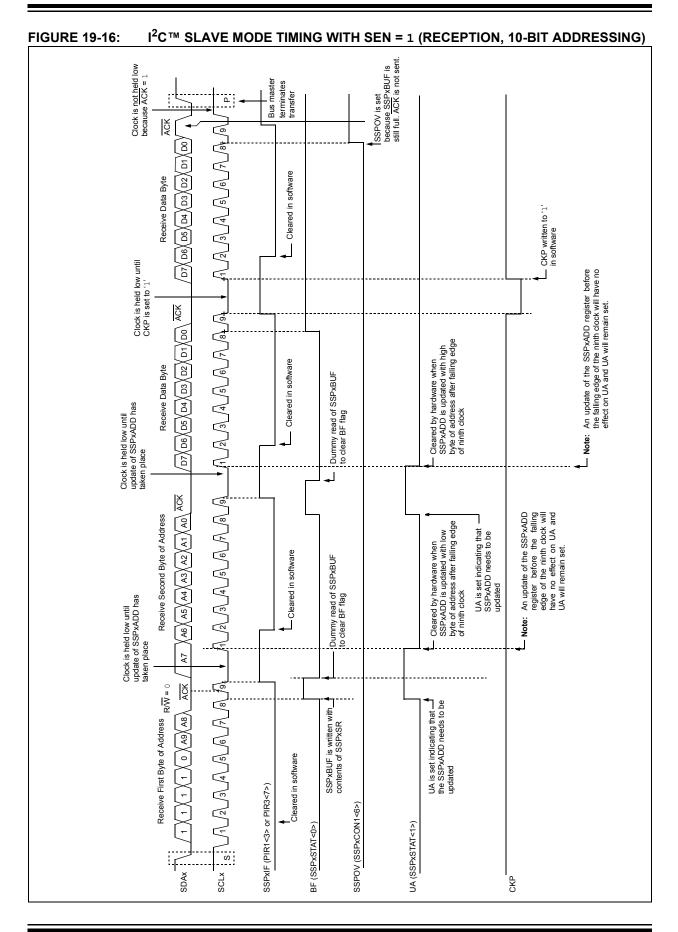

FIGURE 19-11: I<sup>2</sup>C<sup>™</sup> SLAVE MODE TIMING WITH SEN = 0 AND ADMSK<5:1> = 01001 (RECEPTION, 10-BIT ADDRESSING)

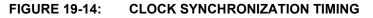

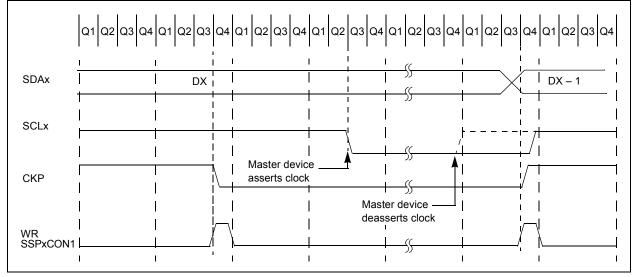

# 19.4.4.5 Clock Synchronization and the CKP Bit

When the CKP bit is cleared, the SCLx output is forced to '0'. However, clearing the CKP bit will not assert the SCLx output low until the SCLx output is already sampled low. Therefore, the CKP bit will not assert the SCLx line until an external  $I^2C$  master device has

already asserted the SCLx line. The SCLx output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have deasserted SCLx. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCLx (see Figure 19-14).

| R/W-0        | U-0                                                                                                                                                    | R/W-0                                             | R/W-0        | R/W-0                     | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------|---------------------------|-----------------|-----------------|-------|

| ADFM         |                                                                                                                                                        | ACQT2                                             | ACQT1        | ACQT0                     | ADCS2           | ADCS1           | ADCS0 |

| bit 7        |                                                                                                                                                        |                                                   |              |                           |                 |                 | bit ( |

| Legend:      |                                                                                                                                                        |                                                   |              |                           |                 |                 |       |

| R = Readab   | le bit                                                                                                                                                 | W = Writable                                      | bit          | U = Unimpler              | nented bit, rea | d as '0'        |       |

| -n = Value a | t POR                                                                                                                                                  | '1' = Bit is set                                  |              | '0' = Bit is cle          | ared            | x = Bit is unkr | nown  |

| bit 7        | <b>ADFM:</b> A/D R<br>1 = Right justi<br>0 = Left justifie                                                                                             | fied                                              | Select bit   |                           |                 |                 |       |

| bit 6        | Unimplement                                                                                                                                            | t <b>ed:</b> Read as '                            | 0'           |                           |                 |                 |       |

| bit 5-3      | ACQT<2:0>: .<br>111 = 20 TAD<br>110 = 16 TAD<br>101 = 12 TAD<br>100 = 8 TAD<br>011 = 6 TAD<br>010 = 4 TAD<br>001 = 2 TAD<br>000 = 0 TAD <sup>(1)</sup> |                                                   |              |                           |                 |                 |       |

| bit 2-0      | ADCS<2:0>: ,<br>111 = FRC (cli<br>110 = Fosc/6<br>101 = Fosc/1<br>100 = Fosc/4<br>011 = FRC (cli<br>010 = Fosc/3<br>001 = Fosc/8<br>000 = Fosc/2       | ock derived fro<br>4<br>6<br>ock derived fro<br>2 | om A/D RC os | scillator) <sup>(1)</sup> |                 |                 |       |

# **Note 1:** If the A/D FRC clock source is selected, a delay of one TCY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

#### REGISTER 21-3: ADCON2: A/D CONTROL REGISTER 2

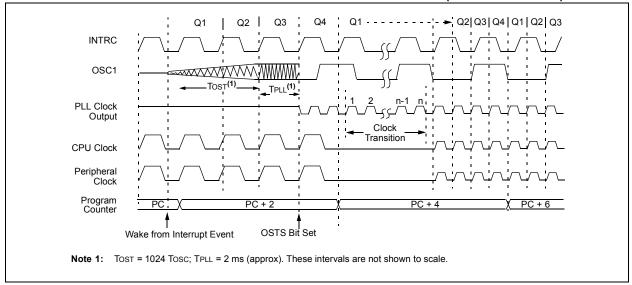

### 24.4 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period, from oscillator start-up to code execution, by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is HS or HSPLL (Crystal-based) modes. Since the EC and ECPLL modes do not require an OST start-up delay, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode. In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 24.4.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including serial SLEEP instructions (refer to **Section 4.1.4 "Multiple Sleep Commands"**). In practice, this means that user code can change the SCS1:SCS0 bits setting or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

#### FIGURE 24-3: TIMING TRANSITION FOR TWO-SPEED START-UP (INTRC TO HSPLL)

| NEGF              | Negate f                                                                                                                                                                                                                                                                                 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | NEGF f {,a}                                                                                                                                                                                                                                                                              |

| Operands:         | $0 \le f \le 255$                                                                                                                                                                                                                                                                        |

| Operation:        | $\mathbf{a} \in [0, 1]$<br>( $\mathbf{f}$ ) + 1 $\rightarrow$ f                                                                                                                                                                                                                          |

| Status Affected:  | N, OV, C, DC, Z                                                                                                                                                                                                                                                                          |

| Encoding:         | 0110 110a ffff ffff                                                                                                                                                                                                                                                                      |

| Description:      | Location 'f' is negated using two's complement. The result is placed in the data memory location 'f'.                                                                                                                                                                                    |

|                   | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.                                                                                                                                                                                 |

|                   | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |

| Words:            | 1                                                                                                                                                                                                                                                                                        |

| Cycles:           | 1                                                                                                                                                                                                                                                                                        |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                          |

| _ | Q1     | Q2           | Q3      | Q4           |

|---|--------|--------------|---------|--------------|

| ſ | Decode | Read         | Process | Write        |

|   |        | register 'f' | Data    | register 'f' |

| Example: | NEGF | REG, | 1 |

|----------|------|------|---|

|----------|------|------|---|

| Before Instruc    | tion |      |      |       |

|-------------------|------|------|------|-------|

| REG               | =    | 0011 | 1010 | [3Ah] |

| After Instruction | on   |      |      |       |

| REG               | =    | 1100 | 0110 | [C6h] |

| NOP                   | No Operation   |              |        |      |    |          |  |

|-----------------------|----------------|--------------|--------|------|----|----------|--|

| Synta                 | ax:            | NOP          |        |      |    |          |  |

| Oper                  | ands:          | None         |        |      |    |          |  |

| Oper                  | ation:         | No operation |        |      |    |          |  |

| Status Affected: None |                |              |        |      |    |          |  |

| Enco                  | ding:          | 0000         | 0000   | 000  | 0  | 0000     |  |

|                       |                | 1111         | XXXX   | XXX  | XX | XXXX     |  |

| Desc                  | ription:       | No operati   | on.    |      |    |          |  |

| Word                  | ls:            | 1            |        |      |    |          |  |

| Cycle                 | es:            | 1            |        |      |    |          |  |

| QC                    | ycle Activity: |              |        |      |    |          |  |

|                       | Q1             | Q2           | Q      | 3    |    | Q4       |  |

|                       | Decode         | No           | No No  |      |    |          |  |

|                       |                | operation    | operat | tion | op | peration |  |

Example:

None.

| TSTF                                                                                                                                                                                                                                                                                 | SZ                                               | Test f, Skip                 | ) if 0                                                                                                                                                              |                 |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                                | ax:                                              | TSTFSZ f {                   | ,a}                                                                                                                                                                 |                 |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                 | ands:                                            | 0≤f≤255<br>a∈[0,1]           |                                                                                                                                                                     |                 |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                 | ation:                                           | skip if f = 0                |                                                                                                                                                                     |                 |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                | s Affected:                                      | None                         |                                                                                                                                                                     |                 |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                 | ding:                                            | 0110                         | 011a fff                                                                                                                                                            | f ffff          |  |  |  |  |

| Description:                                                                                                                                                                                                                                                                         |                                                  | during the c<br>is discarded | If 'f' = 0, the next instruction fetched<br>during the current instruction execution<br>is discarded and a NOP is executed,<br>making this a two-cycle instruction. |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                      |                                                  |                              | ne Access Bar<br>ne BSR is used                                                                                                                                     |                 |  |  |  |  |

| If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                  |                              |                                                                                                                                                                     |                 |  |  |  |  |

| Word                                                                                                                                                                                                                                                                                 | ls:                                              | 1                            |                                                                                                                                                                     |                 |  |  |  |  |

| Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction.                                                                                                                                                                                                      |                                                  |                              |                                                                                                                                                                     |                 |  |  |  |  |

| QC                                                                                                                                                                                                                                                                                   | ycle Activity:                                   | - <b>,</b> -                 |                                                                                                                                                                     |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                      | Q1                                               | Q2                           | Q3                                                                                                                                                                  | Q4              |  |  |  |  |

|                                                                                                                                                                                                                                                                                      | Decode                                           | Read                         | Process                                                                                                                                                             | No              |  |  |  |  |

| lf als                                                                                                                                                                                                                                                                               | in.                                              | register 'f'                 | Data                                                                                                                                                                | operation       |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                | ιρ.<br>Q1                                        | Q2                           | Q3                                                                                                                                                                  | Q4              |  |  |  |  |

|                                                                                                                                                                                                                                                                                      | No                                               | No                           | No                                                                                                                                                                  | No              |  |  |  |  |

|                                                                                                                                                                                                                                                                                      | operation                                        | operation                    | operation                                                                                                                                                           | operation       |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                | ip and followe                                   | d by 2-word in               | struction:                                                                                                                                                          |                 |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                    | Q1                                               | Q2                           | Q3                                                                                                                                                                  | Q4              |  |  |  |  |

|                                                                                                                                                                                                                                                                                      | No                                               | No                           | No                                                                                                                                                                  | No              |  |  |  |  |

|                                                                                                                                                                                                                                                                                      | operation<br>No                                  | operation<br>No              | operation<br>No                                                                                                                                                     | operation<br>No |  |  |  |  |

|                                                                                                                                                                                                                                                                                      | operation                                        | operation                    | operation                                                                                                                                                           | operation       |  |  |  |  |

| <u>Exan</u>                                                                                                                                                                                                                                                                          | <u>nple:</u>                                     | HERE I<br>NZERO :<br>ZERO :  |                                                                                                                                                                     | , 1             |  |  |  |  |

|                                                                                                                                                                                                                                                                                      | Before Instruc<br>PC                             | = Ad                         | dress (HERE)                                                                                                                                                        | )               |  |  |  |  |