Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 66                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 15x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86j10t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

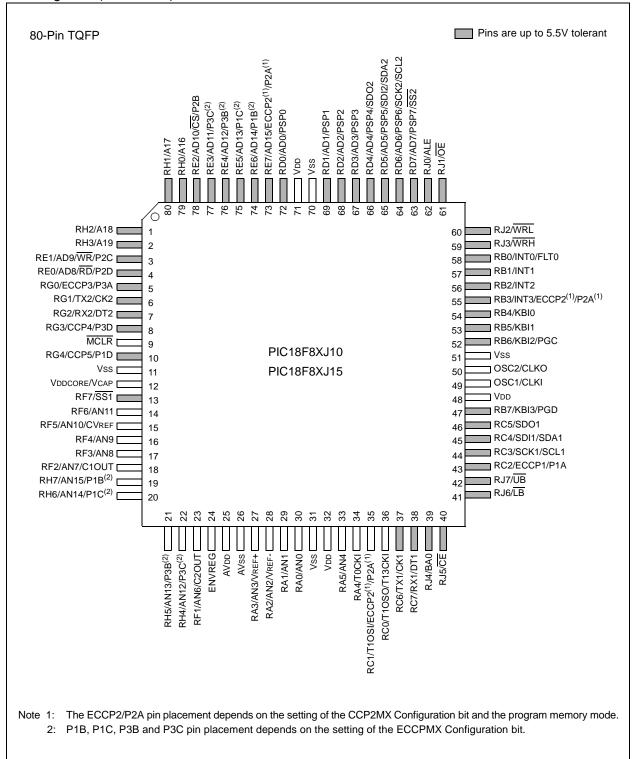

#### Pin Diagrams (Continued)

| TABLE 1-3: PIC18F         | ABLE 1-3: PIC18F6XJ10/6XJ15 PINO UT I/O DESCRIPTIONS (CONTINUED) |            |                      |                                                                     |  |  |

|---------------------------|------------------------------------------------------------------|------------|----------------------|---------------------------------------------------------------------|--|--|

| Pin Name                  | Pin Number                                                       | Pin        | Buffer               | Description                                                         |  |  |

| 1 III INdille             | TQFP                                                             | Туре       | Туре                 | Description                                                         |  |  |

|                           |                                                                  |            |                      | PORTD is a bidirectional I/O port.                                  |  |  |

| RD0/PSP0                  | 58                                                               |            |                      |                                                                     |  |  |

| RD0<br>PSP0               |                                                                  | 1/O<br>1/O | ST<br>TTL            | Digital I/O.<br>Parallel Slave Port data.                           |  |  |

| RD1/PSP1                  | 55                                                               | 1/0        |                      |                                                                     |  |  |

| RD1                       | 55                                                               | I/O        | ST                   | Digital I/O.                                                        |  |  |

| PSP1                      |                                                                  | I/O        | TTL                  | Parallel Slave Port data.                                           |  |  |

| RD2/PSP2                  | 54                                                               |            |                      |                                                                     |  |  |

| RD2<br>PSP2               |                                                                  | I/O<br>I/O | ST<br>TTL            | Digital I/O.<br>Parallel Slave Port data.                           |  |  |

| RD3/PSP3                  | 53                                                               |            |                      |                                                                     |  |  |

| RD3                       |                                                                  | I/O        | ST                   | Digital I/O.                                                        |  |  |

| PSP3                      |                                                                  | I/O        | TTL                  | Parallel Slave Port data.                                           |  |  |

| RD4/PSP4/SDO2<br>RD4      | 52                                                               | I/O        | ST                   | Digital I/O.                                                        |  |  |

| PSP4                      |                                                                  | 1/O        | TTL                  | Parallel Slave Port data.                                           |  |  |

| SDO2                      |                                                                  | 0          | —                    | SPI data out.                                                       |  |  |

| RD5/PSP5/SDI2/SDA2        | 51                                                               |            | 07                   |                                                                     |  |  |

| RD5<br>PSP5               |                                                                  | 1/O<br>1/O | ST<br>TTL            | Digital I/O.<br>Parallel Slave Port data.                           |  |  |

| SDI2                      |                                                                  | I          | ST                   | SPI data in.                                                        |  |  |

| SDA2                      |                                                                  | I/O        | I <sup>2</sup> C/SMB | I <sup>2</sup> C™ data I/O.                                         |  |  |

| RD6/PSP6/SCK2/SCL2<br>RD6 | 50                                                               | I/O        | ST                   | Digital I/O.                                                        |  |  |

| PSP6                      |                                                                  | 1/O        | TTL                  | Parallel Slave Port data.                                           |  |  |

| SCK2                      |                                                                  | I/O        | ST                   | Synchronous serial clock input/output for SPI mode.                 |  |  |

| SCL2                      |                                                                  | I/O        | I <sup>2</sup> C/SMB | Synchronous serial clock input/output for I <sup>2</sup> C mode.    |  |  |

| RD7/PSP7/SS2<br>RD7       | 49                                                               | I/O        | ST                   | Digital I/O.                                                        |  |  |

| PSP7                      |                                                                  | I/O        | TTL                  | Parallel Slave Port data.                                           |  |  |

| SS2                       |                                                                  | Ι          | TTL                  | SPI slave select input.                                             |  |  |

|                           | L compatible in<br>hmitt Trigger in                              |            | CMOS leve            | CMOS = CMOS compatible input or output<br>els Analog = Analog input |  |  |

| I = Inj                   | out                                                              |            |                      | O = Output                                                          |  |  |

| P = Pc                    | ower<br>C™/SMBus inpu                                            | ut buffor  |                      | OD = Open-Drain (no P diode to VDD)                                 |  |  |

|                           |                                                                  |            |                      |                                                                     |  |  |

### TABLE 1-3: PIC18F6XJ10/6XJ15 PINO UT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for ECCP2/P2A when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2/P2A when Configuration bit, CCP2MX, is cleared.

| R/W-0                                         | U-0                               | U-0               | U-0             | R-q <sup>(1)</sup>       | U-0               | R/W-0           | R/W-0 |  |  |

|-----------------------------------------------|-----------------------------------|-------------------|-----------------|--------------------------|-------------------|-----------------|-------|--|--|

| IDLEN                                         |                                   |                   |                 | OSTS                     | —                 | SCS1            | SCS0  |  |  |

| bit 7                                         |                                   |                   |                 |                          |                   |                 | bit 0 |  |  |

|                                               |                                   |                   |                 |                          |                   |                 |       |  |  |

| Legend: q = Value determined by configuration |                                   |                   |                 |                          |                   |                 |       |  |  |

| R = Readab                                    | ole bit                           | W = Writable      | bit             | U = Unimple              | mented bit, rea   | d as '0'        |       |  |  |

| -n = Value a                                  | it POR                            | '1' = Bit is set  |                 | '0' = Bit is cle         | eared             | x = Bit is unkr | nown  |  |  |

|                                               |                                   |                   |                 |                          |                   |                 |       |  |  |

| bit 7                                         | IDLEN: Idle E                     | nable bit         |                 |                          |                   |                 |       |  |  |

|                                               | 1 = Device er                     | nters Idle mode   | e on sleep ir   | nstruction               |                   |                 |       |  |  |

|                                               | 0 = Device er                     | nters Sleep mo    | de on SLEEP     | <sup>o</sup> instruction |                   |                 |       |  |  |

| bit 6-4                                       | Unimplemente                      | ed: Read as '     | o'              |                          |                   |                 |       |  |  |

| bit 3                                         | OSTS: Oscilla                     | ator Start-up Tir | me-out Status   | s bit <sup>(1)</sup>     |                   |                 |       |  |  |

|                                               |                                   |                   |                 |                          | ary oscillator is |                 |       |  |  |

|                                               | 0 = Oscillator                    | Start-up Time     | r time-out is r | unning; primar           | y oscillator is n | ot ready        |       |  |  |

| bit 2                                         | Unimplemente                      | ed: Read as '     | כ'              |                          |                   |                 |       |  |  |

| bit 1-0                                       | SCS<1:0>: S                       | ystem Clock Se    | elect bits      |                          |                   |                 |       |  |  |

|                                               | 11 = Internal                     | e e e e marei     |                 |                          |                   |                 |       |  |  |

|                                               | 10 = Primary oscillator           |                   |                 |                          |                   |                 |       |  |  |

|                                               | 01 = Timer1 c                     |                   |                 |                          |                   |                 |       |  |  |

|                                               | <u>When FOSC2</u><br>00 = Primary |                   |                 |                          |                   |                 |       |  |  |

|                                               | When FOSC2                        |                   |                 |                          |                   |                 |       |  |  |

|                                               | 00 = Internal                     |                   |                 |                          |                   |                 |       |  |  |

|                                               |                                   |                   |                 |                          |                   |                 |       |  |  |

#### REGISTER 3-2: OSCCON: OSCILLATOR CONTROL REGISTER

Note 1: The Reset value is '0' when HS mode and Two-Speed Start-up are both enabled; otherwise, it is '1'.

## 6.1.3 PIC18F8XJ10/8XJ15 PROGRAM MEMORY MODES

The 80-pin devices in this family can address up to a total of 2 Mbytes of program memory. This is achieved through the external memory bus. There are two distinct operating modes available to the controllers:

- Microcontroller (MC)

- Extended Microcontroller (EMC)

The program memory mode is determined by setting the EMB Configuration bits (CONFIG3L<5:4>), as shown in Register 6-1. (See also Section 24.1 "Configuration Bits" for additional details on the device Configuration bits.)

The program memory modes operate as follows:

• The Microcontroller Mode accesses only on-chip Flash memory. Attempts to read above the top of on-chip memory causes a read of all '0's (a NOP instruction).

The Microcontroller mode is also the only operating mode available to 64-pin devices.

The Extended Microcontroller Mode allows access to both internal and external program memories as a single block. The device can access its entire on-chip program memory; above this, the device accesses external program memory up to the 2-Mbyte program space limit. Execution automatically switches between the two memories as required.

The setting of the EMB Configuration bits also controls the address bus width of the external memory bus. This is covered in more detail in Section 8.0 "External Memory Bus".

In all modes, the microcontroller has complete access to data RAM.

Figure 6-3 compares the memory maps of the different program memory modes. The differences between on-chip and external memory access limitations are more fully explained in Table 6-2.

### REGISTER 6-1: CONFIG3L: CONFIGURATION REGISTER 3 LOW

| R/WO-1 | R/WO-1 | R/WO-1 | R/WO-1 | R/WO-1 | U-0 | U-0 | U-0   |

|--------|--------|--------|--------|--------|-----|-----|-------|

| WAIT   | BW     | EMB1   | EMB0   | EASHFT |     | _   | —     |

| bit 7  |        |        |        |        |     |     | bit 0 |

| Legend:                |                     |                        |                    |

|------------------------|---------------------|------------------------|--------------------|

| R = Readable bit       | WO = Write-Once bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value after erase | '1' = Bit is set    | '0' = Bit is cleared   | x = Bit is unknown |

|                        |                     | 0 = Dit is cleared     | X = DILIS UTKHOWH  |

| bit 7   | Wait: External Bus Wait Enable bit                                                                                                                                                                                                                                                                                                          |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Wait states on the external bus are disabled</li> <li>0 = Wait states on the external bus are enabled and selected by MEMCON&lt;5:4&gt;</li> </ul>                                                                                                                                                                             |

| bit 6   | BW: Data Bus Width Select bit<br>1 = 16-Bit Data Width modes<br>0 = 8-Bit Data Width modes                                                                                                                                                                                                                                                  |

| bit 5-4 | EMB<1:0>: External Memory Bus Configuration bits<br>11 = Microcontroller mode, external bus disabled<br>10 = Extended Microcontroller mode, 12-bit address width for external bus<br>01 = Extended Microcontroller mode, 16-bit address width for external bus<br>00 = Extended Microcontroller mode, 20-bit address width for external bus |

| bit 3   | EASHFT: External Address Bus Shift Enable bit<br>1 = Address shifting enabled – external address bus is shifted to start at 000000h<br>0 = Address shifting disabled – external address bus reflects the PC value                                                                                                                           |

| bit 2-0 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                  |

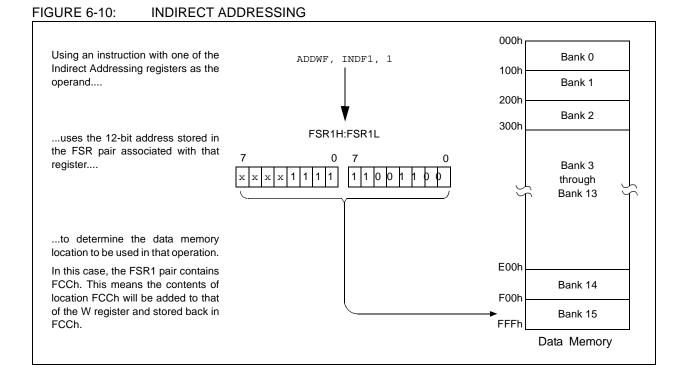

## 6.4.3.1 FSR Registers and the INDF Operand

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used, so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

### 8.3 Wait States

While it may be assumed that external memory devices will operate at the microcontroller clock rate, this is often not the case. In fact, many devices require longer times to write or retrieve data than the time allowed by the execution of table read or table write operations.

To compensate for this, the external memory bus can be configured to add a fixed delay to each table operation using the bus. Wait states are enabled by setting the WAIT Configuration bit. When enabled, the amount of delay is set by the WAIT<1:0> bits (MEMCON<5:4>). The delay is based on multiples of microcontroller instruction cycle time and are added following the instruction cycle when the table operation is executed. The range is from no delay to 3 Tcy (default value).

### 8.4 Port Pin Weak Pull-ups

With the exception of the upper address lines, A<19:16>, the pins associated with the external memory bus are equipped with weak pull-ups. The pull-ups are controlled by the upper three bits of the PORTG register. They are named RDPU, REPU and RJPU and control pull-ups on PORTD, PORTE and PORTJ, respectively. Clearing one of these bits enables the corresponding pull-ups for that port. All pull-ups are disabled by default on all device Resets.

### 8.5 Program Memory Modes and the External Memory Bus

The PIC18F87J10 family of devices is capable of operating in one of two program memory modes, using combinations of on-chip and external program memory. The functions of the multiplexed port pins depend on the program memory mode selected, as well as the setting of the EBDIS bit.

In Microcontroller Mode, the bus is not active and the pins have their port functions only. Writes to the MEMCOM register are not permitted. The Reset value of EBDIS ('0') is ignored and EMB pins behave as I/O ports.

In Extended Microcontroller Mode, the external program memory bus shares I/O port functions on the pins. When the device is fetching or doing table read/table write operations on the external program memory space, the pins will have the external bus function.

If the device is fetching and accessing internal program memory locations only, the EBDIS control bit will change the pins from external memory to I/O port functions. When EBDIS = 0, the pins function as the external bus. When EBDIS = 1, the pins function as I/O ports.

If the device fetches or accesses external memory while EBDIS = 1, the pins will switch to external bus. If the EBDIS bit is set by a program executing from external memory, the action of setting the bit will be delayed until the program branches into the internal memory. At that time, the pins will change from external bus to I/O ports.

If the device is executing out of internal memory when EBDIS = 0, the memory bus address/data and control pins will not be active. They will go to a state where the active address/data pins are tri-state; the  $\overline{CE}$ ,  $\overline{OE}$ ,  $\overline{WRH}$ ,  $\overline{WRL}$ ,  $\overline{UB}$  and  $\overline{LB}$  signals are '1' and ALE and BA0 are '0'. Note that only those pins associated with the current address width are forced to tri-state; the other pins continue to function as I/O. In the case of 16-bit address width, for example, only AD<15:0> (PORTD and PORTE) are affected; A<19:16> (PORTH<3:0>) continue to function as I/O.

In all external memory modes, the bus takes priority over any other peripherals that may share pins with it. This includes the Parallel Slave Port and serial communications modules which would otherwise take priority over the I/O port.

### 8.6 16-Bit Data Width Modes

In 16-Bit Data Width mode, the external memory interface can be connected to external memories in three different configurations:

- 16-Bit Byte Write

- 16-Bit Word Write

- 16-Bit Byte Select

The configuration to be used is determined by the WM<1:0> bits in the MEMCON register (MEMCON<1:0>). These three different configurations allow the designer maximum flexibility in using both 8-bit and 16-bit devices with 16-bit data.

For all 16-bit modes, the Address Latch Enable (ALE) pin indicates that the address bits, AD<15:0>, are available on the external memory interface bus. Following the address latch, the Output Enable signal ( $\overline{OE}$ ) will enable both bytes of program memory at once to form a 16-bit instruction word. The Chip Enable signal ( $\overline{CE}$ ) is active at any time that the microcontroller accesses external memory, whether reading or writing; it is inactive (asserted high) whenever the device is in Sleep mode.

In Byte Select mode, JEDEC standard Flash memories will require BA0 for the byte address line and one I/O line to select between Byte and Word mode. The other 16-bit modes do not need BA0. JEDEC standard static RAM memories will use the UB or LB signals for byte selection.

## 12.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software-selectable operation as a timer or counter in both 8-bit or 16-bit modes

- Readable and writable registers

- Dedicated 8-bit, software programmable prescaler

- · Selectable clock source (internal or external)

- Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 12-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 12-1. Figure 12-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

#### REGISTER 12-1: TOCON: TIMERO CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR0ON | T08BIT | TOCS  | TOSE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:      |                                                  |                                                                                                                                                                                                                                        |                                                                      |                    |

|--------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------|

| R = Readat   | ole bit                                          | W = Writable bit                                                                                                                                                                                                                       | U = Unimplemented bit,                                               | read as '0'        |

| -n = Value a | at POR                                           | '1' = Bit is set                                                                                                                                                                                                                       | '0' = Bit is cleared                                                 | x = Bit is unknown |

| bit 7        | TMR0ON:<br>1 = Enabl<br>0 = Stops                |                                                                                                                                                                                                                                        |                                                                      |                    |

| bit 6        | T08BIT: T<br>1 = Timer                           | imer0 8-Bit/16-Bit Control b<br>0 is configured as an 8-bit ti<br>0 is configured as a 16-bit ti                                                                                                                                       | mer/counter                                                          |                    |

| bit 5        | 1 = Transi                                       | ner0 Clock Source Select bi<br>ition on T0CKI pin<br>al instruction cycle clock (C                                                                                                                                                     | -                                                                    |                    |

| bit 4        | 1 = Incren                                       | ner0 Source Edge Select bit<br>nent on high-to-low transitio<br>nent on low-to-high transitio                                                                                                                                          | n on T0CKI pin                                                       |                    |

| bit 3        | 1 = TImer                                        |                                                                                                                                                                                                                                        | it<br>d. Timer0 clock input bypasse<br>ner0 clock input comes from p | •                  |

| bit 2-0      | 111 = 1:2<br>110 = 1:1<br>101 = 1:6<br>100 = 1:3 | <ul> <li>b&gt;: Timer0 Prescaler Select</li> <li>56 Prescale value</li> <li>28 Prescale value</li> <li>4 Prescale value</li> <li>2 Prescale value</li> <li>6 Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> </ul> | bits                                                                 |                    |

001 = 1:4 Prescale value 000 = 1:2 Prescale value

## 15.0 TIMER3 MODULE

The Timer3 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external) with

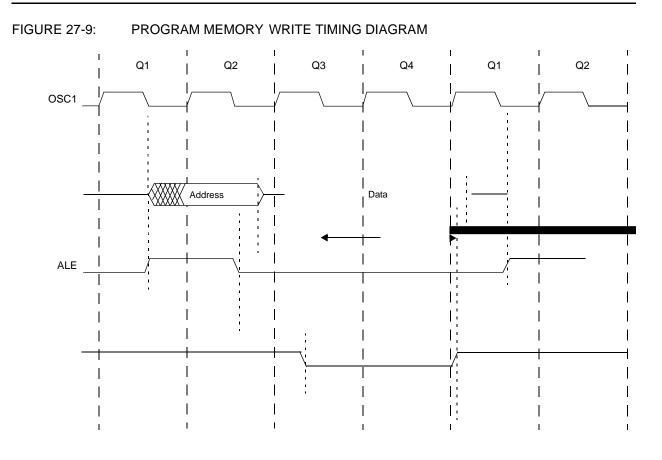

TABLE 27-11: PROGRAM MEMORY WRITE TIMING REQUIREMENTS

| Param.<br>No | Symbol   | Characteristics                                            | Min           | Тур     | Max l | Inits |

|--------------|----------|------------------------------------------------------------|---------------|---------|-------|-------|

| 150          | TadV2alL | Address Out Valid to ALE p(address setup time)             | 0.25 Tcy – 10 |         | —     | ns    |

| 151          | TalL2adl | ALE pto Address Out Invalid (address hold time)            | 5             |         | —     | ns    |

| 153          | TwrH2adl | WRn nto Data Out Invalid (data hold time)                  | 5             |         | —     | ns    |

| 154          | TwrL     | WRn Pulse Width                                            | 0.5 Tcy – 5   | 0.5 TCY | _     | ns    |

| 156          | TadV2wrH | Data Valid before WRn n(data setup time)                   | 0.5 Tcy – 10  |         | _     | ns    |

| 157          | TbsV2wrL | Byte Select Valid before WRn p<br>(byte select setup time) | 0.25 Tcy      |         | —     | ns    |

| 157A         | TwrH2bsl | WRn nto Byte Select Invalid (byte select hold time)        | 0.125 Tcy – 5 |         | _     | ns    |

| 166          | TalH2alH | ALE nto ALE n(cycle time)                                  | —             | Тсү     | _     | ns    |

| 171          | TalH2csL | Chip Enable Active to ALE p                                | 0.25 Tcy – 20 | _       | _     | ns    |

| 171A         | TubL2oeH | AD Valid to Chip Enable Active                             |               | _       | 10    | ns    |

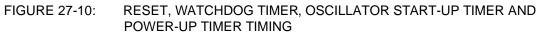

#### TABLE 27-12: RESET, WATCHDOG TIMER, OSCILL ATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic                                              | Min 7     | ӯҏ  | Max U     | nits | Conditions         |

|---------------|--------|-------------------------------------------------------------|-----------|-----|-----------|------|--------------------|

| 30            | TMCL   | MCLR Pulse Width (low)                                      | 2         | —   | _         | Rs   |                    |

| 31            | Twdt   | Watchdog Timer Time-out Period<br>(no postscaler)           | 3.5       | 4.1 | 4.9       | ms   |                    |

| 32            | Tost   | Oscillation Start-up Timer Period                           | 1024 Tosc |     | 1024 Tosc | —    | Tosc = OSC1 period |

| 33            | TPWRT  | Power-up Timer Period                                       | 57.4      | 66  | 77.7      | ms   |                    |

| 34            | Tioz   | I/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset | —         | 2   | —         | ß    |                    |

| 38            | TCSD   | CPU Start-up Time                                           | —         | 200 | —         | Rs   |                    |