Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I²C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 66                                                                         |

| Program Memory Size        | 96KB (48K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 15x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

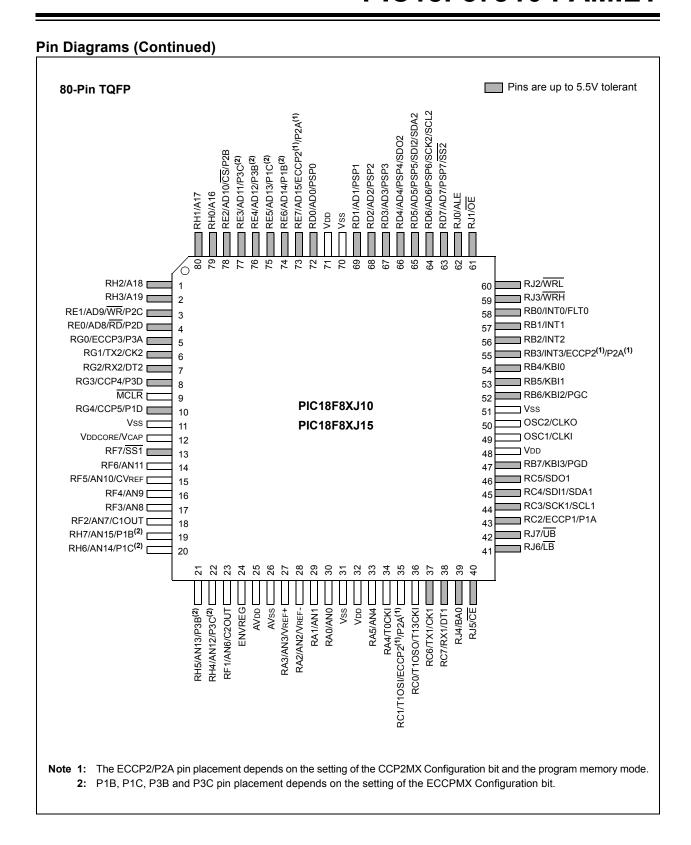

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86j15-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-3: PIC18F6XJ10/6XJ15 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                             | Pin Number    | Pin             | Buffer         | Description                                                                                                                     |

|--------------------------------------|---------------|-----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                             | TQFP          | Type            | Type           | Description                                                                                                                     |

|                                      |               |                 |                | PORTG is a bidirectional I/O port.                                                                                              |

| RG0/ECCP3/P3A<br>RG0<br>ECCP3<br>P3A | 3             | I/O<br>I/O<br>O | ST<br>ST<br>—  | Digital I/O. Capture 3 input/Compare 3 output/PWM 3 output. ECCP3 PWM output A.                                                 |

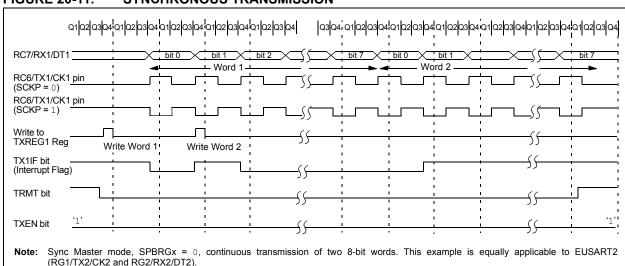

| RG1/TX2/CK2<br>RG1<br>TX2<br>CK2     | 4             | I/O<br>O<br>I/O | ST<br>—<br>ST  | Digital I/O. EUSART2 asynchronous transmit. EUSART2 synchronous clock (see related RX2/DT2).                                    |

| RG2/RX2/DT2<br>RG2<br>RX2<br>DT2     | 5             | I/O<br>I<br>I/O | ST<br>ST<br>ST | Digital I/O. EUSART2 asynchronous receive. EUSART2 synchronous data (see related TX2/CK2).                                      |

| RG3/CCP4/P3D<br>RG3<br>CCP4<br>P3D   | 6             | I/O<br>I/O<br>O | ST<br>ST       | Digital I/O. Capture 4 input/Compare 4 output/PWM 4 output. ECCP3 PWM output D.                                                 |

| RG4/CCP5/P1D<br>RG4<br>CCP5<br>P1D   | 8             | I/O<br>I/O<br>O | ST<br>ST       | Digital I/O. Capture 5 input/Compare 5 output/PWM 5 output. ECCP1 PWM output D.                                                 |

| Vss                                  | 9, 25, 41, 56 | Р               | _              | Ground reference for logic and I/O pins.                                                                                        |

| VDD                                  | 26, 38, 57    | Р               | _              | Positive supply for peripheral digital logic and I/O pins.                                                                      |

| AVss                                 | 20            | Р               | _              | Ground reference for analog modules.                                                                                            |

| AVDD                                 | 19            | Р               | _              | Positive supply for analog modules.                                                                                             |

| ENVREG                               | 18            | 1               | ST             | Enable for on-chip voltage regulator.                                                                                           |

| VDDCORE/VCAP<br>VDDCORE              | 10            | Р               | _              | Core logic power or external filter capacitor connection.  Positive supply for microcontroller core logic (regulator disabled). |

| VCAP                                 |               | Р               |                | External filter capacitor connection (regulator enabled).                                                                       |

**Legend:** TTL = TTL compatible input CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open-Drain (no P diode to VDD)

$I^2C/SMB = I^2C^{TM}/SMBus$  input buffer

Note 1: Default assignment for ECCP2/P2A when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2/P2A when Configuration bit, CCP2MX, is cleared.

#### 3.6.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 3-2) controls several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

The System Clock Select bits, SCS<1:0>, select the clock source. The available clock sources are the primary clock (defined by the FOSC<2:0> Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator. The clock source changes after one or more of the bits are written to, following a brief clock transition interval.

The OSTS (OSCCON<3>) and T1RUN (T1CON<6>) bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer (OST) has timed out and the primary clock is providing the device clock in primary clock modes. The T1RUN bit indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these bits will be set at any time. If neither of these bits are set, the INTRC is providing the clock, or the internal oscillator has just started and is not yet stable.

The IDLEN bit determines if the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "Power-Managed Modes".

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before executing the SLEEP instruction or a very long delay may occur while the Timer1 oscillator starts.

### 3.6.1.1 System Clock Selection and the FOSC2 Configuration Bit

The SCS bits are cleared on all forms of Reset. In the device's default configuration, this means the primary oscillator defined by FOSC<1:0> (that is, one of the HC or EC modes) is used as the primary clock source on device Resets.

The default clock configuration on Reset can be changed with the FOSC2 Configuration bit. The effect of this bit is to set the clock source selected when SCS<1:0> = 00. When FOSC2 = 1 (default), the oscillator source defined by FOSC<1:0> is selected whenever SCS<1:0> = 00. When FOSC2 = 0, the INTRC oscillator is selected whenever SCS<1:2> = 00. Because the SCS bits are cleared on Reset, the FOSC2 setting also changes the default oscillator mode on Reset.

Regardless of the setting of FOSC2, INTRC will always be enabled on device power-up. It will serve as the clock source until the device has loaded its configuration values from memory. It is at this point that the FOSC Configuration bits are read and the oscillator selection of the operational mode is made.

Note that either the primary clock or the internal oscillator will have two bit setting options, at any given time, depending on the setting of FOSC2.

#### 3.6.2 OSCILLATOR TRANSITIONS

PIC18F87J10 family devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 4.1.2 "Entering Power-Managed Modes"**.

### TABLE 6-4: REGISTER FILE SUMMARY (PIC18F87J10 FAMILY) (CONTINUED)

| File Name | Bit 7                                         | Bit 6           | Bit 5                     | Bit 4            | Bit 3           | Bit 2          | Bit 1                      | Bit 0   | Value on POR, BOR | Details on page: |

|-----------|-----------------------------------------------|-----------------|---------------------------|------------------|-----------------|----------------|----------------------------|---------|-------------------|------------------|

| SPBRGH1   | EUSART1 Ba                                    | aud Rate Gene   | erator Registe            | r High Byte      |                 |                |                            |         | 0000 0000         | 56, 243          |

| BAUDCON1  | ABDOVF                                        | RCIDL           | _                         | SCKP             | BRG16           | _              | WUE                        | ABDEN   | 01-0 0-00         | 56, 242          |

| SPBRGH2   | EUSART2 Ba                                    | aud Rate Gene   | erator Registe            | r High Byte      |                 |                | •                          | •       | 0000 0000         | 56, 243          |

| BAUDCON2  | ABDOVF                                        | RCIDL           | _                         | SCKP             | BRG16           | _              | WUE                        | ABDEN   | 01-0 0-00         | 56, 242          |

| ECCP1DEL  | P1RSEN                                        | P1DC6           | P1DC5                     | P1DC4            | P1DC3           | P1DC2          | P1DC1                      | P1DC0   | 0000 0000         | 57, 188          |

| TMR4      | Timer4 Regis                                  | ster            |                           |                  |                 |                |                            |         | 0000 0000         | 57, 168          |

| PR4       | Timer4 Perio                                  | d Register      |                           |                  |                 |                |                            |         | 1111 1111         | 57, 168          |

| T4CON     | _                                             | T4OUTPS3        | T4OUTPS2                  | T4OUTPS1         | T4OUTPS0        | TMR4ON         | T4CKPS1                    | T4CKPS0 | -000 0000         | 57, 167          |

| CCPR4H    | Capture/Com                                   | pare/PWM Re     | egister 4 High            | Byte             |                 |                | •                          | •       | xxxx xxxx         | 57, 170          |

| CCPR4L    | Capture/Com                                   | npare/PWM Re    | egister 4 Low E           | Byte             |                 |                |                            |         | xxxx xxxx         | 57, 170          |

| CCP4CON   | _                                             | _               | DC4B1                     | DC4B0            | CCP4M3          | CCP4M2         | CCP4M1                     | CCP4M0  | 00 0000           | 57, 169          |

| CCPR5H    | Capture/Com                                   | pare/PWM Re     | egister 5 High            | Byte             |                 |                | •                          | •       | xxxx xxxx         | 57, 170          |

| CCPR5L    | Capture/Com                                   | npare/PWM Re    | egister 5 Low E           | Byte             |                 |                |                            |         | xxxx xxxx         | 57, 170          |

| CCP5CON   | _                                             | _               | DC5B1                     | DC5B0            | CCP5M3          | CCP5M2         | CCP5M1                     | CCP5M0  | 00 0000           | 57, 169          |

| SPBRG2    | EUSART2 Baud Rate Generator Register Low Byte |                 |                           |                  |                 |                |                            |         | 0000 0000         | 57, 243          |

| RCREG2    | EUSART2 Receive Register                      |                 |                           |                  |                 |                |                            |         | 0000 0000         | 57, 251,<br>252  |

| TXREG2    | EUSART2 Tr                                    | ansmit Regist   | er                        |                  |                 |                |                            |         | 0000 0000         | 57, 249,<br>250  |

| TXSTA2    | CSRC                                          | TX9             | TXEN                      | SYNC             | SENDB           | BRGH           | TRMT                       | TX9D    | 0000 0010         | 57, 240          |

| RCSTA2    | SPEN                                          | RX9             | SREN                      | CREN             | ADDEN           | FERR           | OERR                       | RX9D    | 0000 000x         | 57, 241          |

| ECCP3AS   | ECCP3ASE                                      | ECCP3AS2        | ECCP3AS1                  | ECCP3AS0         | PSS3AC1         | PSS3AC0        | PSS3BD1                    | PSS3BD0 | 0000 0000         | 57, 189          |

| ECCP3DEL  | P3RSEN                                        | P3DC6           | P3DC5                     | P3DC4            | P3DC3           | P3DC2          | P3DC1                      | P3DC0   | 0000 0000         | 57, 188          |

| ECCP2AS   | ECCP2ASE                                      | ECCP2AS2        | ECCP2AS1                  | ECCP2AS0         | PSS2AC1         | PSS2AC0        | PSS2BD1                    | PSS2BD0 | 0000 0000         | 57, 189          |

| ECCP2DEL  | P2RSEN                                        | P2DC6           | P2DC5                     | P2DC4            | P2DC3           | P2DC2          | P2DC1                      | P2DC0   | 0000 0000         | 57, 188          |

| SSP2BUF   | MSSP2 Rece                                    | eive Buffer/Tra | nsmit Register            | r                |                 |                |                            |         | xxxx xxxx         | 57, 203,<br>238  |

| SSP2ADD   | MSSP2 Addr                                    | ess Register (  | I <sup>2</sup> C™ Slave m | node), MSSP2     | Baud Rate Re    | load Register  | (I <sup>2</sup> C Master m | node)   | 0000 0000         | 57, 203          |

| SSP2STAT  | SMP                                           | CKE             | D/Ā                       | Р                | S               | R/W            | UA                         | BF      | 0000 0000         | 57, 194,<br>204  |

| SSP2CON1  | WCOL                                          | SSPOV           | SSPEN                     | CKP              | SSPM3           | SSPM2          | SSPM1                      | SSPM0   | 0000 0000         | 57, 206,<br>205  |

| SSP2CON2  | GCEN                                          | ACKSTAT         | ACKDT/<br>ADMSK5          | ACKEN/<br>ADMSK4 | RCEN/<br>ADMSK3 | PEN/<br>ADMSK2 | RSEN/<br>ADMSK1            | SEN     | 0000 0000         | 57, 206          |

Legend:

x = unknown, u = unchanged, – = unimplemented, q = value depends on condition

- Note 1: Bit 21 of the PC is only available in Serial Programming modes.

- 2: These bits and/or registers are only available in 80-pin devices; otherwise, they are unimplemented and read as '0'. Reset values are shown for 80-pin devices.

- 3: This register and its bits are not implemented in 64-pin devices. In 80-pin devices, the bits are unwritable and read as '0' in Microcontroller mode.

- 4: The PLLEN bit is available only when either ECPLL or HSPLL Oscillator modes are selected; otherwise, the bit is read as '0'.

- **5:** Reset value is '0' when Two-Speed Start-up is enabled and '1' if disabled.

#### 8.2 Address and Data Width

The PIC18F87J10 family of devices can be independently configured for different address and data widths on the same memory bus. Both address and data width are set by Configuration bits in the CONFIG3L register. As Configuration bits, this means that these options can only be configured by programming the device and are not controllable in software.

The BW bit selects an 8-bit or 16-bit data bus width. Setting this bit (default) selects a data width of 16 bits.

The EMB<1:0> bits determine both the program memory operating mode and the address bus width. The available options are 20-bit, 16-bit and 12-bit, as well as Microcontroller mode (external bus disabled). Selecting a 16-bit or 12-bit width makes a corresponding number of high-order lines available for I/O functions. These pins are no longer affected by the setting of the EBDIS bit. For example, selecting a 16-Bit Addressing mode (EMB<1:0> = 01) disables A<19:16> and allows PORTH<3:0> to function without interruptions from the bus. Using the smaller address widths allows users to tailor the memory bus to the size of the external memory space for a particular design while freeing up pins for dedicated I/O operation.

Because the EMB bits have the effect of disabling pins for memory bus operations, it is important to always select an address width at least equal to the data width. If a 12-bit address width is used with a 16-bit data width, the upper four bits of data will not be available on the bus.

All combinations of address and data widths require multiplexing of address and data information on the same lines. The address and data multiplexing, as well as I/O ports made available by the use of smaller address widths, are summarized in Table 8-2.

### 8.2.1 ADDRESS SHIFTING ON THE EXTERNAL BUS

By default, the address presented on the external bus is the value of the PC. In practical terms, this means that addresses in the external memory device below the top of on-chip memory are unavailable to the microcontroller. To access these physical locations, the glue logic between the microcontroller and the external memory must somehow translate addresses.

To simplify the interface, the external bus offers an extension of Extended Microcontroller mode that automatically performs address shifting. This feature is controlled by the EASHFT Configuration bit. Setting this bit offsets addresses on the bus by the size of the microcontroller's on-chip program memory and sets the bottom address at 0000h. This allows the device to use the entire range of physical addresses of the external memory.

#### 8.2.2 21-BIT ADDRESSING

As an extension of 20-bit address width operation, the external memory bus can also fully address a 2-Mbyte memory space. This is done by using the Bus Address bit 0 (BA0) control line as the Least Significant bit of the address. The  $\overline{\text{UB}}$  and  $\overline{\text{LB}}$  control signals may also be used with certain memory devices to select the upper and lower bytes within a 16-bit wide data word.

This addressing mode is available in both 8-Bit and certain 16-Bit Data Width modes. Additional details are provided in Section 8.6.3 "16-Bit Byte Select Mode" and Section 8.7 "8-Bit Mode".

TABLE 8-2: ADDRESS AND DATA LINES FOR DIFFERENT ADDRESS AND DATA WIDTHS

| Data Width | Address Width | Multiplexed Data and<br>Address Lines (and<br>Corresponding Ports) | Address Only Lines (and Corresponding Ports)      | Ports Available<br>for I/O  |

|------------|---------------|--------------------------------------------------------------------|---------------------------------------------------|-----------------------------|

|            | 12-Bit        |                                                                    | AD<11:8><br>(PORTE<3:0>)                          | PORTE<7:4>,<br>All of PORTH |

| 8-Bit      | 16-Bit        | AD<7:0><br>(PORTD<7:0>)                                            | AD<15:8><br>(PORTE<7:0>)                          | All of PORTH                |

|            | 20-Bit        | (1 01112 17.07)                                                    | A<19:16>, AD<15:8><br>(PORTH<3:0>,<br>PORTE<7:0>) | _                           |

|            | 16-Bit        | AD<15:0>                                                           | _                                                 | All of PORTH                |

| 16-Bit     | 20-Bit        | (PORTD<7:0>,<br>PORTE<7:0>)                                        | A<19:16><br>(PORTH<3:0>)                          | _                           |

TABLE 11-9: PORTD FUNCTIONS

| Pin Name     | Function           | TRIS<br>Setting            | I/O | I/O Type             | Description                                                                       |  |  |  |

|--------------|--------------------|----------------------------|-----|----------------------|-----------------------------------------------------------------------------------|--|--|--|

| RD0/AD0/PSP0 | RD0                | 0                          | 0   | DIG                  | LATD<0> data output.                                                              |  |  |  |

|              |                    | 1                          | ı   | ST                   | PORTD<0> data input.                                                              |  |  |  |

|              | AD0 <sup>(2)</sup> | AD0 <sup>(2)</sup> x O DIG |     |                      | External memory interface, address/data bit 0 output.(1)                          |  |  |  |

|              |                    | Х                          | ı   | TTL                  | External memory interface, data bit 0 input. (1)                                  |  |  |  |

|              | PSP0               |                            | 0   | DIG                  | PSP read output data (LATD<0>); takes priority over port data.                    |  |  |  |

|              |                    |                            | ı   | TTL                  | PSP write data input.                                                             |  |  |  |

| RD1/AD1/PSP1 | RD1                | 0                          | 0   | DIG                  | LATD<1> data output.                                                              |  |  |  |

|              |                    | 1                          | ı   | ST                   | PORTD<1> data input.                                                              |  |  |  |

|              | AD1 <sup>(2)</sup> | Х                          | 0   | DIG                  | External memory interface, address/data bit 1 output.(1)                          |  |  |  |

|              |                    | Х                          | I   | TTL                  | External memory interface, data bit 1 input. (1)                                  |  |  |  |

|              | PSP1               | Х                          | 0   | DIG                  | PSP read output data (LATD<1>); takes priority over port data.                    |  |  |  |

|              |                    | Х                          | I   | TTL                  | PSP write data input.                                                             |  |  |  |

| RD2/AD2/PSP2 | RD2                | 0                          | 0   | DIG                  | LATD<2> data output.                                                              |  |  |  |

|              |                    | 1                          | I   | ST                   | PORTD<2> data input.                                                              |  |  |  |

|              | AD2 <sup>(2)</sup> | Х                          | 0   | DIG                  | External memory interface, address/data bit 2 output.(1)                          |  |  |  |

|              |                    | Х                          | I   | TTL                  | External memory interface, data bit 2 input. (1)                                  |  |  |  |

|              | PSP2               | Х                          | 0   | DIG                  | PSP read output data (LATD<2>); takes priority over port data.                    |  |  |  |

| x I TTL F    |                    |                            | I   | TTL                  | PSP write data input.                                                             |  |  |  |

| RD3/AD3/PSP3 | RD3                | 0                          | 0   | DIG                  | LATD<3> data output.                                                              |  |  |  |

|              |                    | 1                          | ı   | ST                   | PORTD<3> data input.                                                              |  |  |  |

|              | AD3 <sup>(2)</sup> | Х                          | 0   | DIG                  | External memory interface, address/data bit 3 output. (1)                         |  |  |  |

|              |                    | Х                          | ı   | TTL                  | External memory interface, data bit 3 input. (1)                                  |  |  |  |

|              | PSP3               | Х                          | 0   | DIG                  | PSP read output data (LATD<3>); takes priority over port data.                    |  |  |  |

|              |                    | Х                          | I   | TTL                  | PSP write data input.                                                             |  |  |  |

| RD4/AD4/     | RD4                | 0                          | 0   | DIG                  | LATD<4> data output.                                                              |  |  |  |

| PSP4/SDO2    |                    | 1                          | I   | ST                   | PORTD<4> data input.                                                              |  |  |  |

|              | AD4 <sup>(2)</sup> | Х                          | 0   | DIG                  | External memory interface, address/data bit 4 output. (1)                         |  |  |  |

|              |                    | Х                          | I   | TTL                  | External memory interface, data bit 4 input. (1)                                  |  |  |  |

|              | PSP4               | Х                          | 0   | DIG                  | PSP read output data (LATD<4>); takes priority over port data.                    |  |  |  |

|              |                    | Х                          | ı   | TTL                  | PSP write data input.                                                             |  |  |  |

|              | SDO2               | 0                          | 0   | DIG                  | SPI data output (MSSP2 module); takes priority over port data.                    |  |  |  |

| RD5/AD5/     | RD5                | 0                          | 0   | DIG                  | LATD<5> data output.                                                              |  |  |  |

| PSP5/SDI2/   |                    | 1                          | I   | ST                   | PORTD<5> data input.                                                              |  |  |  |

| SDA2         | AD5 <sup>(2)</sup> | Х                          | 0   | DIG                  | External memory interface, address/data bit 5 output. (1)                         |  |  |  |

|              |                    | Х                          | I   | TTL                  | External memory interface, data bit 5 input. (1)                                  |  |  |  |

|              | PSP5               | Х                          | 0   | DIG                  | PSP read output data (LATD<5>); takes priority over port data.                    |  |  |  |

|              |                    | Х                          | I   | TTL                  | PSP write data input.                                                             |  |  |  |

| ľ            | SDI2               | 1                          | I   | ST                   | SPI data input (MSSP2 module).                                                    |  |  |  |

|              | SDA2               | 1                          | 0   | DIG                  | I <sup>2</sup> C™ data output (MSSP2 module); takes priority over port data.      |  |  |  |

|              |                    | 1                          | I   | I <sup>2</sup> C/SMB | I <sup>2</sup> C data input (MSSP2 module); input type depends on module setting. |  |  |  |

**Legend:** PWR = Power Supply, O = Output, I = Input, I<sup>2</sup>C™/SMB = I<sup>2</sup>C/SMBus input buffer, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: External memory interface I/O takes priority over all other digital and PSP I/O.

2: Available on 80-pin devices only.

# 11.9 PORTH, LATH and TRISH Registers

**Note:** PORTH is available only on 80-pin devices.

PORTH is an 8-bit wide, bidirectional I/O port. The corresponding Data Direction register is TRISH. Setting a TRISH bit (= 1) will make the corresponding PORTH pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISH bit (= 0) will make the corresponding PORTH pin an output (i.e., put the contents of the output latch on the selected pin). PORTH<3:0> pins are digital only and tolerate voltages up to 5.5V.

The Output Latch register (LATH) is also memory mapped. Read-modify-write operations on the LATH register read and write the latched output value for PORTH.

All pins on PORTH are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

When the external memory interface is enabled, four of the PORTH pins function as the high-order address lines for the interface. The address output from the interface takes priority over other digital I/O. The corresponding TRISH bits are also overridden.

PORTH pins, RH4 through RH7, are multiplexed with analog converter inputs. The operation of these pins as analog inputs is selected by clearing or setting the PCFG<3:0> control bits in the ADCON1 register.

PORTH can also be configured as the alternate Enhanced PWM output Channels B and C for the ECCP1 and ECCP3 modules. This is done by clearing the ECCPMX Configuration bit.

#### **EXAMPLE 11-8: INITIALIZING PORTH**

| CLRF  | PORTH  | ; Initialize PORTH by ; clearing output |

|-------|--------|-----------------------------------------|

|       |        | : data latches                          |

|       |        | , data fatthes                          |

| CLRF  | LATH   | ; Alternate method                      |

|       |        | ; to clear output                       |

|       |        | ; data latches                          |

| MOVLW | 0Fh    | ; Configure PORTH as                    |

| MOVWF | ADCON1 | ; digital I/O                           |

| MOVLW | 0CFh   | ; Value used to                         |

|       |        | ; initialize data                       |

|       |        | ; direction                             |

| MOVWF | TRISH  | ; Set RH3:RH0 as inputs                 |

|       |        | ; RH5:RH4 as outputs                    |

|       |        | ; RH7:RH6 as inputs                     |

|       |        |                                         |

### 12.0 TIMERO MODULE

The Timer0 module incorporates the following features:

- Software-selectable operation as a timer or counter in both 8-bit or 16-bit modes

- Readable and writable registers

- Dedicated 8-bit, software programmable prescaler

- Selectable clock source (internal or external)

- · Edge select for external clock

- · Interrupt-on-overflow

The T0CON register (Register 12-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 12-1. Figure 12-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

### REGISTER 12-1: TOCON: TIMERO CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N | T08BIT | T0CS  | T0SE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

| =       | THE ACT OF A CONTRACT OF A CON |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | TMR0ON: Timer0 On/Off Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | 1 = Enables Timer0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | 0 = Stops Timer0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 6   | T08BIT: Timer0 8-Bit/16-Bit Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | 1 = Timer0 is configured as an 8-bit timer/counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | 0 = Timer0 is configured as a 16-bit timer/counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 5   | T0CS: Timer0 Clock Source Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | 1 = Transition on T0CKI pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | 0 = Internal instruction cycle clock (CLKO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4   | T0SE: Timer0 Source Edge Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | 1 = Increment on high-to-low transition on T0CKI pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | 0 = Increment on low-to-high transition on T0CKI pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 3   | PSA: Timer0 Prescaler Assignment bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | 1 = Tlmer0 prescaler is NOT assigned. Timer0 clock input bypasses prescaler.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = Timer0 prescaler is assigned. Timer0 clock input comes from prescaler output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 2-0 | T0PS<2:0>: Timer0 Prescaler Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | 111 = 1:256 Prescale value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 110 = 1:128 Prescale value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 101 = 1:64 Prescale value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |