Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | EBI/EMI, FIFO, I <sup>2</sup> C, SCI, SSU                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 65                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/de70835rn80ftv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit   | Bit Name    | Initial<br>Value | R/W        | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------|-------------|------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2, 1  | _           | All 0            | R          | Reserved                                                                                                                                                                                                                                                                                                                                                                      |

|       |             |                  |            | These are read-only bits and cannot be modified.                                                                                                                                                                                                                                                                                                                              |

| 0     | ERR         | 0                | R/(W)*     | Transfer Stop Flag                                                                                                                                                                                                                                                                                                                                                            |

|       |             |                  |            | Indicates that the DTC address error or NMI interrupt<br>request has occurred. If a DTC address error or NMI<br>interrupt occurs while the DTC is active, address error<br>handling or NMI interrupt handling processing is executed<br>after the DTC has released the bus mastership. The DTC<br>stops in the transfer information writing state after<br>transferring data. |

|       |             |                  |            | 0: No interrupt occurs                                                                                                                                                                                                                                                                                                                                                        |

|       |             |                  |            | 1: An interrupt occurs                                                                                                                                                                                                                                                                                                                                                        |

|       |             |                  |            | [Clearing condition]                                                                                                                                                                                                                                                                                                                                                          |

|       |             |                  |            | When writing 0 after reading 1                                                                                                                                                                                                                                                                                                                                                |

| Note: | * Writing 0 | to this bit a    | after read | ing it as 1 clears the flag and is the only allowed way.                                                                                                                                                                                                                                                                                                                      |

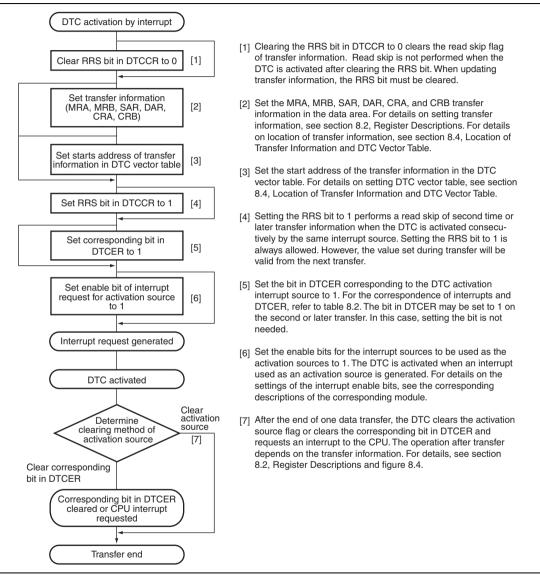

# 8.6 DTC Activation by Interrupt

The procedure for using the DTC with interrupt activation is shown in figure 8.18.

Figure 8.18 Activation of DTC by Interrupt

| Address                     | Area                       | Memory Type              | Capacity  | Bus<br>Width    |  |

|-----------------------------|----------------------------|--------------------------|-----------|-----------------|--|

| H'18000000 to               | CS6 space                  | Normal space             | 64 Mbytes | 8, 16, or       |  |

| H'1BFFFFF                   |                            | SRAM with byte selection |           | 32 bits*2       |  |

|                             |                            | PCMCIA                   |           |                 |  |

|                             |                            | Burst MPX-I/O            |           |                 |  |

| H'1C000000 to               | CS7 space                  | Normal space             | 64 Mbytes | 8, 16, or       |  |

| H'1FFFFFF                   |                            | SRAM with byte selection |           | 32 bits*2       |  |

| H'20000000 to<br>H'FFF7FFF  | Reserved                   |                          |           |                 |  |

| H'FFF80000 to<br>H'FFF9FFFF | SDRAM mode setting space   |                          |           |                 |  |

| H'FFFA0000 to<br>H'FFFF3FFF | Reserved                   |                          |           |                 |  |

| H'FFFF4000 to<br>H'FFFFBFFF | On-chip RAM                |                          | 32 Kbytes | 32 bits         |  |

| H'FFFFC000 to<br>H'FFFFFFF  | On-chip peripheral modules |                          | 16 Kbytes | 8 or 16<br>bits |  |

cannot be guaranteed.

1. The bus width is selected by the mode pins.

2. The bus width is selected by the register setting.

## Table 9.14 Address Map: SH7086 in On-Chip ROM-Enabled Mode

| Address                     | Area        | Memory Type                                                                                     | Capacity   | Bus<br>Width          |  |

|-----------------------------|-------------|-------------------------------------------------------------------------------------------------|------------|-----------------------|--|

| H'00000000 to<br>H'0007FFFF | On-chip ROM |                                                                                                 | 512 Kbytes | 32 bits               |  |

| H'00080000 to<br>H'01FFFFF  | Reserved    |                                                                                                 |            |                       |  |

| H'02000000 to<br>H'03FFFFFF | CS0 space   | Normal space<br>SRAM with byte selection<br>Burst ROM (asynchronous)<br>Burst ROM (synchronous) | 32 Mbytes  | 8, 16, or<br>32 bits* |  |

| H'04000000 to<br>H'07FFFFF  | CS1 space   | Normal space<br>SRAM with byte selection                                                        | 64 Mbytes  | 8, 16, or<br>32 bits* |  |

| Address                     | Area                     | Memory Type                                          | Capacity  | Bus<br>Width          |

|-----------------------------|--------------------------|------------------------------------------------------|-----------|-----------------------|

| H'08000000 to<br>H'0BFFFFF  | CS2 space                | Normal space<br>SRAM with byte selection             | 64 Mbytes | 8, 16, or<br>32 bits* |

|                             |                          | SDRAM                                                |           |                       |

| H'0C000000 to<br>H'0FFFFFF  | CS3 space                | Normal space                                         | 64 Mbytes | 8, 16, or<br>32 bits* |

|                             |                          | SRAM with byte selection SDRAM                       |           | 02 013                |

| H'10000000 to<br>H'13FFFFF  | CS4 space                | Normal space                                         | 64 Mbytes | 8, 16, or<br>32 bits* |

|                             |                          | SRAM with byte selection<br>Burst ROM (asynchronous) |           | 32 Dits*              |

| H'14000000 to               | CS5 space                | Normal space                                         | 64 Mbytes | 8, 16, or             |

| H'17FFFFFF                  |                          | SRAM with byte selection                             |           | 32 bits*              |

|                             |                          | PCMCIA<br>MPX-I/O                                    |           |                       |

| H'18000000 to<br>H'1BFFFFF  | CS6 space                | Normal space<br>SRAM with byte selection             | 64 Mbytes | 8, 16, or<br>32 bits* |

|                             |                          | PCMCIA                                               |           |                       |

|                             |                          | Burst MPX-I/O                                        |           |                       |

| H'1C000000 to               | CS7 space                | Normal space                                         | 64 Mbytes | 8, 16, or             |

| H'1FFFFFFF                  |                          | SRAM with byte selection                             |           | 32 bits*              |

| H'20000000 to<br>H'3FFFFFF  | Reserved                 |                                                      |           |                       |

| H'40000000 to<br>H'7FFFFFF  | CS8 space                | Normal space<br>SRAM with byte selection             | 1 Gbyte   | 8, 16, or<br>32 bits* |

| H'80000000 to<br>H'FFF7FFFF | Reserved                 |                                                      |           |                       |

| H'FFF80000 to<br>H'FFF9FFFF | SDRAM mode setting space |                                                      |           |                       |

| H'FFFA0000 to<br>H'FFFF3FFF | Reserved                 |                                                      |           |                       |

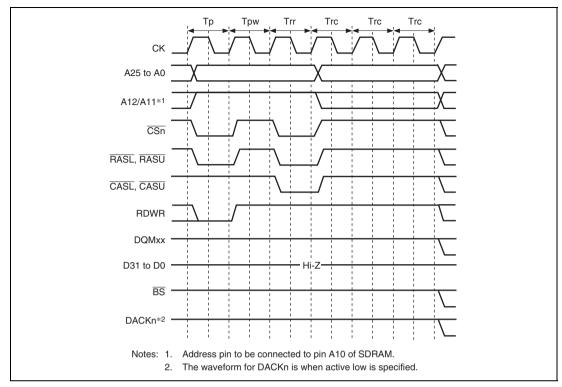

2. Self-refreshing

Self-refresh mode is a kind of standby mode in which the refresh timing and refresh addresses are generated within SDRAM. Self-refreshing is activated by setting both the RMODE bit and the RFSH bit in SDCR to 1. After starting the self-refreshing, PALL command is issued in the Tp cycle after the completion of the precharging bank. A SELF command is then issued after inserting idle cycles of which number is specified by the WTRP[1:0] bits in CS3WCR. SDRAM cannot be accessed while in the self-refresh state. Self-refresh mode is cleared by clearing the RMODE bit to 0. After self-refresh mode has been cleared, command issuance is disabled for the number of cycles specified by the WTRC[1:0] bits in CS3WCR.

Self-refresh timing is shown in figure 9.30. After self-refreshing is cleared, settings must be made so that auto-refreshing is performed at the correct intervals. When self-refreshing is activated from the state in which auto-refreshing is set, auto-refreshing is restarted if the RFSH bit is set to 1 and the RMODE bit is cleared to 0 when self-refresh mode is cleared. If the transition from clearing of self-refresh mode to the start of auto-refreshing takes time, making the RTCNT value 1 less than the RTCOR value will enable auto-refreshing to be started immediately.

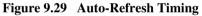

**Bus Mode and Channel Priority:** When the priority is set in fixed mode (CH0 > CH1) and channel 1 is transferring in burst mode, if there is a transfer request to channel 0 with a higher priority, the transfer of channel 0 will begin immediately.

At this time, if channel 0 is also operating in burst mode, the channel 1 transfer will continue after the channel 0 transfer has completely finished.

When channel 0 is in cycle steal mode, channel 0 with a higher priority performs the transfer of one transfer unit and the channel 1 transfer is continuously performed without releasing the bus mastership. The bus mastership will then switch between the two in the order channel 0, channel 1, channel 0, and channel 1. Therefore, the bus state is such that the CPU cycle after the completion of cycle steal mode transfer has been replaced with the channel 1 burst mode transfer. (Hereinafter referred to as burst mode priority execution.)

This example is shown in figure 10.13. When multiple channels are operating in burst modes, the channel with the highest priority is executed first.

When DMA transfer is executed in the multiple channels, the bus mastership will not be given to the bus master until all competing burst transfers are complete.

Figure 10.13 Bus State when Multiple Channels Are Operating

In round-robin mode, the priority changes according to the specification shown in figure 10.3. However, the channel in cycle steal mode cannot be mixed with the channel in burst mode.

#### 10.4.5 Number of Bus Cycle States and DREQ Pin Sampling Timing

**Number of Bus Cycle States:** When the DMAC is the bus master, the number of bus cycle states is controlled by the bus state controller (BSC) in the same way as when the CPU is the bus master. For details, see section 9, Bus State Controller (BSC).

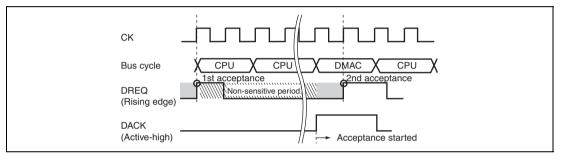

**DREQ Pin Sampling Timing:** Figures 10.14 to 10.17 show the sample timing of the DREQ input in each bus mode, respectively.

Determination of DMAC activation by DREQ takes  $3 \times Bcyc$  (Bcyc is the external clock (B $\phi$  = CK) cycle). Timing of the DACK output for the first DREQ acceptance differs depending on the internal bus state, the AM bit setting in CHCR, and the configuration of the BSC regarding the transfer source/destination areas, but the fastest case is  $6 \times Bcyc$ .

Figure 10.14 Example of DREQ Input Detection in Cycle Steal Mode Edge Detection

| Bit | Bit Name | Initial<br>Value | R/W     | Description                                                                                                                                                                                                                                                                                    |

|-----|----------|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CMFV5    | 0                | R/(W)*1 | Compare Match/Input Capture Flag V5                                                                                                                                                                                                                                                            |

|     |          |                  |         | Status flag that indicates the occurrence of TGRV_5 input capture or compare match.                                                                                                                                                                                                            |

|     |          |                  |         | [Setting conditions]                                                                                                                                                                                                                                                                           |

|     |          |                  |         | <ul> <li>When TCNTV_5 = TGRV_5 and TGRV_5 is<br/>functioning as output compare register</li> </ul>                                                                                                                                                                                             |

|     |          |                  |         | <ul> <li>When TCNTV_5 value is transferred to TGRV_5 by<br/>input capture signal and TGRV_5 is functioning as<br/>input capture register</li> </ul>                                                                                                                                            |

|     |          |                  |         | <ul> <li>When TCNTV_5 value is transferred to TGRV_5 and<br/>TGRV_5 is functioning as a register for measuring the<br/>pulse width of the external input signal. The transfer<br/>timing is specified by the IOC bits in timer I/O control<br/>register V_5 (TIORV_5).*<sup>2</sup></li> </ul> |

|     |          |                  |         | [Clearing conditions]                                                                                                                                                                                                                                                                          |

|     |          |                  |         | • When DTC is activated by a TGIV_5 interrupt and the DISEL bit of MRB in DTC is 0                                                                                                                                                                                                             |

|     |          |                  |         | • When 0 is written to CMFV5 after reading CMFV5 = 1                                                                                                                                                                                                                                           |

#### Table 11.57 MTU2 Interrupts

| Channel | Name   | Interrupt Source                   | Interrupt<br>Flag   | DMAC<br>Activation    | DTC<br>Activation | Priority |

|---------|--------|------------------------------------|---------------------|-----------------------|-------------------|----------|

| 0       | TGIA_0 | TGRA_0 input capture/compare match | TGFA_0              | Possible              | Possible          | High     |

|         | TGIB_0 | TGRB_0 input capture/compare match | TGFB_0              | Not possible          | Possible          | - ↑      |

|         | TGIC_0 | TGRC_0 input capture/compare match | TGFC_0              | Not possible          | Possible          | -        |

|         | TGID_0 | TGRD_0 input capture/compare match | TGFD_0              | Not possible Possible |                   | -        |

|         | TCIV_0 |                                    |                     | Not possible          | Not possible      | -        |

|         | TGIE_0 | TGRE_0 compare match               | match TGFE_0 Not po |                       | Not possible      | -        |

|         | TGIF_0 | TGRF_0 compare match               | TGFF_0              | Not possible          | Not possible      | -        |

| 1       | TGIA_1 | TGRA_1 input capture/compare match | TGFA_1              | Possible              | Possible          | -        |

|         | TGIB_1 | TGRB_1 input capture/compare match | TGFB_1              | Not possible          | Possible          | -        |

|         | TCIV_1 | TCNT_1 overflow                    | TCFV_1              | Not possible          | Not possible      | -        |

|         | TCIU_1 | TCNT_1 underflow                   | TCFU_1              | Not possible          | Not possible      | -        |

| 2       | TGIA_2 | TGRA_2 input capture/compare match | TGFA_2              | Possible              | Possible          | -        |

|         | TGIB_2 | TGRB_2 input capture/compare match | TGFB_2              | Not possible          | Possible          | -        |

|         | TCIV_2 | TCNT_2 overflow                    | TCFV_2              | Not possible          | Not possible      | -        |

|         | TCIU_2 | TCNT_2 underflow                   | TCFU_2              | Not possible          | Not possible      | -        |

| 3       | TGIA_3 | TGRA_3 input capture/compare match | TGFA_3              | Possible              | Possible          | -        |

|         | TGIB_3 | TGRB_3 input capture/compare match | TGFB_3              | Not possible          | Possible          | -        |

|         | TGIC_3 | TGRC_3 input capture/compare match | TGFC_3              | Not possible          | Possible          | -        |

|         | TGID_3 | TGRD_3 input capture/compare match | TGFD_3              | Not possible          | Possible          | -        |

| _       | TCIV_3 | TCNT_3 overflow                    | TCFV_3              | Not possible          | Not possible      |          |

| 4       | TGIA_4 | TGRA_4 input capture/compare match | TGFA_4              | Possible              | Possible          |          |

|         | TGIB_4 | TGRB_4 input capture/compare match | TGFB_4              | Not possible          | Possible          | -        |

|         | TGIC_4 | TGRC_4 input capture/compare match | TGFC_4              | Not possible          | Possible          | -        |

|         | TGID_4 | TGRD_4 input capture/compare match | TGFD_4              | Not possible          | Possible          | _        |

|         | TCIV_4 | TCNT_4 overflow/underflow          | TCFV_4              | Not possible          | Possible          | _        |

| 5       | TGIU_5 | TGRU_5 input capture/compare match | TGFU_5              | Not possible          | Possible          | _        |

|         | TGIV_5 | TGRV_5 input capture/compare match | TGFV_5              | Not possible          | Possible          | _ ↓      |

|         | TGIW_5 | TGRW_5 input capture/compare match | TGFW_5              | Not possible          | Possible          | Low      |

Note: This table shows the initial state immediately after a reset. The relative channel priorities can be changed by the interrupt controller.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|------|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4    | SOL      | 0                | R/W | Serial Data Output Value Select                                                                                                                                                                                                                                                                                                                                                                      |

|      |          |                  |     | The serial data output retains its level of the last bit<br>after completion of transmission. The output level<br>before or after transmission can be specified by setting<br>this bit. When specifying the output level, use the MOV<br>instruction after clearing the SOLP bit to 0. Since writing<br>to this bit during data transmission causes malfunctions,<br>this bit should not be changed. |

|      |          |                  |     | 0: Serial data output is changed to low.                                                                                                                                                                                                                                                                                                                                                             |

|      |          |                  |     | 1: Serial data output is changed to high.                                                                                                                                                                                                                                                                                                                                                            |

| 3    | SOLP     | 1                | R/W | SOL Bit Write Protect                                                                                                                                                                                                                                                                                                                                                                                |

|      |          |                  |     | When changing the output level of serial data, set the SOL bit to 1 or clear the SOL bit to 0 after clearing the SOLP bit to 0 using the MOV instruction.                                                                                                                                                                                                                                            |

|      |          |                  |     | 0: Output level can be changed by the SOL bit                                                                                                                                                                                                                                                                                                                                                        |

|      |          |                  |     | 1: Output level cannot be changed by the SOL bit. This bit is always read as 1.                                                                                                                                                                                                                                                                                                                      |

| 2    | _        | 1                | R   | Reserved                                                                                                                                                                                                                                                                                                                                                                                             |

|      |          |                  |     | This bit is always read as 1. The write value should always be 1.                                                                                                                                                                                                                                                                                                                                    |

| 1, 0 | CSS[1:0] | 01               | R/W | SCS Pin Select                                                                                                                                                                                                                                                                                                                                                                                       |

|      |          |                  |     | Select that the $\overline{\text{SCS}}$ pin functions as $\overline{\text{SCS}}$ input or output.                                                                                                                                                                                                                                                                                                    |

|      |          |                  |     | 00: Setting prohibited                                                                                                                                                                                                                                                                                                                                                                               |

|      |          |                  |     | 01: Setting prohibited                                                                                                                                                                                                                                                                                                                                                                               |

|      |          |                  |     | <ol> <li>Function as SCS automatic input/output (function as<br/>SCS input before and after transfer and output a<br/>low level during transfer)</li> </ol>                                                                                                                                                                                                                                          |

|      |          |                  |     | <ol> <li>Function as SCS automatic output (outputs a high<br/>level before and after transfer and outputs a low<br/>level during transfer)</li> </ol>                                                                                                                                                                                                                                                |

- Writing 1 to IICRST does not clear the BBSY bit in ICCR2 to 0. However, if the states of the SCL and SDA pins lead to the generation of a stop condition, (rising edge on SDA while SCL is at the high level), the BBSY bit may be cleared to 0 as a result. This can also affect other bits in the same way.

- Data transfer stops while a reset is being applied by writing 1 to IICRST. However, functions for detecting start conditions, stop conditions, and failure in bus contention continue to operate. Signals input to the SCL and SDA pins may alter the states of ICCR1, ICCR2, and ICSR.

## **18.3.3** I<sup>2</sup>C Bus Mode Register (ICMR)

ICMR is an 8-bit readable/writable register that selects whether the MSB or LSB is transferred first and selects the transfer bit count.

ICMR is initialized to H'38 by a power-on reset. Bits BC[2:0] are initialized to B'000 by the IICRST bit in ICCR2.

| Bit:           | 7   | 6 | 5 | 4 | 3    | 2   | 1       | 0   |

|----------------|-----|---|---|---|------|-----|---------|-----|

|                | MLS | - | - | - | BCWP |     | BC[2:0] |     |

| Initial value: | 0   | 0 | 1 | 1 | 1    | 0   | 0       | 0   |

| R/W:           | R/W | R | R | R | R/W  | R/W | R/W     | R/W |

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                          |

|------|----------|------------------|-----|----------------------------------------------------------------------|

| 7    | MLS      | 0                | R/W | MSB-First/LSB-First Select                                           |

|      |          |                  |     | 0: MSB-first                                                         |

|      |          |                  |     | 1: LSB-first                                                         |

|      |          |                  |     | Set this bit to 0 when the I <sup>2</sup> C bus format is used.      |

| 6    | _        | 0                | R   | Reserved                                                             |

|      |          |                  |     | This bit is always read as 0. The write value should always be 0.    |

| 5, 4 | _        | All 1            | R   | Reserved                                                             |

|      |          |                  |     | These bits are always read as 1. The write value should always be 1. |

## Table 21.14 SH7086 Multiplexed Pins (Port E)

| Port | Function 1<br>(Related Module) | Function 2<br>(Related Module)                           | Function 3<br>(Related Module) | Function 4<br>(Related Module)          | Function 5<br>(Related Module)        | Function 6<br>(Related Module) |

|------|--------------------------------|----------------------------------------------------------|--------------------------------|-----------------------------------------|---------------------------------------|--------------------------------|

| E    | PE0 I/O (port)                 | DREQ0 input<br>(DMAC)                                    | TIOC0A I/O (MTU2)              | AUDCK output<br>(AUD)* <sup>1</sup>     | _                                     | _                              |

|      | PE1 I/O (port)                 | TEND0 output<br>(DMAC)                                   | TIOC0B I/O (MTU2)              | _                                       | —                                     | _                              |

|      | PE2 I/O (port)                 | DREQ1 input<br>(DMAC)                                    | TIOC0C I/O (MTU2)              | _                                       | —                                     | _                              |

|      | PE3 I/O (port)                 | TEND1 output<br>(DMAC)                                   | TIOC0D I/O (MTU2)              | AUDATA3 output<br>(AUD)* <sup>1</sup>   | _                                     | _                              |

|      | PE4 I/O (port)                 | IOIS16 input (BSC)                                       | TIOC1A I/O (MTU2)              | RXD3 input (SCIF)                       | AUDATA2 output<br>(AUD)* <sup>1</sup> | _                              |

|      | PE5 I/O (port)                 | CS6/CE1B output<br>(BSC)                                 | TIOC1B I/O (MTU2)              | TXD3 output (SCIF)                      | AUDATA1 output<br>(AUD)* <sup>1</sup> | _                              |

|      | PE6 I/O (port)                 | CS7 output (BSC)                                         | TIOC2A I/O (MTU2)              | SCK3 I/O (SCIF)                         | AUDATA0 output<br>(AUD)* <sup>1</sup> | _                              |

|      | PE7 I/O (port)                 | BS output (BSC)                                          | TIOC2B I/O (MTU2)              | UBCTRG output<br>(UBC)                  | RXD2 input (SCI)                      | SSI I/O (SSU)                  |

|      | PE8 I/O (port)                 | TIOC3A I/O (MTU2)                                        | SCK2 I/O (SCI)                 | SSCK I/O (SSU)                          | TMS input (H-UDI)*2                   | _                              |

|      | PE9 I/O (port)                 | TIOC3B I/O (MTU2)                                        | SCK3 I/O (SCIF)                | RTS3 output (SCIF)                      | TRST input<br>(H-UDI)* <sup>2</sup>   | _                              |

|      | PE10 I/O (port)                | TIOC3C I/O (MTU2)                                        | TXD2 output (SCI)              | SSO I/O (SSU)                           | TDI input (H-UDI)*2                   | _                              |

|      | PE11 I/O (port)                | TIOC3D I/O (MTU2)                                        | RXD3 input (SCIF)              | CTS3 input (SCIF)                       | TDO output<br>(H-UDI)* <sup>2</sup>   | _                              |

|      | PE12 I/O (port)                | TIOC4A I/O (MTU2)                                        | TXD3 output (SCIF)             | SCS I/O (SSU)                           | TCK input (H-UDI)*2                   | _                              |

|      | PE13 I/O (port)                | TIOC4B I/O (MTU2)                                        | MRES input (INTC)              | ASEBRKAK output<br>(E10A)* <sup>2</sup> | ASEBRK input<br>(E10A)* <sup>2</sup>  | _                              |

|      | PE14 I/O (port)                | PE14 I/O (port) WRHH/ICIOWR/AH<br>/DQMUU output<br>(BSC) |                                | TIOC4C I/O (MTU2)                       | _                                     | _                              |

|      | PE15 I/O (port)                | CKE output (BSC)                                         | DACK1 output<br>(DMAC)         | TIOC4D I/O (MTU2)                       | IRQOUT output<br>(INTC)               | _                              |

|      | PE16 I/O (port)                | CS8 output (BSC)                                         | TIOC3BS I/O<br>(MTU2S)         | _                                       | _                                     | _                              |

|      | PE17 I/O (port)                | TIOC3DS I/O<br>(MTU2S)                                   | _                              | _                                       | _                                     | _                              |

## 22.2.3 Port B Port Register L (PBPRL)

The port B port register L (PBPRL) is a 16-bit read-only register that always returns the states of the pins regardless of the PFC setting. Bits PB9PR to PB4PR and PB2PR to PB0PR correspond to pins PB9 to PB4 and PB2 to PB0, respectively (multiplexed functions omitted here) in the SH7083. Bits PB9PR to PB0PR correspond to pins PB9 to PB0 (multiplexed functions omitted here) in the SH7084, SH7085, and SH7086

• PBPRL (SH7083)

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9         | 8         | 7         | 6         | 5         | 4         | 3 | 2         | 1         | 0         |

|----------------|----|----|----|----|----|----|-----------|-----------|-----------|-----------|-----------|-----------|---|-----------|-----------|-----------|

|                | -  | -  | -  | -  | -  | -  | PB9<br>PR | PB8<br>PR | PB7<br>PR | PB6<br>PR | PB5<br>PR | PB4<br>PR | - | PB2<br>PR | PB1<br>PR | PB0<br>PR |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | *         | *         | *         | *         | *         | *         | 0 | *         | *         | *         |

| R/W:           | R  | R  | R  | R  | R  | R  | R         | R         | R         | R         | R         | R         | R | R         | R         | R         |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                          |

|----------|----------|------------------|-----|----------------------------------------------------------------------|

| 15 to 10 | _        | All 0            | R   | Reserved                                                             |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0. |

| 9        | PB9PR    | Pin state        | R   | The pin state is returned regardless of the PFC setting.             |

| 8        | PB8PR    | Pin state        | R   | These bits cannot be modified.                                       |

| 7        | PB7PR    | Pin state        | R   | _                                                                    |

| 6        | PB6PR    | Pin state        | R   | _                                                                    |

| 5        | PB5PR    | Pin state        | R   | _                                                                    |

| 4        | PB4PR    | Pin state        | R   |                                                                      |

| 3        | _        | 0                | R   | Reserved                                                             |

|          |          |                  |     | This bit is always read as 0. The write value should always be 0.    |

| 2        | PB2PR    | Pin state        | R   | The pin state is returned regardless of the PFC setting.             |

| 1        | PB1PR    | Pin state        | R   | These bits cannot be modified.                                       |

| 0        | PB0PR    | Pin state        | R   |                                                                      |

# 23.4.4 RAM Emulation Register (RAMER)

When the realtime programming of the user MAT is emulated, RAMER sets the area of the user MAT which is overlapped with a part of the on-chip RAM. The RAM emulation must be executed in user mode or in user program mode.

For the division method of the user-MAT area, see table 23.7. In order to operate the emulation function certainly, the target MAT of the RAM emulation must not be accessed immediately after RAMER is programmed. If it is accessed, the normal access is not guaranteed.

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3    | 2   | 1       | 0   |

|----------------|----|----|----|----|----|----|---|---|---|---|---|---|------|-----|---------|-----|

| Γ              | -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | RAMS |     | RAM[2:0 | ]   |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0   | 0       | 0   |

| R/W:           | R  | R  | R  | R  | R  | R  | R | R | R | R | R | R | R/W  | R/W | R/W     | R/W |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                                                                                              |

|---------|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 4 | _        | All 0            | R   | Reserved                                                                                                                                 |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                     |

| 3       | RAMS     | 0                | R/W | RAM Select                                                                                                                               |

|         |          |                  |     | Sets whether the user MAT is emulated or not. When RAMS = 1, all blocks of the user MAT are in the programming/erasing protection state. |

|         |          |                  |     | <ol> <li>Emulation is not selected<br/>Programming/erasing protection of all user-MAT<br/>blocks is invalid</li> </ol>                   |

|         |          |                  |     | <ol> <li>Emulation is selected<br/>Programming/erasing protection of all user-MAT<br/>blocks is valid</li> </ol>                         |

| 2 to 0  | RAM[2:0] | 000              | R/W | User MAT Area Select                                                                                                                     |

|         |          |                  |     | These bits are used with bit 3 to select the user-MAT area to be overlapped with the on-chip RAM. (See table 23.7.)                      |

## Command Error

Command errors are generated by undefined commands, commands sent in an incorrect order, and the inability to accept a command. For example, sending the clock-mode selection command before device selection or an inquiry command after the transition-to-programming/erasure state command generates a command error.

| Error    |      |      |

|----------|------|------|

| response | H'80 | H'xx |

- Error response H'80 (1 byte): Command error

- Command H'xx (1 byte): Received command

- Order of Commands

In the inquiry-and-selection state, commands should be sent in the following order.

- 1. Send the inquiry on supported devices command (H'20) to get the list of supported devices.

- 2. Select a device from the returned device information, and send the device selection command (H'10) to select that device.

- 3. Send the inquiry on clock mode command (H'21) to get the available clock modes.

- 4. Select a clock mode from among the returned clock modes, and send the clock-mode selection command (H'11).

- 5. After selection of the device and clock mode, send the commands to inquire about frequency multipliers (H'22) and operating frequencies (H'23) to get the information required to select a new bit rate.

- 6. Taking into account the returned information on the frequency multipliers and operating frequencies, send a new-bit-rate selection command (H'3F).

- 7. After the device and clock mode have been selected, get the information required for programming and erasure of the user boot MAT and user MAT by sending the commands to inquire about the user boot MAT (H'24), user MAT (H'25), erasure block (H'26), and programming size (H'27).

- 8. After making all necessary inquiries and the new bit rate selection, send the transition-toprogramming/erasure state command (H'40) to place the boot program in the programming/erasure state.

#### 28.3.8 Watchdog Timer (WDT) Timing

## Table 28.13 Watchdog Timer (WDT) Timing

Conditions:  $V_{cc} = 3.0 \text{ V}$  to 3.6 V or 4.0 V to 5.5 V,  $AV_{cc} = 4.0 \text{ V}$  to 5.5 V,  $AV_{ref} = 4.0 \text{ V}$  to  $AV_{cc}$ ,  $V_{ss} = PLLV_{ss} = AV_{ss} = 0 \text{ V}$ ,  $T_a = -20^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (consumer applications),  $T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (industrial applications)

| Item              | Symbol            | Min. | Max. | Unit | Reference<br>Figure |

|-------------------|-------------------|------|------|------|---------------------|

| WDTOVF delay time | t <sub>wovd</sub> |      | 50   | ns   | Figure 28.50        |

|                   |                   |      |      |      |                     |

| ск                |                   |      |      |      |                     |

| WDTOVF            |                   |      |      |      |                     |

Figure 28.50 WDT Timing

#### [Legend]

- I: Input

- O: Output

- H: High-level output

- L: Low-level output

- Z: High-impedance

- K: Input pins become high-impedance, and output pins retain their state.

- Notes: 1. Output pins become high-impedance when the HIZ bit in standby control register 6 (STBCR6) is set to 1.

- 2. Becomes output when the HIZCNT bit in the common control register (CMNCR) is set to 1.

- 3. Becomes output when the HIZMEM bit in the common control register (CMNCR) is set to 1.

- 4. Becomes high-impedance when the MZIZDL bit in the high-current port control register (HCPCR) is cleared to 0.

- 5. Becomes high-impedance when the MZIZEL bit in the high-current port control register (HCPCR) is cleared to 0.

- 6. Becomes input during a power-on reset. Pull-up to prevent erroneous operation. Pull-down with a resistance of at least 1 M $\Omega$  as required.

- 7. Pulled-up inside the LSI when there is no input.

# Main Revisions for This Edition

| Item                                | Page | Revis                                                                                                                                                                                                                 | sion   | (Se  | e Ma          | nual for Deta                  | ils)                                                                           |                       |                   |                       |                        |

|-------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|---------------|--------------------------------|--------------------------------------------------------------------------------|-----------------------|-------------------|-----------------------|------------------------|

| Overall                             | _    | "l <sup>2</sup> C2"                                                                                                                                                                                                   | cha    | inge | d to "        | IIC2"                          |                                                                                |                       |                   |                       |                        |

| 3.1 Selection of<br>Operating Modes | 55   | Table amended                                                                                                                                                                                                         |        |      |               |                                |                                                                                |                       | Bue Wid           | th of CS0             | Snace                  |

|                                     |      | Mode No.                                                                                                                                                                                                              | FWE    | -    |               | Mode Name                      | On-Chip ROM                                                                    |                       | 85 SH7086         |                       |                        |

| Table 3.1 Selection of              |      | Mode 0                                                                                                                                                                                                                | 0      | 0    | 0             | MCU extension mode             |                                                                                | 8                     | 8                 | 16                    | 16                     |

| Operating Modes*1                   |      | Mode 1                                                                                                                                                                                                                | 0      | 0    | 1             | MCU extension mode             |                                                                                | 16                    | 16                | 32                    | 32                     |

|                                     |      | Mode 2                                                                                                                                                                                                                | 0      | 1    | 0             | MCU extension mode             |                                                                                | Set by                | CSOBC             | R in BS               | 2                      |

|                                     |      | Mode 3                                                                                                                                                                                                                | 0      | 1    | 1             | Single chip mode               | Active                                                                         | _                     |                   |                       |                        |

|                                     |      | Mode 4*2                                                                                                                                                                                                              | 1      | 0    | 0             | Boot mode                      | Active                                                                         | _                     |                   |                       |                        |

|                                     |      | Mode 5*2                                                                                                                                                                                                              | 1      | 0    | 1             | User boot mode                 | Active                                                                         | Set by                | CSOBC             | CR in BS              | 0                      |

|                                     |      | Mode 6*2                                                                                                                                                                                                              | 1      | 1    | 0             | User programming               | Active                                                                         | Set by                | CSOBC             | CR in BS              | 0                      |

|                                     |      | Mode 7*2                                                                                                                                                                                                              | 1      | 1    | 1             | mode                           |                                                                                | _                     |                   |                       |                        |

| 5.8.4 Notes on Slot                 | 103  | Family E10A-USB Emulator, Additional Document for User's Manual: Supplementary<br>Information on Using the SH7083, SH7084, SH7085, and SH7086.<br>2. These are flash memory programming modes.<br>Description deleted |        |      |               |                                |                                                                                |                       |                   |                       |                        |

| Illegal Instruction                 |      | 3. Others                                                                                                                                                                                                             |        |      |               |                                |                                                                                |                       |                   |                       |                        |

| Exception Handling                  |      | The slot illegal instruction exception handling may be<br>generated in this LSI in a case where the instruction is<br>described in assembler or when the middleware of the object<br>is introduced.                   |        |      |               |                                |                                                                                |                       |                   |                       | object                 |

| 8.2.2 DTC Mode                      | 176  | Table                                                                                                                                                                                                                 | am     | onde | bd            |                                |                                                                                |                       |                   |                       |                        |

|                                     | 170  | raple                                                                                                                                                                                                                 | am     |      |               |                                |                                                                                |                       |                   |                       |                        |

| Register B (MRB)                    |      | Bit B                                                                                                                                                                                                                 | it Nan |      | itial<br>alue | R/W Descriptio                 | n                                                                              |                       |                   |                       |                        |

|                                     |      | 5 D                                                                                                                                                                                                                   | ISEL   | Ur   | ndefined      | <ul> <li>DTC Interr</li> </ul> | upt Select                                                                     |                       |                   |                       |                        |

|                                     |      |                                                                                                                                                                                                                       |        |      |               | to the CPU<br>ends. Whe        | bit is set to 1,<br>I every time a<br>n this bit is se<br>ated when the<br>nd. | data tra<br>t to 0, a | nsfer o<br>CPU ir | r a block<br>nterrupt | transfer<br>request is |

|                                     |      |                                                                                                                                                                                                                       |        |      |               |                                | bit should be<br>cted as the ac                                                |                       |                   |                       | IC2 is                 |

| Item                                                                                                         | Page | Revisio             | on (See Manual for De                                    | tails)                                                                         |                        |                                                                              |  |  |  |

|--------------------------------------------------------------------------------------------------------------|------|---------------------|----------------------------------------------------------|--------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------|--|--|--|

| 15.5 Interrupt Sources                                                                                       | 801  | Table amended       |                                                          |                                                                                |                        |                                                                              |  |  |  |

| and DMAC/DTC                                                                                                 |      | Interrupt<br>Source | Description                                              | Interrupt<br>Enable Bit                                                        | DMAC/DTC<br>Activation | Priority                                                                     |  |  |  |

| Table 15.14 SCI<br>Interrupt Sources                                                                         |      | ERI                 | Interrupt caused by receive error<br>(ORER, FER, or PER) | RIE = 1                                                                        | Not possible           | High<br>♠                                                                    |  |  |  |

|                                                                                                              |      | RXI                 | Interrupt caused by receive data full (RDRF)             | RIE = 1 and $EIO = 0$                                                          | Possible               | -                                                                            |  |  |  |

|                                                                                                              |      | TXI                 | Interrupt caused by transmit data<br>empty (TDRE)        | TIE = 1                                                                        | Possible               |                                                                              |  |  |  |

|                                                                                                              |      | TEI                 | Interrupt caused by transmit end (TEND)                  | TEIE = 1                                                                       | Not possible           | Low                                                                          |  |  |  |

| 15.6 Serial Port Register<br>(SCSPTR) and SCI Pins<br>Figure 15.19 SPB1IO<br>Bit, SPB1DT bit, and SCK<br>Pin |      | SCK                 | and title amended                                        | Reset<br>Reset<br>SPB10<br>C<br>SPTRW<br>Reset<br>Reset<br>C<br>SPTRW<br>SPTRW | Serial close           | ut enable signal*<br>k output signal*<br>k input signal*<br>t enable signal* |  |  |  |

| Figure 15.20 SPB0IO<br>Bit, <u>SPB0DT</u> bit, and TXD<br>Pin                                                | 802  | TXD                 | and title amended                                        | Reset<br>R D<br>SPB0IO<br>C<br>SPTRW<br>Reset<br>R D<br>SPB0DT<br>C<br>SPTRW   | t 0 Transr             | al data bus<br>nit enable signal<br>transmit data                            |  |  |  |

| Item                                 | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18.4.5 Slave Receive                 | 950  | Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operation                            |      | The reception procedure and operations in slave receive<br>mode are described below. For operation up to reception of<br>the 1st frame (slave address + $R/\overline{W}$ ), see 18.4.4, Slave<br>Transmit Operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                      |      | <ol> <li>Perform a dummy read of ICDRR. (The read data<br/>indicates slave address + R/W, and is therefore<br/>unnecessary.) The slave device outputs to SDA the level<br/>indicated by the setting of ACKBT in ICIER at the 9th<br/>clock pulse of the receive clock.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                      |      | <ol> <li>After reception of one frame of data finishes, RDRF in<br/>ICSR is set to 1 at the rising edge of the 9th receive clock<br/>pulse. At this time, the received data can be read by<br/>reading ICDRR, and RDRF is cleared to 0<br/>simultaneously. Continuous receive operation can be<br/>accomplished by reading ICDRR each time RDRF is set<br/>to 1.<br/>If 8th receive clock pulse falls while RDRF is 1, SCL is<br/>fixed low until ICDRR is read.</li> <li>If the next receive operation is the final frame, set ACKBT<br/>in ICIER to 1 before reading ICDRR.</li> <li>When RDRF in ICSR is set to 1, read the final receive<br/>data from ICDRR.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 18.12 Slave                   |      | Figure amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Receive Mode Operation<br>Timing (1) |      | RDRF     ICDRS     ICDRA     < |

| Figure 18.13 Slave                   | 951  | Figure amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Receive Mode Operation               | 501  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Timing (2)                           |      | (Slave output)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                      |      | RDRF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |