#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | EBI/EMI, FIFO, I <sup>2</sup> C, SCI, SSU                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 100                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LFQFP (20x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/de70855rn80fpv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.2 Input/Output Pins

Table 4.2 shows the CPG pin configuration.

# Table 4.2Pin Configuration

| Pin Name                                                                                          | Abbr. | I/O    | Description                                        |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------|-------|--------|----------------------------------------------------|--|--|--|--|--|

| Crystal input/output                                                                              | XTAL  | Output | Connects a crystal resonator.                      |  |  |  |  |  |

| pins<br>(clock input pins)                                                                        | EXTAL | Input  | Connects a crystal resonator or an external clock. |  |  |  |  |  |

| Clock output pin                                                                                  | CK    | Output | Outputs an external clock.                         |  |  |  |  |  |

| Note: To use the clock output (CK) pin, appropriate settings may be needed for the pin in the pin |       |        |                                                    |  |  |  |  |  |

function controller (PFC) in some cases. For details, refer to section 21, Pin Function Controller (PFC).

| Address                     | Area                       | Memory Type | Capacity  | Bus<br>Width    |

|-----------------------------|----------------------------|-------------|-----------|-----------------|

| H'FFF80000 to<br>H'FFF9FFFF | SDRAM mode setting space   |             |           |                 |

| H'FFFA0000 to<br>H'FFFF7FFF | Reserved                   |             |           |                 |

| H'FFFF8000 to<br>H'FFFFBFFF | On-chip RAM                |             | 16 Kbytes | 32 bits         |

| H'FFFFC000 to<br>H'FFFFFFF  | On-chip peripheral modules |             | 16 Kbytes | 8 or 16<br>bits |

Notes: Do not access the reserved area. If the reserved area is accessed, the correct operation cannot be guaranteed. In single-chip mode, only the on-chip ROM, on-chip RAM, and on-chip peripheral modules can be accessed; the other areas cannot be accessed.

\* The bus width is selected by the register setting.

#### Table 9.11 Address Map: SH7085 (256-Kbyte Flash Memory Version) in On-Chip ROM-Disabled Mode

| Address       | Area      | Memory Type              | Capacity  | Bus<br>Width          |

|---------------|-----------|--------------------------|-----------|-----------------------|

| H'00000000 to | CS0 space | Normal space             | 64 Mbytes | 16 or 32              |

| H'03FFFFFF    |           | SRAM with byte selection |           | bits*1                |

|               |           | Burst ROM (asynchronous) |           |                       |

|               |           | Burst ROM (synchronous)  |           |                       |

| H'0400000 to  | CS1 space | Normal space             | 64 Mbytes | 8, 16, or             |

| H'07FFFFFF    |           | SRAM with byte selection |           | 32 bits* <sup>2</sup> |

| H'0800000 to  | CS2 space | Normal space             | 64 Mbytes | 8, 16, or             |

| H'0BFFFFFF    |           | SRAM with byte selection |           | 32 bits* <sup>2</sup> |

|               |           | SDRAM                    |           |                       |

| H'0C000000 to | CS3 space | Normal space             | 64 Mbytes | 8, 16, or             |

| H'0FFFFFF     |           | SRAM with byte selection |           | 32 bits*2             |

|               |           | SDRAM                    |           |                       |

| H'10000000 to | CS4 space | Normal space             | 64 Mbytes | 8, 16, or             |

| H'13FFFFFF    |           | SRAM with byte selection |           | 32 bits* <sup>2</sup> |

|               |           | Burst ROM (asynchronous) |           |                       |

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5    | DMAIWA   | 0                | R/W | Specification for Method of Inserting Wait States<br>between Access Cycles during DMA Single Address<br>Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |          |                  |     | Specifies the method of inserting the idle cycles<br>specified by the DMAIW1 and DMAIW0 bits. Clearing<br>this bit will make this LSI insert the idle cycles when<br>another device, which includes this LSI, drives the data<br>bus after an external device with DACK drove it. When<br>the external device with DACK drives the data bus<br>continuously, idle cycles are not inserted. Setting this bit<br>will make this LSI insert the idle cycles after one access<br>is completed even when the continuous accesses to an<br>external device with DACK are performed. |

|      |          |                  |     | <ol> <li>Idle cycles are inserted when another device drives<br/>data bus after external device with DACK drives data<br/>bus</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |          |                  |     | <ol> <li>Idle cycles are always inserted after external device<br/>with DACK is accessed.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4    | _        | 1                | R   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |          |                  |     | This bit is always read as 1. The write value should always be 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3, 2 | _        | All 0            | R   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1    | HIZMEM   | 0                | R/W | Hi-Z Memory Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |          |                  |     | Specifies the pin state in software standby mode for<br>A29 to A0, BS, CSn, RDWR, WRxx, RD, AH, FRAME,<br>ICIORD, ICIOWR, WE, CE1A, CE1B, CE2A, and<br>CE2B. While the bus is released, these pins are in high-<br>impedance state regardless of this bit setting.                                                                                                                                                                                                                                                                                                            |

|      |          |                  |     | 0: High impedance in software standby mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |          |                  |     | 1: Driven in software standby mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                              |

|---------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 to 7 | WR[3:0]  | 1010             | R/W | Number of Read Access Wait Cycles                                                                                                                        |

|         |          |                  |     | Specify the number of wait cycles required for read access.                                                                                              |

|         |          |                  |     | 0000: 0 cycles                                                                                                                                           |

|         |          |                  |     | 0001: 1 cycle                                                                                                                                            |

|         |          |                  |     | 0010: 2 cycles                                                                                                                                           |

|         |          |                  |     | 0011: 3 cycles                                                                                                                                           |

|         |          |                  |     | 0100: 4 cycles                                                                                                                                           |

|         |          |                  |     | 0101: 5 cycles                                                                                                                                           |

|         |          |                  |     | 0110: 6 cycles                                                                                                                                           |

|         |          |                  |     | 0111: 8 cycles                                                                                                                                           |

|         |          |                  |     | 1000: 10 cycles                                                                                                                                          |

|         |          |                  |     | 1001: 12 cycles                                                                                                                                          |

|         |          |                  |     | 1010: 14 cycles                                                                                                                                          |

|         |          |                  |     | 1011: 18 cycles                                                                                                                                          |

|         |          |                  |     | 1100: 24 cycles                                                                                                                                          |

|         |          |                  |     | 1101: Reserved (setting prohibited)                                                                                                                      |

|         |          |                  |     | 1110: Reserved (setting prohibited)                                                                                                                      |

|         |          |                  |     | 1111: Reserved (setting prohibited)                                                                                                                      |

| 6       | WM       | 0                | R/W | External Wait Mask Specification                                                                                                                         |

|         |          |                  |     | Specifies whether or not the external wait input is valid.<br>The specification by this bit is valid even when the<br>number of access wait cycles is 0. |

|         |          |                  |     | 0: External wait input is valid                                                                                                                          |

|         |          |                  |     | 1: External wait input is ignored                                                                                                                        |

| 5 to 2  |          | All 0            | R   | Reserved                                                                                                                                                 |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                     |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                              |

|---------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 to 7 | WR[3:0]  | 1010             | R/W | Number of Wait Cycles in Read Access                                                                                                                     |

|         |          |                  |     | Specify the number of wait cycles required for read access.                                                                                              |

|         |          |                  |     | 0000: 0 cycles                                                                                                                                           |

|         |          |                  |     | 0001: 1 cycle                                                                                                                                            |

|         |          |                  |     | 0010: 2 cycles                                                                                                                                           |

|         |          |                  |     | 0011: 3 cycles                                                                                                                                           |

|         |          |                  |     | 0100: 4 cycles                                                                                                                                           |

|         |          |                  |     | 0101: 5 cycles                                                                                                                                           |

|         |          |                  |     | 0110: 6 cycles                                                                                                                                           |

|         |          |                  |     | 0111: 8 cycles                                                                                                                                           |

|         |          |                  |     | 1000: 10 cycles                                                                                                                                          |

|         |          |                  |     | 1001: 12 cycles                                                                                                                                          |

|         |          |                  |     | 1010: 14 cycles                                                                                                                                          |

|         |          |                  |     | 1011: 18 cycles                                                                                                                                          |

|         |          |                  |     | 1100: 24 cycles                                                                                                                                          |

|         |          |                  |     | 1101: Reserved (setting prohibited)                                                                                                                      |

|         |          |                  |     | 1110: Reserved (setting prohibited)                                                                                                                      |

|         |          |                  |     | 1111: Reserved (setting prohibited)                                                                                                                      |

| 6       | WM       | 0                | R/W | External Wait Mask Specification                                                                                                                         |

|         |          |                  |     | Specifies whether or not the external wait input is valid.<br>The specification by this bit is valid even when the<br>number of access wait cycles is 0. |

|         |          |                  |     | 0: External wait is valid                                                                                                                                |

|         |          |                  |     | 1: External wait is ignored                                                                                                                              |

| 5 to 2  |          | All 0            | R   | Reserved                                                                                                                                                 |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                     |

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                           |

|------|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 0 | HW[1:0]  | 00               | R/W | Delay Cycles from $\overline{\text{RD}}$ and $\overline{\text{WRxx}}$ Negation to Address and $\overline{\text{CSn}}$ Negation                        |

|      |          |                  |     | Specify the number of delay cycles from $\overline{\text{RD}}$ and $\overline{\text{WRxx}}$ negation to address and $\overline{\text{CSn}}$ negation. |

|      |          |                  |     | 00: 0.5 cycle                                                                                                                                         |

|      |          |                  |     | 01: 1.5 cycles                                                                                                                                        |

|      |          |                  |     | 10: 2.5 cycles                                                                                                                                        |

|      |          |                  |     | 11: 3.5 cycles                                                                                                                                        |

### (4) SDRAM

When SDRAM is selected in areas 2 and 3, the WTRP1/0, WTRCD0/1, TRWL1/0, and WTRC1/0 bit settings are effective in both areas in common. When SDRAM should be connected to only one area, select area 3 for SDRAM connection. In this case, the normal space or SRAM with byte selection must be selected for area 2.

#### CS2WCR

| Bit:           | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24  | 23     | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----------------|----|----|----|----|----|----|----|-----|--------|----|----|----|----|----|----|----|

|                | -  | -  | -  | -  | -  | -  | -  | -   | -      | -  | -  | -  | -  | -  | -  | -  |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R   | R      | R  | R  | R  | R  | R  | R  | R  |

|                |    |    |    |    |    |    |    |     |        |    |    |    |    |    |    |    |

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7      | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|                | -  | -  | -  | -  | -  | -  | -  | A2C | L[1:0] | -  | -  | -  | -  | -  | -  | -  |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1   | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R/W | R/W    | R  | R  | R  | R  | R  | R  | R  |

|          |          | Initial |     |                                                                      |

|----------|----------|---------|-----|----------------------------------------------------------------------|

| Bit      | Bit Name | Value   | R/W | Description                                                          |

| 31 to 11 | _        | All 0   | R   | Reserved                                                             |

|          |          |         |     | These bits are always read as 0. The write value should always be 0. |

| 10       | _        | 1       | R   | Reserved                                                             |

|          |          |         |     | This bit is always read as 1. The write value should always be 1.    |

| Bit  | Bit Name  | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|-----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8, 7 | A3CL[1:0] | 10               | R/W | CAS Latency for Area 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |           |                  |     | Specify the CAS latency for area 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |           |                  |     | 00: 1 cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |           |                  |     | 01: 2 cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |           |                  |     | 10: 3 cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |           |                  |     | 11: 4 cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6, 5 | _         | All 0            | R   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |           |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4, 3 | TRWL[1:0] | 00               | R/W | Number of Wait Cycles for Precharge Activation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |           |                  |     | Specify the minimum number of wait cycles to be inserted for activation of precharge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |           |                  |     | <ul> <li>From issuance of WRITA command by this LSI until auto precharge is activated in SDRAM:<br/>ACTV command is issued for the same bank in non-bank active mode.<br/>See the datasheet of the SDRAM to find the number of cycles taken from the acceptance of WRITA command by SDRAM until auto-precharge is activated. These bits should be set so that the above number of cycles will not exceed the number of cycles specified by these bits.</li> <li>From issuance of WRIT command by this LSI until issuance of PRE command:<br/>Different row addresses in the same bank are accessed in bank active mode.</li> <li>The setting for areas 2 and 3 is common.</li> <li>00: 0 cycle (No wait cycles)</li> <li>01: 1 cycle</li> </ul> |

|      |           |                  |     | 10: 2 cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |           |                  |     | 11: 3 cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2    |           | 0                | R   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |           | -                |     | This bit is always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |          | Initial |     |                                                                                                                                                          |

|---------|----------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Bit Name | Value   | R/W | Description                                                                                                                                              |

| 10 to 7 | PCW[3:0] | 1010    | R/W | Number of Access Wait Cycles                                                                                                                             |

|         |          |         |     | Specify the number of wait cycles to be inserted.                                                                                                        |

|         |          |         |     | 0000: 3 cycles                                                                                                                                           |

|         |          |         |     | 0001: 6 cycles                                                                                                                                           |

|         |          |         |     | 0010: 9 cycles                                                                                                                                           |

|         |          |         |     | 0011: 12 cycles                                                                                                                                          |

|         |          |         |     | 0100: 15 cycles                                                                                                                                          |

|         |          |         |     | 0101: 18 cycles                                                                                                                                          |

|         |          |         |     | 0110: 22 cycles                                                                                                                                          |

|         |          |         |     | 0111: 26 cycles                                                                                                                                          |

|         |          |         |     | 1000: 30 cycles                                                                                                                                          |

|         |          |         |     | 1001: 33 cycles                                                                                                                                          |

|         |          |         |     | 1010: 36 cycles                                                                                                                                          |

|         |          |         |     | 1011: 38 cycles                                                                                                                                          |

|         |          |         |     | 1100: 52 cycles                                                                                                                                          |

|         |          |         |     | 1101: 60 cycles                                                                                                                                          |

|         |          |         |     | 1110: 64 cycles                                                                                                                                          |

|         |          |         |     | 1111: 80 cycles                                                                                                                                          |

| 6       | WM       | 0       | R/W | External Wait Mask Specification                                                                                                                         |

|         |          |         |     | Specifies whether or not the external wait input is valid.<br>The specification by this bit is valid even when the<br>number of access wait cycles is 0. |

|         |          |         |     | 0: External wait input is valid                                                                                                                          |

|         |          |         |     | 1: External wait input is ignored                                                                                                                        |

| 5, 4    |          | All 0   | R   | Reserved                                                                                                                                                 |

|         |          |         |     | These bits are always read as 0. The write value should always be 0.                                                                                     |

|         |          |         |     |                                                                                                                                                          |

# Table 11.26 TIORH\_4 (Channel 4)

|               |               |               |               | Description        |                                |  |

|---------------|---------------|---------------|---------------|--------------------|--------------------------------|--|

| Bit 3<br>IOA3 | Bit 2<br>IOA2 | Bit 1<br>IOA1 | Bit 0<br>IOA0 | TGRA_4<br>Function | TIOC4A Pin Function            |  |

| 0             | 0             | 0             | 0             | Output             | Output retained*               |  |

|               |               |               | 1             | compare register   | Initial output is 0            |  |

|               |               |               |               | register           | 0 output at compare match      |  |

|               |               | 1             | 0             |                    | Initial output is 0            |  |

|               |               |               |               |                    | 1 output at compare match      |  |

| 1             |               |               | 1             | -                  | Initial output is 0            |  |

|               |               |               |               |                    | Toggle output at compare match |  |

|               | 1             | 0             | 0             |                    | Output retained                |  |

|               |               |               | 1             |                    | Initial output is 1            |  |

|               |               |               |               |                    | 0 output at compare match      |  |

|               |               | 1             | 0             |                    | Initial output is 1            |  |

|               |               |               |               |                    | 1 output at compare match      |  |

|               |               |               | 1             |                    | Initial output is 1            |  |

|               |               |               |               |                    | Toggle output at compare match |  |

| 1             | Х             | 0             | 0             |                    | Input capture at rising edge   |  |

|               |               |               | 1             | register           | Input capture at falling edge  |  |

|               |               | 1             | х             | _                  | Input capture at both edges    |  |

| Leaen         | 41            |               |               |                    |                                |  |

[Legend]

Don't care x:

Note: \* After power-on reset, 0 is output until TIOR is set. 2. Free-Running Count Operation and Periodic Count Operation:

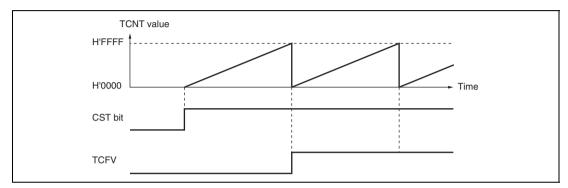

Immediately after a reset, the MTU2's TCNT counters are all designated as free-running counters. When the relevant bit in TSTR is set to 1 the corresponding TCNT counter starts upcount operation as a free-running counter. When TCNT overflows (from H'FFFF to H'0000), the TCFV bit in TSR is set to 1. If the value of the corresponding TCIEV bit in TIER is 1 at this point, the MTU2 requests an interrupt. After overflow, TCNT starts counting up again from H'0000.

Figure 11.5 illustrates free-running counter operation.

When compare match is selected as the TCNT clearing source, the TCNT counter for the relevant channel performs periodic count operation. The TGR register for setting the period is designated as an output compare register, and counter clearing by compare match is selected by means of bits CCLR[2:0] in TCR. After the settings have been made, TCNT starts up-count operation as a periodic counter when the corresponding bit in TSTR is set to 1. When the count value matches the value in TGR, the TGF bit in TSR is set to 1 and TCNT is cleared to H'0000.

If the value of the corresponding TGIE bit in TIER is 1 at this point, the MTU2 requests an interrupt. After a compare match, TCNT starts counting up again from H'0000.

| <b>D</b> !4 | Dit Norre | Initial | <b>D</b> /44 | Description                                                                                                                                                                                                                                      |

|-------------|-----------|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit         | Bit Name  | value   | R/W          | Description                                                                                                                                                                                                                                      |

| 7           | C/A       | 0       | R/W          | Communication Mode                                                                                                                                                                                                                               |

|             |           |         |              | Selects whether the SCIF operates in asynchronous or<br>clock synchronous mode.                                                                                                                                                                  |

|             |           |         |              | 0: Asynchronous mode                                                                                                                                                                                                                             |

|             |           |         |              | 1: Clock synchronous mode                                                                                                                                                                                                                        |

| 6           | CHR       | 0       | R/W          | Character Length                                                                                                                                                                                                                                 |

|             |           |         |              | Selects 7-bit or 8-bit data in asynchronous mode. In the clock synchronous mode, the data length is always eight bits, regardless of the CHR setting.                                                                                            |

|             |           |         |              | 0: 8-bit data                                                                                                                                                                                                                                    |

|             |           |         |              | 1: 7-bit data*                                                                                                                                                                                                                                   |

|             |           |         |              | Note: * When 7-bit data is selected, the MSB (bit 7) of<br>the transmit FIFO data register is not<br>transmitted.                                                                                                                                |

| 5           | PE        | 0       | R/W          | Parity Enable                                                                                                                                                                                                                                    |

|             |           |         |              | Selects whether to add a parity bit to transmit data and<br>to check the parity of receive data, in asynchronous<br>mode. In clock synchronous mode, a parity bit is neither<br>added nor checked, regardless of the PE setting.                 |

|             |           |         |              | 0: Parity bit not added or checked                                                                                                                                                                                                               |

|             |           |         |              | 1: Parity bit added and checked*                                                                                                                                                                                                                 |

|             |           |         |              | Note: * When PE is set to 1, an even or odd parity bit<br>is added to transmit data, depending on the<br>parity mode $(O/\overline{E})$ setting. Receive data parity<br>is checked according to the even/odd $(O/\overline{E})$<br>mode setting. |

| Bit | Bit Name | Initial<br>Value | R/W     | Description                                                                                                                                                                                                                                 |

|-----|----------|------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | STOP     | 0                | R/(W)*1 | Stop Condition Detection Flag                                                                                                                                                                                                               |

|     |          |                  |         | [Clearing condition]                                                                                                                                                                                                                        |

|     |          |                  |         | • When 0 is written to STOP after reading STOP = 1<br>[Setting conditions]                                                                                                                                                                  |

|     |          |                  |         | In master mode, when a stop condition is detected     after frame transfer                                                                                                                                                                  |

|     |          |                  |         | <ul> <li>In slave mode, when a stop condition is detected<br/>after the slave address in the first byte that came<br/>following the detection of a start condition have<br/>matched the address set in SAR.</li> </ul>                      |

| 2   | AL/OVE   | 0                | R/W     | Arbitration Lost Flag/Overrun Error Flag                                                                                                                                                                                                    |

|     |          |                  |         | This flag indicates that arbitration was lost in master mode with the $l^2C$ bus format and that the final bit has been received while RDRF = 1 with the clock synchronous format.                                                          |

|     |          |                  |         | When two or more master devices attempt to seize the bus at nearly the same time, if the $l^2C$ bus interface 2 detects data differing from the data it sent, it sets AL to 1 to indicate that the bus has been occupied by another master. |

|     |          |                  |         | [Clearing condition]                                                                                                                                                                                                                        |

|     |          |                  |         | <ul> <li>When 0 is written to AL/OVE after reading AL/OVE</li> <li>= 1</li> </ul>                                                                                                                                                           |

|     |          |                  |         | [Setting conditions]                                                                                                                                                                                                                        |

|     |          |                  |         | • If the internal SDA and SDA pin disagree at the rise of SCL in master transmit mode                                                                                                                                                       |

|     |          |                  |         | When the SDA pin outputs high in master mode     while a start condition is detected                                                                                                                                                        |

|     |          |                  |         | <ul> <li>When the final bit is received with the clock<br/>synchronous format while RDRF = 1</li> </ul>                                                                                                                                     |

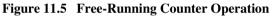

- [1] Write 0 to the ICE bit in ICCR1 to halt functioning of the IIC2.

- [2] Write 1 to the IICRST bit in ICCR2 to reset some registers and the contol part of the IIC2 module.

- [3] Write 0 to the MST and TRS bits in ICCR1 to switch the operating mode to slave receiver mode.

- [4] Write 1 to the FS bit in SAR to clear the BBSY flag in ICCR2 to 0.

- [5] Write 0 to the FS bit in the SAR to select  $I^2C$  bus format.

- [6] Clear the flags in ICSR to 0.

- [7] Write 0 to the IICRST bit to release the IIC2 module from the reset state.

- [8] Initialize IIC2 registers (ICCR1, ICCR2, ICMR, ICIER, and NF2CYC). Clear the ICE, MST, and TRS bits in the ICCR1 to 0.

- [9] Specify the slave address in the SVA[6:0] bit field in the SAR. Clear ACKBT in the ICIER to 0.

- [10] Set external pin PFC for use. Set PFC while SCL and SDA are high-level.

- [11] Write 1 to the ICE bit in the ICCR1 to enable transfer operation.

- Note: For the procedure for initializing IIC2 when communication is in progress, see 18.4.8, Using the IICRST Bit to Reset I<sup>2</sup>C Bus Interface 2.

Figure 18.7 Flowchart of Initialization of I<sup>2</sup>C Bus Interface 2

# Section 21 Pin Function Controller (PFC)

The pin function controller (PFC) is composed of registers that are used to select the functions of multiplexed pins and assign pins to be inputs or outputs. Tables 21.1 to 21.16 list the multiplexed pins of this LSI.

Tables 21.17 to 21.20 list the pin functions in each operating mode.

| Port | Function 1<br>(Related Module) | Function 2<br>(Related Module) | Function 3<br>(Related Module) | Function 4<br>(Related Module) | Function 5<br>(Related Module) |

|------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| А    | PA3 I/O (port)                 | A24 output (BSC)               | RXD1 input (SCI)               | _                              | _                              |

|      | PA4 I/O (port)                 | A23 output (BSC)               | TXD1 output (SCI)              | _                              | _                              |

|      | PA5 I/O (port)                 | A22 output (BSC)               | DREQ1 input (DMAC)             | IRQ1 input (INTC)              | SCK1 I/O (SCI)                 |

|      | PA7 I/O (port)                 | CS3 output (BSC)               | TCLKB input (MTU2)             | _                              | _                              |

|      | PA8 I/O (port)                 | RDWR output (BSC)              | IRQ2 input (INTC)              | TCLKC input (MTU2)             | _                              |

|      | PA9 I/O (port)                 | CKE output (BSC)               | IRQ3 input (INTC)              | TCLKD input (MTU2)             | _                              |

|      | PA10 I/O (port)                | CS0 output (BSC)               | POE4 input (POE)               | —                              | _                              |

|      | PA12 I/O (port)                | WRL/DQMLL output<br>(BSC)      | POE6 input (POE)               |                                | _                              |

|      | PA13 I/O (port)                | WRH/DQMLU output<br>(BSC)      | POE7 input (POE)               | _                              | _                              |

|      | PA14 I/O (port)                | RD output (BSC)                | _                              | _                              | _                              |

|      | PA15 I/O (port)                | CK output (CPG)                | _                              |                                | —                              |

#### Table 21.1 SH7083 Multiplexed Pins (Port A)

### Table 21.2 SH7084 Multiplexed Pins (Port A)

| Port | Function 1<br>(Related Module) | Function 2<br>(Related Module) | Function 3<br>(Related Module) | Function 4<br>(Related Module) | Function 5<br>(Related Module) |

|------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| А    | PA0 I/O (port)                 | CS4 output (BSC)               | RXD0 input (SCI)               | _                              | _                              |

|      | PA1 I/O (port)                 | CS5 output (BSC)               | TXD0 output (SCI)              | —                              | —                              |

|      | PA2 I/O (port)                 | A25 output (BSC)               | DREQ0 input (DMAC)             | IRQ0 input (INTC)              | SCK0 I/O (SCI)                 |

|      | PA3 I/O (port)                 | A24 output (BSC)               | RXD1 input (SCI)               | —                              | _                              |

|      | PA4 I/O (port)                 | A23 output (BSC)               | TXD1 output (SCI)              | —                              | —                              |

|      | PA5 I/O (port)                 | A22 output (BSC)               | DREQ1 input (DMAC)             | IRQ1 input (INTC)              | SCK1 I/O (SCI)                 |

|      | PA6 I/O (port)                 | CS2 output (BSC)               | TCLKA input (MTU2)             | —                              | _                              |

|      | PA7 I/O (port)                 | CS3 output (BSC)               | TCLKB input (MTU2)             | —                              | —                              |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                       |

|-----|----------|------------------|-----|-------------------------------------------------------------------|

| 14  | PA3MD2   | 0                | R/W | PA3 Mode                                                          |

| 13  | PA3MD1   | 0                | R/W | Select the function of the PA3/A24/RXD1 pin.                      |

| 12  | PA3MD0   | 0                | R/W | 000: PA3 I/O (port)                                               |

|     |          |                  |     | 001: RXD1 input (SCI)                                             |

|     |          |                  |     | 101: A24 output (BSC)*                                            |

|     |          |                  |     | Other than above: Setting prohibited                              |

| 11  | _        | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| 10  | PA2MD2   | 0                | R/W | PA2 Mode                                                          |

| 9   | PA2MD1   | 0                | R/W | Select the function of the                                        |

| 8   | PA2MD0   | 0                | R/W | PA2/A25/DREQ0/IRQ0/SCK0 pin.                                      |

|     |          |                  |     | 000: PA2 I/O (port)                                               |

|     |          |                  |     | 001: SCK0 I/O (SCI)                                               |

|     |          |                  |     | 010: DREQ0 input (DMAC)                                           |

|     |          |                  |     | 011: IRQ0 input (INTC)                                            |

|     |          |                  |     | 101: A25 output (BSC)*                                            |

|     |          |                  |     | Other than above: Setting prohibited                              |

| 7   |          | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| 6   | PA1MD2   | 0                | R/W | PA1 Mode                                                          |

| 5   | PA1MD1   | 0                | R/W | Select the function of the PA1/CS5/CE1A/TXD0 pin.                 |

| 4   | PA1MD0   | 0                | R/W | 000: PA1 I/O (port)                                               |

|     |          |                  |     | 001: TXD0 output (SCI)                                            |

|     |          |                  |     | 101: CS5/CE1A output (BSC)*                                       |

|     |          |                  |     | Other than above: Setting prohibited                              |

| 3   | _        | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

# (6) Inquiry on operating frequency

In response to the inquiry on operating frequency, the boot program returns the number of operating frequencies and the maximum and minimum values.

Command

H'23

- Command H'23 (1 byte): Inquiry on operating frequency

Response

| H'33 Size       |       | No. of operating clocks |

|-----------------|-------|-------------------------|

| Operating freq. | (min) | Operating freq. (max)   |

|                 |       |                         |

| SUM             |       |                         |

- Response H'33 (1 byte): Response to the inquiry on operating frequency

- Size (1 byte): The total length of the number of operating clocks, and maximum and minimum values of operating frequency fields.

- Number of operating clocks (1 byte): The number of operating clock frequencies required within the device.

For example, the value two indicates main and peripheral operating clock frequencies.

Minimum value of operating frequency (2 bytes): The minimum frequency of a frequencymultiplied or -divided clock signal.

The value in this field and in the maximum value field is the frequency in MHz to two decimal places, multiplied by 100 (for example, if the frequency is 20.00 MHz, the value multiplied by 100 is 2000, so H'07D0 is returned here).

Maximum value of operating frequency (2 bytes): The maximum frequency of a frequencymultiplied or -divided clock signal.

As many pairs of minimum/maximum values are included as there are operating clocks.

— SUM (1 byte): Checksum

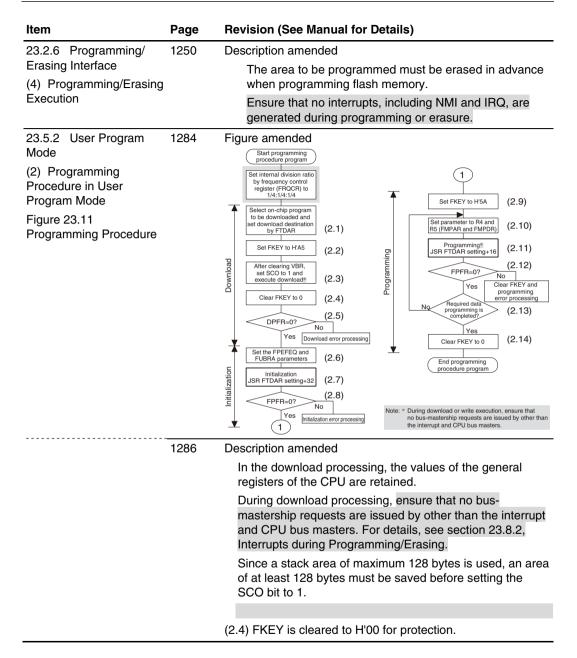

| Item                                                                                                                            | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.4.9 A/D Converter                                                                                                            | 604  | Description and note added                                                                                                                                                                                                                                                                                                         |

| Start Request Delaying<br>Function<br>(e) A/D Converter Start<br>Request Delaying<br>Function Linked with<br>Interrupt Skipping |      | In complementary PWM mode, A/D converter start requests (TRG4AN and TRG4BN) can be issued in coordination with interrupt skipping by making settings in the ITA3AE, ITA4VE, ITB3AE, and ITB4VE bits in the timer A/D converter start request control register (TADCR).                                                             |

|                                                                                                                                 |      | The A/D converter start request delaying function linked to<br>the interrupt skipping function cannot be used when not in<br>complementary PWM mode. In this case, clear the ITA3AE,<br>ITA4VE, ITB3AE, and ITB4VE bits in TADCR to 0.                                                                                             |

|                                                                                                                                 |      | Note: This function must be used in combination with<br>interrupt skipping.                                                                                                                                                                                                                                                        |

|                                                                                                                                 |      |                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                 |      | Furthermore, when this function is to be used, set TADCORA_4 and TADCORB_4 to a value between H'0002 and the TCDR setting minus two.                                                                                                                                                                                               |

| 11.4.10 MTU2-MTU2S                                                                                                              | 607  | Figure amended                                                                                                                                                                                                                                                                                                                     |

| Synchronous Operation                                                                                                           |      | (1) Use TSTR registers in the MTU2 and MTU2S and halt the counters used for synchronous start operation.                                                                                                                                                                                                                           |

| (1) MTU2–MTU2S                                                                                                                  |      | counter start [2] Specify necessary operation with appropriate registers such as                                                                                                                                                                                                                                                   |

| Synchronous Counter<br>Start                                                                                                    |      | TCR and TMDR.  Stop count operation [1] [3] In TCSYSTR in the MTU2, set the bits corresponding to the                                                                                                                                                                                                                              |