Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | EBI/EMI, FIFO, I <sup>2</sup> C, SCI, SSU                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 65                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df70835ad80ftv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 16.23 Receive Data Sampling Timing in Asynchronous Mode                      |

|-------------------------------------------------------------------------------------|

| Section 17 Synchronous Serial Communication Unit (SSU)                              |

| Figure 17.1 Block Diagram of SSU                                                    |

| Figure 17.2 Relationship of Clock Phase, Polarity, and Data                         |

| Figure 17.3 Relationship between Data Input/Output Pins and the Shift Register      |

| Figure 17.4 Example of Initial Settings in SSU Mode                                 |

| Figure 17.5 Example of Transmission Operation (SSU Mode)                            |

| Figure 17.6 Flowchart Example of Data Transmission (SSU Mode)                       |

| Figure 17.7 Example of Reception Operation (SSU Mode)                               |

| Figure 17.8 Flowchart Example of Data Reception (SSU Mode)                          |

| Figure 17.9 Flowchart Example of Simultaneous Transmission/Reception (SSU Mode)     |

| Figure 17.10 Conflict Error Detection Timing (Before Transfer)                      |

| Figure 17.11 Conflict Error Detection Timing (After Transfer End)                   |

| Figure 17.12 Example of Initial Settings in Clock Synchronous Communication Mode911 |

| Figure 17.13 Example of Transmission Operation                                      |

| (Clock Synchronous Communication Mode)                                              |

| Figure 17.14 Flowchart Example of Transmission Operation                            |

| (Clock Synchronous Communication Mode)                                              |

| Figure 17.15 Example of Reception Operation                                         |

| (Clock Synchronous Communication Mode)                                              |

| Figure 17.16 Flowchart Example of Data Reception                                    |

| (Clock Synchronous Communication Mode)                                              |

| Figure 17.17 Flowchart Example of Simultaneous Transmission/Reception               |

| (Clock Synchronous Communication Mode)                                              |

| Section 18 I <sup>2</sup> C Bus Interface 2 (IIC2)                                  |

| Figure 18.1 Block Diagram of I <sup>2</sup> C Bus Interface 2                       |

| Figure 18.2 External Circuit Connections of I/O Pins                                |

| Figure 18.3 I <sup>2</sup> C Bus Formats                                            |

| Figure 18.4 I <sup>2</sup> C Bus Timing                                             |

| Figure 18.5 Master Transmit Mode Operation Timing (1)                               |

| Figure 18.6 Master Transmit Mode Operation Timing (2)                               |

| Figure 18.7 Flowchart of Initialization of I <sup>2</sup> C Bus Interface 2         |

| Figure 18.8 Master Receive Mode Operation Timing (1)                                |

| Figure 18.9 Master Receive Mode Operation Timing (2)                                |

| Figure 18.10 Slave Transmit Mode Operation Timing (1)                               |

| Figure 18.11 Slave Transmit Mode Operation Timing (2)                               |

| Figure 18.12 Slave Receive Mode Operation Timing (1)                                |

| Figure 18.13 Slave Receive Mode Operation Timing (2)                                |

## 2.2.3 System Registers

There are four 32-bit system registers, designated two multiply and accumulate registers (MACH and MACL), a procedure register (PR), and program counter (PC).

• Multiply and accumulate registers (MACH and MACL)

This register stores the results of multiplication and multiply-and-accumulate operation.

- Procedure register (PR) This register stores the return-destination address from subroutine procedures.

- Program counter (PC)

The PC indicates the point which is four bytes (two instructions) after the current execution instruction.

## 2.2.4 Initial Values of Registers

Table 2.1 lists the initial values of registers after a reset.

| Type of register | Register       | Default                                             |

|------------------|----------------|-----------------------------------------------------|

| General register | R0 to R14      | Undefined                                           |

|                  | R15 (SP)       | SP value set in the exception handling vector table |

| Control register | SR             | I3 to I0: 1111 (H'F)                                |

|                  |                | Reserved bits: 0                                    |

|                  |                | Other bits: Undefined                               |

|                  | GBR            | Undefined                                           |

|                  | VBR            | H'0000000                                           |

| System register  | MACH, MACL, PR | Undefined                                           |

|                  | PC             | PC value set in the exception handling vector table |

## Table 2.1 Initial Values of Registers

Written Back Value

| Register | Function               | CRAL is not 1                  | CRAL is 1                                   |  |  |  |  |  |

|----------|------------------------|--------------------------------|---------------------------------------------|--|--|--|--|--|

| SAR      | Source address         | Incremented/decremented/fixed* | DTS = 0: Incremented/<br>decremented/fixed* |  |  |  |  |  |

|          |                        |                                | DTS = 1: SAR initial value                  |  |  |  |  |  |

| DAR      | Destination address    | Incremented/decremented/fixed* | DTS = 0: DAR initial value                  |  |  |  |  |  |

|          |                        |                                | DTS = 1: Incremented/<br>decremented/fixed* |  |  |  |  |  |

| CRAH     | Transfer count storage | CRAH                           | CRAH                                        |  |  |  |  |  |

| CRAL     | Transfer count A       | CRAL – 1                       | CRAH                                        |  |  |  |  |  |

| CRB      | Transfer count B       | Not updated                    | Not updated                                 |  |  |  |  |  |

| Note: *  | Transfer information   | writeback is skinned           |                                             |  |  |  |  |  |

## Table 8.7 Register Function in Repeat Transfer Mode

Note: \* Transfer information writeback is skipped.

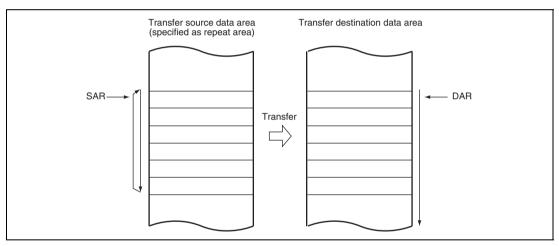

Figure 8.7 Memory Map in Repeat Transfer Mode (When Transfer Source Is Specified as Repeat Area)

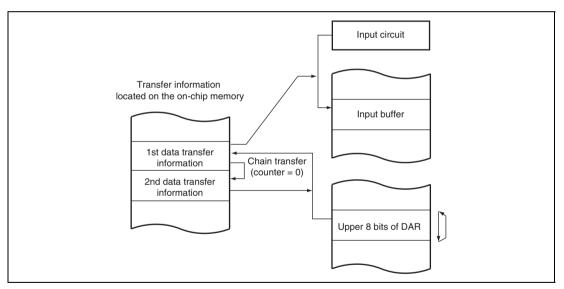

- 3. For the second transfer, set repeat transfer mode (with the source side as the repeat area) for resetting the transfer destination address for the first data transfer. Use the upper eight bits of DAR in the first transfer information area as the transfer destination. Set CHNE = DISEL = 0. If the above input buffer is specified as H'200000 to H'21FFFF, set the transfer counter to 2.

- 4. Execute the first data transfer 65536 times by means of interrupts. When the transfer counter for the first data transfer reaches 0, the second data transfer is started. Set the upper eight bits of the transfer destination address for the first data transfer to H'21. The lower 16 bits of the transfer destination address of the first data transfer and the transfer counter are H'0000.

- 5. Next, execute the first data transfer the 65536 times specified for the first data transfer by means of interrupts. When the transfer counter for the first data transfer reaches 0, the second data transfer is started. Set the upper eight bits of the transfer destination address for the first data transfer to H'20. The lower 16 bits of the transfer destination address of the first data transfer and the transfer counter are H'0000.

- 6. Steps 4 and 5 are repeated endlessly. As repeat mode is specified for the second data transfer, no interrupt request is sent to the CPU.

Figure 8.19 Chain Transfer when Counter = 0

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                              |

|--------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6      | WM       | 0                | R/W | External Wait Mask Specification                                                                                                                         |

|        |          |                  |     | Specifies whether or not the external wait input is valid.<br>The specification by this bit is valid even when the<br>number of access wait cycles is 0. |

|        |          |                  |     | 0: External wait is valid                                                                                                                                |

|        |          |                  |     | 1: External wait is ignored                                                                                                                              |

| 5 to 0 |          | All 0            | R   | Reserved                                                                                                                                                 |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                     |

## (7) Burst ROM (Clock Synchronous)

• CS0WCR

| Bit:           | 31 | 30 | 29 | 28 | 27 | 26  | 25  | 24   | 23  | 22  | 21 | 20 | 19 | 18 | 17  | 16    |

|----------------|----|----|----|----|----|-----|-----|------|-----|-----|----|----|----|----|-----|-------|

|                | -  | -  | -  | -  | -  | -   | -   | -    | -   | -   | -  | -  | -  | -  | BW  | [1:0] |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0    | 0   | 0   | 0  | 0  | 0  | 0  | 0   | 0     |

| R/W:           | R  | R  | R  | R  | R  | R   | R   | R    | R   | R   | R  | R  | R  | R  | R/W | R/W   |

|                |    |    |    |    |    |     |     |      |     |     |    |    |    |    |     |       |

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10  | 9   | 8    | 7   | 6   | 5  | 4  | 3  | 2  | 1   | 0     |

|                | -  | -  | -  | -  | -  |     | W[3 | 3:0] |     | WM  | -  | -  | -  | -  | -   | -     |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 1   | 0   | 1    | 0   | 0   | 0  | 0  | 0  | 0  | 0   | 0     |

| R/W:           | R  | R  | R  | R  | R  | R/W | R/W | R/W  | R/W | R/W | R  | R  | R  | R  | R   | R     |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                                                                 |

|----------|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------|

| 31 to 18 | _        | All 0            | R   | Reserved                                                                                                    |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                        |

| 17, 16   | BW[1:0]  | 00               | R/W | Number of Burst Wait Cycles                                                                                 |

|          |          |                  |     | Specify the number of wait cycles to be inserted in the second or subsequent access cycles in burst access. |

|          |          |                  |     | 00: 0 cycles                                                                                                |

|          |          |                  |     | 01: 1 cycle                                                                                                 |

|          |          |                  |     | 10: 2 cycles                                                                                                |

|          |          |                  |     | 11: 3 cycles                                                                                                |

# Table 9.23Relationship between BSZ[1:0], A2ROW[1:0]/A3ROW[1:0],<br/>A2COL[1:0]/A3COL[1:0], and Address Multiplex Output (4)-1

|                           | Setting                   |                           |                |                                |

|---------------------------|---------------------------|---------------------------|----------------|--------------------------------|

| BSZ[1:0]                  | A2ROW[1:0]/<br>A3ROW[1:0] | A2COL[1:0]/<br>A3COL[1:0] | _              |                                |

| 10 (16 bits)              | 00 (11 bits)              | 00 (8 bits)               | _              |                                |

| Output Pin of<br>This LSI |                           |                           | -<br>SDRAM Pin | Function                       |

| A17                       | A25                       | A17                       |                | Unused                         |

| A16                       | A24                       | A16                       | —              |                                |

| A15                       | A23                       | A15                       |                |                                |

| A14                       | A22                       | A14                       |                |                                |

| A13                       | A21* <sup>2</sup>         | A21* <sup>2</sup>         | A12 (BA1)      | Specifies bank                 |

| A12                       | A20* <sup>2</sup>         | A20* <sup>2</sup>         | A11 (BA0)      |                                |

| A11                       | A19                       | L/H* <sup>1</sup>         | A10/AP         | Specifies<br>address/precharge |

| A10                       | A18                       | A10                       | A9             | Address                        |

| A9                        | A17                       | A9                        | A8             |                                |

| A8                        | A16                       | A8                        | A7             |                                |

| A7                        | A15                       | A7                        | A6             |                                |

| A6                        | A14                       | A6                        | A5             |                                |

| A5                        | A13                       | A5                        | A4             |                                |

| A4                        | A12                       | A4                        | A3             |                                |

| A3                        | A11                       | A3                        | A2             |                                |

| A2                        | A10                       | A2                        | A1             |                                |

| A1                        | A9                        | A1                        | A0             |                                |

| A0                        | A8                        | A0                        |                | Unused                         |

| Example of con            | nected memory             |                           |                |                                |

16-Mbit product (512 kwords  $\times$  16 bits  $\times$  2 banks, column 8 bits product): 1

Notes: 1. L/H is a bit used in the command specification; it is fixed at L or H according to the access mode.

2. Bank address specification

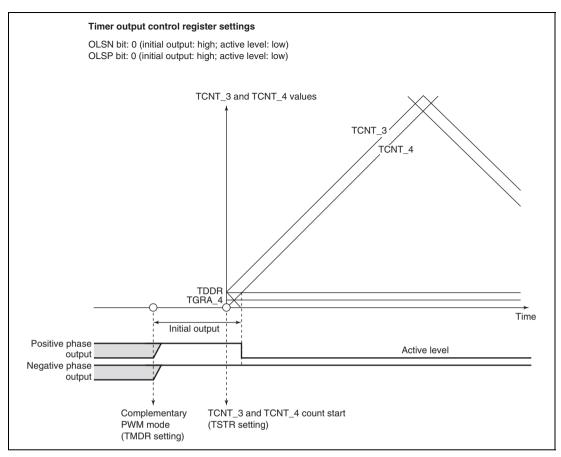

Figure 11.45 Example of Initial Output in Complementary PWM Mode (2)

## (b) Examples of Synchronous Counter Start Operation

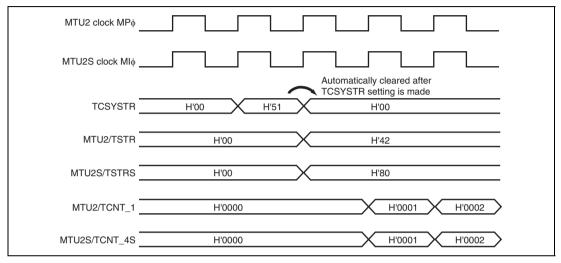

Figures 11.84 (1), 11.84 (2), 11.84 (3), and 11.84 (4) show examples of synchronous counter start operation when the clock frequency ratio between the MTU2 and MTU2S is 1:1, 1:2, 1:3, and 1:4, respectively.

In these examples, the count clock settings are MP\$/1 (MTU2) and MI\$/1 (MTU2S).

Figure 11.84 (1) Example of Synchronous Counter Start Operation (MTU2-to-MTU2S Clock Frequency Ratio = 1:1)

## (4) Timing for Counter Clearing by Compare Match/Input Capture

Figures 11.100 and 11.101 show the timing when counter clearing on compare match is specified, and figure 11.102 shows the timing when counter clearing on input capture is specified.

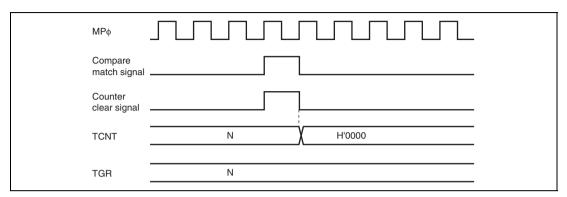

#### Figure 11.100 Counter Clear Timing (Compare Match) (Channels 0 to 4)

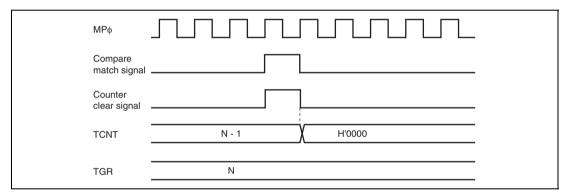

Figure 11.101 Counter Clear Timing (Compare Match) (Channel 5)

## (3) TCFV Flag/TCFU Flag Setting Timing

Figure 11.113 shows the timing for setting of the TCFV flag in TSR on overflow, and TCIV interrupt request signal timing.

Figure 11.114 shows the timing for setting of the TCFU flag in TSR on underflow, and TCIU interrupt request signal timing.

| ΜΡφ, Ρφ             |               |

|---------------------|---------------|

| TCNT input<br>clock |               |

| TCNT<br>(overflow)  | H'FFFF H'0000 |

| Overflow<br>signal  |               |

| TCFV flag           |               |

| TCIV interrupt      |               |

Figure 11.113 TCIV Interrupt Setting Timing

| ΜΡφ, Ρφ             |               |  |

|---------------------|---------------|--|

| TCNT<br>input clock |               |  |

| TCNT<br>(underflow) | H'0000 H'FFFF |  |

| Underflow<br>signal |               |  |

| TCFU flag           |               |  |

| TCIU interrupt      |               |  |

Figure 11.114 TCIU Interrupt Setting Timing

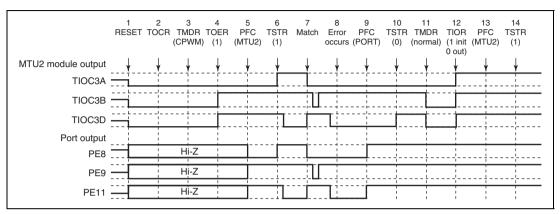

**Operation when Error Occurs during Complementary PWM Mode Operation, and Operation is Restarted in Normal Mode:** Figure 11.161 shows an explanatory diagram of the case where an error occurs in complementary PWM mode and operation is restarted in normal mode after re-setting.

- 1. After a reset, MTU2 output is low and ports are in the high-impedance state.

- 2. Select the complementary PWM output level and cyclic output enabling/disabling with TOCR.

- 3. Set complementary PWM.

- 4. Enable channel 3 and 4 output with TOER.

- 5. Set MTU2 output with the PFC.

- 6. The count operation is started by TSTR.

- 7. The complementary PWM waveform is output on compare-match occurrence.

- 8. An error occurs.

- 9. Set port output with the PFC and output the inverse of the active level.

- 10. The count operation is stopped by TSTR. (MTU2 output becomes the complementary PWM output initial value.)

- 11. Set normal mode. (MTU2 output goes low.)

- 12. Initialize the pins with TIOR.

- 13. Set MTU2 output with the PFC.

- 14. Operation is restarted by TSTR.

## 15.3.7 Serial Status Register (SCSSR)

SCSSR is an 8-bit register that contains status flags to indicate the SCI operating state.

The CPU can always read and write to SCSSR, but cannot write 1 to status flags TDRE, RDRF, ORER, PER, and FER. These flags can be cleared to 0 only after 1 is read from the flags. The TEND flag is a read-only bit and cannot be modified.

| Bit:           | 7      | 6      | 5      | 4      | 3      | 2    | 1   | 0    |

|----------------|--------|--------|--------|--------|--------|------|-----|------|

|                | TDRE   | RDRF   | ORER   | FER    | PER    | TEND | MPB | MPBT |

| Initial value: | 1      | 0      | 0      | 0      | 0      | 1    | 0   | 0    |

| R/W:           | R/(W)* | R/(W)* | R/(W)* | R/(W)* | R/(W)* | R    | R   | R/W  |

Note: \* Writing 0 to this bit after reading it as 1 clears the flag and is the only allowed way.

|     |          | Initial |        |                                                                                                                                                                                                                                                                                                                      |

|-----|----------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | value   | R/W    | Description                                                                                                                                                                                                                                                                                                          |

| 7   | TDRE     | 1       | R/(W)* | Transmit Data Register Empty                                                                                                                                                                                                                                                                                         |

|     |          |         |        | Indicates whether data has been transferred from the transmit data register (SCTDR) to the transmit shift register (SCTSR) and SCTDR has become ready to be written with next serial transmit data.                                                                                                                  |

|     |          |         |        | 0: Indicates that SCTDR holds valid transmit data                                                                                                                                                                                                                                                                    |

|     |          |         |        | [Clearing conditions]                                                                                                                                                                                                                                                                                                |

|     |          |         |        | • When 0 is written to TDRE after reading TDRE = 1                                                                                                                                                                                                                                                                   |

|     |          |         |        | <ul> <li>When the DMAC is activated by a TXI interrupt<br/>and transmit data is written to SCTDR</li> </ul>                                                                                                                                                                                                          |

|     |          |         |        | <ul> <li>When the DTC is activated by a TXI interrupt and transmit data is transferred to SCTDR while the DISEL bit of MRB in the DTC is 0 (except when the transfer counter value of the DTC is H'0000)</li> <li>1: Indicates that SCTDR does not hold valid transmit data</li> <li>[Setting conditions]</li> </ul> |

|     |          |         |        | <ul> <li>By a power-on reset or in standby mode</li> </ul>                                                                                                                                                                                                                                                           |

|     |          |         |        | When the TE bit in SCSCR is 0                                                                                                                                                                                                                                                                                        |

|     |          |         |        | <ul> <li>When data is transferred from SCTDR to SCTSR<br/>and data can be written to SCTDR</li> </ul>                                                                                                                                                                                                                |

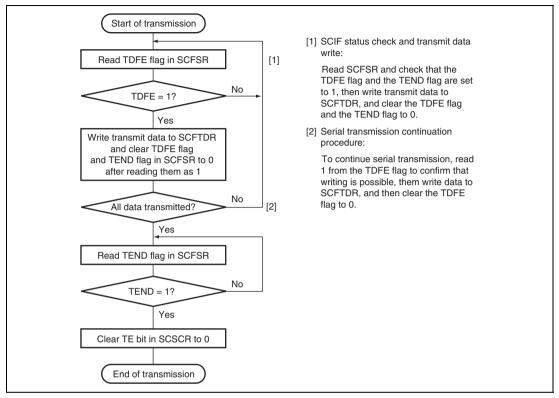

## Transmitting Serial Data (Clock Synchronous Mode): Figure 16.13 shows a sample flowchart

for transmitting serial data.

Figure 16.13 Sample Flowchart for Transmitting Serial Data

|      |          | Initial         |     |                                                                      |

|------|----------|-----------------|-----|----------------------------------------------------------------------|

| Bit  | Bit Name | Value           | R/W | Description                                                          |

| 5    | PD29MD1  | 0               | R/W | PD29 Mode                                                            |

| 4    | PD29MD0  | 0*1             | R/W | Select the function of the PD29/D29/CS3/TIOC3BS pin.                 |

|      |          |                 |     | 00: PD29 I/O (port)                                                  |

|      |          |                 |     | 01: D29 I/O (BSC)* <sup>2</sup>                                      |

|      |          |                 |     | 10: $\overline{CS3}$ output (BSC)* <sup>2</sup>                      |

|      |          |                 |     | 11: TIOC3BS I/O (MTU2S)                                              |

| 3, 2 | _        | All 0           | R   | Reserved                                                             |

|      |          |                 |     | These bits are always read as 0. The write value should always be 0. |

| 1    | PD28MD1  | 0               | R/W | PD28 Mode                                                            |

| 0    | PD28MD0  | 0* <sup>1</sup> | R/W | Select the function of the PD28/D28/CS2/TIOC3DS pin.                 |

|      |          |                 |     | 00: PD28 I/O (port)                                                  |

|      |          |                 |     | 01: D28 I/O (BSC)* <sup>2</sup>                                      |

|      |          |                 |     | 10: $\overline{CS2}$ output (BSC)* <sup>2</sup>                      |

|      |          |                 |     | 11: TIOC3DS I/O (MTU2S)                                              |

Notes: 1. The initial value is 1 in the on-chip ROM disabled 32-bit external-extension mode.

2. This function is enabled only in the on-chip ROM enabled/disabled external-extension mode. Do not set 1 in single-chip mode.

## • Port D Control Register H3 (PDCRH3)

| Bit:           | 15 | 14 | 13          | 12          | 11 | 10 | 9           | 8           | 7 | 6 | 5           | 4           | 3 | 2 | 1           | 0           |

|----------------|----|----|-------------|-------------|----|----|-------------|-------------|---|---|-------------|-------------|---|---|-------------|-------------|

|                | -  | -  | PD27<br>MD1 | PD27<br>MD0 | -  | -  | PD26<br>MD1 | PD26<br>MD0 | - | - | PD25<br>MD1 | PD25<br>MD0 | - | - | PD24<br>MD1 | PD24<br>MD0 |

| Initial value: | 0  | 0  | 0           | 0*          | 0  | 0  | 0           | 0*          | 0 | 0 | 0           | 0*          | 0 | 0 | 0           | 0*          |

| R/W:           | R  | R  | R/W         | R/W         | R  | R  | R/W         | R/W         | R | R | R/W         | R/W         | R | R | R/W         | R/W         |

Note: \* The initial value is 1 in the on-chip ROM disabled 32-bit external-extension mode.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                          |

|--------|----------|------------------|-----|----------------------------------------------------------------------|

| 15, 14 |          | All 0            | R   | Reserved                                                             |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0. |

## 21.2 Usage Notes

- 1. In this LSI, the same function is available as a multiplexed function on multiple pins. This approach is intended to increase the number of selectable pin functions and to allow the easier design of boards. If two or more pins are specified for one function, however, there are two cautions shown below.

- When the pin function is input

Signals input to several pins are formed as one signal through OR or AND logic and the signal is transmitted into the LSI. Therefore, a signal that differs from the input signals may be transmitted to the LSI depending on the input signals in other pins that have the same functions. Table 21.22 shows the transmit forms of input functions allocated to several pins. When using one of the functions shown below in multiple pins, use it with care of signal polarity considering the transmit forms.

## Table 21.22 Transmit Forms of Input Functions Allocated to Multiple Pins

| ОК Туре                                                                                                           | AND Type                                                       |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| SCK0, SCK3, RXD0, RXD3,<br>TIOC3AS to TIOC3DS, TIOC4AS to TIOC4DS,<br>TIC5U, TIC5V, TIC5W, TIC5US, TIC5VS, TIC5WS | IRQ0 to IRQ7, DREQ0, DREQ1, BREQ,<br>WAIT, ADTRG, POE4 to POE8 |

- OR type: Signals input to several pins are formed as one signal through OR logic and the signal is transmitted into the LSI.

- AND type: Signals input to several pins are formed as one signal through AND logic and the signal is transmitted into the LSI.

- When the pin function is output

Each selected pin can output the same function.

- 2. When the port input is switched from a low level to the DREQ or the IRQ edge for the pins that are multiplexed with input/output and DREQ or IRQ, the corresponding edge is detected.

- 3. Do not set functions other than those specified in tables 21.17 to 21.20. Otherwise, correct operation cannot be guaranteed.

- 4. PFC setting in single-chip mode (MCU operating mode 3)

In single-chip mode, do not set the PFC to select address bus, data bus, bus control, or the  $\overline{BREQ}$ ,  $\overline{BACK}$ , CK, DACK, or TEND signals. If they are selected, address bus signals function as high- or low-level outputs, data bus signals function as high-impedance outputs, and the other output signals function as high-level outputs. As  $\overline{BREQ}$  and  $\overline{WAIT}$  function as inputs, do not leave them open. However, the bus-mastership-request inputs and external waits are disabled.

## 22.6.1 Register Descriptions

Port F is an 8-bit input-only port in the SH7083, SH7084, and SH7085; a 16-bit input-only port in the SH7086. Port F has the following register. For details on register addresses and register states during each processing, refer to section 27, List of Registers.

## **Table 22.11 Register Configuration**

| Register Name          | Abbrevia-<br>tion | R/W | Initial Value | Address    | Access Size |

|------------------------|-------------------|-----|---------------|------------|-------------|

| Port F data register L | PFDRL             | R   | H'xxxx        | H'FFFFD382 | 8, 16       |

## 22.6.2 Port F Data Register L (PFDRL)

The port F data register L (PFDRL) is a 16-bit read-only register that stores port F data. Bits PF7DR to PF0DR correspond to pins PF7 to PF0 (multiplexed functions omitted here) in the SH7083, SH7084, and SH7085. Bits PF15DR to PF0DR correspond to pins PF15 to PF0 (multiplexed functions omitted here) in the SH7086.

Any value written into these bits is ignored, and there is no effect on the state of the pins. When any of the bits are read, the pin state rather than the bit value is read directly. However, when an A/D converter analog input is being sampled, values of 1 are read out. Table 22.12 summarizes port F data register L read/write operations.

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                       |

|---------|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 0 | UA31 to  | Undefined        | R/W | User Branch Destination Address                                                                                                                                                                                                                                                                                                                                   |

|         | UA0      |                  |     | When the user branch is not required, address 0 (H'00000000) must be set.                                                                                                                                                                                                                                                                                         |

|         |          |                  |     | The user branch destination must be an area other than<br>the flash memory, an area other than the RAM area in<br>which on-chip program has been transferred, or the<br>external bus space.                                                                                                                                                                       |

|         |          |                  |     | Note that the CPU must not branch to an area without<br>the execution code and get out of control. The on-chip<br>program download area and stack area must not be<br>overwritten. If CPU runaway occurs or the download<br>area or stack area is overwritten, the value of flash<br>memory cannot be guaranteed.                                                 |

|         |          |                  |     | The download of the on-chip program, initialization,<br>initiation of the programming/erasing program must not<br>be executed in the processing of the user branch<br>destination. Programming or erasing cannot be<br>guaranteed when returning from the user branch<br>destination. The program data which has already been<br>prepared must not be programmed. |

|         |          |                  |     | Store general registers R8 to R15. General registers R0 to R7 are available without storing them.                                                                                                                                                                                                                                                                 |

|         |          |                  |     | Moreover, the programming/erasing interface registers<br>must not be written to or RAM emulation mode must not<br>be entered in the processing of the user branch<br>destination.                                                                                                                                                                                 |

|         |          |                  |     | After the processing of the user branch has ended, the programming/erasing program must be returned to by using the RTS instruction.                                                                                                                                                                                                                              |

| _       |          |                  |     | For the execution intervals of the user branch processing, see note 2 (User branch processing intervals) in section 23.8.3, Other Notes.                                                                                                                                                                                                                          |

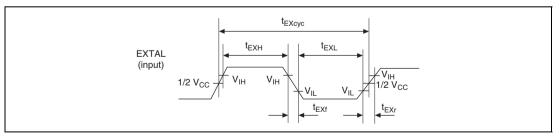

## 28.3.1 Clock Timing

## Table 28.6 Clock Timing

Conditions:  $V_{cc} = 3.0 \text{ V}$  to 3.6 V or 4.0 V to 5.5 V,  $AV_{cc} = 4.0 \text{ V}$  to 5.5 V,  $AV_{ref} = 4.0 \text{ V}$  to  $AV_{cc}$ ,  $V_{ss} = PLLV_{ss} = AV_{ss} = 0 \text{ V}$ ,  $T_a = -20^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (consumer applications),  $T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (industrial applications)

| Item                                       | Symbol             | Min.                     | Max. | Unit | Reference<br>Figure |

|--------------------------------------------|--------------------|--------------------------|------|------|---------------------|

| EXTAL clock input frequency                | f <sub>ex</sub>    | 5                        | 12.5 | MHz  | Figure 28.1         |

| EXTAL clock input cycle time               | t <sub>excyc</sub> | 80                       | 200  | ns   | _                   |

| EXTAL clock input low pulse width          | t <sub>exL</sub>   | 20                       |      | ns   | _                   |

| EXTAL clock input high pulse width         | t <sub>exH</sub>   | 20                       |      | ns   | _                   |

| EXTAL clock input rise time                | t <sub>EXr</sub>   | _                        | 5    | ns   | _                   |

| EXTAL clock input fall time                | t <sub>EXf</sub>   |                          | 5    | ns   | _                   |

| CK clock output frequency                  | f <sub>op</sub>    | 10                       | 40   | MHz  | Figure 28.2         |

| CK clock output cycle time                 | t <sub>cyc</sub>   | 25                       | 100  | ns   | _                   |

| CK clock output low pulse width            | t <sub>скь</sub>   | 1/2t <sub>cyc</sub> -7.5 |      | ns   | _                   |

| CK clock output high pulse width           | t <sub>скн</sub>   | 1/2t <sub>cyc</sub> -7.5 |      | ns   | _                   |

| CK clock output rise time                  | t <sub>cKr</sub>   | _                        | 5    | ns   | _                   |

| CK clock output fall time                  | t <sub>скf</sub>   |                          | 5    | ns   | _                   |

| Power-on oscillation settling time         | t <sub>osc1</sub>  | 10                       |      | ms   | Figure 28.3         |

| Standby return oscillation settling time 1 | t <sub>osc2</sub>  | 10                       |      | ms   | Figure 28.4         |

| Standby return oscillation settling time 2 | t <sub>osc3</sub>  | 10                       |      | ms   | Figure 28.5         |

Figure 28.1 EXTAL Clock Input Timing

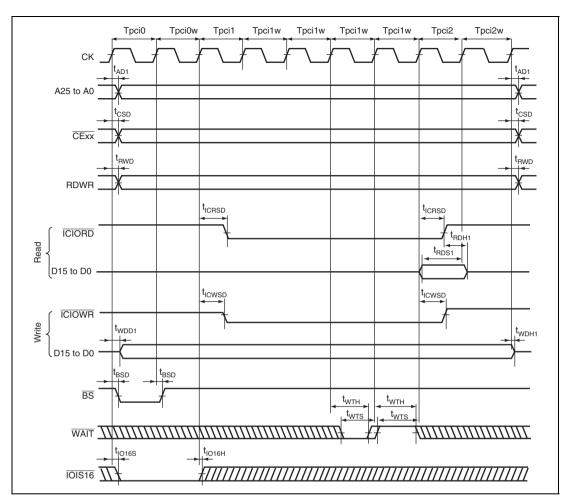

Figure 28.44 PCMCIA I/O Card Interface Bus Timing (TED = 2.5 Cycles, TEH = 1.5 Cycles, One External Wait Cycle)

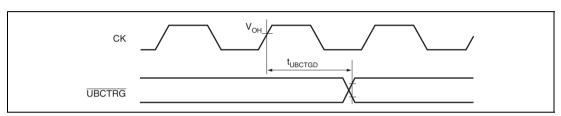

## 28.3.14 UBC Trigger Timing

## Table 28.19 UBC Trigger Timing

Conditions:  $V_{cc} = 3.0 \text{ V}$  to 3.6 V or 4.0 V to 5.5 V,  $AV_{cc} = 4.0 \text{ V}$  to 5.5 V,  $AV_{ref} = 4.0 \text{ V}$  to  $AV_{cc}$ ,  $V_{ss} = PLLV_{ss} = AV_{ss} = 0 \text{ V}$ ,  $T_a = -20^{\circ}\text{C}$  to +85°C (consumer applications),  $T_a = -40^{\circ}\text{C}$  to +85°C (industrial applications)

| Item              | Symbol              | Min. | Max. | Unit | Reference<br>Figure |

|-------------------|---------------------|------|------|------|---------------------|

| UBCTRG delay time | t <sub>ubctgd</sub> | _    | 150  | ns   | Figure 28.61        |

|                   |                     |      |      |      |                     |

Figure 28.61 UBC Trigger Timing