Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | EBI/EMI, FIFO, I <sup>2</sup> C, SCI, SSU                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 76                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | <u> </u>                                                                        |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 112-LQFP                                                                        |

| Supplier Device Package    | 112-LQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df70845ad80fpv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Related Manuals: The latest versions of all related manuals are available from our web site. Please ensure you have the latest versions of all documents you require. http://www.renesas.com/

SH7083, SH7084, SH7085, and SH7086 Group Manuals:

| Document Title                   | Document No. |

|----------------------------------|--------------|

| SH7080 Group Hardware Manual     | This manual  |

| SH-1/SH-2/SH-DSP Software Manual | REJ09B0171   |

User's Manuals for Development Tools:

| Document Title                                                                                                                | Document No. |

|-------------------------------------------------------------------------------------------------------------------------------|--------------|

| SuperH <sup>™</sup> RISC engine C/C++ Compiler, Assembler,<br>Optimizing Linkage Editor Compiler Package V.9.04 User's Manual | REJ10J2202   |

| High-performance Embedded Workshop User's Manual                                                                              | REJ10J2169   |

| Application Note:                                                                                                             |              |

| Document Title                                                                                                                | Document No. |

| SuperH RISC engine C/C++ Compiler Package Application Note                                                                    | REJ05B0463   |

All trademarks and registered trademarks are the property of their respective owners.

|      | 8.2.10   | Bus Function Extending Register (BSCEHR)                               | 183   |

|------|----------|------------------------------------------------------------------------|-------|

| 8.3  | Activati | ion Sources                                                            |       |

| 8.4  | Location | n of Transfer Information and DTC Vector Table                         | 184   |

| 8.5  | Operatio | on                                                                     | 189   |

|      | 8.5.1    | Transfer Information Read Skip Function                                | 194   |

|      | 8.5.2    | Transfer Information Writeback Skip Function                           | 195   |

|      | 8.5.3    | Normal Transfer Mode                                                   | 195   |

|      | 8.5.4    | Repeat Transfer Mode                                                   | 196   |

|      | 8.5.5    | Block Transfer Mode                                                    | 198   |

|      | 8.5.6    | Chain Transfer                                                         | 199   |

|      | 8.5.7    | Operation Timing                                                       | 201   |

|      | 8.5.8    | Number of DTC Execution Cycles                                         | 204   |

|      | 8.5.9    | DTC Bus Release Timing                                                 | 206   |

|      | 8.5.10   | DTC Activation Priority Order                                          | 209   |

| 8.6  | DTC Ac   | ctivation by Interrupt                                                 |       |

| 8.7  | Example  | les of Use of the DTC                                                  | 211   |

|      | 8.7.1    | Normal Transfer Mode                                                   |       |

|      | 8.7.2    | Chain Transfer when Counter = 0                                        | 211   |

| 8.8  | Interrup | ot Sources                                                             | 213   |

| 8.9  | Usage N  | Notes                                                                  | 213   |

|      | 8.9.1    | Module Standby Mode Setting                                            | 213   |

|      | 8.9.2    | On-Chip RAM                                                            | 213   |

|      | 8.9.3    | DTCE Bit Setting                                                       | 213   |

|      | 8.9.4    | Chain Transfer                                                         | 213   |

|      | 8.9.5    | Transfer Information Start Address, Source Address,                    |       |

|      |          | and Destination Address                                                |       |

|      | 8.9.6    | Access to DMAC or DTC Registers through DTC                            | 214   |

|      | 8.9.7    | Notes on IRQ Interrupt as DTC Activation Source                        |       |

|      | 8.9.8    | Notes on SCI and SCIF as DTC Activation Sources                        | 214   |

|      | 8.9.9    | Clearing Interrupt Source Flag                                         | 214   |

|      | 8.9.10   | Conflict between NMI Interrupt and DTC Activation                      | 215   |

|      | 8.9.11   | Operation when a DTC Activation Request Is Cancelled While in Progress | s 215 |

| Sect | ion 9 B  | Bus State Controller (BSC)                                             | 217   |

| 9.1  |          | s                                                                      |       |

| 9.2  | Input/O  | Output Pins                                                            | 220   |

| 9.3  | Area Ov  | verview                                                                | 222   |

|      | 9.3.1    | Area Division                                                          | 222   |

|      | 9.3.2    | Address Map                                                            |       |

| 9.4  | Register | r Descriptions                                                         | 241   |

| Table 9.23 | Relationship between BSZ[1:0], A2ROW[1:0]/A3ROW[1:0],                 |          |

|------------|-----------------------------------------------------------------------|----------|

| A2C        | OL[1:0]/A3COL[1:0], and Address Multiplex Output (4)-2                | 313      |

| Table 9.24 | Relationship between BSZ[1:0], A2ROW[1:0]/A3ROW[1:0],                 |          |

| A2C        | OL[1:0]/A3COL[1:0], and Address Multiplex Output (5)-1                | 314      |

| Table 9.24 | Relationship between BSZ[1:0], A2ROW[1:0]/A3ROW[1:0],                 |          |

| A2C        | OL[1:0]/A3COL[1:0], and Address Multiplex Output (5)-2                | 315      |

| Table 9.25 | Relationship between BSZ[1:0], A2ROW[1:0]/A3ROW[1:0],                 |          |

| A2C        | OL[1:0]/A3COL[1:0], and Address Multiplex Output (6)-1                | 316      |

| Table 9.25 | Relationship between BSZ[1:0], A2ROW[1:0]/A3ROW[1:0],                 |          |

| A2C        | OL[1:0]/A3COL[1:0], and Address Multiplex Output (6)-2                | 317      |

| Table 9.26 | Relationship between Access Size and Number of Bursts                 | 318      |

| Table 9.27 | Access Address in SDRAM Mode Register Write                           | 336      |

| Table 9.28 | Relationship between Bus Width, Access Size, and Number of Bursts     | 339      |

| Table 9.29 | Minimum Number of Idle Cycles between CPU Access Cycles in            |          |

| Norr       | nal Space Interface                                                   | 360      |

| Table 9.30 | Minimum Number of Idle Cycles between Access Cycles during            |          |

| DMA        | AC Dual Address Mode and DTC Transfer for the Normal Space Interface  | 361      |

| Table 9.31 | Minimum Number of Idle Cycles during DMAC Single Address Mode Tran    | nsfer to |

| the N      | Normal Space Interface from the External Device with DACK             | 362      |

| Table 9.32 | Minimum Number of Idle Cycles between Access Cycles of CPU,           |          |

| the I      | DMAC Dual Address Mode, and DTC for the SDRAM Interface               | 364      |

| Table 9.33 | Minimum Number of Idle Cycles between Access Cycles of                |          |

| the I      | DMAC Single Address Mode for the SDRAM Interface (1)                  | 367      |

| Table 9.34 | Minimum Number of Idle Cycles between Access Cycles of                |          |

| the I      | DMAC Single Address Mode for the SDRAM Interface (2)                  | 370      |

| Table 9.35 | Number of Cycles for Access to On-Chip Peripheral I/O Registers       | 379      |

| Table 9.36 | Number of External Access Cycles                                      | 382      |

|            |                                                                       |          |

| Section 10 |                                                                       |          |

| Table 10.1 | Pin Configuration                                                     |          |

| Table 10.2 | Register Configuration                                                |          |

| Table 10.3 | Selecting External Request Modes with RS Bits                         | 401      |

| Table 10.4 | Selecting External Request Detection with DL, DS Bits                 |          |

| Table 10.5 | Selecting External Request Detection with DO Bit                      |          |

| Table 10.6 | Selecting On-Chip Peripheral Module Request Modes with RS3 to RS0 Bit | s 403    |

| Table 10.7 | Supported DMA Transfers                                               | 408      |

| Table 10.8 | Relationship between Request Modes and Bus Modes by                   |          |

| DMA        | A Transfer Category                                                   |          |

| Table 10.9 | Number of Cycles per Access to On-Chip RAM by DMAC                    | 428      |

## 9.4.3 CSn Space Wait Control Register (CSnWCR) (n = 0 to 8)

CSnWCR specifies various wait cycles for memory accesses. The bit configuration of this register varies as shown below according to the memory type (TYPE 2, TYPE 1, or TYPE 0) specified by the CSn space bus control register (CSnBCR). Specify CSnWCR before accessing the target area. CSnWCR should be modified only after CSnBCR setting is completed.

### (1) Normal Space, SRAM with Byte Selection

# • CS0WCR, CS1WCR, CS2WCR, CS3WCR, CS4WCR, CS5WCR, CS6WCR, CS7WCR, CS8WCR

| Bit:           | 31 | 30 | 29 | 28  | 27   | 26      | 25  | 24  | 23  | 22  | 21 | 20  | 19  | 18   | 17      | 16  |

|----------------|----|----|----|-----|------|---------|-----|-----|-----|-----|----|-----|-----|------|---------|-----|

|                | -  | -  | -  | -   | -    | -       | -   | -   | -   | -   | -  | BAS | -   |      | WW[2:0] |     |

| Initial value: | 0  | 0  | 0  | 0   | 0    | 0       | 0   | 0   | 0   | 0   | 0  | 0   | 0   | 0    | 0       | 0   |

| R/W:           | R  | R  | R  | R   | R    | R       | R   | R   | R   | R   | R  | R/W | R   | R/W  | R/W     | R/W |

|                |    |    |    |     |      |         |     |     |     |     |    |     |     |      |         |     |

| Bit:           | 15 | 14 | 13 | 12  | 11   | 10      | 9   | 8   | 7   | 6   | 5  | 4   | 3   | 2    | 1       | 0   |

|                | -  | -  | -  | SW[ | 1:0] | WR[3:0] |     | WM  | -   | -   | -  | -   | HW[ | 1:0] |         |     |

| Initial value: | 0  | 0  | 0  | 0   | 0    | 1       | 0   | 1   | 0   | 0   | 0  | 0   | 0   | 0    | 0       | 0   |

| R/W:           | R  | R  | R  | R/W | R/W  | R/W     | R/W | R/W | R/W | R/W | R  | R   | R   | R    | R/W     | R/W |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                                                                                             |

|----------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 21 |          | All 0            | R   | Reserved                                                                                                                                |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                    |

| 20       | BAS      | 0                | R/W | Byte Access Selection when SRAM with Byte Selection is Used                                                                             |

|          |          |                  |     | Specifies the WRxx and RDWR signal timing when SRAM interface with byte selection is used.                                              |

|          |          |                  |     | 0: Asserts the WRxx signal at the read/write timing and asserts the RDWR signal during the write access cycle.                          |

|          |          |                  |     | <ol> <li>Asserts the WRxx signal during the read/write access<br/>cycle and asserts the RDWR signal at the write<br/>timing.</li> </ol> |

| 19       | _        | 0                | R   | Reserved                                                                                                                                |

|          |          |                  |     | This bit is always read as 0. The write value should always be 0.                                                                       |

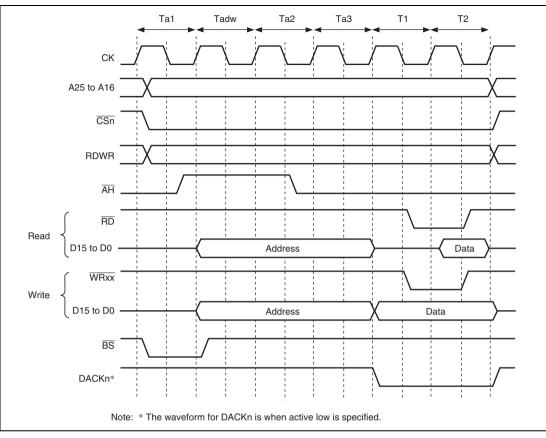

Figure 9.13 Access Timing for MPX Space (Address Cycle Wait 1, Data Cycle No Wait)

- A. Insert one idle cycle to access the interface other than the SDRAM interface after the write access cycle is performed in the SDRAM interface.

- B. Insert one idle cycle to access the SDRAM interface after the normal space interface with the external wait invalidated or the byte-selection SRAM interface with the BAS bit = 0 specified is accessed.

- C. Insert one idle cycle to access the SDRAM interface after the MPX-I/O interface is accessed.

- D. Insert two idle cycles to access the MPX-I/O interface from the external bus that is in the idle status.

- E. Insert one idle cycle to access the MPX-I/O interface after a read cycle is performed in the normal space interface, byte-selection SRAM interface with the BAS bit = 0, and the SDRAM interface.

- F. Insert two idle cycles to access the MPX-I/O interface after a write cycle is performed in the SDRAM interface.

Tables 9.29 to 9.34 list the minimum number of idle cycles to be inserted for the normal space interface and the SDRAM interface. The CSnBCR Idle Setting column in the tables describes the number of idle cycles to be set for IWW, IWRWD, IWRWS, IWRRD, and IWRRS.

## Table 9.30Minimum Number of Idle Cycles between Access Cycles during DMAC Dual<br/>Address Mode and DTC Transfer for the Normal Space Interface

| BSC Register Setting  |                        |   | cess Size is<br>n Bus Width | When Access Size Exceeds Bus Width |                                           |                                   |                                |  |  |

|-----------------------|------------------------|---|-----------------------------|------------------------------------|-------------------------------------------|-----------------------------------|--------------------------------|--|--|

| CSnWCR.<br>WM Setting | CSnBCR<br>Idle Setting |   |                             | Continuous<br>Read <sup>*1</sup>   | Read to<br>Write <sup>*<sup>2</sup></sup> | Continuous<br>Write <sup>*1</sup> | Write to<br>Read* <sup>2</sup> |  |  |

| 1                     | 0                      | 2 | 0                           | 0                                  | 2                                         | 0                                 | 0                              |  |  |

| 0                     | 0                      | 2 | 1                           | 1                                  | 2                                         | 1                                 | 1                              |  |  |

| 1                     | 1                      | 2 | 1                           | 1                                  | 2                                         | 1                                 | 1                              |  |  |

| 0                     | 1                      | 2 | 1                           | 1                                  | 2                                         | 1                                 | 1                              |  |  |

| 1                     | 2                      | 2 | 2                           | 2                                  | 2                                         | 2                                 | 2                              |  |  |

| 0                     | 2                      | 2 | 2                           | 2                                  | 2                                         | 2                                 | 2                              |  |  |

| 1                     | 4                      | 4 | 4                           | 4                                  | 4                                         | 4                                 | 4                              |  |  |

| 0                     | 4                      | 4 | 4                           | 4                                  | 4                                         | 4                                 | 4                              |  |  |

Notes: DMAC and DTC are driven by  $B\phi$ . The minimum number of idle cycles is not affected by changing a clock ratio.

Minimum number of idle cycles between the word access to address 0 and the word access to address 2 in the 32-bit access with a 16-bit bus width, minimum number of idle cycles between the byte access to address 0 and the byte access to address 1 in the 16-bit access with an 8-bit bus width, minimum number of idle cycles between the byte accesses to address 0, to address 1, to address 2, and to address 3 in the 32-bit access with an 8-bit bus width, and minimum number of idle cycles between consecutive accesses in 16-byte transfer.

2. Other than the above cases.

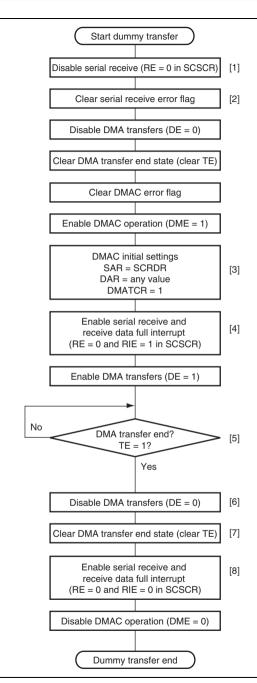

- [1] [1] Disable serial receive so no interrupt (RXI) occurs during the transfer sequence.

- [2] Clear the serial receive error flag. At this point, do not clear the interrupt source flag (RDRF in SCSSR).

- [3] Initialize the DMAC. Set the DMA transfer count to 1 (DMATCR = 1).

- [4] While serial receive remains disabled, enable the receive data full interrupt (RE = 0 and RIE = 1 in SCSCR).

- [5] Wait for the DMA transfer to end. If the DEI interrupt is enabled (IE = 1), a DEI interrupt will be generated when the DMA transfer ends.

- [6] Disable DMA transfers (DE = 0).

- [7] Clear the DMA transfer end state (clear TE).

- [8] Disable the receive data full interrupt (RIE = 0 in SCSCR) to disable interrupt requests.

## 11.3.2 Timer Mode Register (TMDR)

The TMDR registers are 8-bit readable/writable registers that are used to set the operating mode of each channel. The MTU2 has five TMDR registers, one each for channels 0 to 4. TMDR register settings should be changed only when TCNT operation is stopped.

| Bit:           | 7 | 6   | 5   | 4   | 3       | 2   | 1   | 0   |  |

|----------------|---|-----|-----|-----|---------|-----|-----|-----|--|

|                | - | BFE | BFB | BFA | MD[3:0] |     |     |     |  |

| Initial value: | 0 | 0   | 0   | 0   | 0       | 0   | 0   | 0   |  |

| R/W:           | - | R/W | R/W | R/W | R/W     | R/W | R/W | R/W |  |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | _        | 0                |     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6   | BFE      | 0                | R/W | Buffer Operation E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |          |                  |     | Specifies whether TGRE_0 and TGRF_0 are to operate<br>in the normal way or to be used together for buffer<br>operation. Compare match with TGRF occurs even<br>when TGRF is used as a buffer register.                                                                                                                                                                                                                                                                                                                                                     |

|     |          |                  |     | In channels 1 to 4, this bit is reserved. It is always read as 0 and the write value should always be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |          |                  |     | 0: TGRE_0 and TGRF_0 operate normally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |          |                  |     | 1: TGRE_0 and TGRF_0 used together for buffer<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5   | BFB      | 0                | R/W | Buffer Operation B* <sup>1</sup> * <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |          |                  |     | Specifies whether TGRB is to operate in the normal<br>way, or TGRB and TGRD are to be used together for<br>buffer operation. When TGRD is used as a buffer<br>register, TGRD input capture/output compare do not<br>take place in modes other than complementary PWM<br>mode, but compare match with TGRD occurs in<br>complementary PWM mode. Since the TGFD flag will<br>be set if a compare match occurs during Tb interval in<br>complementary PWM mode, the TGIED bit in timer<br>interrupt enable register 3/4 (TIER_3/4) should be<br>cleared to 0. |

|     |          |                  |     | In channels 1 and 2, which have no TGRD, bit 5 is reserved. It is always read as 0 and cannot be modified.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |          |                  |     | 0: TGRB and TGRD operate normally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |          |                  |     | 1: TGRB and TGRD used together for buffer operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                  |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------|

| 6   | TTGE2    | 0                | R/W | A/D Converter Start Request Enable 2                                                                                         |

|     |          |                  |     | Enables or disables generation of A/D converter start<br>requests by TCNT_4 underflow (trough) in<br>complementary PWM mode. |

|     |          |                  |     | In channels 0 to 3, bit 6 is reserved. It is always read as 0 and the write value should always be 0.                        |

|     |          |                  |     | <ol> <li>A/D converter start request generation by TCNT_4<br/>underflow (trough) disabled</li> </ol>                         |

|     |          |                  |     | <ol> <li>A/D converter start request generation by TCNT_4<br/>underflow (trough) enabled</li> </ol>                          |

| 5   | TCIEU    | 0                | R/W | Underflow Interrupt Enable                                                                                                   |

|     |          |                  |     | Enables or disables interrupt requests (TCIU) by the TCFU flag when the TCFU flag in TSR is set to 1 in channels 1 and 2.    |

|     |          |                  |     | In channels 0, 3, and 4, bit 5 is reserved. It is always read as 0 and the write value should always be 0.                   |

|     |          |                  |     | 0: Interrupt requests (TCIU) by TCFU disabled                                                                                |

|     |          |                  |     | 1: Interrupt requests (TCIU) by TCFU enabled                                                                                 |

| 4   | TCIEV    | 0                | R/W | Overflow Interrupt Enable                                                                                                    |

|     |          |                  |     | Enables or disables interrupt requests (TCIV) by the<br>TCFV flag when the TCFV flag in TSR is set to 1.                     |

|     |          |                  |     | 0: Interrupt requests (TCIV) by TCFV disabled                                                                                |

|     |          |                  |     | 1: Interrupt requests (TCIV) by TCFV enabled                                                                                 |

| 3   | TGIED    | 0                | R/W | TGR Interrupt Enable D                                                                                                       |

|     |          |                  |     | Enables or disables interrupt requests (TGID) by the TGFD bit when the TGFD bit in TSR is set to 1 in channels 0, 3, and 4.  |

|     |          |                  |     | In complementary PWM mode, clear the TGIED bit to 0 on channels 3 and 4.                                                     |

|     |          |                  |     | In channels 1 and 2, bit 3 is reserved. It is always read as 0 and the write value should always be 0.                       |

|     |          |                  |     | 0: Interrupt requests (TGID) by TGFD bit disabled                                                                            |

|     |          |                  |     | 1: Interrupt requests (TGID) by TGFD bit enabled                                                                             |

## 11.3.7 Timer Buffer Operation Transfer Mode Register (TBTM)

The TBTM registers are 8-bit readable/writable registers that specify the timing for transferring data from the buffer register to the timer general register in PWM mode. The MTU2 has three TBTM registers, one each for channels 0, 3, and 4.

| Bit:           | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|----------------|---|---|---|---|---|------|------|------|

|                | - | - | - | - | - | TTSE | TTSB | TTSA |

| Initial value: | 0 | 0 | 0 | 0 | 0 | 0    | 0    | 0    |

| R/W:           | R | R | R | R | R | R/W  | R/W  | R/W  |

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                   |

|--------|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Bit Name |                  |     | •                                                                                                                                                                                                             |

| 7 to 3 | _        | All 0            | R   | Reserved                                                                                                                                                                                                      |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                          |

| 2      | TTSE     | 0                | R/W | Timing Select E                                                                                                                                                                                               |

|        |          |                  |     | Specifies the timing for transferring data from TGRF_0<br>to TGRE_0 when they are used together for buffer<br>operation.                                                                                      |

|        |          |                  |     | In channels 3 and 4, bit 2 is reserved. It is always read<br>as 0 and the write value should always be 0. When<br>using channel 0 in other than PWM mode, do not set<br>this bit to 1.                        |

|        |          |                  |     | 0: When compare match E occurs in channel 0                                                                                                                                                                   |

|        |          |                  |     | 1: When TCNT_0 is cleared                                                                                                                                                                                     |

| 1      | TTSB     | 0                | R/W | Timing Select B                                                                                                                                                                                               |

|        |          |                  |     | Specifies the timing for transferring data from TGRD to<br>TGRB in each channel when they are used together for<br>buffer operation. When using a channel in other than<br>PWM mode, do not set this bit to1. |

|        |          |                  |     | 0: When compare match B occurs in each channel                                                                                                                                                                |

|        |          |                  |     | 1: When TCNT is cleared in each channel                                                                                                                                                                       |

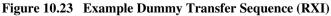

## Figure 11.78 Relationship between Bits T3AEN and T4VEN in Timer Interrupt Skipping Set Register (TITCR) and Buffer Transfer-Enabled Period

## 16.3.4 Transmit FIFO Data Register (SCFTDR)

SCFTDR is a 16-stage 8-bit FIFO register that stores data for serial transmission. When the SCIF detects that the transmit shift register (SCTSR) is empty, it moves transmit data written in the SCFTDR into SCTSR and starts serial transmission. Continuous serial transmission is performed until there is no transmit data left in SCFTDR. SCFTDR can always be written to by the CPU.

When SCFTDR is full of transmit data (16 bytes), no more data can be written. If writing of new data is attempted, the data is ignored.

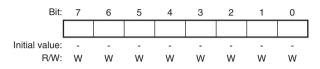

| Bit    | Bit Name | Initial<br>value | R/W | Description                    |

|--------|----------|------------------|-----|--------------------------------|

| 7 to 0 |          | Undefined        | W   | FIFO for transmits serial data |

## 16.3.5 Serial Mode Register (SCSMR)

SCSMR is a 16-bit register that specifies the SCIF serial communication format and selects the clock source for the baud rate generator.

The CPU can always read and write to SCSMR.

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4   | 3    | 2 | 1   | 0     |

|----------------|----|----|----|----|----|----|---|---|-----|-----|-----|-----|------|---|-----|-------|

|                | -  | -  | -  | -  | -  | -  | - | - | C/Ā | CHR | PE  | 0/E | STOP | - | CKS | [1:0] |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0   | 0   | 0   | 0   | 0    | 0 | 0   | 0     |

| R/W:           | R  | R  | R  | R  | R  | R  | R | R | R/W | R/W | R/W | R/W | R/W  | R | R/W | R/W   |

| Bit     | Bit Name | Initial<br>value | R/W | Description                                                          |

|---------|----------|------------------|-----|----------------------------------------------------------------------|

| 15 to 8 | —        | All 0            | R   | Reserved                                                             |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0. |

## Section 21 Pin Function Controller (PFC)

The pin function controller (PFC) is composed of registers that are used to select the functions of multiplexed pins and assign pins to be inputs or outputs. Tables 21.1 to 21.16 list the multiplexed pins of this LSI.

Tables 21.17 to 21.20 list the pin functions in each operating mode.

| Port | Function 1<br>(Related Module)            | Function 2<br>(Related Module)            | Function 3<br>(Related Module) | Function 4<br>(Related Module) | Function 5<br>(Related Module) |

|------|-------------------------------------------|-------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| А    | PA3 I/O (port)                            | A24 output (BSC)                          | RXD1 input (SCI)               | _                              | _                              |

|      | PA4 I/O (port)                            | A23 output (BSC)                          | TXD1 output (SCI)              | _                              | _                              |

|      | PA5 I/O (port)                            | A22 output (BSC)                          | DREQ1 input (DMAC)             | IRQ1 input (INTC)              | SCK1 I/O (SCI)                 |

|      | PA7 I/O (port)                            | CS3 output (BSC)                          | TCLKB input (MTU2)             | _                              | _                              |

|      | PA8 I/O (port)                            | RDWR output (BSC)                         | IRQ2 input (INTC)              | TCLKC input (MTU2)             | _                              |

|      | PA9 I/O (port)                            | CKE output (BSC)                          | IRQ3 input (INTC)              | TCLKD input (MTU2)             | _                              |

|      | PA10 I/O (port)                           | CS0 output (BSC)                          | POE4 input (POE)               | —                              | _                              |

|      | PA12 I/O (port)                           | PA12 I/O (port) WRL/DQMLL output<br>(BSC) |                                |                                | _                              |

|      | PA13 I/O (port) WRH/DQMLU output<br>(BSC) |                                           | POE7 input (POE)               | _                              | _                              |

|      | PA14 I/O (port)                           | RD output (BSC)                           | _                              | _                              | _                              |

|      | PA15 I/O (port)                           | CK output (CPG)                           | _                              |                                | —                              |

#### Table 21.1 SH7083 Multiplexed Pins (Port A)

## Table 21.2 SH7084 Multiplexed Pins (Port A)

| Port | Function 1<br>(Related Module) | Function 2<br>(Related Module) | Function 3<br>(Related Module) | Function 4<br>(Related Module) | Function 5<br>(Related Module) |

|------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| А    | PA0 I/O (port)                 | CS4 output (BSC)               | RXD0 input (SCI)               | _                              | _                              |

|      | PA1 I/O (port)                 | CS5 output (BSC)               | TXD0 output (SCI)              | —                              | —                              |

|      | PA2 I/O (port)                 | A25 output (BSC)               | DREQ0 input (DMAC)             | IRQ0 input (INTC)              | SCK0 I/O (SCI)                 |

|      | PA3 I/O (port)                 | A24 output (BSC)               | RXD1 input (SCI)               | —                              | _                              |

|      | PA4 I/O (port)                 | A23 output (BSC)               | TXD1 output (SCI)              | —                              | —                              |

|      | PA5 I/O (port)                 | A22 output (BSC)               | DREQ1 input (DMAC)             | IRQ1 input (INTC)              | SCK1 I/O (SCI)                 |

|      | PA6 I/O (port)                 | CS2 output (BSC)               | TCLKA input (MTU2)             | —                              | _                              |

|      | PA7 I/O (port)                 | CS3 output (BSC)               | TCLKB input (MTU2)             | —                              | —                              |

## 22.6 Port F

Port F in the SH7083, SH7084, and SH7085 is an input-only port with the 8 pins shown in figure 22.15.

| -      | - | PF7 (input)/AN7 (input) |

|--------|---|-------------------------|

|        | ◀ | PF6 (input)/AN6 (input) |

|        | - | PF5 (input)/AN5 (input) |

| Port F | - | PF4 (input)/AN4 (input) |

| FOILF  | - | PF3 (input)/AN3 (input) |

|        | ◄ | PF2 (input)/AN2 (input) |

|        | - | PF1 (input)/AN1 (input) |

|        | - | PF0 (input)/AN0 (input) |

## Figure 22.15 Port F (SH7083, SH7084, SH7085)

Port F in the SH7086 is an input-only port with the 16 pins shown in figure 22.16.

|        | <b> </b> ◀── | PF15 (input)/AN15 (input) |

|--------|--------------|---------------------------|

|        |              | PF14 (input)/AN14 (input) |

|        |              | PF13 (input)/AN13 (input) |

|        | <b></b>      | PF12 (input)/AN12 (input) |

|        |              | PF11 (input)/AN11 (input) |

|        | <b></b>      | PF10 (input)/AN10 (input) |

|        | <b></b>      | PF9 (input)/AN9 (input)   |

| Port F |              | PF8 (input)/AN8 (input)   |

|        |              | PF7 (input)/AN7 (input)   |

|        |              | PF6 (input)/AN6 (input)   |

|        |              | PF5 (input)/AN5 (input)   |

|        |              | PF4 (input)/AN4 (input)   |

|        |              | PF3 (input)/AN3 (input)   |

|        |              | PF2 (input)/AN2 (input)   |

|        |              | PF1 (input)/AN1 (input)   |

|        |              | PF0 (input)/AN0 (input)   |

### Figure 22.16 Port F (SH7086)

- During erase processing, ensure that no bus-mastership requests are issued by other than the interrupt and CPU bus masters. For details, see section 23.8.2, Interrupts during Programming/Erasing.

- (3.4) The return value in the erasing program, FPFR (general register R0) is checked.

- (3.5) Determine whether erasure of the necessary blocks has finished.

If more than one block is to be erased, update the FEBS parameter and repeat steps (3.2) to (3.5). Blocks that have already been erased can be erased again.

(3.6) After erasure finishes, clear FKEY and specify software protection.

If this LSI is restarted by a power-on reset immediately after user MAT erasing has finished, secure a reset period (period of  $\overline{\text{RES}} = 0$ ) that is at least as long as the normal 100 µs.

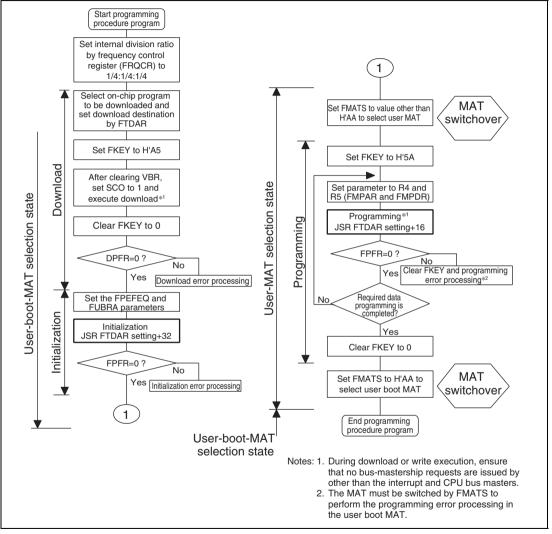

## (2) User MAT Programming in User Boot Mode

For programming the user MAT in user boot mode, additional processings made by setting FMATS are required: switching from user-boot-MAT selection state to user-MAT selection state, and switching back to user-boot-MAT selection state after programming completes. Figure 23.14 shows the procedure for programming the user MAT in user boot mode.

Figure 23.14 Procedure for Programming User MAT in User Boot Mode

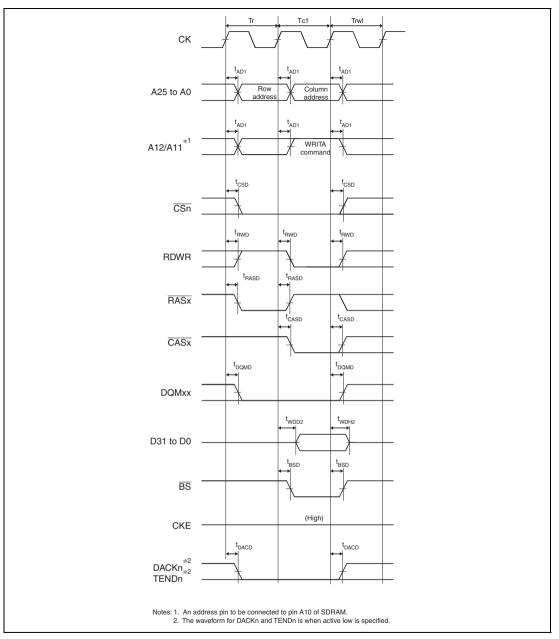

Figure 28.28 Synchronous DRAM Single Write Bus Cycle (Auto Precharge, TRWL = 1 Cycle)

| Item                                                                                                                                                                                                                                  | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <ul> <li>11.4.8 Complementary<br/>PWM Mode</li> <li>(2) Outline of<br/>Complementary PWM<br/>Mode Operation</li> <li>(n) Output Waveform<br/>Control at Synchronous<br/>Counter Clearing in<br/>Complementary PWM<br/>Mode</li> </ul> | 580  | Description amended<br>Setting the WRE bit in TWCR to 1 suppresses initial output<br>when synchronous counter clearing occurs in the Tb2 interval<br>in complementary PWM mode and controls abrupt change in<br>duty cycle at synchronous counter clearing.<br>Initial output suppression is applicable only when<br>synchronous clearing occurs in the Tb2 interval as indicated<br>by (10) or (11) in figure 11.56. When synchronous clearing<br>occurs outside that interval, the initial value specified by the<br>OLS bits in TOCR is output. Even in the Tb2 interval, if<br>synchronous clearing occurs in the initial value output period<br>(indicated by (1) in figure 11.56) immediately after the<br>counters start operation, initial value output is not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Figure 11.56 Timing for<br>Synchronous Counter<br>Clearing                                                                                                                                                                            | 581  | Suppressed.<br>Figure amended<br>Counter start<br>TGRA_3<br>TGRB_3<br>TGRB_4<br>TGRB_4<br>TODR<br>TODR<br>TODR<br>TODR<br>TODR<br>TODR<br>TODR<br>TODR<br>TODR<br>TODR<br>TOT_4<br>TODR<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4<br>TOT_4 |  |  |  |  |

| Examples of Output<br>Waveform Control at<br>Synchronous Counter<br>Clearing in<br>Complementary PWM<br>Mode                                                                                                                          |      | Description amended<br>In the MTU2S, these examples are equivalent to the cases<br>when the MTU2S operates in complementary PWM mode<br>and synchronous counter clearing is generated while the<br>SCC bit is cleared to 0 and the WRE bit is set to 1 in<br>TWCRS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

RENESAS