#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | EBI/EMI, FIFO, I <sup>2</sup> C, SCI, SSU                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 100                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LFQFP (20x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df70855ad80fpv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Section 24 Mask ROM                                                                        |

|--------------------------------------------------------------------------------------------|

| Figure 24.1 Mask ROM Block Diagram                                                         |

|                                                                                            |

| Section 25 RAM                                                                             |

| Figure 25.1 On-chip RAM Addresses                                                          |

|                                                                                            |

| Section 28 Electrical Characteristics                                                      |

| Figure 28.1 EXTAL Clock Input Timing                                                       |

| Figure 28.2 CK Clock Output Timing                                                         |

| Figure 28.3 Power-On Oscillation Settling Timing                                           |

| Figure 28.4 Oscillation Settling Timing on Return from Standby (Return by Reset) 1437      |

| Figure 28.5 Oscillation Settling Timing on Return from Standby (Return by NMI or IRQ) 1438 |

| Figure 28.6 Reset Input Timing                                                             |

| Figure 28.7 Interrupt Signal Input Timing                                                  |

| Figure 28.8 Interrupt Signal Output Timing                                                 |

| Figure 28.9 Bus Release Timing                                                             |

| Figure 28.10 Pin Driving Timing in Standby Mode                                            |

| Figure 28.11 Basic Bus Timing for Normal Space (No Wait)1445                               |

| Figure 28.12 Basic Bus Timing for Normal Space (One Software Wait Cycle) 1446              |

| Figure 28.13 Basic Bus Timing for Normal Space (One External Wait Cycle) 1447              |

| Figure 28.14 Basic Bus Timing for Normal Space                                             |

| (One Software Wait Cycle, External Wait Cycle Valid (WM Bit = 0),                          |

| No Idle Cycle)1448                                                                         |

| Figure 28.15 CS Extended Bus Cycle for Normal Space                                        |

| (SW = 1 Cycle, HW = 1 Cycle, One External Wait Cycle)1449                                  |

| Figure 28.16 Bus Cycle of SRAM with Byte Selection                                         |

| (SW = 1 Cycle, HW = 1 Cycle, One External Wait Cycle,                                      |

| BAS = 0 ( $\overline{\text{UB}}/\overline{\text{LB}}$ in Write Cycle Controlled))          |

| Figure 28.17 Bus Cycle of SRAM with Byte Selection                                         |

| (SW = 1 Cycle, HW = 1 Cycle, One External Wait Cycle, BAS = 1                              |

| (WE in Write Cycle Controlled))1451                                                        |

| Figure 28.18 MPX-I/O Interface Bus Cycle                                                   |

| (Three Address Cycles, One Software Wait Cycle, One External Wait Cycle)1452               |

| Figure 28.19 Burst MPX-I/O Interface Bus Cycle Single Read Write                           |

| (One Address Cycle, One Software Wait Cycle)1453                                           |

| Figure 28.20 Burst MPX-I/O Interface Bus Cycle Single Read Write                           |

| (One Address Cycle, One Software Wait Cycle, One External Wait Cycle) 1454                 |

| Figure 28.21 Burst MPX-I/O Interface Bus Cycle Burst Read Write                            |

| (One Address Cycle, One Software Wait Cycle)                                               |

| Figure 28.38 Synchronous DRAM Auto-Refreshing Timing                      |    |

|---------------------------------------------------------------------------|----|

| (WTRP = 1 Cycle, WTRC = 3 Cycles)                                         | 72 |

| Figure 28.39 Synchronous DRAM Self-Refreshing Timing                      |    |

| (WTRP = 1 Cycle, WTRC = 3 Cycles)                                         | 73 |

| Figure 28.40 Synchronous DRAM Mode Register Write Timing (WTRP = 1 Cycle) | 74 |

| Figure 28.41 PCMCIA Memory Card Interface Bus Timing                      | 75 |

| Figure 28.42 PCMCIA Memory Card Interface Bus Timing                      |    |

| (TED = 2.5 Cycles, TEH = 1.5 Cycles, One External Wait Cycle)             | 76 |

| Figure 28.43 PCMCIA I/O Card Interface Bus Timing14'                      | 77 |

| Figure 28.44 PCMCIA I/O Card Interface Bus Timing                         |    |

| (TED = 2.5 Cycles, TEH = 1.5 Cycles, One External Wait Cycle)             | 78 |

| Figure 28.45 DREQ Input Timing                                            | 79 |

| Figure 28.46 MTU2 Input/Output Timing                                     | 80 |

| Figure 28.47 MTU2 Clock Input Timing                                      | 81 |

| Figure 28.48 MTU2S Input/Output Timing                                    | 82 |

| Figure 28.49 I/O Port Input/Output Timing                                 | 83 |

| Figure 28.50 WDT Timing                                                   | 84 |

| Figure 28.51 Input Clock Timing                                           | 85 |

| Figure 28.52 SCI Input/Output Timing                                      | 86 |

| Figure 28.53 Input Clock Timing                                           | 87 |

| Figure 28.54 SCIF Input/Output Timing                                     | 88 |

| Figure 28.55 SSU Timing (Master, CPHS = 1)                                | 90 |

| Figure 28.56 SSU Timing (Master, CPHS = 0)                                | 90 |

| Figure 28.57 SSU Timing (Slave, CPHS = 1)                                 | 91 |

| Figure 28.58 SSU Timing (Slave, CPHS = 0)                                 | 91 |

| Figure 28.59 POE Input Timing                                             | 92 |

| Figure 28.60 I <sup>2</sup> C2 Input/Output Timing                        | 94 |

| Figure 28.61 UBC Trigger Timing                                           | 95 |

| Figure 28.62 External Trigger Input Timing                                | 96 |

| Figure 28.63 Output Load Circuit                                          | 97 |

| Figure 28.64 Connection of V <sub>CL</sub> Capacitor                      | 00 |

| Appendix                                                                  | )1 |

| Figure E.1 TFP-100BV                                                      |    |

| Figure E.2 FP-112EV                                                       |    |

| Figure E.3 FP-144LV                                                       |    |

| Figure E.4 FP-176EV                                                       |    |

| Figure E.5 BP-112V                                                        |    |

| Table 11.40 | Setting of Interrupt Skipping Count by Bits 3ACOR[2:0]    |     |

|-------------|-----------------------------------------------------------|-----|

| Table 11.41 | Setting of Interrupt Skipping Count by Bits 4VCOR[2:0]    |     |

| Table 11.42 | Setting of Bits BTE[1:0]                                  |     |

| Table 11.43 | Register Combinations in Buffer Operation                 | 530 |

| Table 11.44 | Cascaded Combinations                                     |     |

| Table 11.45 | TICCR Setting and Input Capture Input Pins                | 535 |

| Table 11.46 | PWM Output Registers and Output Pins                      |     |

| Table 11.47 | Phase Counting Mode Clock Input Pins                      |     |

| Table 11.48 | Up/Down-Count Conditions in Phase Counting Mode 1         |     |

| Table 11.49 | Up/Down-Count Conditions in Phase Counting Mode 2         |     |

| Table 11.50 | Up/Down-Count Conditions in Phase Counting Mode 3         |     |

| Table 11.51 | Up/Down-Count Conditions in Phase Counting Mode 4         | 549 |

| Table 11.52 | Output Pins for Reset-Synchronized PWM Mode               | 552 |

| Table 11.53 | Register Settings for Reset-Synchronized PWM Mode         |     |

| Table 11.54 | Output Pins for Complementary PWM Mode                    | 555 |

| Table 11.55 | Register Settings for Complementary PWM Mode              | 556 |

| Table 11.56 | Registers and Counters Requiring Initialization           | 563 |

| Table 11.57 | MTU2 Interrupts                                           |     |

| Table 11.58 | Interrupt Sources and A/D Converter Start Request Signals |     |

| Table 11.59 | Mode Transition Combinations                              |     |

|             |                                                           |     |

| Section 12  |                                                           |     |

| Table 12.1  | MTU2S Functions                                           |     |

| Table 12.2  | Pin Configuration                                         |     |

| Table 12.3  | Register Configuration                                    |     |

| Section 12  | Dout Output Englis (DOE)                                  | (02 |

| Section 13  | 1                                                         |     |

| Table 13.1  | Pin Configuration                                         |     |

| Table 13.2  | Pin Combinations                                          |     |

| Table 13.3  | Register Configuration                                    |     |

| Table 13.4  | Target Pins and Conditions for High-Impedance Control     |     |

| Table 13.5  | Interrupt Sources and Conditions                          |     |

| Section 14  | Watchdog Timer (WDT)                                      |     |

| Table 14.1  | WDT Pin Configuration                                     |     |

| Table 14.2  | Register Configuration                                    |     |

| Table 14.2  | Interrupt Source                                          |     |

| 14010 1 1.5 |                                                           |     |

| Section 15  | Serial Communication Interface (SCI)                      | 739 |

|             |                                                           |     |

| Table 15.1  | Pin Configuration                                         |     |

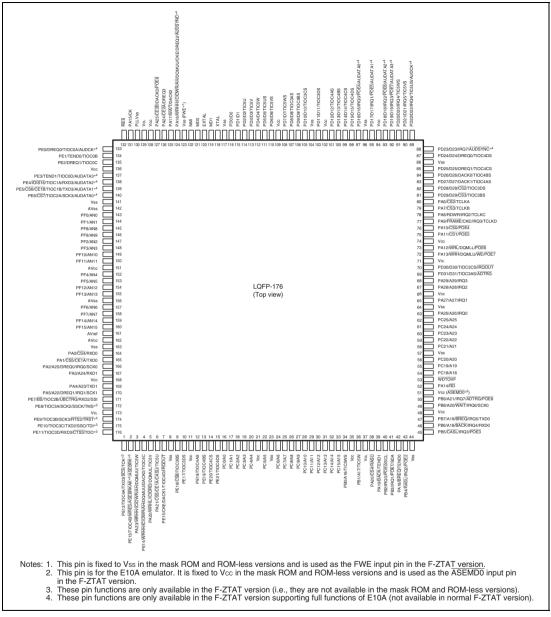

Figure 1.5 Pin Assignments of SH7086

# 4.3 Clock Operating Mode

Table 4.3 shows the clock operating mode of this LSI.

### Table 4.3Clock Operating Mode

| Clock C | perating | Clo                                 | ck I/O |                                                       |                  |

|---------|----------|-------------------------------------|--------|-------------------------------------------------------|------------------|

| Mode    | ,        | Source                              | Output | PLL Circuit                                           | Input to Divider |

| 1       |          | EXTAL input or<br>crystal resonator | CK*    | ON (×8)                                               | ×8               |

| Note: * |          | the pin function cor                |        | ut (CK) pin, appropriate<br>For details, refer to sec | -                |

**Mode 1:** The frequency of the external clock input from the EXTAL pin is multiplied by 8 in the PLL circuit before being supplied to the on-chip modules in this LSI, which eliminates the need to generate a high-frequency clock outside the LSI. Since the input clock frequency ranging from 5 MHz to 12.5 MHz can be used, the internal clock (I $\phi$ ) frequency ranges from 10 MHz to 80 MHz.

Maximum operating frequencies:

$I\phi = 80 \text{ MHz}$ ,  $B\phi = 40 \text{ MHz}$ ,  $P\phi = 40 \text{ MHz}$ ,  $MI\phi = 80 \text{ MHz}$ , and  $MP\phi = 40 \text{ MHz}$

Table 4.4 shows the frequency division ratios that can be specified with FRQCR.

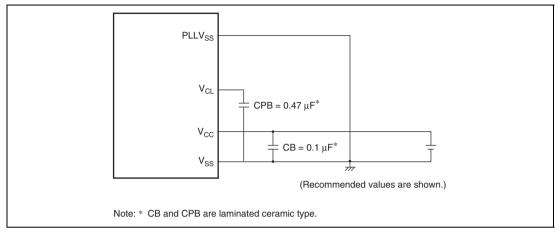

A circuitry shown in figure 4.6 is recommended as an external circuitry around the PLL. Separate the PLL power lines (PLLVss) and the system power lines (Vcc, Vss) at the board power supply source, and be sure to insert bypass capacitors CB and CPB close to the pins.

Figure 4.6 Recommended External Circuitry around PLL

break occurs at a delayed branch instruction or its delay slot, the user break may not actually take place until the first instruction at the branch destination.

### 7.4.4 Sequential Break

- By setting the SEQ bit in BRCR to 1, the sequential break is issued when a channel B break condition matches after a channel A break condition matches. A user break is not generated even if a channel B break condition matches before a channel A break condition matches. When channels A and B conditions match at the same time, the sequential break is not issued. To clear the channel A condition match when a channel A condition match has occurred but a channel B condition match has not yet occurred in a sequential break specification, clear the SEQ bit in BRCR to 0 and clear the condition match flag to 0 in channel A.

- In sequential break specification, the L or I bus can be selected and the execution times break condition can be also specified. For example, when the execution times break condition is specified, the break condition is satisfied when a channel B condition matches with BETR = H'0001 after a channel A condition has matched.

### 7.4.5 Value of Saved Program Counter

When a user break occurs, the address of the instruction from where execution is to be resumed is saved in the stack, and the exception handling state is entered. If the L bus is specified as a break condition, the instruction at which the user break should occur can be clearly determined (except for when data is included in the break condition). If the I bus is specified as a break condition, the instruction at which the user break should occur cannot be clearly determined.

- When instruction fetch (before instruction execution) is specified as a break condition: The address of the instruction that matched the break condition is saved in the stack. The instruction that matched the condition is not executed, and the user break occurs before it. However when a delay slot instruction matches the condition, the address of the delayed branch instruction is saved in the stack.

- 2. When instruction fetch (after instruction execution) is specified as a break condition: The address of the instruction following the instruction that matched the break condition is saved in the stack. The instruction that matches the condition is executed, and the user break occurs before the next instruction is executed. However when a delayed branch instruction or delay slot matches the condition, these instructions are executed, and the branch destination address is saved in the stack.

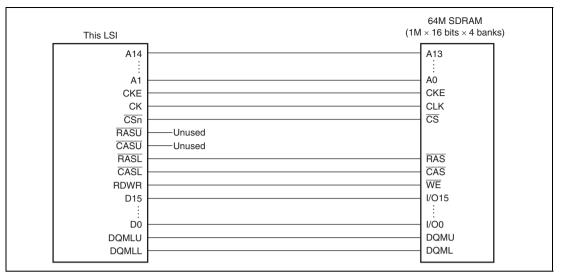

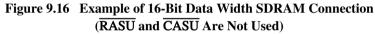

Figure 9.17 Example of 16-Bit Data Width SDRAM Connection (RASU and CASU Are Used)

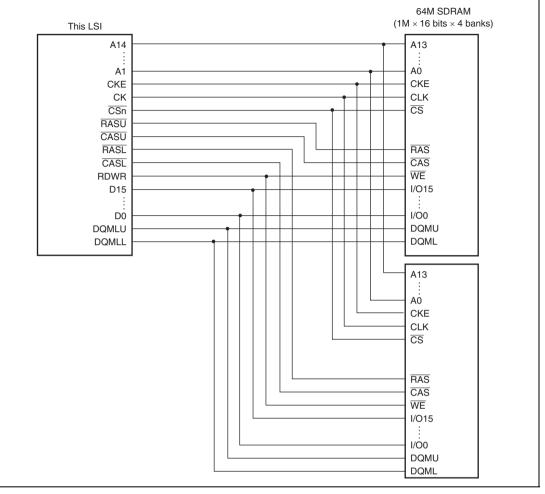

Figure 10.21 Example of DMAC Operation Timing— Activation by an On-Chip Peripheral Module (in the Case of Cycle Stealing Transfer, Dual Address Mode, Low-Level Detection, I¢:B¢:P¢ = 1:1/2:1/2, and Data Transfer from On-Chip Peripheral Module to On-Chip RAM)

### (c) Initialization

In complementary PWM mode, there are nine registers that must be initialized. In addition, there is a register that specifies whether to generate dead time (it should be used only when dead time generation should be disabled).

Before setting complementary PWM mode with bits MD[3:0] in the timer mode register (TMDR), the following initial register values must be set.

TGRC\_3 operates as the buffer register for TGRA\_3, and should be set with 1/2 the PWM carrier cycle + dead time Td. The timer cycle buffer register (TCBR) operates as the buffer register for the timer cycle data register (TCDR), and should be set with 1/2 the PWM carrier cycle. Set dead time Td in the timer dead time data register (TDDR).

When dead time is not needed, the TDER bit in the timer dead time enable register (TDER) should be cleared to 0, TGRC\_3 and TGRA\_3 should be set to 1/2 the PWM carrier cycle + 1, and TDDR should be set to 1.

Set the respective initial PWM duty values in buffer registers TGRD\_3, TGRC\_4, and TGRD\_4.

The values set in the five buffer registers excluding TDDR are transferred simultaneously to the corresponding compare registers when complementary PWM mode is set.

Set TCNT\_4 to H'0000 before setting complementary PWM mode.

| Register/Counter       | Set Value                                                         |

|------------------------|-------------------------------------------------------------------|

| TGRC_3                 | 1/2 PWM cycle + dead time Td                                      |

|                        | (1/2 PWM cycle + 1 when dead time generation is disabled by TDER) |

| TDDR                   | Dead time Td (1 when dead time generation is disabled by TDER)    |

| TCBR                   | 1/2 PWM carrier cycle                                             |

| TGRD_3, TGRC_4, TGRD_4 | Initial PWM duty value for each phase                             |

| TCNT_4                 | H'0000                                                            |

| TOCR1, TOCR2           | PWM output level setting                                          |

### Table 11.56 Registers and Counters Requiring Initialization

Note: The TGRC\_3 set value must be the sum of 1/2 the PWM cycle set in TCBR and dead time Td set in TDDR. When dead time generation is disabled by TDER, TGRC\_3 must be set to 1/2 the PWM cycle + 1.

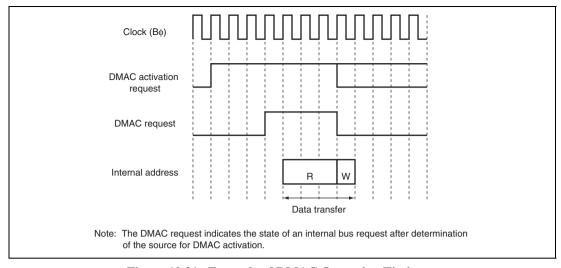

# 14.6.3 System Reset by WDTOVF Signal

If the  $\overline{\text{WDTOVF}}$  signal is input to the  $\overline{\text{RES}}$  pin of this LSI, this LSI cannot be initialized correctly.

Avoid input of the  $\overline{\text{WDTOVF}}$  signal to the  $\overline{\text{RES}}$  pin of this LSI through glue logic circuits. To reset the entire system with the  $\overline{\text{WDTOVF}}$  signal, use the circuit shown in figure 14.5.

Figure 14.5 Example of System Reset Circuit Using WDTOVF Signal

# 14.6.4 Manual Reset in Watchdog Timer Mode

When a manual reset occurs in watchdog timer mode, the current bus cycle is continued. If a manual reset occurs while the bus is released or during DMAC burst transfer, manual reset exception handling will be pended until the CPU acquires the bus mastership.

# 14.6.5 Internal Reset in Watchdog Timer Mode

When an internal reset is generated by an overflow of the watchdog timer counter (WTCNT) in watchdog timer mode, the watchdog timer control/status register (WTCSR) is not initialized and its value is maintained.

# 16.3.4 Transmit FIFO Data Register (SCFTDR)

SCFTDR is a 16-stage 8-bit FIFO register that stores data for serial transmission. When the SCIF detects that the transmit shift register (SCTSR) is empty, it moves transmit data written in the SCFTDR into SCTSR and starts serial transmission. Continuous serial transmission is performed until there is no transmit data left in SCFTDR. SCFTDR can always be written to by the CPU.

When SCFTDR is full of transmit data (16 bytes), no more data can be written. If writing of new data is attempted, the data is ignored.

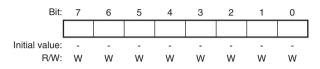

| Bit    | Bit Name | Initial<br>value | R/W | Description                    |

|--------|----------|------------------|-----|--------------------------------|

| 7 to 0 |          | Undefined        | W   | FIFO for transmits serial data |

# 16.3.5 Serial Mode Register (SCSMR)

SCSMR is a 16-bit register that specifies the SCIF serial communication format and selects the clock source for the baud rate generator.

The CPU can always read and write to SCSMR.

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4   | 3    | 2 | 1   | 0     |

|----------------|----|----|----|----|----|----|---|---|-----|-----|-----|-----|------|---|-----|-------|

|                | -  | -  | -  | -  | -  | -  | - | - | C/Ā | CHR | PE  | O/Ē | STOP | - | CKS | [1:0] |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0   | 0   | 0   | 0   | 0    | 0 | 0   | 0     |

| R/W:           | R  | R  | R  | R  | R  | R  | R | R | R/W | R/W | R/W | R/W | R/W  | R | R/W | R/W   |

| Bit     | Bit Name | Initial<br>value | R/W | Description                                                          |

|---------|----------|------------------|-----|----------------------------------------------------------------------|

| 15 to 8 | —        | All 0            | R   | Reserved                                                             |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0. |

| SH7080 | Group |

|--------|-------|

|--------|-------|

| Bit | Bit Name | Initial<br>Value | R/W                 | Description                                                                                                                          |

|-----|----------|------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 6   | TEND     | 0                | R/(W)* <sup>1</sup> | •                                                                                                                                    |

| U   | 12110    | U                |                     | [Clearing conditions]                                                                                                                |

|     |          |                  |                     | <ul> <li>When 0 is written to TEND after reading TEND = 1</li> </ul>                                                                 |

|     |          |                  |                     | When data is written to ICDRT                                                                                                        |

|     |          |                  |                     | • DTC is activated by IITXI interrupt and the DISEL bit in MRB of DTC is 0.                                                          |

|     |          |                  |                     | [Setting conditions]                                                                                                                 |

|     |          |                  |                     | <ul> <li>When the ninth clock of SCL rises with the l<sup>2</sup>C bus<br/>format while the TDRE flag is 1</li> </ul>                |

|     |          |                  |                     | • When the final bit of transmit frame is sent with the clock synchronous serial format                                              |

| 5   | RDRF     | 0                | R/(W)*1             | Receive Data Register Full                                                                                                           |

|     |          |                  |                     | [Clearing conditions]                                                                                                                |

|     |          |                  |                     | • When 0 is written to RDRF after reading RDRF = 1                                                                                   |

|     |          |                  |                     | When ICDRR is read                                                                                                                   |

|     |          |                  |                     | • DTC is activated by IIRXI interrupt and the DISEL bit in MRB of DTC is 0.                                                          |

|     |          |                  |                     | [Setting condition]                                                                                                                  |

|     |          |                  |                     | When a receive data is transferred from ICDRS to     ICDRR                                                                           |

| 4   | NACKF    | 0                | R/(W)*1             | No Acknowledge Detection Flag* <sup>2</sup>                                                                                          |

|     |          |                  |                     | [Clearing condition]                                                                                                                 |

|     |          |                  |                     | <ul> <li>When 0 is written to NACKF after reading NACKF</li> <li>= 1</li> </ul>                                                      |

|     |          |                  |                     | [Setting condition]                                                                                                                  |

|     |          |                  |                     | <ul> <li>When no acknowledge is detected from the receive<br/>device in transmission while the ACKE bit in ICIER<br/>is 1</li> </ul> |

Number of multipliers (1 byte): The number of selectable frequency multipliers and divisors for the device.

This is normally 2, which indicates the main operating frequency and the operating frequency of the peripheral modules.

- Multiplier 1 (1 byte): Multiplier or divisor for the main operating frequency Multiplier: Numerical value of the frequency multiplier (e.g. H'04 for ×4) Divisor: Two's complement negative numerical value in the case of frequency division (e.g. H'FE [-2] for ×1/2)

- Multiplier 2 (1 byte): Multiplier or divisor for the peripheral operating frequency Multiplier: Numerical value of the frequency multiplier (e.g. H'04 for ×4) Divisor: Two's complement negative numerical value in the case of frequency division (e.g. H'FE [-2] for ×1/2)

- SUM (1 byte): Checksum

## Response I

Response H'06 (1 byte): Response to the new-bit-rate selection command The ACK code is returned if the specified bit rate was selectable.

| Error    |      |       |

|----------|------|-------|

| response | H'BF | ERROR |

- Error response H'BF (1 byte): Error response to new bit rate selection

- ERROR (1 byte): Error code

- H'11: Sum-check error

- H'24: Bit rate selection error (the specified bit rate is not selectable).

- H'25: Input frequency error (the specified input frequency is not within the range from the minimum to the maximum value).

- H'26: Frequency multiplier error (the specified multiplier does not match an available one).

- H'27: Operating frequency error (the specified operating frequency is not within the range from the minimum to the maximum value).

is not accessible, such as single-chip mode, the required procedure programs, interrupt vector table, interrupt processing routine, and user branch program should be transferred to on-chip RAM before programming/erasing of the flash memory starts.

- 5. The flash memory is not accessible during programming/erasing operations. Therefore, the programming/erasing program must be downloaded to on-chip RAM in advance. Areas for executing each procedure program for initiating programming/erasing and the user program at the user branch destination for programming/erasing must be located in on-chip memory other than flash memory or the external address space.

- 6. After programming/erasing, access to flash memory is inhibited until FKEY is cleared. A reset state ( $\overline{\text{RES}} = 0$ ) for more than at least 100 µs must be taken when the LSI mode is changed to reset on completion of a programming/erasing operation.

Transitions to the reset state during programming/erasing are inhibited. When the reset signal is accidentally input to the LSI, a longer period in the reset state than usual (100  $\mu$ s) is needed before the reset signal is released.

- 7. Switching of the MATs by FMATS is needed for programming/erasing of the user MAT in user boot mode. The program which switches the MATs should be executed from the on-chip RAM. For details, see section 23.8.1, Switching between User MAT and User Boot MAT. Please make sure you know which MAT is selected when switching the MATs.

- 8. When the program data storage area indicated by the FMPDR parameter in the programming processing is within the flash memory area, an error will occur. Therefore, temporarily transfer the program data to on-chip RAM to change the address set in FMPDR to an address other than flash memory.

Based on these conditions, tables 23.17 and 23.18 show the areas in which the program data can be stored and executed according to the operation type and mode.

|             | Initiated Mode    |                 |  |  |  |

|-------------|-------------------|-----------------|--|--|--|

| Operation   | User Program Mode | User Boot Mode* |  |  |  |

| Programming | Table 23.18 (1)   | Table 23.18 (3) |  |  |  |

| Erasing     | Table 23.18 (2)   | Table 23.18 (4) |  |  |  |

RENESAS

### Table 23.17 Executable MAT

Note: \* Programming/Erasing is possible to user MATs.

Page 1340 of 1654

|                                    |              | No. of | Ŧ          |             | Access    | No. of Access | Connected Bus |

|------------------------------------|--------------|--------|------------|-------------|-----------|---------------|---------------|

| Register Name                      | Abbreviation | Bits   | Address    | Module      | Size      | States        | Width         |

| A/D control/status register_0      | ADCSR_0      | 16     | H'FFFFC910 | A/D         | 16        | Pø reference  | 16 bits       |

| A/D control register_0             | ADCR_0       | 16     | H'FFFFC912 | (Channel 0) | 16        | B:2           |               |

| A/D data register 4                | ADDR4        | 16     | H'FFFFC980 | A/D         | 16        | W:2           |               |

| A/D data register 5                | ADDR5        | 16     | H'FFFFC982 | (Channel 1) | 16        | _             |               |

| A/D data register 6                | ADDR6        | 16     | H'FFFFC984 |             | 16        | _             |               |

| A/D data register 7                | ADDR7        | 16     | H'FFFFC986 |             | 16        | _             |               |

| A/D control/status register_1      | ADCSR_1      | 16     | H'FFFFC990 |             | 16, 8, 32 |               |               |

| A/D control register_1             | ADCR_1       | 16     | H'FFFFC992 |             | 16        |               |               |

| A/D data register 8                | ADDR8        | 16     | H'FFFFCA00 | A/D         | 16        | -             |               |

| A/D data register 9                | ADDR9        | 16     | H'FFFFCA02 | (Channel 2) | 16        | _             |               |

| A/D data register 10               | ADDR10       | 16     | H'FFFFCA04 |             | 16        | _             |               |

| A/D data register 11               | ADDR11       | 16     | H'FFFFCA06 |             | 16        | _             |               |

| A/D data register 12               | ADDR12       | 16     | H'FFFFCA08 |             | 16        | -             |               |

| A/D data register 13               | ADDR13       | 16     | H'FFFFCA0A |             | 16        | -             |               |

| A/D data register 14               | ADDR14       | 16     | H'FFFFCA0C |             | 16        | -             |               |

| A/D data register 15               | ADDR15       | 16     | H'FFFFCA0E |             | 16        | -             |               |

| A/D control/status register_2      | ADCSR_2      | 16     | H'FFFFCA10 |             | 16        | -             |               |

| A/D control register_2             | ADCR_2       | 16     | H'FFFFCA12 |             | 16        | -             |               |

| Flash code control/status register | FCCS         | 8      | H'FFFFCC00 | FLASH       | 8         | Pø reference  | 16 bits       |

| Flash program code select register | FPCS         | 8      | H'FFFFCC01 | _           | 8         | B:5           |               |

| Flash erase code select register   | FECS         | 8      | H'FFFFCC02 |             | 8         | -             |               |

| Flash key code register            | FKEY         | 8      | H'FFFFCC04 | _           | 8         | _             |               |

| Flash MAT select register          | FMATS        | 8      | H'FFFFCC05 | _           | 8         | _             |               |

| Flash transfer destination address | FTDAR        | 8      | H'FFFFCC06 | _           | 8         | _             |               |

| register                           |              |        |            |             |           |               |               |

| DTC enable register A              | DTCERA       | 16     | H'FFFFCC80 | DTC         | 8, 16     | Pø reference  | 16 bits       |

| DTC enable register B              | DTCERB       | 16     | H'FFFFCC82 |             | 8, 16     | B:2           |               |

| DTC enable register C              | DTCERC       | 16     | H'FFFFCC84 |             | 8, 16     | W:2           |               |

| DTC enable register D              | DTCERD       | 16     | H'FFFFCC86 |             | 8, 16     | L:4           |               |

| DTC enable register E              | DTCERE       | 16     | H'FFFFCC88 |             | 8, 16     | _             |               |

| DTC control register               | DTCCR        | 8      | H'FFFFCC90 | _           | 8         | _             |               |

| DTC vector base register           | DTCVBR       | 32     | H'FFFFCC94 | _           | 8, 16, 32 | -             |               |

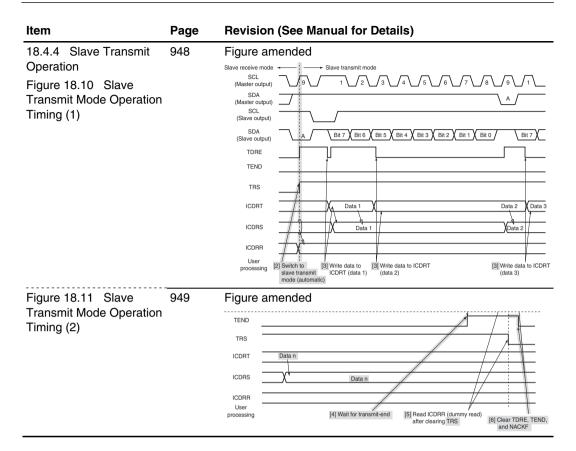

| Item                                                                                        | Page     | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.4.8 Complementary                                                                        | 560, 561 | Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PWM Mode<br>(2) Outline of<br>Complementary PWM<br>Mode Operation<br>(b) Register Operation |          | In complementary PWM mode, nine registers, comprising compare registers, buffer registers, and temporary registers, are used to control the PWM duty. Figure 11.40 shows an example of complementary PWM mode operation.                                                                                                                                                                                                                                                                                                                  |

|                                                                                             |          | The registers which are constantly compared with the counters to perform PWM output are TGRB_3, TGRA_4, and TGRB_4. When one of these registers matches the counter, the level set in the corresponding timer output control register (TOCR1 or TOCR2) is output on the PWM pin.                                                                                                                                                                                                                                                          |

|                                                                                             |          | The buffer registers for these compare registers are TGRD_3, TGRC_4, and TGRD_4.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                             |          | Between a buffer register and compare register there is a temporary register. The temporary registers cannot be accessed by the CPU.                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                             |          | Data in a compare register is changed by writing the new data to the corresponding buffer register. The buffer registers can be read or written at any time.                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                             |          | When overwriting the data in the buffer registers, always<br>write to TGRD_4 last to enable data transfer from the buffer<br>registers to the temporary registers. At this time, transfer is<br>also enabled from the timer cycle register buffer registers<br>(TGRA_3 and TCBR) to the temporary registers. All five<br>temporary registers can be used simultaneously for transfers.                                                                                                                                                    |

|                                                                                             |          | When transfer is enabled during the Ta interval, data written<br>to the buffer register is transferred immediately to the<br>temporary register. Transfer to the temporary register does<br>not take place in the Tb1 or Tb2 interval. Data for which<br>transfer is enabled during either of these intervals is<br>transferred to the temporary register after the interval ends.                                                                                                                                                        |

|                                                                                             |          | The value transferred to a temporary register is transferred to<br>the compare register either when the Tb1 interval ends<br>(when TGRA_3 is matched if TCNTS is counting up) or when<br>the Tb2 interval ends (when H'0000 is matched if TCNTS is<br>counting down). The timing for transfer from the temporary<br>register to the compare register can be selected with bits<br>MD[3:0] in the timer mode register (TMDR). Figure 11.40<br>shows an example in which the mode is selected in which the<br>change is made in the trough. |

RENESAS

| Item                                                      | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.4.8 Complementary<br>PWM Mode<br>(2) Outline of        | 565  | Figure amended Transfer from temporary register to compare register                                                                                                                                                                                                                                                                           |

| Complementary PWM<br>Mode Operation                       |      | $T_{a} \rightarrow \overleftarrow{T_{b1}} \overleftarrow{T_{a}} \overleftarrow{T_{b2}} \overleftarrow{T_{a}}$                                                                                                                                                                                                                                 |

| (f) Dead Time<br>Suppressing                              |      |                                                                                                                                                                                                                                                                                                                                               |

| Figure 11.41 Example of<br>Operation without Dead<br>Time |      | TGRA_4                                                                                                                                                                                                                                                                                                                                        |

|                                                           |      | TDDR=1                                                                                                                                                                                                                                                                                                                                        |

|                                                           |      | Buffer register TGRC_4 Data1 Data2                                                                                                                                                                                                                                                                                                            |

|                                                           |      | Temporary register TEMP2 Data1 Data2                                                                                                                                                                                                                                                                                                          |

|                                                           |      | Compare register TGRA_4                                                                                                                                                                                                                                                                                                                       |

|                                                           |      | TIOC4A                                                                                                                                                                                                                                                                                                                                        |

|                                                           |      | TIOC4C Output waveform is active-low.                                                                                                                                                                                                                                                                                                         |

| (g) PWM Cycle Setting                                     | 566  | Description amended                                                                                                                                                                                                                                                                                                                           |

|                                                           |      | With dead time: TGRA_3 set value = TCDR set value +<br>TDDR set value                                                                                                                                                                                                                                                                         |

|                                                           |      | TCDR set value > Double the TDDR set value + 2                                                                                                                                                                                                                                                                                                |

|                                                           |      | Without dead time: TGRA_3 set value = TCDR set value + 1<br>TCDR set value > 4                                                                                                                                                                                                                                                                |

|                                                           |      | The TGRA_3 and TCDR settings are made by setting the values in buffer registers TGRC_3 and TCBR. When a write is performed to TGRD_4 and transfer is enabled, the values set in TGRC_3 and TCBR are transferred simultaneously to TGRA_3 and TCDR in accordance with the transfer timing selected by bits MD[3:0] in the timer mode register. |

| Figure 11.42 Example of<br>PWM Cycle Updating             | 567  | Figure replaced                                                                                                                                                                                                                                                                                                                               |