#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | EBI/EMI, FIFO, I <sup>2</sup> C, SCI, SSU                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 65                                                                              |

| Program Memory Size        | -                                                                               |

| Program Memory Type        | ROMIess                                                                         |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/ds70830an80ftv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Tables

| Section 1  | Overview1                                        |

|------------|--------------------------------------------------|

| Table 1.1  | Features                                         |

| Table 1.2  | Pin Functions                                    |

|            |                                                  |

| Section 2  | CPU                                              |

| Table 2.1  | Initial Values of Registers                      |

| Table 2.2  | Word Data Sign Extension                         |

| Table 2.3  | Delayed Branch Instructions                      |

| Table 2.4  | T Bit                                            |

| Table 2.5  | Access to Immediate Data                         |

| Table 2.6  | Access to Absolute Address                       |

| Table 2.7  | Access with Displacement                         |

| Table 2.8  | Addressing Modes and Effective Addresses         |

| Table 2.9  | Instruction Formats                              |

| Table 2.10 | Instruction Types                                |

| Table 2.11 | Data Transfer Instructions                       |

| Table 2.12 | Arithmetic Operation Instructions                |

| Table 2.13 | Logic Operation Instructions                     |

| Table 2.14 | Shift Instructions                               |

| Table 2.15 | Branch Instructions                              |

| Table 2.16 | System Control Instructions                      |

| Section 3  | MCU Operating Modes                              |

| Table 3.1  | Selection of Operating Modes <sup>*1</sup>       |

| Table 3.2  | Pin Configuration                                |

| 14010 5.2  |                                                  |

| Section 4  | Clock Pulse Generator (CPG)                      |

| Table 4.1  | Operating Clock for Each Module70                |

| Table 4.2  | Pin Configuration                                |

| Table 4.3  | Clock Operating Mode                             |

| Table 4.4  | Frequency Division Ratios Specifiable with FRQCR |

| Table 4.5  | Register Configuration                           |

| Table 4.6  | Damping Resistance Values (Reference Values)     |

| Table 4.7  | Crystal Resonator Characteristics                |

| Section 5  | Exception Handling                               |

| Table 5.1  | Types of Exceptions and Priority                 |

|            |                                                  |

| Classification                                    | Symbol                                      | I/O | Name                                                    | Function                                                                                                                                        |

|---------------------------------------------------|---------------------------------------------|-----|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Multi function timer-<br>pulse unit 2 (MTU2)      | TCLKA,<br>TCLKB,<br>TCLKC,<br>TCLKD         | I   | MTU2 timer clock input                                  | External clock input pins for the timer.<br>Only TCLKB, TCLKC, and TCLKD are available in the SH7083.                                           |

|                                                   | TIOC0A,<br>TIOC0B,<br>TIOC0C,<br>TIOC0D     | I/O | MTU2 input<br>capture/output<br>compare<br>(channel 0)  | The TGRA_0 to TGRD_0 input capture input/output compare output/PWM output pins.                                                                 |

|                                                   | TIOC1A,<br>TIOC1B                           | I/O | MTU2 input<br>capture/output<br>compare<br>(channel 1)  | The TGRA_1 to TGRB_1 input<br>capture input/output compare<br>output/PWM output pins.<br>Only TIOC1A is available in the<br>SH7083.             |

|                                                   | TIOC2A,<br>TIOC2B                           | I/O | MTU2 input<br>capture/output<br>compare<br>(channel 2)  | The TGRA_2 to TGRB_2 input capture input/output compare output/PWM output pins.                                                                 |

|                                                   | TIOC3A,<br>TIOC3B,<br>TIOC3C,<br>TIOC3D     | I/O | MTU2 input<br>capture/output<br>compare<br>(channel 3)  | The TGRA_3 to TGRD_3 input<br>capture input/output compare<br>output/PWM output pins.<br>Only TIOC3A and TIOC3C are<br>available in the SH7083. |

|                                                   | TIOC4A,<br>TIOC4B,<br>TIOC4C,<br>TIOC4D     | I/O | MTU2 input<br>capture/output<br>compare<br>(channel 4)  | The TGRA_4 to TGRD_4 input capture input/output compare output/PWM output pins.                                                                 |

|                                                   | TIC5U,<br>TIC5V,<br>TIC5W                   | I   | MTU2 input<br>capture<br>(channel 5)                    | The TGRU_5, TGRV_5, and TGRW_5 input capture input pins.                                                                                        |

| Multi function timer-<br>pulse unit 2S<br>(MTU2S) | TIOC3AS,<br>TIOC3BS,<br>TIOC3CS,<br>TIOC3DS | I/O | MTU2S input<br>capture/output<br>compare<br>(channel 3) | The TGRA_3S to TGRD_3S input capture input/output compare output/PWM output pins.                                                               |

|                                                   | TIOC4AS,<br>TIOC4BS,<br>TIOC4CS,<br>TIOC4DS | I/O | MTU2S input<br>capture/output<br>compare<br>(channel 4) | The TGRA_4S to TGRD_4S input capture input/output compare output/PWM output pins.                                                               |

| Addressing<br>Mode                        | Instruction<br>Format | Effective Address Calculation Method                                                                                                                                                                            | Calculation<br>Formula                                                     |

|-------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Register<br>indirect with<br>displacement | @(disp:4,<br>Rn)      | Effective address is register Rn contents with<br>4-bit displacement disp added. After disp is<br>zero-extended, it is multiplied by 1 (byte), 2<br>(word), or 4 (longword), according to the<br>operand size.  | Byte: Rn + disp<br>Word: Rn + disp × 2<br>Longword: Rn +<br>disp × 4       |

| Index<br>register indirect                | @(R0, Rn)             | Effective address is sum of register Rn and R0 contents.                                                                                                                                                        | Rn + R0                                                                    |

| GBR indirect<br>with<br>displacement      | @(disp:8,<br>GBR)     | Effective address is register GBR contents with<br>8-bit displacement disp added. After disp is<br>zero-extended, it is multiplied by 1 (byte), 2<br>(word), or 4 (longword), according to the<br>operand size. | Byte: GBR + disp<br>Word: GBR + disp ×<br>2<br>Longword: GBR +<br>disp × 4 |

| Index GBR<br>indirect                     | @(R0,<br>GBR)         | Effective address is sum of register GBR and<br>R0 contents.                                                                                                                                                    | GBR + R0                                                                   |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | IRQ4F    | 0                | R/W | <ul> <li>Indicates the status of an IRQ4 interrupt request.</li> <li>When level detection mode is selected</li> <li>O: An IRQ4 interrupt has not been detected</li> <li>[Clearing condition]</li> <li>Driving pin IRQ4 high</li> </ul>                                                                                                                                                                                                                                                                                                                                                                               |

|     |          |                  |     | <ol> <li>An IRQ4 interrupt has been detected         <pre>[Setting condition]         Driving pin IRQ4 low</pre> </li> <li>When edge detection mode is selected         <pre>O: An IRQ4 interrupt has not been detected             [Clearing conditions]</pre></li></ol>                                                                                                                                                                                                                                                                                                                                            |

|     |          |                  |     | 1: An IRQ4 interrupt request has been detected<br>[Setting condition]<br>Detecting the specified edge of pin IRQ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | IRQ3F    | 0                | R/W | <ul> <li>Indicates the status of an IRQ3 interrupt request.</li> <li>When level detection mode is selected</li> <li>Chan IRQ3 interrupt has not been detected [Clearing condition] Driving pin IRQ3 high</li> <li>An IRQ3 interrupt has been detected [Setting condition] Driving pin IRQ3 low</li> <li>When edge detection mode is selected</li> <li>Chan IRQ3 interrupt has not been detected [Clearing conditions] - Writing 0 after reading IRQ3F = 1 - Accepting an IRQ3 interrupt</li> <li>An IRQ3 interrupt request has been detected [Setting condition] Detecting the specified edge of pin IRQ3</li> </ul> |

- 7. PCMCIA direct interface

- Supports the IC memory card and I/O card interface defined in JEIDA specifications Ver. 4.2 (PCMCIA2.1 Rev. 2.1)

- Wait-cycle insertion controllable by program

- 8. Burst MPX-I/O interface

- Directly connects peripheral LSIs with address/data multiplexing

- Supports burst transfer

- 9. Burst ROM (clock synchronous) interface

- Directly connects clock-synchronous burst ROM

- 10. Refresh function

- Supports the auto-refresh and self-refresh functions

- Specifies the refresh interval using the refresh counter and clock selection

- Can execute concentrated refresh by specifying the refresh counts (1, 2, 4, 6, or 8)

- 11. Usage as interval timer for refresh counter

- Generates an interrupt request at compare match

|      |          | Initial |     |                                                                                                                                           |

|------|----------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| Bit  | Bit Name | Value   | R/W | Description                                                                                                                               |

| 1, 0 | HW[1:0]  | 00      | R/W | Delay Cycles from $\overline{\text{RD}}$ and $\overline{\text{WRxx}}$ Negation to $\overline{\text{CSn}}$<br>Negation                     |

|      |          |         |     | Specify the number of delay cycles from $\overline{\text{RD}}$ and $\overline{\text{WRxx}}$ negation to $\overline{\text{CSn}}$ negation. |

|      |          |         |     | 00: 0.5 cycle                                                                                                                             |

|      |          |         |     | 01: 1.5 cycles                                                                                                                            |

|      |          |         |     | 10: 2.5 cycles                                                                                                                            |

|      |          |         |     | 11: 3.5 cycles                                                                                                                            |

# (3) Burst ROM (Asynchronous)

#### • CS0WCR, CS4WCR

| Bit:           | 31 | 30 | 29 | 28  | 27    | 26  | 25  | 24   | 23  | 22  | 21 | 20  | 19 | 18 | 17  | 16    |

|----------------|----|----|----|-----|-------|-----|-----|------|-----|-----|----|-----|----|----|-----|-------|

|                | -  | -  | -  | -   | -     | -   | -   | -    | -   | -   | -  | BEN | -  | -  | BW  | [1:0] |

| Initial value: | 0  | 0  | 0  | 0   | 0     | 0   | 0   | 0    | 0   | 0   | 0  | 0   | 0  | 0  | 0   | 0     |

| R/W:           | R  | R  | R  | R   | R     | R   | R   | R    | R   | R   | R  | R/W | R  | R  | R/W | R/W   |

| Bit:           | 15 | 14 | 13 | 12  | 11    | 10  | 9   | 8    | 7   | 6   | 5  | 4   | 3  | 2  | 1   | 0     |

|                | -  | -  | -  | SW  | [1:0] |     | W[  | 3:0] |     | WM  | -  | -   | -  | -  | нw  | [1:0] |

| Initial value: | 0  | 0  | 0  | 0   | 0     | 1   | 0   | 1    | 0   | 0   | 0  | 0   | 0  | 0  | 0   | 0     |

| R/W:           | R  | R  | R  | R/W | R/W   | R/W | R/W | R/W  | R/W | R/W | R  | R   | R  | R  | R/W | R/W   |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                          |

|----------|----------|------------------|-----|----------------------------------------------------------------------|

| 31 to 21 | _        | All 0            | R   | Reserved                                                             |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0. |

| Bus Width | BEN Bit      | Access Size | Number of Bursts | Number of Accesses |

|-----------|--------------|-------------|------------------|--------------------|

| 8 bits    | Not affected | 8 bits      | 1                | 1                  |

|           | Not affected | 16 bits     | 2                | 1                  |

|           | Not affected | 32 bits     | 4                | 1                  |

|           | 0            | 16 bytes    | 16               | 1                  |

|           | 1            |             | 4                | 4                  |

| 16 bits   | Not affected | 8 bits      | 1                | 1                  |

|           | Not affected | 16 bits     | 1                | 1                  |

|           | Not affected | 32 bits     | 2                | 1                  |

|           | 0            | 16 bytes    | 8                | 1                  |

|           | 1            |             | 2                | 4                  |

| 32 bits   | Not affected | 8 bits      | 1                | 1                  |

|           | Not affected | 16 bits     | 1                | 1                  |

|           | Not affected | 32 bits     | 1                | 1                  |

|           | Not affected | 16 bytes    | 4                | 1                  |

#### Table 9.28 Relationship between Bus Width, Access Size, and Number of Bursts

## Table 9.33 Minimum Number of Idle Cycles between Access Cycles of the DMAC Single Address Mode for the SDRAM Interface (1)

Transfer from the external device with DACK to the SDRAM interface:

|                        | BSC Register Settir    |                        |                                  |

|------------------------|------------------------|------------------------|----------------------------------|

| CMNCR.DMAIW<br>Setting | CS3WCR.WTRP<br>Setting | CS3WCR.TRWL<br>Setting | Minimum Number of<br>Idle Cycles |

| 0                      | 1                      | 0                      | <b>1</b> * <sup>2</sup>          |

| 0                      | 1                      | 1                      | 1                                |

| 0                      | 1                      | 2                      | 2                                |

| 0                      | 1                      | 3                      | 3                                |

| 0                      | 2                      | 0                      | 1                                |

| 0                      | 2                      | 1                      | 2                                |

| 0                      | 2                      | 2                      | 3                                |

| 0                      | 2                      | 3                      | 4                                |

| 0                      | 3                      | 0                      | 2                                |

| 0                      | 3                      | 1                      | 3                                |

| 0                      | 3                      | 2                      | 4                                |

| 0                      | 3                      | 3                      | 5                                |

| 0                      | 4                      | 0                      | 3                                |

| 0                      | 4                      | 1                      | 4                                |

| 0                      | 4                      | 2                      | 5                                |

| 0                      | 4                      | 3                      | 6                                |

| 1                      | 1                      | 0                      | 1                                |

| 1                      | 1                      | 1                      | 1                                |

| 1                      | 1                      | 2                      | 2                                |

| 1                      | 1                      | 3                      | 3                                |

| 1                      | 2                      | 0                      | 1                                |

| 1                      | 2                      | 1                      | 2                                |

| 1                      | 2                      | 2                      | 3                                |

| 1                      | 2                      | 3                      | 4                                |

| 1                      | 3                      | 0                      | 2                                |

| 1                      | 3                      | 1                      | 3                                |

| 1                      | 3                      | 2                      | 4                                |

| 1                      | 3                      | 3                      | 5                                |

| 1                      | 4                      | 0                      | 3                                |

|                        |                        |                        |                                  |

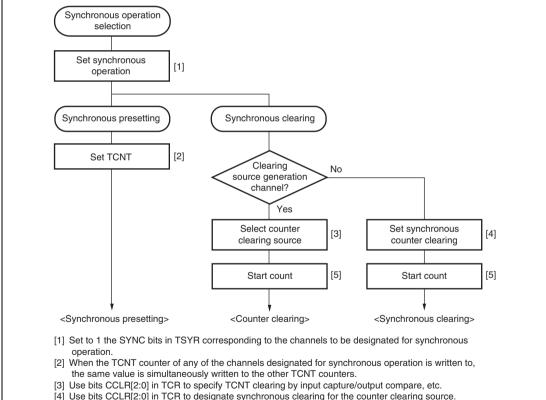

# 11.4.2 Synchronous Operation

In synchronous operation, the values in a number of TCNT counters can be rewritten simultaneously (synchronous presetting). Also, a number of TCNT counters can be cleared simultaneously by making the appropriate setting in TCR (synchronous clearing).

Synchronous operation enables TGR to be incremented with respect to a single time base.

Channels 0 to 4 can all be designated for synchronous operation. Channel 5 cannot be used for synchronous operation.

# Example of Synchronous Operation Setting Procedure:

Figure 11.12 shows an example of the synchronous operation setting procedure.

[5] Set to 1 the CST bits in TSTR for the relevant channels, to start the count operation.

Figure 11.12 Example of Synchronous Operation Setting Procedure

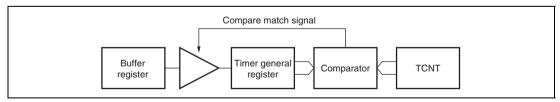

# 11.4.3 Buffer Operation

Buffer operation, provided for channels 0, 3, and 4, enables TGRC and TGRD to be used as buffer registers. In channel 0, TGRF can also be used as a buffer register.

Buffer operation differs depending on whether TGR has been designated as an input capture register or as a compare match register.

Note: TGRE\_0 cannot be designated as an input capture register and can only operate as a compare match register.

Table 11.43 shows the register combinations used in buffer operation.

| Table 11.43 | Register | <b>Combinations i</b> | in Buffer | Operation |

|-------------|----------|-----------------------|-----------|-----------|

|-------------|----------|-----------------------|-----------|-----------|

| Channel | Timer General Register | Buffer Register |

|---------|------------------------|-----------------|

| 0       | TGRA_0                 | TGRC_0          |

|         | TGRB_0                 | TGRD_0          |

|         | TGRE_0                 | TGRF_0          |

| 3       | TGRA_3                 | TGRC_3          |

|         | TGRB_3                 | TGRD_3          |

| 4       | TGRA_4                 | TGRC_4          |

|         | TGRB_4                 | TGRD_4          |

• When TGR is an output compare register

When a compare match occurs, the value in the buffer register for the corresponding channel is transferred to the timer general register.

This operation is illustrated in figure 11.14.

Figure 11.14 Compare Match Buffer Operation

| 12       3.0       187500         14       3.5       218750         16       4.0       250000         18       4.5       281250         20       5.0       312500         22       5.5       343750         24       6.0       375000         28       7.0       437500         30       7.5       468750         32       8.0       500000         34       8.5       531250         36       9.0       562500         38       9.5       593750 | Ρφ (MHz) | External Input Clock (MHz) | Maximum Bit Rate (bits/s) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------|---------------------------|

| 143.5218750164.0250000184.5281250205.0312500225.5343750246.0375000266.5406250287.0437500307.5468750328.0500000348.5531250369.0562500389.5593750                                                                                                                                                                                                                                                                                                   | 10       | 2.5                        | 156250                    |

| 164.0250000184.5281250205.0312500225.5343750246.0375000266.5406250287.0437500307.5468750328.0500000348.5531250369.0562500389.5593750                                                                                                                                                                                                                                                                                                              | 12       | 3.0                        | 187500                    |

| 184.5281250205.0312500225.5343750246.0375000266.5406250287.0437500307.5468750328.0500000348.5531250369.0562500389.5593750                                                                                                                                                                                                                                                                                                                         | 14       | 3.5                        | 218750                    |

| 20       5.0       312500         22       5.5       343750         24       6.0       375000         26       6.5       406250         28       7.0       437500         30       7.5       468750         32       8.0       500000         34       8.5       531250         36       9.0       562500         38       9.5       593750                                                                                                       | 16       | 4.0                        | 250000                    |

| 22       5.5       343750         24       6.0       375000         26       6.5       406250         28       7.0       437500         30       7.5       468750         32       8.0       500000         34       8.5       531250         36       9.0       562500         38       9.5       593750                                                                                                                                         | 18       | 4.5                        | 281250                    |

| 246.0375000266.5406250287.0437500307.5468750328.0500000348.5531250369.0562500389.5593750                                                                                                                                                                                                                                                                                                                                                          | 20       | 5.0                        | 312500                    |

| 266.5406250287.0437500307.5468750328.0500000348.5531250369.0562500389.5593750                                                                                                                                                                                                                                                                                                                                                                     | 22       | 5.5                        | 343750                    |

| 28       7.0       437500         30       7.5       468750         32       8.0       500000         34       8.5       531250         36       9.0       562500         38       9.5       593750                                                                                                                                                                                                                                               | 24       | 6.0                        | 375000                    |

| 307.5468750328.0500000348.5531250369.0562500389.5593750                                                                                                                                                                                                                                                                                                                                                                                           | 26       | 6.5                        | 406250                    |

| 32       8.0       50000         34       8.5       531250         36       9.0       562500         38       9.5       593750                                                                                                                                                                                                                                                                                                                    | 28       | 7.0                        | 437500                    |

| 34         8.5         531250           36         9.0         562500           38         9.5         593750                                                                                                                                                                                                                                                                                                                                     | 30       | 7.5                        | 468750                    |

| 36         9.0         562500           38         9.5         593750                                                                                                                                                                                                                                                                                                                                                                             | 32       | 8.0                        | 500000                    |

| 38 9.5 593750                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34       | 8.5                        | 531250                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36       | 9.0                        | 562500                    |

| 40 10.0 625000                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38       | 9.5                        | 593750                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40       | 10.0                       | 625000                    |

#### Table 15.8 Maximum Bit Rates with External Clock Input (Asynchronous Mode)

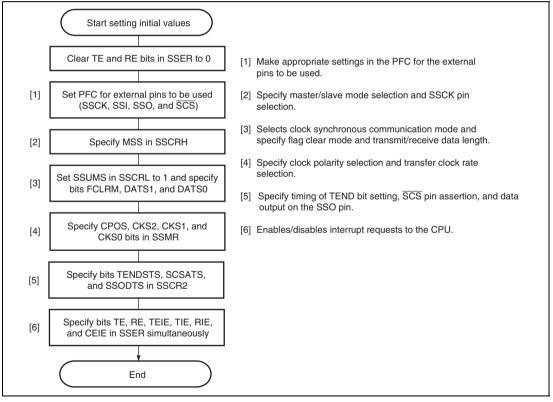

# 17.4.7 Clock Synchronous Communication Mode

In clock synchronous communication mode, data communications are performed via three lines: clock line (SSCK), data input line (SSI), and data output line (SSO).

# (1) Initial Settings in Clock Synchronous Communication Mode

Figure 17.12 shows an example of the initial settings in clock synchronous communication mode. Before data transfer, clear both the TE and RE bits in SSER to 0 to set the initial values.

Note: Before changing operating modes and communications formats, clear both the TE and RE bits to 0. Although clearing the TE bit to 0 sets the TDRE bit to 1, clearing the RE bit to 0 does not change the values of the RDRF and ORER bits and SSRDR. Those bits retain the previous values.

Figure 17.12 Example of Initial Settings in Clock Synchronous Communication Mode

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                             |

|-----|----------|------------------|-----|---------------------------------------------------------------------------------------------------------|

|     |          |                  | -   | •                                                                                                       |

| 14  | PE7MD2   | 0                | R/W | PE7 Mode                                                                                                |

| 13  | PE7MD1   | 0                | R/W | Select the function of the<br>PE7/BS/TIOC2B/UBCTRG/RXD2/SSI pin.                                        |

| 12  | PE7MD0   | 0                | R/W |                                                                                                         |

|     |          |                  |     | 000: PE7 I/O (port)                                                                                     |

|     |          |                  |     | 001: TIOC2B I/O (MTU2)                                                                                  |

|     |          |                  |     | 010: RXD2 input (SCI)                                                                                   |

|     |          |                  |     | 011: BS output (BSC)*                                                                                   |

|     |          |                  |     | 101: SSI I/O (SSU)                                                                                      |

|     |          |                  |     | 111: UBCTRG output (UBC)                                                                                |

|     |          |                  |     | Other than above: Setting prohibited                                                                    |

| 11  |          | 0                | R   | Reserved                                                                                                |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0.                                       |

| 10  | PE6MD2   | 0                | R/W | PE6 Mode                                                                                                |

| 9   | PE6MD1   | 0                | R/W | Select the function of the                                                                              |

| 8   | PE6MD0   | 0                | R/W | PE6/CS7/TIOC2A/SCK3/AUDATA0 pin. Fixed to<br>AUDATA0 output when using the AUD function of the<br>E10A. |

|     |          |                  |     | 000: PE6 I/O (port)                                                                                     |

|     |          |                  |     | 001: TIOC2A I/O (MTU2)                                                                                  |

|     |          |                  |     | 010: SCK3 I/O (SCIF)                                                                                    |

|     |          |                  |     | 101: CS7 output (BSC)*                                                                                  |

|     |          |                  |     | Other than above: Setting prohibited                                                                    |

| 7   |          | 0                | R   | Reserved                                                                                                |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0.                                       |

#### 21.1.12 IRQOUT Function Control Register (IFCR)

IFCR is a 16-bit readable/writable register that is used to control the IRQOUT pin output when it is selected as the multiplexed pin function by port D control register H4 (PDCRH4) and port E control register L4 (PECRL4). When PDCRH4 or PECRL4 selects another function, the IFCR setting does not affect the pin function.

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3          | 2          | 1          | 0          |

|----------------|----|----|----|----|----|----|---|---|---|---|---|---|------------|------------|------------|------------|

|                | -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | IRQ<br>MD3 | IRQ<br>MD2 | IRQ<br>MD1 | IRQ<br>MD0 |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0          | 0          | 0          | 0          |

| R/W:           | R  | R  | R  | R  | R  | R  | R | R | R | R | R | R | R/W        | R/W        | R/W        | R/W        |

|         |          | Initial |     |                                                                                                                              |

|---------|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Bit Name | Value   | R/W | Description                                                                                                                  |

| 15 to 4 | _        | All 0   | R   | Reserved                                                                                                                     |

|         |          |         |     | These bits are always read as 0. The write value should always be 0.                                                         |

| 3       | IRQMD3   | 0       | R/W | Port D IRQOUT Pin Function Select                                                                                            |

| 2       | IRQMD2   | 0       | R/W | Select the IRQOUT pin function when bits 9 and 8 (PD30MD1 and PD30MD0) in PDCRH4 are set to B'10.                            |

|         |          |         |     | 00: Interrupt request accept signal output                                                                                   |

|         |          |         |     | 01: Refresh signal output                                                                                                    |

|         |          |         |     | <ol> <li>10: Interrupt request accept signal output or refresh<br/>signal output (depends on the operating state)</li> </ol> |

|         |          |         |     | 11: Always high-level output                                                                                                 |

| 1       | IRQMD1   | 0       | R/W | Port E IRQOUT Pin Function Select                                                                                            |

| 0       | IRQMD0   | 0       | R/W | Select the IRQOUT pin function when bits 14 to 12 (PE15MD2 to PE15MD0) in PECRL4 are set to B'011.                           |

|         |          |         |     | 00: Interrupt request accept signal output                                                                                   |

|         |          |         |     | 01: Refresh signal output                                                                                                    |

|         |          |         |     | <ol> <li>Interrupt request accept signal output or refresh<br/>signal output (depends on the operating state)</li> </ol>     |

|         |          |         |     | 11: Always high-level output                                                                                                 |

#### 22.6.1 Register Descriptions

Port F is an 8-bit input-only port in the SH7083, SH7084, and SH7085; a 16-bit input-only port in the SH7086. Port F has the following register. For details on register addresses and register states during each processing, refer to section 27, List of Registers.

#### **Table 22.11 Register Configuration**

| Register Name          | Abbrevia-<br>tion | R/W | Initial Value | Address    | Access Size |

|------------------------|-------------------|-----|---------------|------------|-------------|

| Port F data register L | PFDRL             | R   | H'xxxx        | H'FFFFD382 | 8, 16       |

#### 22.6.2 Port F Data Register L (PFDRL)

The port F data register L (PFDRL) is a 16-bit read-only register that stores port F data. Bits PF7DR to PF0DR correspond to pins PF7 to PF0 (multiplexed functions omitted here) in the SH7083, SH7084, and SH7085. Bits PF15DR to PF0DR correspond to pins PF15 to PF0 (multiplexed functions omitted here) in the SH7086.

Any value written into these bits is ignored, and there is no effect on the state of the pins. When any of the bits are read, the pin state rather than the bit value is read directly. However, when an A/D converter analog input is being sampled, values of 1 are read out. Table 22.12 summarizes port F data register L read/write operations.

# 23.7 Flash Memory Emulation in RAM

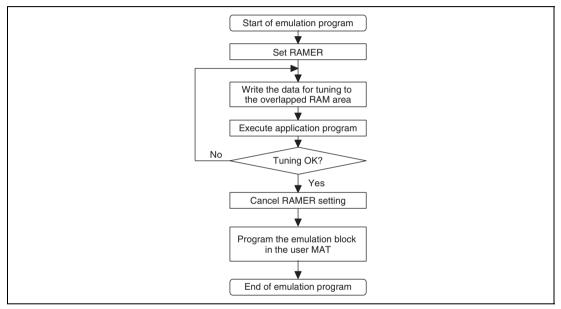

To provide real-time emulation in RAM of data that is to be written to the flash memory, a part of the RAM can be overlaid on an area of flash memory (user MAT) that has been specified by the RAM emulation register (RAMER). After the RAMER setting is made, the RAM is accessible in both the user MAT area and as the RAM area that has been overlaid on the user MAT area. Such emulation is possible in user mode and user program mode.

Figure 23.17 shows an example of the emulation of realtime programming of the user MAT area.

Figure 23.17 Emulation of Flash Memory in RAM

| Register             | Bit        | Bit        | Bit        | Bit        | Bit        | Bit         | Bit       | Bit       |     |

|----------------------|------------|------------|------------|------------|------------|-------------|-----------|-----------|-----|

| Abbreviation         | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2  | 25/17/9/1 | 24/16/8/0 | Mod |

| CS2WCR* <sup>2</sup> | _          | —          |            | —          |            | —           |           | —         | BSC |

|                      | —          | —          | —          | BAS        | _          |             | WW[2:0]   |           |     |

|                      | —          | _          | _          | sw         | [1:0]      |             | WR[3:1]   |           |     |

|                      | WR[0]      | WM         | —          | _          | _          | _           | нм        | /[1:0]    |     |

| CS2WCR∗⁵             | —          | _          | _          | _          | _          | _           | _         | —         |     |

|                      | —          | _          | _          | _          | _          | _           | _         | —         |     |

|                      | —          | _          | —          | _          | _          | _           | _         | A2CL[1]   |     |

|                      | A2CL[0]    | —          | —          | —          | —          | _           | —         | —         |     |

| CS3WCR* <sup>2</sup> | —          | —          | —          | —          | —          | _           | —         | —         |     |

|                      | —          | —          | —          | BAS        | —          |             | WW[2:0]   |           |     |

|                      | _          | _          | _          | sw         | [1:0]      |             | WR[3:1]   |           |     |

|                      | WR[0]      | WM         | _          | _          |            | _           | нм        | /[1:0]    |     |

| CS3WCR∗⁵             | _          | _          | _          | _          | _          | _           | —         | _         |     |

|                      | _          | _          |            | _          |            | _           | _         | _         |     |

|                      | _          | WTR        | P[1:0]     | _          | WTRO       | CD[1:0]     | _         | A3CL[1]   |     |

|                      | A3CL[0]    | _          |            | TRW        | L[1:0]     | — WTRC[1:0] |           | RC[1:0]   |     |

| CS4WCR* <sup>2</sup> | _          | _          | _          | _          |            | _           | _         | _         |     |

|                      | _          | _          |            | BAS        |            |             | WW[2:0]   |           |     |

|                      | _          | _          | _          | sw         | [1:0]      |             | WR[3:1]   |           |     |

|                      | WR[0]      | WM         |            | _          |            | _           | нм        | /[1:0]    | 1   |

| CS4WCR*3             | _          | _          | _          | _          |            | _           |           | _         | 1   |

|                      |            | _          | _          | BEN        | _          | _           | BW        | /[1:0]    | 1   |

|                      |            | _          |            | sw         | [1:0]      |             | W[3:1]    |           | 1   |

|                      | W[0]       | WM         | _          | _          |            | _           | нм        | /[1:0]    | 1   |

| CS5WCR* <sup>2</sup> | _          | _          | _          | _          | _          | _           | _         | _         | 1   |

|                      | _          | _          | _          | BAS        | _          |             | WW[2:0]   |           | 1   |

|                      | _          | _          | _          | SW         | [1:0]      |             | WR[3:1]   |           | 1   |

|                      | WR[0]      | WM         | _          | _          | _          | _           | нм        | /[1:0]    | 1   |

| Item                           | Symbol             | Min.                      | Max.                      | Unit | Reference Figure        |

|--------------------------------|--------------------|---------------------------|---------------------------|------|-------------------------|

| CAS delay time                 | $t_{casd}$         | 1                         | 18                        | ns   | Figures 28.24 to 28.40  |

| DQM delay time                 | t <sub>dqmd</sub>  | 1                         | 18                        | ns   | Figures 28.24 to 28.37  |

| CKE delay time                 | t <sub>cked</sub>  | 1                         | 18                        | ns   | Figure 28.39            |

| AH delay time                  | t <sub>ahd</sub>   | 1/2t <sub>всус</sub> + 1  | 1/2t <sub>всус</sub> + 18 | ns   | Figure 28.18            |

| Multiplexed address delay time | t <sub>MAD</sub>   |                           | 18                        | ns   | Figure 28.18            |

| Multiplexed address hold time  | t <sub>MAH</sub>   | 1                         | _                         | ns   | Figure 28.18            |

| DACK, TEND delay time          | t <sub>dacd</sub>  | 1                         | 18                        | ns   | Figures 28.11 to 28.35  |

| FRAME delay time               | t <sub>FMD</sub>   | 1                         | 18                        | ns   | Figure 28.19 to 28.22   |

| ICIORD delay time              | t <sub>icrsd</sub> | 1/2t <sub>всус</sub> + 1  | 1/2t <sub>Bcyc</sub> + 18 | ns   | Figures 28.43,<br>28.44 |

| ICIOWR delay time              | t <sub>icwsd</sub> | 1/2t <sub>Bcyc</sub> + 1  | 1/2t <sub>Bcyc</sub> + 18 | ns   | Figures 28.43,<br>28.44 |

| IOIS16 setup time              | t <sub>IO16S</sub> | 1/2t <sub>всус</sub> + 13 | _                         | ns   | Figure 28.44            |

| IOIS16 hold time               | t <sub>IO16H</sub> | 1/2t <sub>всус</sub> + 10 |                           | ns   | Figure 28.44            |

Notes:  $t_{B_{CVC}}$  indicates external bus clock period (B $\phi$  = CK).

1. n denotes the number of wait cycles.

2. If the access time conditions are satisfied, the  $t_{\mbox{\tiny RDS1}}$  condition does not need to be satisfied.

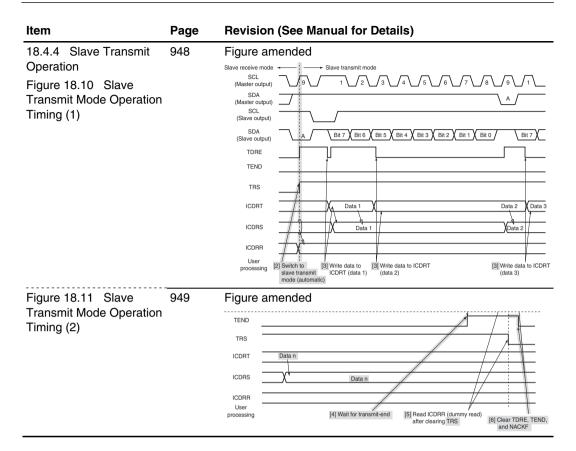

| Item                                                                                                                                                                                                                                                                                                                    | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>11.4.9 A/D Converter<br/>Start Request Delaying<br/>Function</li> <li>(a) Example of<br/>Procedure for Specifying<br/>A/D Converter Start<br/>Request Delaying<br/>Function</li> <li>Figure 11.79 Example of<br/>Procedure for Specifying<br/>A/D Converter Start<br/>Request Delaying<br/>Function</li> </ul> | 602  | <ul> <li>Figure amended</li> <li>AD converter start request delaying function</li> <li>Set A/D converter start request cycle register (TADCOBRA_4 or TADCOBEB_4) and timer A/D converter start request cycle register (TADCORA_4 or TADCOR_4). (TADCORA_4). (The same initial value must be specified in the cycle buffer register and cycle register.</li> <li>Set A/D converter start request cycle</li> <li>Set the timing of transfer from cycle set buffer register</li> <li>Set kinkage with interrupt skipping</li> <li>Enable A/D converter start request for the timer A/D converter start request cycle buffer register to A/D converter start request cycle buffer register to A/D converter start request cycle buffer register.</li> <li>Set linkage with interrupt skipping</li> <li>Farable A/D converter start request delaying function</li> <li>A/D converter start request delaying function</li> <li>Set ITA3AE, ITA4VE, ITB3AE, ITB4VE, DT4AE, or DT4BE bis fo 0 when complementary PWM mode is not selected.</li> <li>Set ITA3AE, ITA4VE, ITB3AE, ITB4VE, DT4AE, or DT4BE bis fo 0 when complementary PWM mode is not selected.</li> <li>Clear the ITA3AE, ITA4VE, ITB3AE, ITB4VE, DT4AE, or DT4BE bits fo 0 when complementary PWM mode is not selected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>(b) Basic Operation</li> <li>Example of A/D</li> <li>Converter Start Request</li> <li>Delaying Function</li> <li>Figure 11.80 Basic</li> <li>Example of A/D</li> <li>Converter Start Request</li> <li>Signal (TRG4AN)</li> <li>Operation</li> </ul>                                                            | 603  | Figure amended<br>Transfer from cycle buffer<br>register to cycle register<br>TADCORA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBRA.4<br>TADCOBR |

| (c) A/D Converter Start<br>Request Enabled Interval                                                                                                                                                                                                                                                                     | -    | Section added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (d) Buffer Transfer                                                                                                                                                                                                                                                                                                     | 604  | Description added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                         |      | When using buffer transfer in complementary PWM mode,<br>exercise care regarding the buffer transfer timing. For details,<br>see 11.7.24, Notes on Using the A/D Converter Start<br>Request Delaying Function in Complementary PWM Mode.<br>Also, clear the BF1 bit to 0 when not in complementary PWM<br>mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

RENESAS