#### Welcome to E-XFL.COM

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

E·XF

| Details                         |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Active                                                      |

| Core Processor                  | PowerPC 603e                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 300MHz                                                      |

| Co-Processors/DSP               | -                                                           |

| RAM Controllers                 | SDRAM                                                       |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | -                                                           |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 3.3V                                                        |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | -                                                           |

| Package / Case                  | 352-LBGA                                                    |

| Supplier Device Package         | 352-TBGA (35x35)                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8245lvv300d |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The peripheral logic integrates a PCI bridge, dual universal asynchronous receiver/transmitter (DUART), memory controller, DMA controller, PIC interrupt controller, a message unit (and  $I_2O$  interface), and an  $I^2C$  controller. The processor core is a full-featured, high-performance processor with floating-point support, memory management, a 16-Kbyte instruction cache, a 16-Kbyte data cache, and power management features. The integration reduces the overall packaging requirements and the number of discrete devices required for an embedded system.

An internal peripheral logic bus interfaces the processor core to the peripheral logic. The core can operate at a variety of frequencies, allowing the designer to trade off performance for power consumption. The processor core is clocked from a separate PLL that is referenced to the peripheral logic PLL. This allows the microprocessor and the peripheral logic block to operate at different frequencies while maintaining a synchronous bus interface. The interface uses a 64- or 32-bit data bus (depending on memory data bus width) and a 32-bit address bus along with control signals that enable the interface between the processor and peripheral logic to be optimized for performance. PCI accesses to the MPC8245 memory space are passed to the processor bus for snooping when snoop mode is enabled.

The general-purpose processor core and peripheral logic serve a variety of embedded applications. The MPC8245 can be used as either a PCI host or PCI agent controller.

# 2 Features

Major features of the MPC8245 are as follows:

- Processor core

- High-performance, superscalar processor core

- Integer unit (IU), floating-point unit (FPU) (software enabled or disabled), load/store unit (LSU), system register unit (SRU), and branch processing unit (BPU)

- 16-Kbyte instruction cache

- 16-Kbyte data cache

- Lockable L1 caches-Entire cache or on a per-way basis up to three of four ways

- Dynamic power management: 60x nap, doze, and sleep modes

- Peripheral logic

- Peripheral logic bus

- Various operating frequencies and bus divider ratios

- 32-bit address bus, 64-bit data bus

- Full memory coherency

- Decoupled address and data buses for pipelining of peripheral logic bus accesses

- Store gathering on peripheral logic bus-to-PCI writes

- Memory interface

- Up to 2 Gbytes of SDRAM memory

- High-bandwidth data bus (32- or 64-bit) to SDRAM

- Programmable timing supporting SDRAM

- One to eight banks of 16-, 64-, 128-, 256-, or 512-Mbit memory devices

| Characteristic                      |                    | Symbol           | Recommended<br>Value | Unit     | Notes     |

|-------------------------------------|--------------------|------------------|----------------------|----------|-----------|

| PLL supply voltage—peripheral logic | AV <sub>DD</sub> 2 | 1.8/1.9/2.0 V ±  | V                    | 4, 7, 12 |           |

|                                     |                    |                  | 2.0/2.1 V ±          | V        | 5, 7, 12  |

| PCI reference                       |                    | LV <sub>DD</sub> | 5.0 ± 5%             | V        | 2, 10, 11 |

|                                     |                    |                  | 3.3 ± 0.3            | V        | 3, 10, 11 |

| Input voltage                       | PCI inputs         | V <sub>in</sub>  | 0 to 3.6 or 5.75     | V        | 2, 3      |

|                                     | All other inputs   |                  | 0 to 3.6             | V        | 6         |

| Die-junction temperature            |                    | Тj               | 0 to 105             | °C       |           |

### Table 2. Recommended Operating Conditions<sup>1</sup> (continued)

### Notes:

- 1. These are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

- 2. PCI pins are designed to withstand LV<sub>DD</sub> + 5% V DC when LV<sub>DD</sub> is connected to a 5.0-V DC power supply.

- 3. PCI pins are designed to withstand LV<sub>DD</sub> + 0.5 V DC when LV<sub>DD</sub> is connected to a 3.3-V DC power supply.

- The voltage supply value of 1.8/1.9/2.0 V ± 100 mV applies to parts marked as having a maximum CPU speed of 266 and 300 MHz. See Table 7. For each chosen nominal value (1.8/1.9/2.0 V) the supply voltage should not exceed ± 100 mV of the nominal value.

- The voltage supply value of 2.0/2.1 V ± 100 m V applies to parts marked as having a maximum CPU speed of 333 and 350 MHz. See Table 7. For each chosen nominal value (2.0/2.1 V) the supply voltage should not exceed ± 100 mV of the nominal value.

### Cautions:

- Input voltage (V<sub>in</sub>) must not be greater than the supply voltage (V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2) by more than 2.5 V at all times, including during power-on reset. Input voltage (V<sub>in</sub>) must not be greater than GV<sub>DD</sub>/OV<sub>DD</sub> by more than 0.6 V at all times, including during power-on reset.

- OV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2 by more than 1.8 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 8. V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2 must not exceed OV<sub>DD</sub> by more than 0.6 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- GV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2 by more than 1.8 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 10.LV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2 by more than 5.4 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 11. LV<sub>DD</sub> must not exceed OV<sub>DD</sub> by more than 3.0 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 12. This voltage is the input to the filter discussed in Section 7.1, "PLL Power Supply Filtering," and not necessarily the voltage at the AV<sub>DD</sub> pin, which may be reduced from V<sub>DD</sub> by the filter.

**Electrical and Thermal Characteristics**

# 4.3 **Power Characteristics**

Table 5 provides power consumption data for the MPC8245.

| Maria                | PCI Bus Clock/Memory Bus Clock/CPU Clock Frequency (MHz) |              |              |              |                                 |     |     |      |         |

|----------------------|----------------------------------------------------------|--------------|--------------|--------------|---------------------------------|-----|-----|------|---------|

| Mode                 | 66/66/266                                                | 66/133/266   | 66/66/300    | 66/100/300   | 33/83/333 66/133/333 66/100/350 |     |     | Unit | Notes   |

| Typical              | 1.7<br>(1.5)                                             | 2.0<br>(1.8) | 1.8<br>(1.7) | 2.0<br>(1.8) | 2.0                             | 2.3 | 2.2 | W    | 1, 5    |

| Max—FP               | 2.2<br>(1.9)                                             | 2.4<br>(2.1) | 2.3<br>(2.0) | 2.5<br>(2.2) | 2.6                             | 2.8 | 2.8 | W    | 1, 2    |

| Max—INT              | 1.8<br>(1.6)                                             | 2.1<br>(1.8) | 2.0<br>(1.8) | 2.1<br>(1.8) | 2.2                             | 2.4 | 2.4 | W    | 1, 3    |

| Doze                 | 1.1<br>(1.0)                                             | 1.4<br>(1.3) | 1.2<br>(1.1) | 1.4<br>(1.3) | 1.4                             | 1.6 | 1.5 | W    | 1, 4, 6 |

| Nap                  | 0.4<br>(0.4)                                             | 0.7<br>(0.7) | 0.4<br>(0.4) | 0.6<br>(0.6) | 0.5                             | 0.7 | 0.6 | W    | 1, 4, 6 |

| Sleep                | 0.2<br>(0.2)                                             | 0.4<br>(0.4) | 0.2<br>(0.4) | 0.3<br>(0.3) | 0.3                             | 0.4 | 0.3 | W    | 1, 4, 6 |

| •••••                |                                                          |              | 1/0          | D Power Supp | olies <sup>10</sup>             |     |     |      |         |

| M                    | ode                                                      |              | Min          |              |                                 | Max |     | Unit | Notes   |

| Typ—OV <sub>DD</sub> | )                                                        |              | 134 (121)    |              | 334 (301)                       |     |     | mW   | 7, 8    |

| Typ—GV <sub>DD</sub> | GV <sub>DD</sub> 324 (292)                               |              |              |              | 800 (720)                       |     | mW  | 7, 9 |         |

### Table 5. Power Consumption

### Notes:

- 1. The values include  $V_{DD}$ ,  $AV_{DD}$ , and  $AV_{DD}^2$  but do not include I/O supply power. Information on  $OV_{DD}$  and  $GV_{DD}$  supply power is captured in the I/O power supplies section of this table. Values shown in parenthesis () indicate power consumption at  $V_{DD}/AV_{DD}/AV_{DD}^2 = 1.8$  V.

- Maximum—FP power is measured at V<sub>DD</sub> = 2.1 V with dynamic power management enabled while running an entirely cache-resident, looping, floating-point multiplication instruction.

- Maximum—INT power is measured at V<sub>DD</sub> = 2.1 V with dynamic power management enabled while running entirely cache-resident, looping, integer instructions.

- 4. Power saving mode maximums are measured at V<sub>DD</sub> = 2.1 V while the device is in doze, nap, or sleep mode.

- Typical power is measured at V<sub>DD</sub> = AV<sub>DD</sub> = 2.0 V, OV<sub>DD</sub> = 3.3 V where a nominal FP value, a nominal INT value, and a value where there is a continuous flush of cache lines with alternating ones and zeros on 64-bit boundaries to local memory are averaged.

- 6. Power saving mode data measured with only two PCI\_CLKs and two SDRAM\_CLKs enabled.

- The typical minimum I/O power values were results of the MPC8245 performing cache resident integer operations at the slowest frequency combination of 33:66:200 (PCI:Mem:CPU) MHz.

- 8. The typical maximum OV<sub>DD</sub> value resulted from the MPC8245 operating at the fastest frequency combination of 66:100:350 (PCI:Mem:CPU) MHz and performing continuous flushes of cache lines with alternating ones and zeros to PCI memory.

- The typical maximum GV<sub>DD</sub> value resulted from the MPC8245 operating at the fastest frequency combination of 66:100:350 (PCI:Mem:CPU) MHz and performing continuous flushes of cache lines with alternating ones and zeros on 64-bit boundaries to local memory.

- 10. Power consumption of PLL supply pins (AV<sub>DD</sub> and AV<sub>DD</sub>2) < 15 mW. Guaranteed by design and not tested.

### Table 8. Clock AC Timing Specifications (continued)

At recommended operating conditions (see Table 2) with  $LV_{DD}$  = 3.3 V ± 0.3 V

| Num | Characteristics and Conditions      | Min                            | Мах | Unit | Notes |

|-----|-------------------------------------|--------------------------------|-----|------|-------|

| 16  | DLL lock range for other modes      | See Figure 8 through Figure 10 |     | ns   | 6     |

| 17  | Frequency of operation (OSC_IN)     | 25                             | 66  | MHz  |       |

| 19  | OSC_IN rise and fall times          | _                              | 5   | ns   | 7     |

| 20  | OSC_IN duty cycle measured at 1.4 V | 40                             | 60  | %    |       |

| 21  | OSC_IN frequency stability          | —                              | 100 | ppm  |       |

Notes:

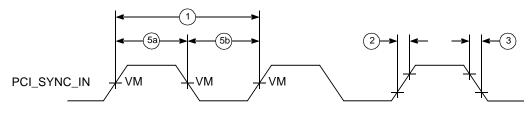

- 1. Rise and fall times for the PCI\_SYNC\_IN input are measured from 0.4 to 2.4 V.

- 2. Specification value at maximum frequency of operation.

- 3. Pin-to-pin skew includes quantifying the additional amount of clock skew (or jitter) from the DLL besides any intentional skew added to the clocking signals from the variable length DLL synchronization feedback loop, that is, the amount of variance between the internal *sys\_logic\_clk* and the SDRAM\_SYNC\_IN signal after the DLL is locked. While pin-to-pin skew between SDRAM\_CLKs can be measured, the relationship between the internal *sys\_logic\_clk* and the external SDRAM\_SYNC\_IN cannot be measured and is guaranteed by design.

- 4. Relock time is guaranteed by design and characterization. Relock time is not tested.

- 5. Relock timing is guaranteed by design. PLL-relock time is the maximum amount of time required for PLL lock after a stable V<sub>DD</sub> and PCI\_SYNC\_IN are reached during the reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep mode. Also note that HRST\_CPU/HRST\_CTRL must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the reset sequence.

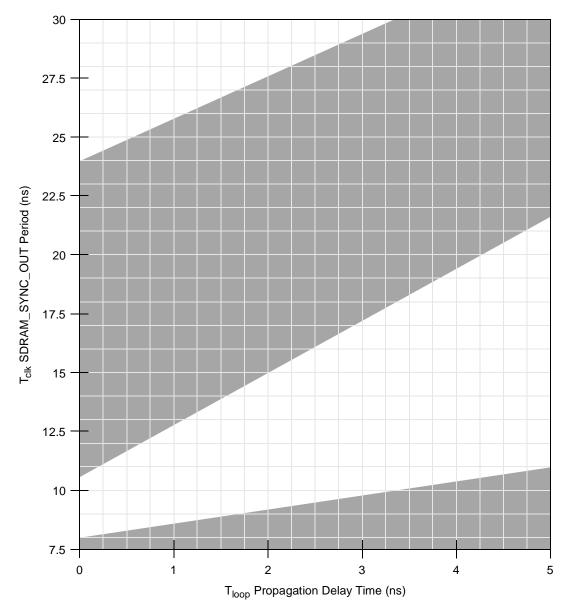

- 6. DLL\_EXTEND is bit 7 of the PMC2 register <72>. N is a non-zero integer (see Figure 7 through Figure 10). T<sub>clk</sub> is the period of one SDRAM\_SYNC\_OUT clock cycle in ns. T<sub>loop</sub> is the propagation delay of the DLL synchronization feedback loop (PC board runner) from SDRAM\_SYNC\_OUT to SDRAM\_SYNC\_IN in ns; 6.25 inches of loop length (unloaded PC board runner) corresponds to approximately 1 ns of delay. For details about how Figure 7 through Figure 10 may be used refer to the Freescale application note AN2164, MPC8245/MPC8241 Memory Clock Design Guidelines, for details on MPC8245 memory clock design.

- 7. Rise and fall times for the OSC\_IN input is guaranteed by design and characterization. OSC\_IN input rise and fall times are not tested.

Figure 6 shows the PCI\_SYNC\_IN input clock timing diagram with the labeled number items listed in Table 8.

VM = Midpoint Voltage (1.4 V)

Figure 6. PCI\_SYNC\_IN Input Clock Timing Diagram

Figure 7 through Figure 10 show the DLL locking range loop delay vs. frequency of operation. These graphs define the areas of DLL locking for various modes. The gray areas show where the DLL locks.

**Electrical and Thermal Characteristics**

Figure 8. DLL Locking Range Loop Delay Versus Frequency of Operation for DLL\_Extend=1 and Normal Tap Delay

### Table 13. I<sup>2</sup>C AC Electrical Specifications (continued)

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 12).

| Parameter                                                                       | Symbol <sup>1</sup> | Min                                | Max | Unit |

|---------------------------------------------------------------------------------|---------------------|------------------------------------|-----|------|

| Noise margin at the HIGH level for each connected device (including hysteresis) | V <sub>NH</sub>     | $0.2 \times \text{OV}_{\text{DD}}$ | _   | V    |

### Note:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>I2DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>I2SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the t<sub>I2C</sub> clock reference (K) going to the stop condition (P) reaching the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 2. As a transmitter, the MPC8245 provides a delay time of at least 300 ns for the SDA signal (referred to as the Vihmin of the SCL signal) to bridge the undefined region of the falling edge of SCL to avoid unintended generation of Start or Stop condition. When the MPC8245acts as the I<sup>2</sup>C bus master while transmitting, it drives both SCL and SDA. As long as the load on SCL and SDA is balanced, the MPC8245 does not cause the unintended generation of a Start or Stop condition. Therefore, the 300 ns SDA output delay time is not a concern. If, under some rare condition, the 300 ns SDA output delay time is required for the MPC8245 as transmitter, the following setting is recommended for the FDR bit field of the I2CFDR register to ensure both the desired I<sup>2</sup>C SCL clock frequency and SDA output delay time are achieved. It is assumed that the desired I<sup>2</sup>C SCL clock frequency is 400 KHz and the digital filter sampling rate register (DFFSR bits in I2CFDR) is programmed with its default setting of 0x10 (decimal 16):

| SDRAM Clock Frequency       | 100 MHz     | 133 MHz     |

|-----------------------------|-------------|-------------|

| FDR Bit Setting             | 0x00        | 0x2A        |

| Actual FDR Divider Selected | 384         | 896         |

|                             | 000 4 1/11- | 4 40 4 1/11 |

Actual I<sup>2</sup>C SCL Frequency Generated 260.4 KHz 148.4 KHz

For details on I<sup>2</sup>C frequency calculation, refer to the application note AN2919 "Determining the I<sup>2</sup>C Frequency Divider Ratio for SCL".

- 3. The maximum t<sub>I2DXKL</sub> has only to be met if the device does not stretch the LOW period (t<sub>I2CL</sub>) of the SCL signal.

- 4. Guaranteed by design.

Figure 16 provides the AC test load for the  $I^2C$ .

Figure 16. I<sup>2</sup>C AC Test Load

#### Electrical and Thermal Characteristics

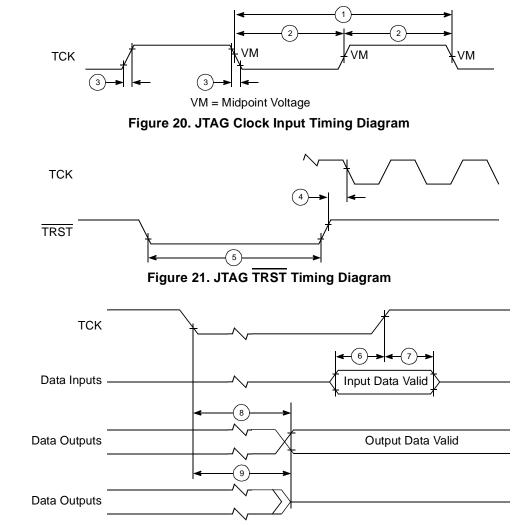

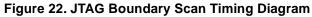

| Num | Characteristic            | Min | Мах | Unit | Notes |

|-----|---------------------------|-----|-----|------|-------|

| 11  | TMS, TDI data hold time   | 15  | -   | ns   |       |

| 12  | TCK to TDO data valid     | 0   | 15  | ns   |       |

| 13  | TCK to TDO high impedance | 0   | 15  | ns   |       |

Table 15. JTAG AC Timing Specification (Independent of PCI\_SYNC\_IN) (continued)

### Notes:

1. TRST is an asynchronous signal. The setup time is for test purposes only.

2. Nontest (other than TDI and TMS) signal input timing with respect to TCK.

3. Nontest (other than TDO) signal output timing with respect to TCK.

Figure 20 through Figure 23 show the different timing diagrams.

Figure 23. Test Access Port Timing Diagram

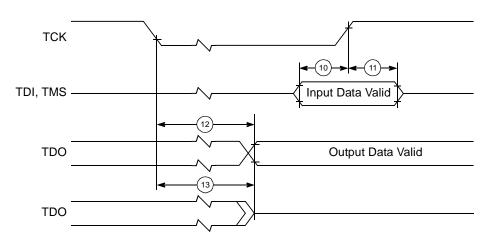

# 5 Package Description

This section details package parameters, pin assignments, and dimensions.

## 5.1 Package Parameters

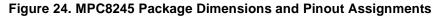

The MPC8245 uses a 35 mm  $\times$  35 mm, cavity-up, 352-pin tape ball grid array (TBGA) package. The package parameters are as follows.

| Package Outline                   | $35 \text{ mm} \times 35 \text{ mm}$                                                          |

|-----------------------------------|-----------------------------------------------------------------------------------------------|

| Interconnects                     | 352                                                                                           |

| Pitch                             | 1.27 mm                                                                                       |

| Solder Balls                      | ZU (TBGA package)—62 Sn/36 Pb/2 Ag<br>VV (Lead-free version of package)—95.5 Sn/4.0 Ag/0.5 Cu |

| Solder Ball Diameter              | 0.75 mm                                                                                       |

| Maximum Module Height             | 1.65 mm                                                                                       |

| <b>Co-Planarity Specification</b> | 0.15 mm                                                                                       |

| Maximum Force                     | 6.0 lbs. total, uniformly distributed over package (8 grams/ball)                             |

Package Description

## 5.2 Pin Assignments and Package Dimensions

Figure 24 shows the top surface, side profile, and pinout of the MPC8245, 352 TBGA package.

2. All measurements are in millimeters (mm).

# 5.3 **Pinout Listings**

Table 16 provides the pinout listing for the MPC8245, 352 TBGA package.

### Table 16. MPC8245 Pinout Listing

| Name      | Pin Numbers                                                                                                                                 | Туре             | Power<br>Supply  | Output<br>Driver Type | Notes      |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------------|------------|

|           | PCI Int                                                                                                                                     | erface Signals   |                  |                       |            |

| C/BE[3:0] | P25 K23 F23 A25                                                                                                                             | I/O              | OV <sub>DD</sub> | DRV_PCI               | 6, 15      |

| DEVSEL    | H26                                                                                                                                         | I/O              | OV <sub>DD</sub> | DRV_PCI               | 8, 15      |

| FRAME     | J24                                                                                                                                         | I/O              | OV <sub>DD</sub> | DRV_PCI               | 8, 15      |

| IRDY      | K25                                                                                                                                         | I/O              | OV <sub>DD</sub> | DRV_PCI               | 8, 15      |

| LOCK      | J26                                                                                                                                         | Input            | OV <sub>DD</sub> |                       | 8          |

| AD[31:0]  | V25 U25 U26 U24 U23 T25 T26<br>R25 R26 N26 N25 N23 M26 M25<br>L25 L26 F24 E26 E25 E23 D26<br>D25 C26 A26 B26 A24 B24 D19<br>B23 B22 D22 C22 | I/O              | OV <sub>DD</sub> | DRV_PCI               | 6, 15      |

| PAR       | G25                                                                                                                                         | I/O              | OV <sub>DD</sub> | DRV_PCI               | 15         |

| GNT[3:0]  | W25 W24 W23 V26                                                                                                                             | Output           | OV <sub>DD</sub> | DRV_PCI               | 6, 15      |

| GNT4/DA5  | W26                                                                                                                                         | Output           | OV <sub>DD</sub> | DRV_PCI               | 7, 15, 14  |

| REQ[3:0]  | Y25 AA26 AA25 AB26                                                                                                                          | Input            | OV <sub>DD</sub> | _                     | 6, 12      |

| REQ4/DA4  | Y26                                                                                                                                         | I/O              | OV <sub>DD</sub> |                       | 12, 14     |

| PERR      | G26                                                                                                                                         | I/O              | OV <sub>DD</sub> | DRV_PCI               | 8, 15, 18  |

| SERR      | F26                                                                                                                                         | I/O              | OV <sub>DD</sub> | DRV_PCI               | 8, 15, 16  |

| STOP      | H25                                                                                                                                         | I/O              | OV <sub>DD</sub> | DRV_PCI               | 8, 15      |

| TRDY      | K26                                                                                                                                         | I/O              | OV <sub>DD</sub> | DRV_PCI               | 8, 15      |

| INTA      | AC26                                                                                                                                        | Output           | OV <sub>DD</sub> | DRV_PCI               | 10, 15, 16 |

| IDSEL     | P26                                                                                                                                         | Input            | OV <sub>DD</sub> | _                     |            |

|           | Memory                                                                                                                                      | Interface Signal | s                |                       | •          |

| MDL[0:31] | AD17 AE17 AE15 AF15 AC14<br>AE13 AF13 AF12 AF11 AF10 AF9<br>AD8 AF8 AF7 AF6 AE5 B1 A1 A3<br>A4 A5 A6 A7 D7 A8 B8 A10 D10<br>A12 B11 B12 A14 | I/O              | GV <sub>DD</sub> | DRV_STD_MEM           | 5, 6       |

| MDH[0:31] | AC17 AF16 AE16 AE14 AF14<br>AC13 AE12 AE11 AE10 AE9 AE8<br>AC7 AE7 AE6 AF5 AC5 E4 A2 B3<br>D4 B4 B5 D6 C6 B7 C9 A9 B10<br>A11 A13 B13 A15   | I/O              | GV <sub>DD</sub> | DRV_STD_MEM           | 6          |

| Name                      | Pin Numbers                                                                         | Туре                                                              | Power<br>Supply     | Output<br>Driver Type | Notes     |

|---------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------|-----------------------|-----------|

| V <sub>DD</sub>           | AA24 AC16 AC19 AD12 AD6 AD9<br>C15 C18 C21 D11 D8 F3 H23 J3<br>L23 M3 R24 T4 V24 W4 | Power for core<br>1.8/2.0 V                                       | V <sub>DD</sub>     | _                     | 22        |

| No Connect                | D17                                                                                 | —                                                                 | _                   | _                     | 23        |

| AV <sub>DD</sub>          | C17                                                                                 | 7 Power for PLL AV <sub>DD</sub><br>(CPU core logic)<br>1.8/2.0 V |                     | _                     | 22        |

| AV <sub>DD</sub> 2        | AF24                                                                                | Power for PLL<br>(peripheral<br>logic)<br>1.8/2.0 V               | AV <sub>DD</sub> 2  |                       | 22        |

|                           | Debug/M                                                                             | anufacturing Pins                                                 | 6                   |                       |           |

| DA0/QACK                  | F2                                                                                  | Output                                                            | $OV_{DD}$           | DRV_STD_MEM           | 4, 10, 25 |

| DA1/CKO                   | B15                                                                                 | Output                                                            | OV <sub>DD</sub>    | DRV_STD_MEM           | 14        |

| DA2                       | C25                                                                                 | Output                                                            | $OV_{DD}$           | DRV_PCI               | 2         |

| DA3/PCI_CLK4              | AF26                                                                                | Output                                                            | ${\rm GV}_{\rm DD}$ | DRV_PCI_CLK           | 14        |

| DA4/REQ4                  | Y26                                                                                 | I/O                                                               | $OV_{DD}$           | _                     | 12, 14    |

| DA5/GNT4                  | W26                                                                                 | Output                                                            | $OV_{DD}$           | DRV_PCI               | 7, 15, 14 |

| DA[10:6]/<br>PLL_CFG[0:4] | A22 B19 A21 B18 B17                                                                 | I/O                                                               | OV <sub>DD</sub>    | DRV_STD_MEM           | 6, 14, 20 |

| DA[11]                    | AD26                                                                                | Output                                                            | $OV_{DD}$           | DRV_PCI               | 2         |

| DA[12:13]                 | AF17 AF19                                                                           | Output                                                            | OV <sub>DD</sub>    | DRV_STD_MEM           | 2, 6      |

| Table 16. | MPC8245 | Pinout | Listing ( | (continued) |

|-----------|---------|--------|-----------|-------------|

|-----------|---------|--------|-----------|-------------|

**PLL Configurations**

|                |                                   | 266-MHz Part <sup>9</sup>                                              |                                                       |                                | 3                                                                      | 300-MHz Part <sup>9</sup>                             |                                |                                | Multipliers                    |  |

|----------------|-----------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|--|

| Ref. No. [0:4] | PLL_CFG<br>[0:4] <sup>10,13</sup> | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/<br>MemBus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/<br>MemBus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI-to-<br>Mem<br>(Mem<br>VCO) | Mem-to-<br>CPU<br>(CPU<br>VCO) |  |

| 13             | 10011 <sup>12</sup>               |                                                                        | Not available                                         |                                | 25 <sup>2,7</sup>                                                      | 100                                                   | 300                            | 4 (2)                          | 3 (2)                          |  |

| 14             | 10100 <sup>12</sup>               | 26 <sup>6</sup> –38 <sup>5</sup>                                       | 52–76                                                 | 182–266                        | 26 <sup>6</sup> -42 <sup>5</sup>                                       | 52–84                                                 | 182–294                        | 2 (4)                          | 3.5 (2)                        |  |

| 15             | 10101 <sup>12</sup>               | Not available                                                          |                                                       |                                | 27 <sup>3</sup> -30 <sup>5,7</sup>                                     | 68–75                                                 | 272–300                        | 2.5 (2)                        | 4 (2)                          |  |

| 16             | 10110 <sup>12</sup>               | 25–33 <sup>5</sup>                                                     | 50–66                                                 | 200–264                        | 25–37 <sup>5</sup>                                                     | 50–74                                                 | 200–296                        | 2 (4)                          | 4 (2)                          |  |

| 17             | 10111 <sup>12</sup>               | 25–33 <sup>5</sup>                                                     | 100–132                                               | 200–264                        | 25–33 <sup>2</sup>                                                     | 100–132                                               | 200–264                        | 4 (2)                          | 2 (2)                          |  |

| 18             | 11000 <sup>12</sup>               | 27 <sup>3</sup> –35 <sup>5</sup>                                       | 68–88                                                 | 204–264                        | 27 <sup>3</sup> -40 <sup>5,7</sup>                                     | 68–100                                                | 204–300                        | 2.5 (2)                        | 3 (2)                          |  |

| 19             | 11001 <sup>12</sup>               | 36 <sup>6</sup> –53 <sup>5</sup>                                       | 72–106                                                | 180–265                        | 36 <sup>6</sup> –59 <sup>2</sup>                                       | 72–118                                                | 180–295                        | 2 (2)                          | 2.5 (2)                        |  |

| 1A             | 11010 <sup>12</sup>               | 50 <sup>18</sup> –66 <sup>1</sup>                                      | 50–66                                                 | 200–264                        | 50 <sup>18</sup> –66 <sup>1</sup>                                      | 50–66                                                 | 200–264                        | 1 (4)                          | 4 (2)                          |  |

| 1B             | 11011 <sup>12</sup>               | 34 <sup>3</sup> –44 <sup>5</sup>                                       | 68–88                                                 | 204–264                        | 34 <sup>3</sup> -50 <sup>5,7</sup>                                     | 68–100                                                | 204–300                        | 2 (2)                          | 3 (2)                          |  |

| 1C             | 11100 <sup>12</sup>               | 44 <sup>3</sup> –59 <sup>5</sup>                                       | 66–88                                                 | 198–264                        | 44 <sup>3</sup> –66 <sup>1</sup>                                       | 66–99                                                 | 198–297                        | 1.5 (2)                        | 3 (2)                          |  |

| 1D             | 11101 <sup>12</sup>               | 48 <sup>6</sup> –66 <sup>1</sup>                                       | 72–99                                                 | 180–248                        | 48 <sup>6</sup> –66 <sup>1</sup>                                       | 72–99                                                 | 180–248                        | 1.5 (2)                        | 2.5 (2)                        |  |

| 1E<br>Rev B    | 11110 <sup>8</sup>                |                                                                        | Not usable                                            |                                |                                                                        | Not usable                                            |                                | Off                            | Off                            |  |

| 1E<br>Rev D    | 11110                             | 33 <sup>3</sup> –38 <sup>5</sup>                                       | 66–76                                                 | 231–266                        | 33 <sup>3</sup> –42 <sup>5</sup>                                       | 66–84                                                 | 231–294                        | 2(2)                           | 3.5(2)                         |  |

Table 17. PLL Configurations (266- and 300-MHz Parts) (continued)

| Table 17. PLL Configurations | (266- and 300-MHz Parts) | (continued) |

|------------------------------|--------------------------|-------------|

|------------------------------|--------------------------|-------------|

|          |                                   | 266-MHz Part <sup>9</sup> 300-MHz Part <sup>9</sup>                    |                                                       |                                |                                                                        | 9                                                     | Multipliers                    |                                |                                |

|----------|-----------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Ref. No. | PLL_CFG<br>[0:4] <sup>10,13</sup> | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/<br>MemBus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/<br>MemBus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI-to-<br>Mem<br>(Mem<br>VCO) | Mem-to-<br>CPU<br>(CPU<br>VCO) |

| 1F       | 11111 <sup>8</sup>                | Not usable                                                             |                                                       | Not usable                     |                                                                        |                                                       | Off                            | Off                            |                                |

Notes:

- 1. Limited by the maximum PCI input frequency (66 MHz).

- 2 Limited by the maximum system memory interface operating frequency (100 MHz @ 300 MHz CPU).

- 3. Limited by the minimum memory VCO frequency (133 MHz).

- 4. Limited due to the maximum memory VCO frequency (372 MHz).

- 5. Limited by the maximum CPU operating frequency.

- 6. Limited by the minimum CPU VCO frequency (360 MHz).

- 7. Limited by the maximum CPU VCO frequency (maximum marked CPU speed X 2).

- 8. In clock-off mode, no clocking occurs inside the MPC8245, regardless of the PCI\_SYNC\_IN input.

- 9. Range values are rounded down to the nearest whole number (decimal place accuracy removed).

- 10. PLL\_CFG[0:4] settings not listed are reserved.

- 11. Multiplier ratios for this PLL\_CFG[0:4] setting differ from the MPC8240 and are not backward-compatible.

- 12. PCI\_SYNC\_IN range for this PLL\_CFG[0:4] setting differs from or does not exist on the MPC8240 and may not be fully backward-compatible.

- 13. Bits 7–4 of register offset <0xE2> contain the PLL\_CFG[0:4] setting value.

- 14. In PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal processor directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI:Mem) mode operation. This mode is for hardware modeling. The AC timing specifications in this document do not apply in PLL bypass mode.

- 15. In dual PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal peripheral logic directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI\_SYNC\_IN:Mem) mode operation. In this mode, the OSC\_IN input signal clocks the internal processor directly in 1:1 (OSC\_IN:CPU) mode operation, and the processor PLL is disabled. The PCI\_SYNC\_IN and OSC\_IN input clocks must be externally synchronized. This mode is for hardware modeling. The AC timing specifications in this document do not apply in dual PLL bypass mode.

- 16. Limited by the maximum system memory interface operating frequency (133 MHz @ 266 MHz CPU).

- 17. Limited by the minimum CPU operating frequency (100 MHz).

- 18. Limited by the minimum memory bus frequency (50 MHz).

|     |                                   | 333 MHz Part <sup>9</sup>                                              |                                                    |                                | 350 MHz Part <sup>9</sup>                                              |                                                    |                                | Multip                         | oliers                         |

|-----|-----------------------------------|------------------------------------------------------------------------|----------------------------------------------------|--------------------------------|------------------------------------------------------------------------|----------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Ref | PLL_<br>CFG[0:4] <sup>10,13</sup> | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/Mem<br>Bus Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph<br>Logic/Mem<br>Bus Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI-to-<br>Mem<br>(Mem<br>VCO) | Mem-to-<br>CPU<br>(CPU<br>VCO) |

| 0   | 00000 <sup>12</sup>               | 25–44 <sup>16</sup>                                                    | 75–132                                             | 188–330                        | 25–44 <sup>16</sup>                                                    | 75–132                                             | 188–330                        | 3 (2)                          | 2.5 (2)                        |

| 1   | 00001 <sup>12</sup>               | 25–37 <sup>5,7</sup>                                                   | 75–111                                             | 225–333                        | 25–38 <sup>5</sup>                                                     | 75–114                                             | 225–342                        | 3 (2)                          | 3 (2)                          |

### Table 18. PLL Configurations (333- and 350-MHz Parts)

### System Design

reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 26 allows the COP port to independently assert HRESET or TRST, while ensuring that the target can drive HRESET as well. If the JTAG interface and COP header will not be used, TRST should be tied to HRESET through a 0- $\Omega$  isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during power-on. Although Freescale recommends that the COP header be designed into the system as shown in Figure 26, if this is not possible, the isolation resistor will allow future access to TRST in the case where a JTAG interface may need to be wired onto the system in debug situations.

The COP interface has a standard header for connection to the target system based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). Typically, pin 14 is removed as a connector key.

There is no standardized way to number the COP header shown in Figure 26. Consequently, different emulator vendors number the pins differently. Some pins are numbered top-to-bottom and left-to-right while others use left-to-right then top-to-bottom and still others number the pins counter clockwise from pin 1 (as with an IC). Regardless of the numbering, the signal placement recommended in Figure 26 is common to all known emulators.

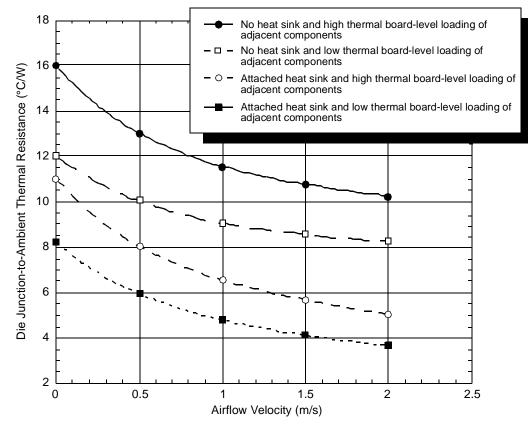

Figure 28. Die Junction-to-Ambient Resistance

The board designer can choose between several types of heat sinks to place on the MPC8245. Several commercially-available heat sinks for the MPC8245 are provided by the following vendors:

Aavid Thermalloy 603-224-9988 80 Commercial St. Concord, NH 03301 Internet: www.aavidthermalloy.com Alpha Novatech 408-749-7601 473 Sapena Ct. #15 Santa Clara, CA 95054 Internet: www.alphanovatech.com International Electronic Research Corporation (IERC) 818-842-7277 413 North Moss St. Burbank, CA 91502 Internet: www.ctscorp.com Tyco Electronics 800-522-6752 Chip Coolers<sup>TM</sup> P.O. Box 3668 Harrisburg, PA 17105-3668 Internet: www.chipcoolers.com

### 7.8.2 Adhesives and Thermal Interface Materials

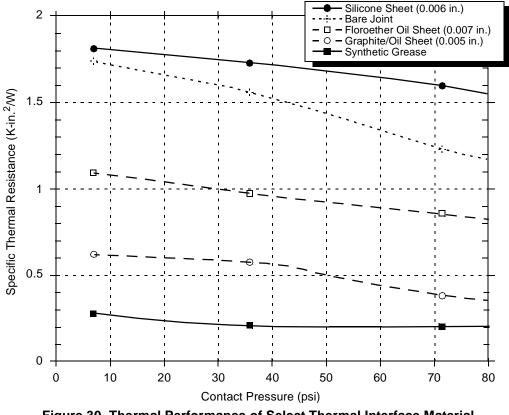

A thermal interface material placed between the top of the package and the bottom of the heat sink minimizes thermal contact resistance. For applications that attach the heat sink by a spring clip mechanism, Figure 30 shows the thermal performance of three thin-sheet thermal-interface materials (silicone, graphite/oil, floroether oil), a bare joint, and a joint with thermal grease as a function of contact pressure. As shown, the performance of these thermal interface materials improves with increasing contact pressure. Thermal grease significantly reduces the interface thermal resistance. That is, the bare joint offers a thermal resistance approximately seven times greater than the thermal grease joint.

A spring clip attaches heat sinks to holes in the printed-circuit board (see Figure 30). Therefore, synthetic grease offers the best thermal performance, considering the low interface pressure. The selection of any thermal interface material depends on factors such as thermal performance requirements, manufacturability, service temperature, dielectric properties, and cost.

Figure 30. Thermal Performance of Select Thermal Interface Material

The board designer can choose between several types of thermal interfaces. Heat sink adhesive materials are selected on the basis of high conductivity and adequate mechanical strength to meet equipment shock/vibration requirements. Several commercially-available thermal interfaces and adhesive materials are provided by the following vendors:

Chomerics, Inc. 77 Dragon Ct. Woburn, MA 01888-4014 Internet: www.chomerics.com

781-935-4850

System Design

| Dow-Corning Corporation<br>Dow-Corning Electronic Materials<br>2200 W. Salzburg Rd.<br>Midland, MI 48686-0997<br>Internet: www.dow.com | 800-248-2481 |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                                         | 888-642-7674 |

| The Bergquist Company<br>18930 West 78 <sup>th</sup> St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com                 | 800-347-4572 |

| Thermagon Inc.<br>4707 Detroit Ave.<br>Cleveland, OH 44102<br>Internet: www.thermagon.com                                              | 888-246-9050 |

### 7.8.3 Heat Sink Usage

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from the equation:

$T_J = T_A + (R_{\theta JA} \times P_D)$

where

$T_A$  = ambient temperature for the package (°C)  $R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)  $P_D$  = power dissipation in the package (W)

The junction-to-ambient thermal resistance is an industry-standard value that provides a quick and easy estimation of thermal performance. Unfortunately, two values are in common usage: the value determined on a single-layer board and the value obtained on a board with two planes. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single-layer board is appropriate for the tightly packed printed-circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where

$$\begin{split} R_{\theta JA} &= \text{junction-to-ambient thermal resistance (°C/W)} \\ R_{\theta JC} &= \text{junction-to-case thermal resistance (°C/W)} \\ R_{\theta CA} &= \text{case-to-ambient thermal resistance (°C/W)} \end{split}$$

Document Revision History

# 8 Document Revision History

Table 19 provides a revision history for this hardware specification.

| Table | 19. Re | vision | History | Table |

|-------|--------|--------|---------|-------|

| IUNIO |        | 101011 |         | Iabio |

| Revision | Date       | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 10       | 8/07       | Section 3, Table 3, and Table 7—Changed format of recommended voltage supply values so that delta to the chosen nominal does not exceed $\pm$ 100 mV.<br>Completely replaced Section 4.6 with compliant I <sup>2</sup> C specifications as with other related integrated processor devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 9        | 12/27/05   | Document—Added Power Architecture information.<br>Section 4.1—Changed increased absolute maximum range for V <sub>DD</sub> in Table 1. Updated format of nominal voltage listings in Table 2.<br>Section 9.2—Removed Note 3 from Table 21.<br>Updated back page information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 8        | 11/15/2005 | Document—Imported new template and made minor editorial changes.<br>Removed references to a 466 MHz part since it is not available for new orders.<br>Section 4.3.2—Added paragraph for using DLL mode that provides lowest locked tap point read in 0xE3.<br>Section 5.3—Updated the driver and I/O assignment information for the multiplexed PCI clock and DUART signals. Added note for HRST_CPU and HRST_CTRL, which had been mentioned only in Figure 2.<br>Section 9.2—Updated the part ordering specifications for the extended temperature parts. Also updated the section to reflect what we offer for new orders.<br>Section 9.3—Added new section, "Part Marking." Updated Figure 33 to match with current part marking format. |  |  |  |  |  |  |

| 7        | 10/07/2004 | Section 4.1.2—Table 2: Corrected range of AV <sub>DD</sub> and AVDD <sub>2</sub> .<br>Section 9.1—Table 21: Corrected voltage range under Process Descriptor column. Minor reformatting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 6.1      | 05/24/2004 | Section 4.5.3—Table 11: Spec 12b was improved from 4.5 ns to 4.0 ns. This improvement is guaranteed on devices marked after work week (WW) 28 of 2004. A device's work week may be determined from the "YYWW" portion of the devices trace ability code which is marked on the top of the device. So for WW28 in 2004, the device's YYWW is marked as 0428. For more information refer to Figure 33                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 6        | 05/11/2004 | Section 4.1.2—Table 2: Corrected range of $GV_{DD}$ to 3.3 ± 5%.<br>Section 4.2.1—Table 4: Changed the default for drive strength of DRV_STD_MEM.<br>Section 4.5.1—Table 8: Changed the wording description for item 15.<br>Section 4.5.2—Table 10: Changed T <sub>os</sub> range and wording in note; Figure 11:changed wording for SDRAM_SYNC_IN description relative to T <sub>OS</sub> .<br>Section 4.5.3—Table 11: Changed timing specification for <i>sys_logic_clk</i> to output valid (memory control, address, and data signals).                                                                                                                                                                                                  |  |  |  |  |  |  |

| 5.1      | _          | Section 4.3.1—Table 9: Corrected last row to state the correct description for the bit setting. Max tap delay, DLL extend. Figure 8: Corrected the label name for the DLL graph to state "DLL Locking Range Loop Delay vs. Frequency of Operation for DLL_Extend=1 and Normal Tap Delay"                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

### Table 19. Revision History Table (continued)

| Revision | Date | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5        | _    | Section 4.1.2 — Added note 6 and related label for latching of the PLL_CFG signals.<br>Section 4.1.3 — Updated specifications for the input high and input low voltages of PCI_SYNC_IN.<br>Section 4.3 — Table 7, updated specifications for the voltage range of V <sub>DD</sub> for specific CPU frequencies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |      | Section 4.3.1 — Table 8: Corrected typo for first number 1a to 1; Updated characteristics for the DLL lock range for the default and remaining three DLL locking modes; Reworded note description for note 6. Replaced contents of Table 9 with bit descriptions for the four DLL locking modes. In Figures 7 through 10, updated the DLL locking mode graphs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |      | Section 4.3.2 — Table 10: Changed the name of references for timing parameters from SDRAM_SYNC_IN to <i>sys_logic_clk</i> to be consistent with Figure 11. Followed the same change for note 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |      | Section 4.3.3— Table 11: Changed the name of references for timing parameters from SDRAM_SYNC_IN to <i>sys_logic_clk</i> to be consistent with Figure 11. Followed the same change for note 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |      | Section 5.3 — Table 17: Removed extra listing of DRDY in Test/Configuration signal list and updated relevant notes for signal in Memory Interface signal listing. Updated note #20. Added note 26 for the signals of the UART interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |      | Section 7.6 — Added reference to AN2128 application note that highlights the differences between the MPC8240 and the MPC8245.<br>Section 7.7 — Added relevant notes to this section and updated Figure 29.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4        | _    | Section 1.4.1.2—Updated notes for GV <sub>DD</sub> , AV <sub>DD</sub> , AV <sub>DD2</sub> .<br>Section 1.5.1—Updated solder ball information to include lead-free (V V) balls.<br>Section 1.5.3—Updated Note 25 for QACK/DA0 signal. Added a sentence to Note 3.<br>Section 1.6 —Incorporated Note 19 into Note 12 and modified Tables 18 and 19 accordingly.<br>Section 1.9—Updated part marking nomenclature where appropriate to include the lead-free offering.<br>Replaced reference to PNS document MPC8245RZUPNS with MPC8245ARZUPNS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3        |      | Section 1.4.1.2—Figure 2: Updated Note 2 and removed 'voltage regulator delay' label since Section 1.7.2 is being deleted this revision. Added Figures 4 and 5 to show voltage overshoot and undershoot of the PCI interface on the MPC8245.<br>Section 1.4.1.3—Table 3: Updated the maximum input capacitance from 7 to 16 pF based on characterization data.<br>Section 1.4.3.1—Updated PCI_SYNC_IN jitter specifications to 200 ps.<br>Section 1.4.3.3—Table 11, item 12b: added the word 'address' to help clarify which signals the spec applies to. Figure 15: edited timing for items 12a0 and 12a2 to correspond with Table 11.<br>Section 1.5.3—Updated notes for the QACK/DA0 signal because this signal has been found to have no internal pull resistor.<br>Section 1.6—Corrected note numbers for reference numbers 3,10,1B, and 1C of the PLL tables.<br>Updated PLL specifications for modes 7 and 1E.<br>Section 1.7.2—Removed this section since the information already exists in Section 1.4.1.5.<br>Section 1.7.4—Added the words 'the clamping voltage' to describe LV <sub>DD</sub> in the sixth paragraph.<br>Changed the QACK/DA0 signal from the list of signals having an internal pull-up resistor to the list of signals needing a weak pull-up resistor to OV <sub>DD</sub> .<br>Section 1.9.1—Tables 21 thru 23: Added processor version register value. |

## 9.2 Part Numbers Not Fully Addressed by This Document

Parts with application modifiers or revision levels not fully addressed in this specification document are described in separate part number specifications that supplement and supersede this document. Table 21 shows the part numbers addressed by the MPC8245TXXnnnx series. The revision level can be determined by reading the Revision ID register at address offset 0x08.

### Table 21. Part Numbers Addressed by MPC8245TXXnnnx Series Part Number Specification Markings (Document Order No. MPC8245ECS01AD)

| MPC             | nnnn               | X                     | XX                                  | nnn                                                                        | X                 |                                        |

|-----------------|--------------------|-----------------------|-------------------------------------|----------------------------------------------------------------------------|-------------------|----------------------------------------|

| Product<br>Code | Part<br>Identifier | Process<br>Descriptor | Package <sup>1</sup>                | Processor<br>Frequency <sup>2</sup>                                        | Revision Level    | Processor<br>Version<br>Register Value |

| MPC             | 8245               | T: -40°<br>to 105°C   | ZU = TBGA<br>V V= Lead-free<br>TBGA | 266 MHz, 300 MHz:<br>1.7 V to 2.1 V<br>333 MHz, 350 MHz:<br>1.9 V to 2.2 V | D:1.4 Rev ID:0x14 | 0x80811014                             |

Notes:

1. See Section 5, "Package Description," for more information on available package types.

2. Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by a hardware specifications addendum may support other maximum core frequencies.

Table 22 shows the part numbers addressed by the MPC8245ARZUnnnx series.

### Table 22. Part Numbers Addressed by MPC8245ARZUnnnx Series Part Number Specification Markings (Document Order No. MPC8245ECS02AD)

| MPC             | nnnn               | X                                  | X                     | XX                                  | nnn                                 | X                 |                                           |

|-----------------|--------------------|------------------------------------|-----------------------|-------------------------------------|-------------------------------------|-------------------|-------------------------------------------|

| Product<br>Code | Part<br>Identifier | Process <sup>3</sup><br>Identifier | Process<br>Descriptor | Package <sup>1</sup>                | Processor<br>Frequency <sup>2</sup> | Revision Level    | Processor<br>Version<br>Register<br>Value |

| MPC             | 8245               | A                                  | R: 0° to 85°C         | ZU = TBGA<br>V V= Lead-free<br>TBGA | 400 MHz<br>2.1 V ±<br>100 mV        | D:1.4 Rev ID:0x14 | 0x80811014                                |

### Notes:

1. See Section 5, "Package Description," for more information on available package types.

- Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by a hardware specifications addendum may support other maximum core frequencies.

- Process identifier 'A' represents parts that are manufactured under a 29-angstrom process verses the original 35-angstrom process.