Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f816kpmc-g-sne2 |

|----------------------------|--------------------------------------------------------------------------------|

| Supplier Device Package    | 64-LQFP (12x12)                                                                |

| Package / Case             | 64-LQFP                                                                        |

| Mounting Type              | Surface Mount                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Oscillator Type            | External                                                                       |

| Data Converters            | A/D 12x8/10b                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.88V ~ 5.5V                                                                   |

| RAM Size                   | 1K x 8                                                                         |

| EEPROM Size                | -                                                                              |

| Program Memory Type        | FLASH                                                                          |

| Program Memory Size        | 36KB (36K x 8)                                                                 |

| lumber of I/O              | 58                                                                             |

| eripherals                 | LVD, POR, PWM, WDT                                                             |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, UART/USART                                      |

| peed                       | 16MHz                                                                          |

| Core Size                  | 8-Bit                                                                          |

| Core Processor             | F <sup>2</sup> MC-8FX                                                          |

| Product Status             | Obsolete                                                                       |

| Details                    |                                                                                |

| Part number Parameter | MB95F814K                                                                                                                                                                        | MB95F816K                  | MB95F818K                     |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------|

| Standby mode          | There are four standby modes as <ul> <li>Stop mode</li> <li>Sleep mode</li> <li>Watch mode</li> <li>Time-base timer mode</li> <li>In standby mode, two further optice</li> </ul> |                            | by mode and deep standby mode |

| Package               |                                                                                                                                                                                  | FPT-64P-M38<br>FPT-64P-M39 |                               |

# 2. Packages And Corresponding Products

| Part number Package | MB95F814K | MB95F816K | MB95F818K |

|---------------------|-----------|-----------|-----------|

| FPT-64P-M38         | O         | 0         | O         |

| FPT-64P-M39         | 0         | 0         | 0         |

#### O: Available

# 3. Differences Among Products And Notes On Product Selection

#### Current consumption

When using the on-chip debug function, take account of the current consumption of Flash program/erase. For details of current consumption, see "Electrical Characteristics".

### Package

For details of information on each package, see "Packages And Corresponding Products" and "Package Dimension".

# · Operating voltage

The operating voltage varies, depending on whether the on-chip debug function is used or not. For details of operating voltage, see "Electrical Characteristics".

#### · On-chip debug function

The on-chip debug function requires that Vcc, Vss and one serial wire be connected to an evaluation tool. For details of the connection method, refer to "CHAPTER 25 EXAMPLE OF SERIAL PROGRAMMING CONNECTION" in "New 8FX MB95810K Series Hardware Manual".

Document Number: 002-04694 Rev. \*B

# 5. Pin Functions

| Din no  | D:           | I/O circuit | Function                                           |                   | I/O type |      |      |  |

|---------|--------------|-------------|----------------------------------------------------|-------------------|----------|------|------|--|

| Pin no. | Pin name     | type*1      | Function                                           | Input             | Output   | OD*2 | PU*3 |  |

| 1       | <b>AV</b> cc | _           | Analog power supply pin for 8/10-bit A/D converter | _                 | _        | _    | _    |  |

| 2       | AVR          |             | Reference input pin for 8/10-bit A/D converter     |                   | _        | _    | _    |  |

| 3       | PE3          | F           | General-purpose I/O port                           | Hysteresis        | CMOS     |      | О    |  |

| J       | INT13        | '           | External interrupt input pin                       | Tiyotorcolo       | OWICO    |      |      |  |

| 4       | PE2          | F           | General-purpose I/O port                           | Hysteresis        | CMOS     |      | О    |  |

| 7       | INT12        | '           | External interrupt input pin                       | Tiyotorcolo       | OWICO    |      |      |  |

| 5       | PE1          | F           | General-purpose I/O port                           | Hysteresis        | CMOS     |      | О    |  |

| 3       | INT11        |             | External interrupt input pin                       | Tiyotorcolo       | OWICO    |      | O    |  |

| 6       | PE0          | F           | General-purpose I/O port                           | Hysteresis        | CMOS     | _    | О    |  |

| O       | INT10        | <b>'</b>    | External interrupt input pin                       | Tiyoteresis       | CIVIOS   |      | U    |  |

|         | P83          |             | General-purpose I/O port                           |                   |          |      |      |  |

| 7       | TRG0*4       | F           | 16-bit PPG timer ch. 0 trigger input pin           | Hysteresis        | sis CMOS | _    | О    |  |

|         | ADTG*4       |             | 8/10-bit A/D converter trigger input pin           |                   |          |      |      |  |

| 8       | P82          | F           | General-purpose I/O port                           | Hysteresis        | CMOS     | _    | О    |  |

| 9       | P81          | F           | General-purpose I/O port                           | Hysteresis        | CMOS     | _    | О    |  |

| 10      | P80          | F           | General-purpose I/O port                           | Hysteresis        | CMOS     |      | О    |  |

| 11      | P71          | F           | General-purpose I/O port                           | Uvotorogio        | CMOS     |      |      |  |

| 11      | TI0          | F           | 16-bit reload timer ch. 0 input pin                | Hysteresis        | CMOS     |      | О    |  |

| 40      | P70          | _           | General-purpose I/O port                           | 11                | 01400    |      |      |  |

| 12      | TO0          | F           | 16-bit reload timer ch. 0 output pin               | Hysteresis        | CMOS     |      | О    |  |

| 13      | P72          | F           | General-purpose I/O port                           | Hysteresis        | CMOS     | _    | О    |  |

| 4.4     | PF0          | <u> </u>    | General-purpose I/O port                           | 11                | 01400    |      |      |  |

| 14      | X0           | В           | Main clock input oscillation pin                   | Hysteresis        | CMOS     |      | _    |  |

| 4.5     | PF1          | Б           | General-purpose I/O port                           | I li rata na alia | CMCC     |      |      |  |

| 15      | X1           | В           | Main clock I/O oscillation pin                     | Hysteresis        | CMOS     |      | _    |  |

| 16      | Vss          | _           | Power supply pin (GND)                             | _                 | _        | _    | _    |  |

| 17      | Vcc          | _           | Power supply pin                                   | _                 | _        | _    | _    |  |

| 18      | С            | _           | Decoupling capacitor connection pin                |                   | _        | _    | _    |  |

| 40      | PG2          | 0           | General-purpose I/O port                           | I li rata na alia | CMCC     |      |      |  |

| 19      | X1A          | С           | Subclock I/O oscillation pin                       | Hysteresis        | CMOS     |      | О    |  |

| 20      | PG1          | C           | General-purpose I/O port                           | Uvotorosi-        | CMOS     |      |      |  |

| 20      | X0A          | С           | Subclock input oscillation pin                     | Hysteresis        | CMOS     | _    | О    |  |

| 24      | PF2          | ^           | General-purpose I/O port                           | Uvotorosi-        | CMOC     |      |      |  |

| 21      | RST          | Α           | Reset pin                                          | Hysteresis        | CMOS     | О    |      |  |

| <u> </u> | <b>.</b> | I/O circuit |                                           |                   | I/O type    |      |      |  |

|----------|----------|-------------|-------------------------------------------|-------------------|-------------|------|------|--|

| Pin no.  | Pin name | type*1      | Function                                  | Input             | Output      | OD*2 | PU*3 |  |

| 22       | P00      | _           | General-purpose I/O port                  | Lluctoropio       | CMOC        |      | 0    |  |

| 22       | INT00    | D           | External interrupt input pin              | Hysteresis        | CMOS        |      | О    |  |

| 00       | P01      | _           | General-purpose I/O port                  | I li rata na alia | CMCC        |      |      |  |

| 23       | INT01    | D           | External interrupt input pin              | Hysteresis        | CMOS        |      | О    |  |

| 0.4      | P02      | _           | General-purpose I/O port                  | I li rata na alia | CMOS        |      |      |  |

| 24       | INT02    | D           | External interrupt input pin              | Hysteresis        | CMOS        |      | О    |  |

| 25       | P03      | D           | General-purpose I/O port                  | Livotorogia       | CMOS        |      | 0    |  |

| 25       | INT03    | U           | External interrupt input pin              | Hysteresis        | CIVIOS      |      | U    |  |

| 26       | P04      | Б           | General-purpose I/O port                  | Lluctoropio       | CMOS        |      |      |  |

| 26       | INT04    | D           | External interrupt input pin              | Hysteresis        | CMOS        |      | О    |  |

| 27       | P05      | Б           | General-purpose I/O port                  | Lluctoropio       | CMOS        |      |      |  |

| 21       | INT05    | D           | External interrupt input pin              | Hysteresis        | CMOS        |      | О    |  |

| 28       | P06      | Б           | General-purpose I/O port                  | Hysteresis        | Lluctorooio | CMOS |      |  |

| 20       | INT06    | D           | External interrupt input pin              |                   | CMOS        |      | О    |  |

| 20       | P07      | Б           | General-purpose I/O port                  | Lluctoropio       | CMOS        |      |      |  |

| 29       | INT07    | D           | External interrupt input pin              | Hysteresis        | CMOS        |      | О    |  |

| 20       | P10      |             | General-purpose I/O port                  | CMOS              | CMOS        |      |      |  |

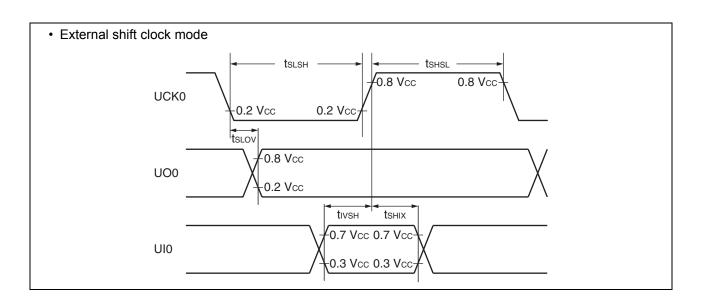

| 30       | UI0      | I           | UART/SIO ch. 0 data input pin             | CIVIOS            | CIVIOS      |      | О    |  |

| 24       | P11      | F           | General-purpose I/O port                  | I livetenesia C   | CMOS        |      |      |  |

| 31       | UO0      | F           | UART/SIO ch. 0 data output pin            | Hysteresis        | CMOS        |      | О    |  |

| 32       | P12      |             | General-purpose I/O port                  | Lluctoropio       | CMOS        | 0    |      |  |

| 32       | DBG      | G           | DBG input pin                             | Hysteresis        | CMOS        | О    | _    |  |

|          | P13      |             | General-purpose I/O port                  |                   |             |      |      |  |

| 33       | UCK0     | F           | UART/SIO ch. 0 clock I/O pin              | Lluctoropio       | CMOS        |      |      |  |

| 33       | TRG0*4   | F           | 16-bit PPG timer ch. 0 trigger input pin  | Hysteresis        | CMOS        |      | О    |  |

|          | ADTG*4   |             | 8/10-bit A/D converter trigger input pin  |                   |             |      |      |  |

| 34       | P14      | F           | General-purpose I/O port                  | Hysteresis        | CMOS        |      | 0    |  |

| 34       | PPG0     |             | 16-bit PPG timer ch. 0 output pin         | пуѕістеѕіѕ        | CIVIOS      |      | U    |  |

| 35       | P20      | F           | General-purpose I/O port                  | Lyotoropia        | CMOS        |      | 0    |  |

| აა       | PPG00    | F           | 8/16-bit PPG ch. 0 output pin             | Hysteresis        | CIVIOS      |      | U    |  |

| 36       | P21      | F           | General-purpose I/O port                  | Hysteresis        | CMOS        |      | 0    |  |

| 36       | PPG01    |             | 8/16-bit PPG ch. 0 output pin             | riysteresis       | CIVIOS      |      |      |  |

| 37       | P22      | F           | General-purpose I/O port                  | Uveteroois        | CMOS        |      | 0    |  |

| 31       | TO00     |             | 8/16-bit composite timer ch. 0 output pin | Hysteresis CMC    | CIVIOS      |      |      |  |

| 38       | P23      | F           | General-purpose I/O port                  | Hyetorosis CMOS   | CMOS        |      |      |  |

| 30       | TO01     | ]           | 8/16-bit composite timer ch. 0 output pin | Hysteresis        | CIVIOS      |      | О    |  |

| Type | Circuit              |                                                            | Remarks                                                                        |

|------|----------------------|------------------------------------------------------------|--------------------------------------------------------------------------------|

| D    | ₹R C                 | — Pull-up control                                          | <ul><li>CMOS output</li><li>Hysteresis input</li><li>Pull-up control</li></ul> |

|      | P-ch                 | — Digital output                                           | High current output                                                            |

|      | N-ch                 | — Digital output                                           |                                                                                |

|      |                      | Standby control     Hysteresis input                       |                                                                                |

| E    | ₹R C                 | —— Pull-up control                                         | <ul><li>CMOS output</li><li>Hysteresis input</li><li>Pull-up control</li></ul> |

|      | P-ch                 | — Digital output                                           | Analog input                                                                   |

|      | N-ch                 | —— Digital output                                          |                                                                                |

|      | <u></u>              | —— Analog input                                            |                                                                                |

|      |                      | A/D control     Standby control     Hysteresis input       |                                                                                |

| F    | ₹R C                 | — Pull-up control                                          | <ul><li>CMOS output</li><li>Hysteresis input</li><li>Pull-up control</li></ul> |

|      | P-ch                 | —— Digital output                                          | . a. ap contact                                                                |

|      | N-ch                 | — Digital output                                           |                                                                                |

|      |                      | <ul><li>Standby control</li><li>Hysteresis input</li></ul> |                                                                                |

| G    |                      | Standby control Hysteresis input                           | N-ch open drain output     Hysteresis input                                    |

|      | Digital output  N-ch |                                                            |                                                                                |

| Н    | N-ch                 | — Digital output                                           | N-ch open drain output     CMOS input                                          |

|      |                      | — Standby control                                          |                                                                                |

|      |                      | — CMOS input                                               |                                                                                |

#### Latch-up

Semiconductor devices are constructed by the formation of P-type and N-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic PNPN junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred mA to flow continuously at the power supply pin. This condition is called latch-up.

CAUTION: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

- (1) Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

- (2) Be sure that abnormal current flows do not occur during the power-on sequence.

#### Observance of Safety Regulations and Standards

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

# • Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

### • Precautions Related to Usage of Devices

Cypress semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

# 7.2 Precautions for Package Mounting

Package mounting may be either lead insertion type or surface mount type. In either case, for heat resistance during soldering, you should only mount under Cypress's recommended conditions. For detailed information about mount conditions, contact your sales representative.

#### Lead Insertion Type

Mounting of lead insertion type packages onto printed circuit boards may be done by two methods: direct soldering on the board, or mounting by using a socket.

Direct mounting onto boards normally involves processes for inserting leads into through-holes on the board and using the flow soldering (wave soldering) method of applying liquid solder. In this case, the soldering process usually causes leads to be subjected to thermal stress in excess of the absolute ratings for storage temperature. Mounting processes should conform to Cypress recommended mounting conditions.

If socket mounting is used, differences in surface treatment of the socket contacts and IC lead surfaces can lead to contact deterioration after long periods. For this reason it is recommended that the surface treatment of socket contacts and IC leads be verified before mounting.

Document Number: 002-04694 Rev. \*B

## 9. Pin Connection

# · Treatment of unused pins

If an unused input pin is left unconnected, a component may be permanently damaged due to malfunctions or latchups. Always pull up or pull down an unused input pin through a resistor of at least  $2 \text{ k}\Omega$ . Set an unused input/output pin to the output state and leave it unconnected, or set it to the input state and treat it the same as an unused input pin. If there is an unused output pin, leave it unconnected.

#### Power supply pins

To reduce unnecessary electro-magnetic emission, prevent malfunctions of strobe signals due to an increase in the ground level, and conform to the total output current standard, always connect the Vcc pin and the Vss pin to the power supply and ground outside the device. In addition, connect the current supply source to the Vcc pin and the Vss pin with low impedance.

It is also advisable to connect a ceramic capacitor of approximately 0.1 μF as a bypass capacitor between the Vcc pin and the Vss pin at a location close to this device.

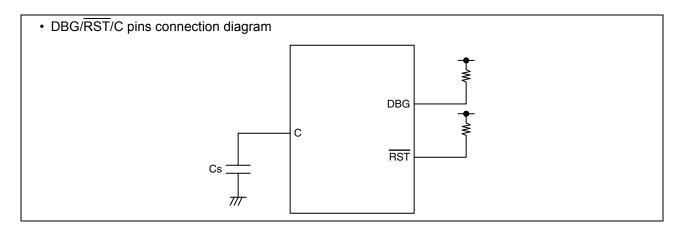

#### DBG pin

Connect the DBG pin to an external pull-up resistor of 2 k $\Omega$  or above.

After power-on, ensure that the DBG pin does not stay at "L" level until the reset output is released.

The DBG pin becomes a communication pin in debug mode. Since the actual pull-up resistance depends on the tool used and the interconnection length, refer to the tool document when selecting a pull-up resistor.

# • RST pin

Connect the RST pin to an external pull-up resistor of 2 k $\Omega$  or above.

To prevent the device from unintentionally entering the reset mode due to noise, minimize the interconnection length between a pull-up resistor and the RST pin and that between a pull-up resistor and the Vcc pin when designing the layout of the printed circuit board.

The PF2/RST pin functions as the reset input/output pin after power-on. In addition, the reset output of the PF2/RST pin can be enabled by the RSTOE bit in the SYSC register, and the reset input function and the general purpose I/O function can be selected by the RSTEN bit in the SYSC register.

## Analog power supply

Always set the same potential to the AVcc pin and the Vcc pin. When Vcc is larger than AVcc, the current may flow through the AN00 to AN11 pins.

#### • Treatment of power supply pins on the 8/10-bit A/D converter

Ensure that AVcc is equal to Vcc and AVss equal to Vss even when the 8/10-bit A/D converter is not in use. Noise riding on the AVcc pin may cause accuracy degradation. Therefore, connect a ceramic capacitor of 0.1 µF (approx.) as a bypass capacitor between the AVcc pin and the AVss pin in the vicinity of this device.

# C pin

Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. The decoupling capacitor for the Vcc pin must have a capacitance equal to or larger than the capacitance of Cs. For the connection to a decoupling capacitor Cs, see the diagram below. To prevent the device from unintentionally entering a mode to which the device is not set to transit due to noise, minimize the distance between the C pin and Cs and the distance between Cs and the Vss pin when designing the layout of a printed circuit board.

# · Note on serial communication

In serial communication, reception of wrong data may occur due to noise or other causes. Therefore, design a printed circuit board to prevent noise from occurring. Taking account of the reception of wrong data, take measures such as adding a checksum to the end of data in order to detect errors. If an error is detected, retransmit the data.

Correspondence between registers and pins for port 4

|          |   | Correspondence between related register bits and pins |   |   |      |      |      |      |  |  |  |  |  |

|----------|---|-------------------------------------------------------|---|---|------|------|------|------|--|--|--|--|--|

| Pin name | - | -                                                     | - | - | P43  | P42  | P41  | P40  |  |  |  |  |  |

| PDR4     |   |                                                       |   |   |      |      |      |      |  |  |  |  |  |

| DDR4     |   |                                                       |   |   | bit2 | bit2 | b:44 | b:t0 |  |  |  |  |  |

| PUL4     | - | -                                                     | - | - | bit3 | DILZ | bit1 | bit0 |  |  |  |  |  |

| AIDRH    |   |                                                       |   |   |      |      |      |      |  |  |  |  |  |

#### 15.5.4 Port 4 operations

- Operation as an output port

- A pin becomes an output port if the bit in the DDR4 register corresponding to that pin is set to "1".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When a pin is used as an output port, it outputs the value of the PDR4 register to external pins.

- If data is written to the PDR4 register, the value is stored in the output latch and is output to the pin set as an output port as it is.

- Reading the PDR4 register returns the PDR4 register value.

# Operation as an input port

- A pin becomes an input port if the bit in the DDR4 register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When using a pin shared with the analog input function as an input port, set the corresponding bit in the A/D input disable register (upper) (AIDRH) to "1".

- If data is written to the PDR4 register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDR4 register returns the pin value. However, if the read-modify-write (RMW) type of instruction is used to read the PDR4 register, the PDR4 register value is returned.

#### Operation as a peripheral function input pin

- To set a pin as an input port, set the bit in the DDR4 register corresponding to the input pin of a peripheral function to "0".

- When using a pin shared with the analog input function as another peripheral function input pin, configure it as an input port by setting the bit in the AIDRH register corresponding to that pin to "1".

- Reading the PDR4 register returns the pin value, regardless of whether the peripheral function uses that pin as its

input pin. However, if the read-modify-write (RMW) type of instruction is used to read the PDR4 register, the PDR4

register value is returned.

#### Operation at reset

If the CPU is reset, all bits in the DDR4 register are initialized to "0" and port input is enabled. As for a pin shared with the analog input function, its port input is disabled because the AIDRH register is initialized to "0".

# Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDR4 register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

#### Operation as an analog input pin

• Set the bit in the DDR4 register bit corresponding to the analog input pin to "0" and the bit corresponding to that pin

- P52/PPG1 pin

- This pin has the following peripheral function:

- 16-bit PPG timer ch. 1 output pin (PPG1)

- Block diagram of P52/PPG1

# • P53/TRG1 pin

This pin has the following peripheral function:

• 16-bit PPG timer ch. 1 trigger input pin (TRG1)

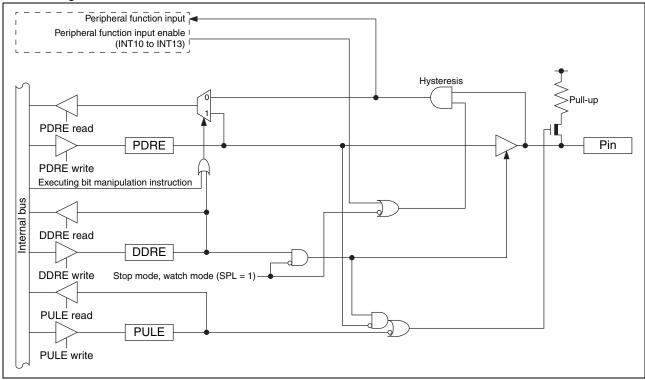

• Block diagram of PE0/INT10, PE1/INT11, PE2/INT12 and PE3/INT13

# 15.10.3 Port E registers

# Port E register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                              |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|------------------------------------|--|--|--|--|

| PDRE                  | 0    | Pin state is "L" level. | PDRE value is "0".                          | As output port, outputs "L" level. |  |  |  |  |

| FURE                  | 1    | Pin state is "H" level. | PDRE value is "1".                          | As output port, outputs "H" level. |  |  |  |  |

| DDRE                  | 0    |                         | Port input enabled                          | d                                  |  |  |  |  |

| DDRE                  | 1    |                         | Port output enable                          | d                                  |  |  |  |  |

| PULE                  | 0    |                         | Pull-up disabled                            |                                    |  |  |  |  |

| FULE                  | 1    |                         | Pull-up enabled                             |                                    |  |  |  |  |

# · Correspondence between registers and pins for port E

|          |   | Correspondence between related register bits and pins |   |   |      |      |      |      |  |  |  |  |

|----------|---|-------------------------------------------------------|---|---|------|------|------|------|--|--|--|--|

| Pin name | - | -                                                     | - | - | PE3  | PE2  | PE1  | PE0  |  |  |  |  |

| PDRE     |   |                                                       |   |   |      |      |      |      |  |  |  |  |

| DDRE     | - | -                                                     | - | - | bit3 | bit2 | bit1 | bit0 |  |  |  |  |

| PULE     |   |                                                       |   |   |      |      |      |      |  |  |  |  |

#### 15.12.3 Port G registers

Port G register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                              |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|------------------------------------|--|--|--|--|

| PDRG                  | 0    | Pin state is "L" level. | PDRG value is "0".                          | As output port, outputs "L" level. |  |  |  |  |

| FBRG                  | 1    | Pin state is "H" level. | PDRG value is "1".                          | As output port, outputs "H" level. |  |  |  |  |

| DDRG                  | 0    |                         | Port input enabled                          | d                                  |  |  |  |  |

| DDRG                  | 1    |                         | Port output enable                          | d                                  |  |  |  |  |

| PULG                  | 0    |                         | Pull-up disabled                            |                                    |  |  |  |  |

| FOLG                  | 1    |                         | Pull-up enabled                             |                                    |  |  |  |  |

### Correspondence between registers and pins for port G

|          |   | Correspondence between related register bits and pins |   |   |   |      |      |   |  |  |  |  |  |

|----------|---|-------------------------------------------------------|---|---|---|------|------|---|--|--|--|--|--|

| Pin name | - | -                                                     | - | - | - | PG2  | PG1  | - |  |  |  |  |  |

| PDRG     |   |                                                       |   |   |   |      |      |   |  |  |  |  |  |

| DDRG     | - | -                                                     | - | - | - | bit2 | bit1 | - |  |  |  |  |  |

| PULG     |   |                                                       |   |   |   |      |      |   |  |  |  |  |  |

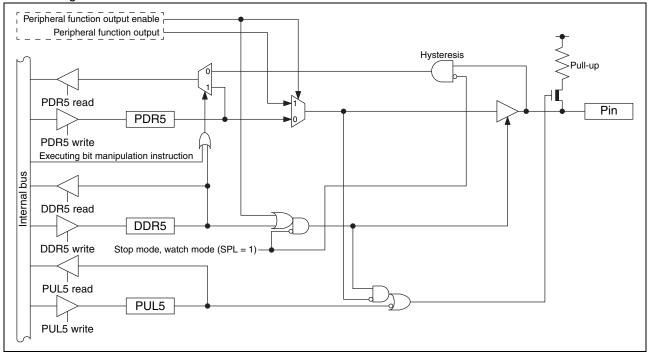

#### 15.12.4 Port G operations

- Operation as an output port

- A pin becomes an output port if the bit in the DDRG register corresponding to that pin is set to "1".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When a pin is used as an output port, it outputs the value of the PDRG register to external pins.

- If data is written to the PDRG register, the value is stored in the output latch and is output to the pin set as an output port as it is.

- Reading the PDRG register returns the PDRG register value.

#### Operation as an input port

- · A pin becomes an input port if the bit in the DDRG register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- If data is written to the PDRG register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDRG register returns the pin value. However, if the read-modify-write (RMW) type of instruction is used to read the PDRG register, the PDRG register value is returned.

### Operation at reset

If the CPU is reset, all bits in the DDRG register are initialized to "0" and port input is enabled.

### Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDRG register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

# Operation of the pull-up register

Setting the bit in the PULG register to "1" makes the pull-up resistor be internally connected to the pin. When the pin output is "L" level, the pull-up resistor is disconnected regardless of the value of the PULG register.

|                                                                                          | Normal                                                   |                                                          | Stop                                                                   | mode                                                        | Watch                                                                       | mode                                                        |                                                                                                                 |

|------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Pin name                                                                                 | operation                                                | Sleep mode                                               | SPL=0                                                                  | SPL=1                                                       | SPL=0                                                                       | SPL=1                                                       | On reset                                                                                                        |

| P12/DBG                                                                                  | I/O port/<br>peripheral<br>function I/O                  | I/O port/<br>peripheral<br>function I/O                  | - Previous state<br>kept<br>- Input blocked*2                          | - Hi-Z<br>- Input blocked*²                                 | - Previous state<br>kept<br>- Input blocked*2                               | - Hi-Z<br>- Input blocked*²                                 | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.)                            |

| P13/UCK0/<br>TRG0/ADTG                                                                   | I/O port/<br>peripheral<br>function I/O                  | I/O port/<br>peripheral<br>function I/O                  | - Previous state<br>kept<br>- Input<br>blocked*2,*6                    | - Hi-Z* <sup>5</sup><br>- Input<br>blocked* <sup>2,*6</sup> | - Previous state<br>kept<br>- Input<br>blocked*2,*6                         | - Hi-Z* <sup>5</sup><br>- Input<br>blocked* <sup>2,*6</sup> | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.)                            |

| P14/PPG0<br>P20/PPG00<br>P21/PPG01<br>P22/TO00<br>P23/TO01                               | I/O port/<br>peripheral<br>function I/O                  | I/O port/<br>peripheral<br>function I/O                  | - Previous state<br>kept<br>- Input blocked*2                          | - Hi-Z* <sup>5</sup><br>- Input blocked* <sup>2</sup>       | - Previous state<br>kept<br>- Input blocked*2                               | - Hi-Z* <sup>5</sup><br>- Input blocked* <sup>2</sup>       | <ul> <li>Hi-Z</li> <li>Input</li> <li>enabled*<sup>3</sup></li> <li>(However, it does not function.)</li> </ul> |

| P24/EC0                                                                                  | I/O port/<br>peripheral<br>function I/O                  | I/O port/<br>peripheral<br>function I/O                  | - Previous state<br>kept<br>- Input<br>blocked*2,*6                    | - Hi-Z* <sup>5</sup><br>- Input<br>blocked* <sup>2,*6</sup> | <ul> <li>Previous state<br/>kept</li> <li>Input<br/>blocked*2,*6</li> </ul> | - Hi-Z* <sup>5</sup><br>- Input<br>blocked* <sup>2,*6</sup> | <ul> <li>Hi-Z</li> <li>Input</li> <li>enabled*<sup>3</sup></li> <li>(However, it does not function.)</li> </ul> |

| P32/AN02/<br>CMP0_O<br>P35/AN05/<br>CMP1_O                                               | I/O port/<br>peripheral<br>function I/O/<br>analog input | I/O port/<br>peripheral<br>function I/O/<br>analog input | <ul> <li>Previous state<br/>kept*8</li> <li>Input blocked*2</li> </ul> | - Hi-Z* <sup>5</sup><br>- Input blocked* <sup>2</sup>       | <ul> <li>Previous state<br/>kept*8</li> <li>Input blocked*2</li> </ul>      | - Hi-Z*5<br>- Input blocked*2                               | - Hi-Z<br>- Input<br>blocked* <sup>2</sup>                                                                      |

| P30/AN00/<br>CMP0_N<br>P31/AN01/<br>CMP0_P<br>P33/AN03/<br>CMP1_N<br>P34/AN04/<br>CMP1_P | I/O port/<br>peripheral<br>function I/O/<br>analog input | I/O port/<br>peripheral<br>function I/O/<br>analog input | - Previous state<br>kept<br>- Input<br>blocked*2,*7                    | - Hi-Z* <sup>5</sup><br>- Input<br>blocked* <sup>2,*7</sup> | - Previous state<br>kept<br>- Input<br>blocked*2,*7                         | - Hi-Z* <sup>5</sup><br>- Input<br>blocked* <sup>2,*7</sup> | - Hi-Z<br>- Input<br>blocked* <sup>2</sup>                                                                      |

| P36/AN06<br>P37/AN07<br>P40/AN08<br>P41/AN09<br>P42/AN10<br>P43/AN11                     | I/O port/<br>analog input                                | I/O port/<br>analog input                                | - Previous state<br>kept<br>- Input blocked*2                          | - Hi-Z* <sup>5</sup><br>- Input blocked* <sup>2</sup>       | - Previous state<br>kept<br>- Input blocked*2                               | - Hi-Z* <sup>5</sup><br>- Input blocked* <sup>2</sup>       | - Hi-Z<br>- Input<br>blocked* <sup>2</sup>                                                                      |

| P50/SCL<br>P51/SDA                                                                       | I/O port/<br>peripheral<br>function I/O                  | I/O port/<br>peripheral<br>function I/O                  | - Previous state<br>kept<br>- Input<br>blocked*2,*9                    | - Hi-Z<br>- Input<br>blocked* <sup>2,*9</sup>               | - Previous state<br>kept<br>- Input<br>blocked*2,*9                         | - Hi-Z<br>- Input<br>blocked* <sup>2, *9</sup>              | - Hi-Z<br>- Input<br>enabled* <sup>3</sup><br>(However, it<br>does not<br>function.)                            |

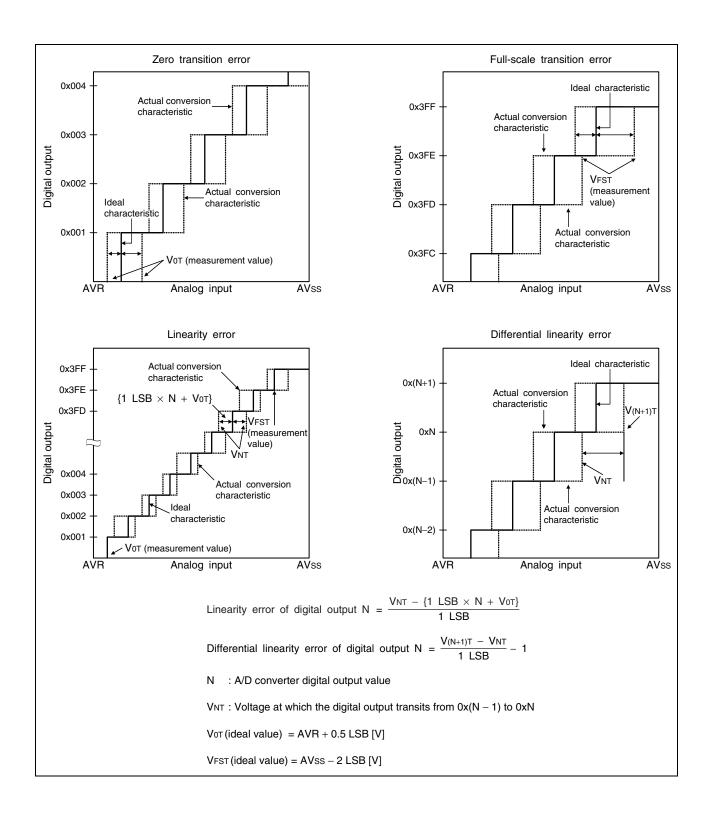

# 18. Electrical Characteristics

# **18.1 Absolute Maximum Ratings**

| Donomoston                             | Ol               | Rating    |         | 11                                                                              | Domonico                                                                                   |  |  |

|----------------------------------------|------------------|-----------|---------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Parameter                              | Symbol           | Min       | Max     | Unit                                                                            | Remarks                                                                                    |  |  |

| Power supply voltage*1                 | AVcc,<br>Vcc     | Vss - 0.3 | Vss + 6 | V                                                                               | *2                                                                                         |  |  |

| ,,,,                                   | AVR              | Vss - 0.3 |         | V                                                                               |                                                                                            |  |  |

| Input voltage*1                        | Vı               | Vss - 0.3 |         | V                                                                               | *3                                                                                         |  |  |

| Output voltage*1                       | Vo               | Vss - 0.3 |         | V                                                                               | *3                                                                                         |  |  |

| Maximum clamp current                  | ICLAMP           | -2        | +2      | mA                                                                              | Applicable to specific pins*4                                                              |  |  |

| Total maximum clamp current            | $\Sigma$  Iclamp |           | 20      | mA                                                                              | Applicable to specific pins*4                                                              |  |  |

| "L" level maximum output current       | Іоь              | _         | 15      | mA                                                                              |                                                                                            |  |  |

| "L" level average current              | lolav1           |           | 4       | mΛ                                                                              | Other than P00 to P07 Average output current = operating current × operating ratio (1 pin) |  |  |

| Ç                                      | lolav2           | _         | 12      | mA                                                                              | P00 to P07 Average output current = operating current × operating ratio (1 pin)            |  |  |

| "L" level total maximum output current | $\Sigma$ lol     | _         | 100     | mA                                                                              |                                                                                            |  |  |

| "L" level total average output current | $\Sigma$ lolav   |           | 37      | mA                                                                              | Total average output current = operating current × operating ratio (Total number of pins)  |  |  |

| "H" level maximum output current       | Іон              | _         | -15     | mA                                                                              |                                                                                            |  |  |

| "H" level average                      | Iонаv1           |           | -4      | mA                                                                              | Other than P00 to P07 Average output current = operating current × operating ratio (1 pin) |  |  |

| current                                | IOHAV2 —8        |           |         | P00 to P07 Average output current = operating current × operating ratio (1 pin) |                                                                                            |  |  |

| "H" level total maximum output current | $\Sigma$ Іон     | _         | -100    | mA                                                                              |                                                                                            |  |  |

| "H" level total average output current | $\Sigma$ Iohav   | _         | -47     | mA                                                                              | Total average output current = operating current × operating ratio (Total number of pins)  |  |  |

| Power consumption                      | Pd               |           | 320     | mW                                                                              |                                                                                            |  |  |

| Operating temperature                  | TA               | -40       | +85     | °C                                                                              |                                                                                            |  |  |

| Storage temperature                    | Tstg             | -55       | +150    | °C                                                                              |                                                                                            |  |  |

<sup>\*1:</sup> These parameters are based on the condition that Vss is 0.0 V.

<sup>\*2:</sup> Apply equal potential to AVcc and Vcc. AVR must not exceed AVcc.

<sup>\*3:</sup> V<sub>1</sub> and V<sub>0</sub> must not exceed V<sub>CC</sub> + 0.3 V. V<sub>1</sub> must not exceed the rated voltage. However, if the maximum current to/from an input is limited by means of an external component, the I<sub>CLAMP</sub> rating is used instead of the V<sub>1</sub> rating.

<sup>\*4:</sup> Specific pins: P00 to P07, P10, P11, P13, P14, P20 to P24, P30 to P37, P40 to P43, P52, P53, P60 to P67, P70 to P72, P80 to P83, PE0 to PE3, PF0, PF1, PG1, PG2

<sup>•</sup> Use under recommended operating conditions.

<sup>•</sup> Use with DC voltage (current).

$(Vcc = 5.0 V\pm 10\%, Vss = 0.0 V, TA = -40 °C to +85 °C)$

| Danamatan           | O b. a.l    | D'       | Condition                                                                                                               |     | Value |       | 1114 | Damada                                                                                           |

|---------------------|-------------|----------|-------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|------|--------------------------------------------------------------------------------------------------|

| Parameter           | Symbol      | Pin name | Condition                                                                                                               | Min | Typ*1 | Max*2 | Unit | Remarks                                                                                          |

|                     | lv          |          | Current consumption of the comparator                                                                                   | _   | 60    | 160   | μΑ   |                                                                                                  |

|                     | ILVD        |          | Current consumption of the low-voltage detection reset circuit                                                          |     | 4     | 7     | μΑ   | With the LVD reset<br>already enabled by<br>the LVD reset<br>circuit control<br>register (LVDCC) |

|                     | Іспн        | Vcc      | Current consumption of the main CR oscillator                                                                           | _   | 240   | 320   | μA   |                                                                                                  |

| Power               | Icrl        | VCC      | Current consumption of the sub-CR oscillator oscillating at 100 kHz                                                     |     | 7     | 20    | μΑ   |                                                                                                  |

| supply<br>current*3 | Імѕтву      |          | Current consumption<br>difference between<br>normal standby mode<br>and deep standby<br>mode<br>T <sub>A</sub> = +25 °C | _   | 22    | 30    | μΑ   |                                                                                                  |

|                     | la          |          | Vcc = 5.5 V FcH = 16 MHz Current consumption of the A/D converter                                                       | l   | 2     | 3.1   | mA   |                                                                                                  |

|                     | AVcc<br>IAH |          | FCRH = 4 MHz FMP = 4 MHz Current consumption with the A/D converter halted TA = +25 °C                                  | _   | 1     | 5     | μΑ   |                                                                                                  |

<sup>\*1:</sup>  $V_{CC} = 5.0 \text{ V}$ ,  $T_A = +25 ^{\circ}\text{C}$

- See "4. AC Characteristics Clock Timing" for Fch, Fcl, Fcrh and Fmcrpll.

- See "4. AC Characteristics Source Clock/Machine Clock" for FMP and FMPL.

- The power supply current value in standby mode is measured in deep standby mode. The current consumption in normal standby mode is higher than that in deep standby mode. The power supply current value in normal standby mode can be found by adding the current consumption difference between normal standby mode and deep standby mode (Instray) to the power supply current value in deep standby mode. For details of normal standby mode and deep standby mode, refer to "CHAPTER 3 CLOCK CONTROLLER" in "New 8FX MB95810K Series Hardware Manual".

<sup>\*2:</sup> Vcc = 5.5 V, T<sub>A</sub> = +85 °C (unless otherwise specified)

<sup>\*3: •</sup> The power supply current is determined by the external clock. When the low-voltage detection reset circuit is selected, the power supply current is the sum of adding the current consumption of the low-voltage detection reset circuit (ILVD) to one of the values from Icc to Icch. In addition, when both the low-voltage detection reset circuit and a CR oscillator are selected, the power supply current is the sum of adding up the current consumption of the low-voltage detection reset circuit (ILVD), the current consumption of the CR oscillators (ICRH or Icrl) and one of the values from Icc to Icch. In on-chip debug mode, the main CR oscillator (ICRH) and the low-voltage detection reset circuit are always in operation, and current consumption therefore increases accordingly.

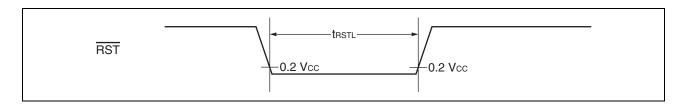

#### 18.4.3 External Reset

| Parameter                 | Symbol        | Value            |     | Unit | Remarks |

|---------------------------|---------------|------------------|-----|------|---------|

| Parameter                 | Syllibol      | Min              | Max | Oill |         |

| RST "L" level pulse width | <b>t</b> RSTL | 2 <b>t</b> MCLK* |     | ns   |         |

<sup>\*:</sup> See "Source Clock/Machine Clock" for tmclk.

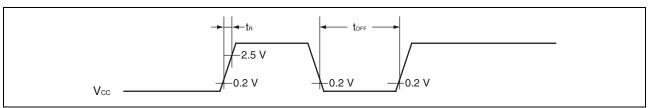

### 18.4.4 Power-on Reset

$$(V_{SS} = 0.0 \text{ V}, T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$$

| Parameter                | Symbol       | Condition | Va  | lue | Unit  | Remarks                  |

|--------------------------|--------------|-----------|-----|-----|-------|--------------------------|

| Farameter                | Syllibol     | Condition | Min | Max | Oilit |                          |

| Power supply rising time | <b>t</b> R   |           |     | 50  | ms    |                          |

| Power supply cutoff time | <b>t</b> off |           | 1   |     | ms    | Wait time until power-on |

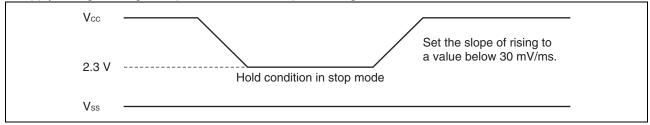

Note: A sudden change of power supply voltage may activate the power-on reset function. When changing the power supply voltage during the operation, set the slope of rising to a value below within 30 mV/ms as shown below.

# 18.4.10 Comparator Timing

$(Vcc = 2.88 \text{ V to } 5.5 \text{ V}, Vss = 0.0 \text{ V}, T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$

| Parameter                        | Pin name                                | Value |     |           | Unit  | Remarks                               |  |

|----------------------------------|-----------------------------------------|-------|-----|-----------|-------|---------------------------------------|--|

| Parameter                        | Fili liaille                            | Min   | Тур | Max       | Oilit | Remarks                               |  |

| Voltage range                    | CMP0_P,<br>CMP0_N,<br>CMP1_P,<br>CMP1_N | 0     | _   | Vcc – 1.3 | V     |                                       |  |

| Offset voltage                   | CMP0_P,<br>CMP0_N,<br>CMP1_P,<br>CMP1_N | -15   | _   | +15       | mV    |                                       |  |

| Delay time                       | CMP0_O,                                 |       | 650 | 1200      | ns    | Overdrive 5 mV                        |  |

| Delay time                       | CMP1_O                                  |       | 140 | 420       | ns    | Overdrive 50 mV                       |  |

| Power down delay                 | CMP0_O,<br>CMP1_O                       | _     | _   | 1200      | ns    | Power down recovery PD: 1 → 0         |  |

| Power up stabilization wait time | CMP0_O,<br>CMP1_O                       |       | _   | 1200      | ns    | Output stabilization time at power up |  |

# 18.4.11 BGR for Comparator

$(V_{CC} = 2.88 \text{ V to } 5.5 \text{ V}, \text{ Vss} = 0.0 \text{ V}, \text{ TA} = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$

| Parameter                        | Symbol   |        | Value |        | Unit  | Remarks     |  |

|----------------------------------|----------|--------|-------|--------|-------|-------------|--|

| Farameter                        | Syllibol | Min    | Тур   | Max    | Oilit |             |  |

| Power up stabilization wait time | _        | _      | _     | 150    | μs    | Load: 10 pF |  |

| Output voltage                   | VBGR     | 1.1495 | 1.21  | 1.2705 | V     |             |  |

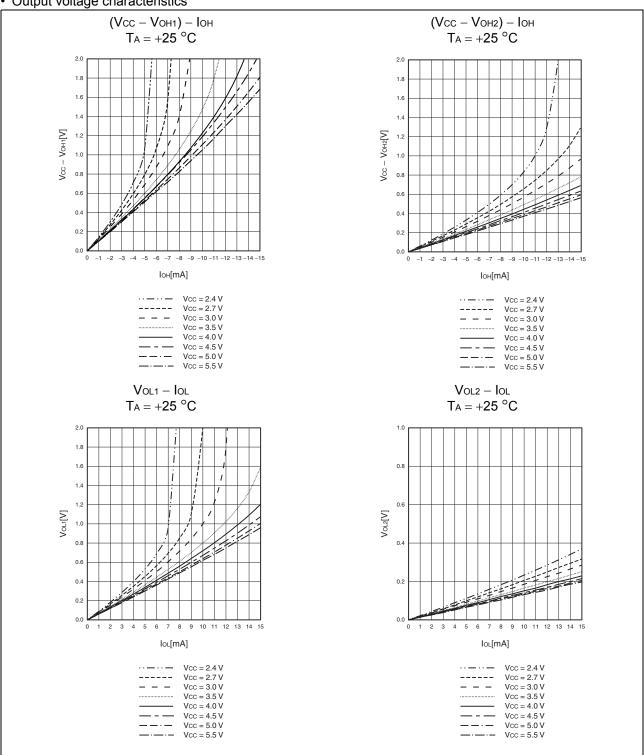

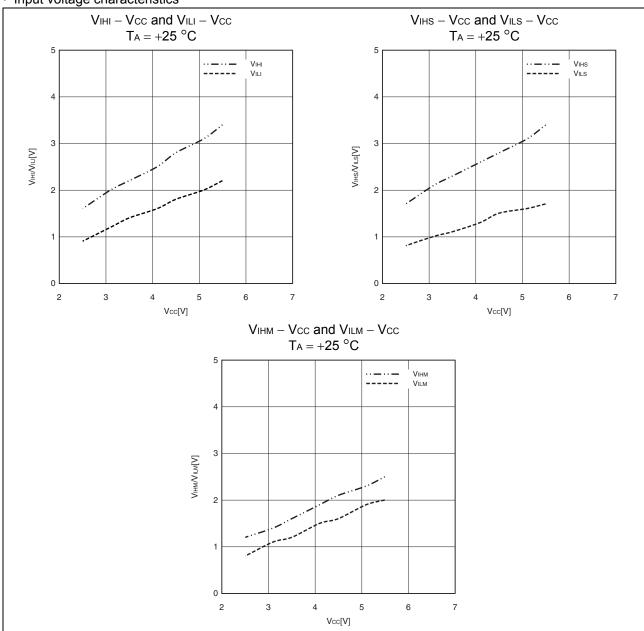

## Output voltage characteristics