Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | F <sup>2</sup> MC-8FX                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 16MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, UART/USART                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 58                                                                              |

| Program Memory Size        | 60KB (60K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.88V ~ 5.5V                                                                    |

| Data Converters            | A/D 12x8/10b                                                                    |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f818kpmc1-g-sne2 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 9. Pin Connection

## · Treatment of unused pins

If an unused input pin is left unconnected, a component may be permanently damaged due to malfunctions or latchups. Always pull up or pull down an unused input pin through a resistor of at least 2 k $\Omega$ . Set an unused input/output pin to the output state and leave it unconnected, or set it to the input state and treat it the same as an unused input pin. If there is an unused output pin, leave it unconnected.

## · Power supply pins

To reduce unnecessary electro-magnetic emission, prevent malfunctions of strobe signals due to an increase in the ground level, and conform to the total output current standard, always connect the Vcc pin and the Vss pin to the power supply and ground outside the device. In addition, connect the current supply source to the Vcc pin and the Vss pin with low impedance.

It is also advisable to connect a ceramic capacitor of approximately 0.1  $\mu$ F as a bypass capacitor between the V<sub>cc</sub> pin and the V<sub>ss</sub> pin at a location close to this device.

## DBG pin

Connect the DBG pin to an external pull-up resistor of 2 k $\Omega$  or above.

After power-on, ensure that the DBG pin does not stay at "L" level until the reset output is released.

The DBG pin becomes a communication pin in debug mode. Since the actual pull-up resistance depends on the tool used and the interconnection length, refer to the tool document when selecting a pull-up resistor.

## RST pin

Connect the RST pin to an external pull-up resistor of 2 k $\!\Omega$  or above.

To prevent the device from unintentionally entering the reset mode due to noise, minimize the interconnection length between a pull-up resistor and the  $\overrightarrow{\text{RST}}$  pin and that between a pull-up resistor and the V<sub>CC</sub> pin when designing the layout of the printed circuit board.

The PF2/RST pin functions as the reset input/output pin after power-on. In addition, the reset output of the PF2/RST pin can be enabled by the RSTOE bit in the SYSC register, and the reset input function and the general purpose I/O function can be selected by the RSTEN bit in the SYSC register.

Analog power supply

Always set the same potential to the AVcc pin and the Vcc pin. When Vcc is larger than AVcc, the current may flow through the AN00 to AN11 pins.

## • Treatment of power supply pins on the 8/10-bit A/D converter

Ensure that AVcc is equal to Vcc and AVss equal to Vss even when the 8/10-bit A/D converter is not in use. Noise riding on the AVcc pin may cause accuracy degradation. Therefore, connect a ceramic capacitor of  $0.1 \,\mu\text{F}$  (approx.) as a bypass capacitor between the AVcc pin and the AVss pin in the vicinity of this device.

## • C pin

Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. The decoupling capacitor for the V<sub>CC</sub> pin must have a capacitance equal to or larger than the capacitance of C<sub>S</sub>. For the connection to a decoupling capacitor C<sub>S</sub>, see the diagram below. To prevent the device from unintentionally entering a mode to which the device is not set to transit due to noise, minimize the distance between the C pin and C<sub>S</sub> and the distance between C<sub>S</sub> and the V<sub>SS</sub> pin when designing the layout of a printed circuit board.

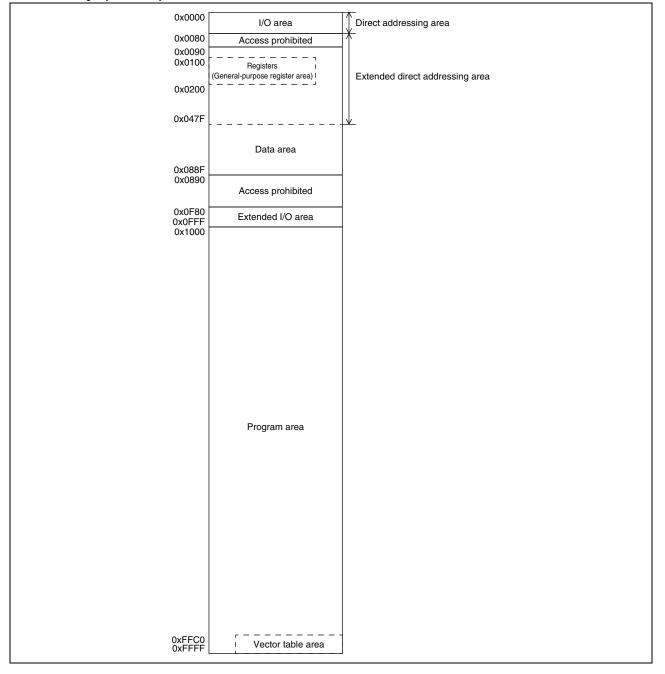

## 12.5 Memory space map

| Address                | Register abbreviation | Register name                                           | R/W | Initial value |

|------------------------|-----------------------|---------------------------------------------------------|-----|---------------|

| 0x0FC5<br>to<br>0x0FE2 | _                     | (Disabled)                                              | _   | _             |

| 0x0FE3                 | WCDR                  | Watch counter data register                             | R/W | 0b00111111    |

| 0x0FE4                 | CRTH                  | Main CR clock trimming register (upper)                 | R/W | 0b000XXXXX    |

| 0x0FE5                 | CRTL                  | Main CR clock trimming register (lower)                 | R/W | 0b000XXXXX    |

| 0x0FE6                 | _                     | (Disabled)                                              | —   | —             |

| 0x0FE7                 | CRTDA                 | Main CR clock temperature dependent adjustment register | R/W | 0b000XXXXX    |

| 0x0FE8                 | SYSC                  | System configuration register                           | R/W | 0b11000011    |

| 0x0FE9                 | CMCR                  | Clock monitoring control register                       | R/W | 0b0000000     |

| 0x0FEA                 | CMDR                  | Clock monitoring data register                          | R   | 0b0000000     |

| 0x0FEB                 | WDTH                  | Watchdog timer selection ID register (upper)            | R   | 0bXXXXXXXX    |

| 0x0FEC                 | WDTL                  | Watchdog timer selection ID register (lower)            | R   | 0bXXXXXXXX    |

| 0x0FED,<br>0x0FEE      | _                     | (Disabled)                                              | -   | _             |

| 0x0FEF                 | WICR                  | Interrupt pin selection circuit control register        | R/W | 0b01000000    |

| 0x0FF0<br>to<br>0x0FFF | _                     | (Disabled)                                              | _   | _             |

- R/W access symbols

- R/W : Readable/Writable

- R : Read only

- Initial value symbols

- 0 : The initial value of this bit is "0".

- 1 : The initial value of this bit is "1".

- X : The initial value of this bit is undefined.

Note: Do not write to an address that is "(Disabled)". If a "(Disabled)" address is read, an indeterminate value is returned.

# 15. I/O Ports

## List of port registers

| Register name             | Read/Write | Initial value |           |

|---------------------------|------------|---------------|-----------|

| Port 0 data register      | PDR0       | R, RM/W       | 0b0000000 |

| Port 0 direction register | DDR0       | R/W           | 0b0000000 |

| Port 1 data register      | PDR1       | R, RM/W       | 0b0000000 |

| Port 1 direction register | DDR1       | R/W           | 0b0000000 |

| Port 2 data register      | PDR2       | R, RM/W       | 0b0000000 |

| Port 2 direction register | DDR2       | R/W           | 0b0000000 |

| Port 3 data register      | PDR3       | R, RM/W       | 0b0000000 |

| Port 3 direction register | DDR3       | R/W           | 0b0000000 |

| Port 4 data register      | PDR4       | R, RM/W       | 0b0000000 |

| Port 4 direction register | DDR4       | R/W           | 0b0000000 |

| Port 5 data register      | PDR5       | R, RM/W       | 0b0000000 |

| Port 5 direction register | DDR5       | R/W           | 0b0000000 |

| Port 6 data register      | PDR6       | R, RM/W       | 0b0000000 |

| Port 6 direction register | DDR6       | R/W           | 0b0000000 |

| Port 7 data register      | PDR7       | R, RM/W       | 0b0000000 |

| Port 7 direction register | DDR7       | R/W           | 0b0000000 |

| Port 8 data register      | PDR8       | R, RM/W       | 0b0000000 |

| Port 8 direction register | DDR8       | R/W           | 0b0000000 |

| Port E data register      | PDRE       | R, RM/W       | 0b0000000 |

| Port E direction register | DDRE       | R/W           | 0b0000000 |

| Port F data register      | PDRF       | R, RM/W       | 0b0000000 |

| Port F direction register | DDRF       | R/W           | 0b0000000 |

| Port G data register      | PDRG       | R, RM/W       | 0b0000000 |

| Port G direction register | DDRG       | R/W           | 0b0000000 |

| Port 0 pull-up register   | PUL0       | R/W           | 0b0000000 |

| Port 1 pull-up register   | PUL1       | R/W           | 0b0000000 |

| Port 2 pull-up register   | PUL2       | R/W           | 0b0000000 |

| Port 3 pull-up register   | PUL3       | R/W           | 0b0000000 |

| Port 4 pull-up register   | PUL4       | R/W           | 0b0000000 |

| Port 5 pull-up register   | PUL5       | R/W           | 0b0000000 |

| Port 6 pull-up register   | PUL6       | R/W           | 0b0000000 |

| Port 7 pull-up register   | PUL7       | R/W           | 0b0000000 |

| Port 8 pull-up register   | PUL8       | R/W           | 0b0000000 |

| Port E pull-up register   | PULE       | R/W           | 0b0000000 |

| Port G pull-up register   | PULG       | R/W           | 0b0000000 |

• Correspondence between registers and pins for port 4

|          |   | Correspondence between related register bits and pins |   |   |      |      |      |      |  |  |  |  |  |

|----------|---|-------------------------------------------------------|---|---|------|------|------|------|--|--|--|--|--|

| Pin name | - | -                                                     | - | - | P43  | P42  | P41  | P40  |  |  |  |  |  |

| PDR4     |   |                                                       |   |   |      |      |      |      |  |  |  |  |  |

| DDR4     |   |                                                       |   |   | bit3 | bit2 | bit1 | bit0 |  |  |  |  |  |

| PUL4     | - | -                                                     | - | - | DILO | DILZ | DILI | DILU |  |  |  |  |  |

| AIDRH    |   |                                                       |   |   |      |      |      |      |  |  |  |  |  |

15.5.4 Port 4 operations

Operation as an output port

- A pin becomes an output port if the bit in the DDR4 register corresponding to that pin is set to "1".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When a pin is used as an output port, it outputs the value of the PDR4 register to external pins.

- If data is written to the PDR4 register, the value is stored in the output latch and is output to the pin set as an output port as it is.

- Reading the PDR4 register returns the PDR4 register value.

- Operation as an input port

- A pin becomes an input port if the bit in the DDR4 register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When using a pin shared with the analog input function as an input port, set the corresponding bit in the A/D input disable register (upper) (AIDRH) to "1".

- If data is written to the PDR4 register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDR4 register returns the pin value. However, if the read-modify-write (RMW) type of instruction is used to read the PDR4 register, the PDR4 register value is returned.

- Operation as a peripheral function input pin

- To set a pin as an input port, set the bit in the DDR4 register corresponding to the input pin of a peripheral function to "0".

- When using a pin shared with the analog input function as another peripheral function input pin, configure it as an input port by setting the bit in the AIDRH register corresponding to that pin to "1".

- Reading the PDR4 register returns the pin value, regardless of whether the peripheral function uses that pin as its input pin. However, if the read-modify-write (RMW) type of instruction is used to read the PDR4 register, the PDR4 register value is returned.

- Operation at reset

If the CPU is reset, all bits in the DDR4 register are initialized to "0" and port input is enabled. As for a pin shared with the analog input function, its port input is disabled because the AIDRH register is initialized to "0".

- Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDR4 register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

- Operation as an analog input pin

- Set the bit in the DDR4 register bit corresponding to the analog input pin to "0" and the bit corresponding to that pin

## 15.7.4 Port 6 operations

- Operation as an output port

- A pin becomes an output port if the bit in the DDR6 register corresponding to that pin is set to "1".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When a pin is used as an output port, it outputs the value of the PDR6 register to external pins.

- If data is written to the PDR6 register, the value is stored in the output latch and is output to the pin set as an output port as it is.

- Reading the PDR6 register returns the PDR6 register value.

- · Operation as an input port

- A pin becomes an input port if the bit in the DDR6 register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- If data is written to the PDR6 register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDR6 register returns the pin value. However, if the read-modify-write (RMW) type of instruction is used to read the PDR6 register, the PDR6 register value is returned.

- Operation as a peripheral function output pin

- A pin becomes a peripheral function output pin if the peripheral output function is enabled by setting the output enable bit of a peripheral function corresponding to that pin.

- The pin value can be read from the PDR6 register even if the peripheral function output is enabled. Therefore, the

output value of a peripheral function can be read by the read operation on the PDR6 register. However, if the readmodify-write (RMW) type of instruction is used to read the PDR6 register, the PDR6 register value is returned.

- Operation as a peripheral function input pin

- To set a pin as an input port, set the bit in the DDR6 register corresponding to the input pin of a peripheral function to "0".

- Reading the PDR6 register returns the pin value, regardless of whether the peripheral function uses that pin as its input pin. However, if the read-modify-write (RMW) type of instruction is used to read the PDR6 register, the PDR6 register value is returned.

# Operation at reset If the CPU is reset, all bits in the DDR6 register are initialized to "0" and port input is enabled.

- Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop

mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDR6 register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open. However, if the interrupt input of P65/SCK and P67/SIN is enabled by the external interrupt control register ch. 0 (EIC00)

of the external interrupt circuit and the interrupt pin selection circuit control register (WICR) of the interrupt pin selection circuit, the input is enabled and is not blocked.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

- Operation of the pull-up register

Setting the bit in the PUL6 register to "1" makes the pull-up resistor be internally connected to the pin. When the pin output is "L" level, the pull-up resistor is disconnected regardless of the value of the PUL6 register.

## 15.8.3 Port 7 registers

Port 7 register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                              |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|------------------------------------|--|--|

| PDR7                  | 0    | Pin state is "L" level. | PDR7 value is "0".                          | As output port, outputs "L" level. |  |  |

| FUR                   | 1    | Pin state is "H" level. | PDR7 value is "1".                          | As output port, outputs "H" level. |  |  |

| DDR7                  | 0    | Port input enabled      |                                             |                                    |  |  |

| DDRI                  | 1    |                         | Port output enable                          | d                                  |  |  |

| PUL7                  | 0    |                         | Pull-up disabled                            |                                    |  |  |

| FUL/                  | 1    |                         | Pull-up enabled                             |                                    |  |  |

Correspondence between registers and pins for port 7

|          |   | Correspondence between related register bits and pins |   |   |   |      |      |      |  |  |  |  |  |

|----------|---|-------------------------------------------------------|---|---|---|------|------|------|--|--|--|--|--|

| Pin name | - | -                                                     | - | - | - | P72  | P71  | P70  |  |  |  |  |  |

| PDR7     |   |                                                       |   |   |   |      |      |      |  |  |  |  |  |

| DDR7     | - | -                                                     | - | - | - | bit2 | bit1 | bit0 |  |  |  |  |  |

| PUL7     |   |                                                       |   |   |   |      |      |      |  |  |  |  |  |

## 15.8.4 Port 7 operations

- Operation as an output port

- A pin becomes an output port if the bit in the DDR7 register corresponding to that pin is set to "1".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When a pin is used as an output port, it outputs the value of the PDR7 register to external pins.

- If data is written to the PDR7 register, the value is stored in the output latch and is output to the pin set as an output port as it is.

- Reading the PDR7 register returns the PDR7 register value.

- Operation as an input port

- A pin becomes an input port if the bit in the DDR7 register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- If data is written to the PDR7 register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDR7 register returns the pin value. However, if the read-modify-write (RMW) type of instruction is used to read the PDR7 register, the PDR7 register value is returned.

- Operation as a peripheral function output pin

- A pin becomes a peripheral function output pin if the peripheral output function is enabled by setting the output enable bit of a peripheral function corresponding to that pin.

- The pin value can be read from the PDR7 register even if the peripheral function output is enabled. Therefore, the

output value of a peripheral function can be read by the read operation on the PDR7 register. However, if the readmodify-write (RMW) type of instruction is used to read the PDR7 register, the PDR7 register value is returned.

- Operation as a peripheral function input pin

- To set a pin as an input port, set the bit in the DDR7 register corresponding to the input pin of a peripheral function to "0".

- Reading the PDR7 register returns the pin value, regardless of whether the peripheral function uses that pin as its

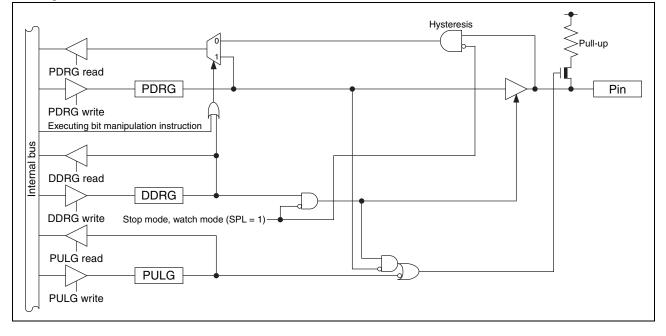

## 15.12 Port G

Port G is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95810K Series Hardware Manual".

## 15.12.1 Port G configuration

- Port G is made up of the following elements.

- General-purpose I/O pins/peripheral function I/O pins

- Port G data register (PDRG)

- Port G direction register (DDRG)

- Port G pull-up register (PULG)

## 15.12.2 Block diagram of port G

- PG1/X0A pin

- This pin has the following peripheral function:

- Subclock input oscillation pin (X0A)

- PG2/X1A pin

- This pin has the following peripheral function:

- Subclock I/O oscillation pin (X1A)

- · Block diagram of PG1/X0A and PG2/X1A

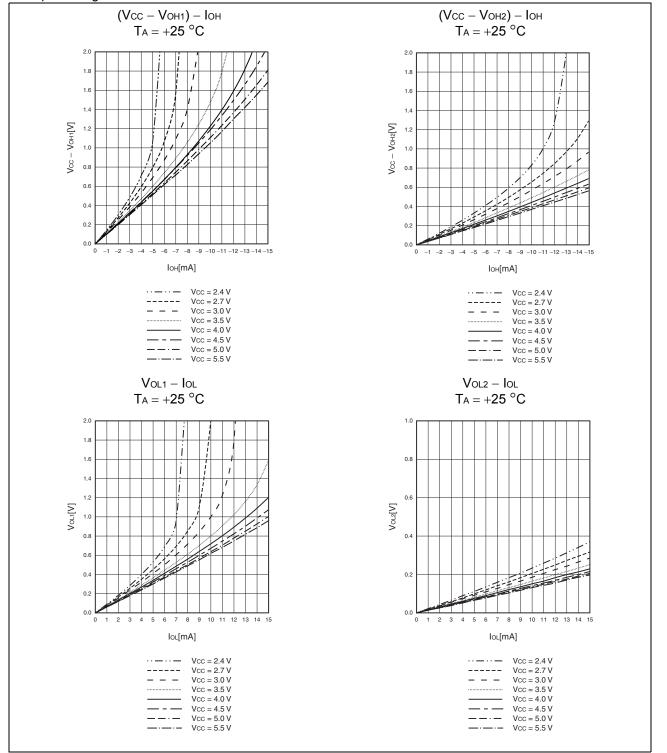

## **18.3 DC Characteristics**

|                                                        |        |                                                      |                    | (100 0    | Value |           |      | , I <sub>A</sub> = –40 °C to +85                     |

|--------------------------------------------------------|--------|------------------------------------------------------|--------------------|-----------|-------|-----------|------|------------------------------------------------------|

| Parameter                                              | Symbol | Pin name                                             | Condition          | Min       | Тур   | Max       | Unit | Remarks                                              |

| <i>"</i>                                               | Vіні   | P10, P50, P51,<br>P67                                |                    | 0.7 Vcc   | _     | Vcc + 0.3 | V    | CMOS input level                                     |

| "H" level<br>input<br>voltage                          | Vins   | Other than P10,<br>P50, P51, P67,<br>PF2             | _                  | 0.8 Vcc   | _     | Vcc + 0.3 | V    | Hysteresis input                                     |

|                                                        | Vінм   | PF2                                                  |                    | 0.8 Vcc   | _     | Vcc + 0.3 | V    | Hysteresis input                                     |

|                                                        | Vili   | P10, P50, P51,<br>P67                                | _                  | Vss - 0.3 |       | 0.3 Vcc   | V    | CMOS input level                                     |

| "L" level<br>input<br>voltage                          | VILS   | Other than P10,<br>P50, P51, P67,<br>PF2             | _                  | Vss – 0.3 | _     | 0.2 Vcc   | V    | Hysteresis input                                     |

|                                                        | VILM   | PF2                                                  |                    | Vss-0.3   | _     | 0.2 Vcc   | V    | Hysteresis input                                     |

| Open-drain<br>output<br>application<br>voltage         | VD     | P12, P50, P51,<br>PF2                                | _                  | Vss – 0.3 |       | Vss + 5.5 | V    |                                                      |

| "H" level<br>output<br>voltage                         | Voh1   | Output pins<br>other than P00<br>to P07, P12,<br>PF2 | Іон <b>=</b> –4 mA | Vcc - 0.5 |       | _         | V    |                                                      |

| -                                                      | Vон2   | P00 to P07                                           | Iон <b>=</b> –8 mA | Vcc-0.5   | —     | —         | V    |                                                      |

| "L" level<br>output<br>voltage                         | Vol1   | Output pins<br>other than P00<br>to P07              | lo∟ = 4 mA         | _         | _     | 0.4       | V    |                                                      |

| vollage                                                | Vol2   | P00 to P07                                           | lo∟ = 12 mA        | —         | _     | 0.4       | V    |                                                      |

| Input leak<br>current (Hi-Z<br>output leak<br>current) | lu     | All input pins                                       | 0.0 V < VI < Vcc   | -5        | _     | +5        | μA   | When the internal<br>pull-up resistor is<br>disabled |

| Internal<br>pull-up<br>resistor                        | Rpull  | Other than P12,<br>P50, P51,<br>PF0 to PF2           | V1 = 0 V           | 25        | 50    | 100       | kΩ   | When the internal pull-up resistor is enabled        |

| Input<br>capacitance                                   | Cin    | Other than<br>AVcc, AVss,<br>AVR, Vcc and<br>Vss     | f = 1 MHz          | _         | 5     | 15        | pF   |                                                      |

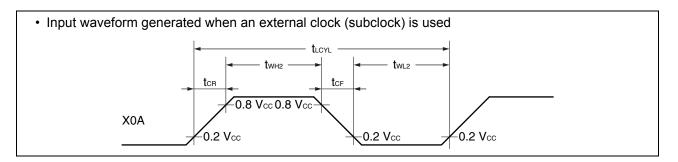

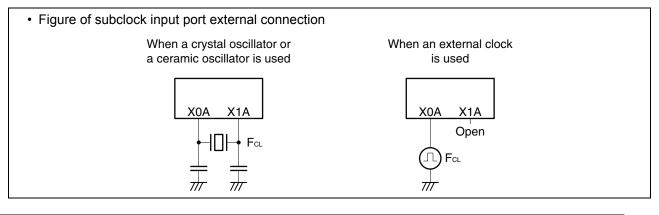

## **18.4 AC Characteristics**

## 18.4.1 Clock Timing

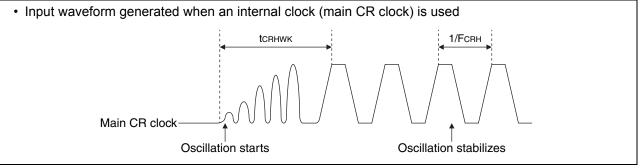

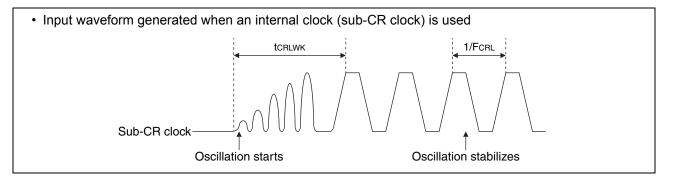

(Vcc = 2.88 V to 5.5 V, Vss = 0.0 V, T<sub>A</sub> = -40 °C to +85 °C)

| Parameter          | Symbol  | Symbol Pin name Condition Value |           | Value |        | l lmit | Domorko |                                                                                                                                                                                                                                                                              |

|--------------------|---------|---------------------------------|-----------|-------|--------|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter          | Symbol  | Pin name                        | Condition | Min   | Тур    | Max    | Unit    | Remarks                                                                                                                                                                                                                                                                      |

|                    | Fсн     | X0, X1                          | —         | 1     | —      | 16.25  | MHz     | When the main oscillation<br>circuit is used                                                                                                                                                                                                                                 |

|                    | ГСН     | X0                              | X1: open  | 1     |        | 12     | MHz     | When the main external clock                                                                                                                                                                                                                                                 |

|                    |         | X0, X1                          | *         | 1     | _      | 32.5   | MHz     | is used                                                                                                                                                                                                                                                                      |

|                    |         |                                 |           | 3.92  | 4      | 4.08   | MHz     | $\begin{array}{l} \mbox{Operating conditions}\\ \bullet \mbox{ The main CR clock is used.}\\ \bullet \mbox{ 0 }^{\circ}\mbox{C} \leq T_A \leq +70 \ ^{\circ}\mbox{C} \end{array}$                                                                                            |

|                    | Ескн    | _                               | _         | 3.8   | 4      | 4.2    | MHz     | $\begin{array}{l} \mbox{Operating conditions}\\ \bullet \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                                                                                                                                |

|                    |         |                                 |           | 7.84  | 8      | 8.16   | MHz     | Operating conditions<br>• PLL multiplication rate: 2<br>• 0 $^{\circ}C \le T_{A} \le +70 \ ^{\circ}C$                                                                                                                                                                        |

|                    |         |                                 |           | 7.6   | 8      | 8.4    | MHz     | $\begin{array}{l} \mbox{Operating conditions}\\ \bullet \mbox{ PLL multiplication rate: 2}\\ \bullet \mbox{ - 40 } ^{\circ}\mbox{C} \leq T_{A} < 0 \ ^{\circ}\mbox{C}, \\ + \mbox{ 70 } ^{\circ}\mbox{C} < T_{A} \leq + \mbox{ 85 } \ ^{\circ}\mbox{C} \end{array}$          |

|                    | -       |                                 |           | 9.8   | 10     | 10.2   | MHz     | Operating conditions<br>• PLL multiplication rate: 2.5<br>• $0 \ ^{\circ}C \le T_{A} \le +70 \ ^{\circ}C$                                                                                                                                                                    |

| Clock<br>frequency |         |                                 |           | 9.5   | 10     | 10.5   | MHz     | $\begin{array}{l} \hline \text{Operating conditions}\\ \bullet \ \text{PLL multiplication rate: 2.5}\\ \bullet \ -40\ ^{\circ}\text{C} \leq \text{T}_{\text{A}} < 0\ ^{\circ}\text{C},\\ +70\ ^{\circ}\text{C} < \text{T}_{\text{A}} \leq +85\ ^{\circ}\text{C} \end{array}$ |

|                    | FMCRPLL |                                 |           | 11.76 | 12     | 12.24  | MHz     | Operating conditions<br>• PLL multiplication rate: 3<br>• $0 \ ^{\circ}C \le T_A \le +70 \ ^{\circ}C$                                                                                                                                                                        |

|                    |         |                                 |           | 11.4  | 12     | 12.6   | MHz     | $\begin{array}{l} \text{Operating conditions} \\ \bullet \ \text{PLL multiplication rate: 3} \\ \bullet \ -40 \ ^{\circ}\text{C} \leq \text{T}_{\text{A}} < 0 \ ^{\circ}\text{C}, \\ +70 \ ^{\circ}\text{C} < \text{T}_{\text{A}} \leq +85 \ ^{\circ}\text{C} \end{array}$   |

|                    |         |                                 |           | 15.68 | 16     | 16.32  | MHz     | Operating conditions<br>• PLL multiplication rate: 4<br>• $0 \ ^{\circ}C \le T_{A} \le +70 \ ^{\circ}C$                                                                                                                                                                      |

|                    |         |                                 |           | 15.2  | 16     | 16.8   | MHz     | $\begin{array}{l} \mbox{Operating conditions}\\ \bullet \mbox{ PLL multiplication rate: 4}\\ \bullet \mbox{ - 40 }^{\circ}\mbox{C} \leq T_A < 0 \;^{\circ}\mbox{C},\\ + \; 70 \;^{\circ}\mbox{C} < T_A \leq + \; 85 \;^{\circ}\mbox{C} \end{array}$                          |

|                    | Fc∟     | X0A, X1A                        | _         | _     | 32.768 | _      | kHz     | When the suboscillation<br>circuit is used                                                                                                                                                                                                                                   |

|                    |         | ΛυΑ, ΛΙΑ                        |           | _     | 32.768 | _      | kHz     | When the sub-external clock is used                                                                                                                                                                                                                                          |

|                    | FCRL    |                                 | _         | 50    | 100    | 150    | kHz     | When the sub-CR clock is<br>used                                                                                                                                                                                                                                             |

## 18.4.2 Source Clock/Machine Clock

(Vcc = 5.0 V±10%, Vss = 0.0 V, T<sub>A</sub> = -40 °C to +85 °C)

| Parameter                    | Symbol        | Pin  |       | Value  |         | Unit  | Remarks                                 |

|------------------------------|---------------|------|-------|--------|---------|-------|-----------------------------------------|

| i arameter                   | Symbol        | name | Min   | Тур    | Max     | Onit  | Remarks                                 |

|                              |               |      |       |        |         |       | When the main external clock is used    |

|                              |               |      | 61.5  |        | 2000    | ns    | Min: Fcн = 32.5 MHz, divided by 2       |

|                              |               |      |       |        |         |       | Max: Fcн = 1 MHz, divided by 2          |

|                              |               |      |       |        |         |       | When the main CR clock is used          |

| Source clock<br>cycle time*1 | tsclk         | _    | 62.5  |        | 1000    | ns    | Min: FCRH = 4 MHz, multiplied by 4      |

|                              | LOOLIN        |      |       |        |         |       | Max: FCRH = 4 MHz, divided by 4         |

|                              |               |      |       | 61     |         | μs    | When the suboscillation clock is used   |

|                              |               |      |       | 01     |         | μο    | FcL = 32.768 kHz, divided by 2          |

|                              |               |      |       | 20     |         | μs    | When the sub-CR clock is used           |

|                              |               |      |       | 20     |         | -     | FCRL = 100 kHz, divided by 2            |

|                              | Esp           |      | 0.5   |        | 16.25   |       | When the main oscillation clock is used |

| Source clock                 | I SP          |      | _     | 4      | 12.5    | MHz   | When the main CR clock is used          |

| frequency                    | Fspl          | —    | _     | 16.384 | _       | kHz   | When the suboscillation clock is used   |

|                              |               |      |       | 50     | —       | kHz   | When the sub-CR clock is used           |

|                              |               |      |       |        |         | KI IZ | FCRL = 100 kHz, divided by 2            |

|                              |               |      |       |        | 32000   |       | When the main oscillation clock is used |

|                              |               |      | 61.5  | —      |         |       | Min: Fsp = 16.25 MHz, no division       |

|                              |               |      |       |        |         |       | Max: Fsp = 0.5 MHz, divided by 16       |

| Machine clock                |               |      |       |        |         |       | When the main CR clock is used          |

| cycle time*2                 |               |      | 250   |        | 4000    | ns    | Min: Fsp = 4 MHz, no division           |

| (minimum                     | <b>t</b> MCLK |      |       |        |         |       | Max: Fsp = 4 MHz, divided by 16         |

| instruction                  | LINCLK        |      |       |        |         |       | When the suboscillation clock is used   |

| execution time)              |               |      | 61    |        | 976.5   | μs    | Min: Fspl = 16.384 kHz, no division     |

|                              |               |      |       |        |         |       | Max: Fspl = 16.384 kHz, divided by 16   |

|                              |               |      |       |        |         |       | When the sub-CR clock is used           |

|                              |               |      | 20    |        | 320     | μs    | Min: Fspl = 50 kHz, no division         |

|                              |               |      |       |        |         |       | Max: Fspl = 50 kHz, divided by 16       |

|                              | Fмр           |      | 0.031 |        | 16.25   | MHz   |                                         |

| Machine clock                |               |      | 0.25  |        | 16      | MHz   | When the main CR clock is used          |

| frequency                    |               | —    | 1.024 |        | 16.384  | kHz   |                                         |

| nequency                     | FMPL          |      | 3.125 |        | – 50 kH |       | When the sub-CR clock is used           |

|                              |               |      | 5.125 |        | 50      |       | FCRL = 100 kHz                          |

\*1: This is the clock before it is divided according to the division ratio set by the machine clock division ratio select bits (SYCC:DIV[1:0]). This source clock is divided to become a machine clock according to the division ratio set by the machine clock division ratio select bits (SYCC:DIV[1:0]). In addition, a source clock can be selected from the following.

- · Main clock divided by 2

- Main CR clock

- PLL multiplication of main CR clock (Select a multiplication rate from 2, 2.5, 3 and 4.)

- Subclock divided by 2

- Sub-CR clock divided by 2

\*2: This is the operating clock of the microcontroller. A machine clock can be selected from the following.

- Source clock (no division)

- Source clock divided by 4

- Source clock divided by 8

- Source clock divided by 16

| Denne                                                                   | <b>.</b>        | Pin          | 0                                        | Val                    |                        | 10  v,  TA = -40  C t |                                                                                                                                                                                                  |  |

|-------------------------------------------------------------------------|-----------------|--------------|------------------------------------------|------------------------|------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                         | Symbol          | name         | Condition                                | Min                    | Max                    | Unit                  | Remarks                                                                                                                                                                                          |  |

| SCL clock<br>"L" width                                                  | <b>t</b> LOW    | SCL          |                                          | (2 + nm/2)tмськ – 20   | _                      | ns                    | Master mode                                                                                                                                                                                      |  |

| SCL clock<br>"H" width                                                  | <b>t</b> high   | SCL          |                                          | (nm/2)tмськ – 20       | (nm/2)tмськ + 20       | ns                    | Master mode                                                                                                                                                                                      |  |

| START<br>condition<br>hold time                                         | thd;sta         | SCL,<br>SDA0 | -<br>-<br>-<br>- R = 1.7 kΩ,             | (-1 + nm/2)tмськ – 20  | (-1 + nm)tмськ + 20    | ns                    | Master mode<br>Maximum value<br>is applied when<br>m, n = 1, 8.<br>Otherwise, the<br>minimum value is<br>applied.                                                                                |  |

| STOP<br>condition<br>setup time                                         | <b>t</b> su;sто | SCL,<br>SDA  |                                          | (1 + nm/2)tмськ – 20   | (1 + nm/2)tмськ + 20   | ns                    | Master mode                                                                                                                                                                                      |  |

| START<br>condition<br>setup time                                        | tsu;sta         | SCL,<br>SDA  |                                          | (1 + nm/2)tмськ – 20   | (1 + nm/2)tмськ + 20   | ns                    | Master mode                                                                                                                                                                                      |  |

| Bus free time<br>between<br>STOP<br>condition<br>and START<br>condition | <b>t</b> BUF    | SCL,<br>SDA  |                                          |                        | (2 nm + 4) tмськ – 20  | _                     | ns                                                                                                                                                                                               |  |

| Data hold<br>time                                                       | <b>t</b> hd;dat | SCL,<br>SDA  | R = 1.7  KS2,<br>C = 50 pF <sup>*1</sup> | 3 tмс∟к – 20           | _                      | ns                    | Master mode                                                                                                                                                                                      |  |

| Data setup<br>time                                                      | tsu;dat         | SCL,<br>SDA  |                                          | (-2 + nm/2) tмс∟к – 20 | (-1 + nm/2) tмс∟к + 20 | ns                    | Master mode<br>It is assumed that<br>"L" of SCL is not<br>extended. The<br>minimum value is<br>applied to the first<br>bit of continuous<br>data. Otherwise,<br>the maximum<br>value is applied. |  |

| Setup time<br>between<br>clearing<br>interrupt and<br>SCL rising        | tsu;int         | SCL          |                                          | (nm/2) tмськ – 20      | (1 + nm/2) tмськ + 20  | ns                    | The minimum<br>value is applied<br>to the interrupt at<br>the ninth SCL $\downarrow$ .<br>The maximum<br>value is applied<br>to the interrupt at<br>the eighth SCL $\downarrow$ .                |  |

| SCL clock<br>"L" width                                                  | <b>t</b> LOW    | SCL          |                                          | 4 tmclk – 20           | _                      | ns                    | At reception                                                                                                                                                                                     |  |

| SCL clock<br>"H" width                                                  | tніgн           | SCL          |                                          | 4 tmclk – 20           | —                      | ns                    | At reception                                                                                                                                                                                     |  |

(Vcc = 5.0 V±10%, Vss = 0.0 V, T<sub>A</sub> = -40 °C to +85 °C)

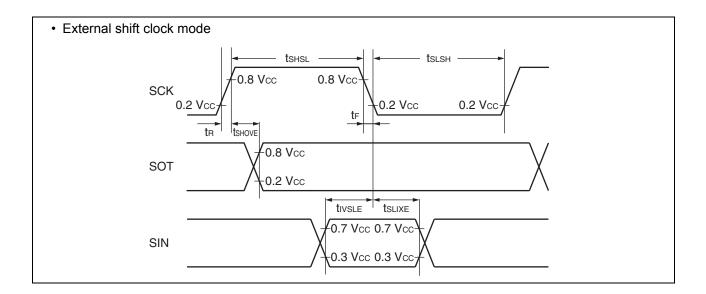

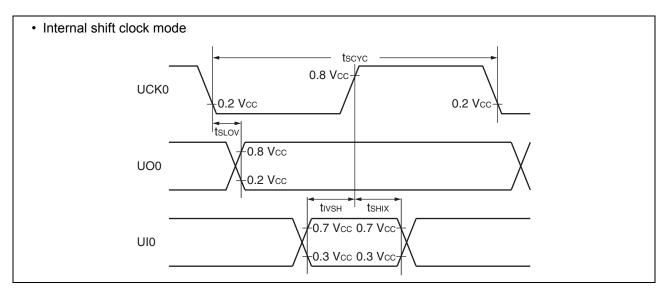

## 18.4.9 UART/SIO, Serial I/O Timing

| Parameter                                     | Symbol Pin name |           | Condition                | Va               | Unit |      |

|-----------------------------------------------|-----------------|-----------|--------------------------|------------------|------|------|

| Farailleter                                   | Symbol          | Fininanie | Condition                | Min              | Мах  | Unit |

| Serial clock cycle time                       | tscyc           | UCK0      |                          | <b>4 t</b> мськ* | —    | ns   |

| $UCK \downarrow \rightarrow UO$ time          | tslov           | UCK0, UO0 | Internal clock operation | -190             | +190 | ns   |

| Valid UI $\rightarrow$ UCK $\uparrow$         | tivsh           | UCK0, UI0 |                          | <b>2 t</b> мськ* | -    | ns   |

| UCK $\uparrow \rightarrow$ valid UI hold time | tsнix           | UCK0, UI0 |                          | 2 tmclk*         | _    | ns   |

| Serial clock "H" pulse width                  | ts∺s∟           | UCK0      |                          | <b>4 t</b> мськ* | -    | ns   |

| Serial clock "L" pulse width                  | tslsh           | UCK0      |                          | <b>4 t</b> мськ* | -    | ns   |

| UCK $\downarrow \rightarrow$ UO time          | tslov           | UCK0, UO0 | External clock operation | —                | 190  | ns   |

| Valid UI $\rightarrow$ UCK $\uparrow$         | tivsh           | UCK0, UI0 |                          | <b>2 t</b> мськ* | —    | ns   |

| UCK $\uparrow \rightarrow$ valid UI hold time | tsнıx           | UCK0, UI0 |                          | 2 <b>t</b> MCLK* |      | ns   |

\*: See "Source Clock/Machine Clock" for tMCLK.

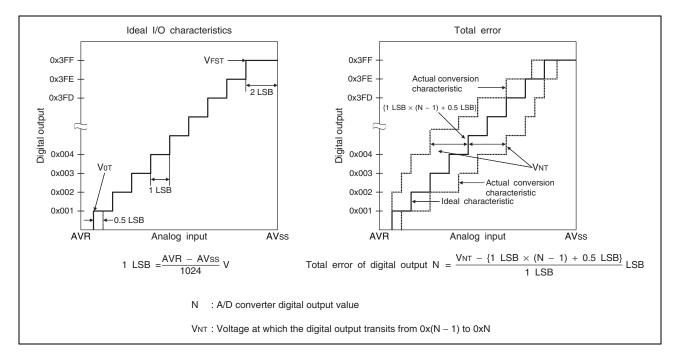

#### 18.5.3 Definitions of A/D Converter Terms

Resolution

٠

It indicates the level of analog variation that can be distinguished by the A/D converter.

When the number of bits is 10, analog voltage can be divided into  $2^{10} = 1024$ .

• Linearity error (unit: LSB)

It indicates how much an actual conversion value deviates from the straight line connecting the zero transition point ("000000000"  $\leftarrow \rightarrow$  "0000000001") of a device to the full-scale transition point ("1111111111"  $\leftarrow \rightarrow$  "111111110") of the same device.

• Differential linear error (unit: LSB)

It indicates how much the input voltage required to change the output code by 1 LSB deviates from an ideal value. Total error (unit: LSB)

It indicates the difference between an actual value and a theoretical value. The error can be caused by a zero transition error, a full-scale transition errors, a linearity error, a quantum error, or noise.

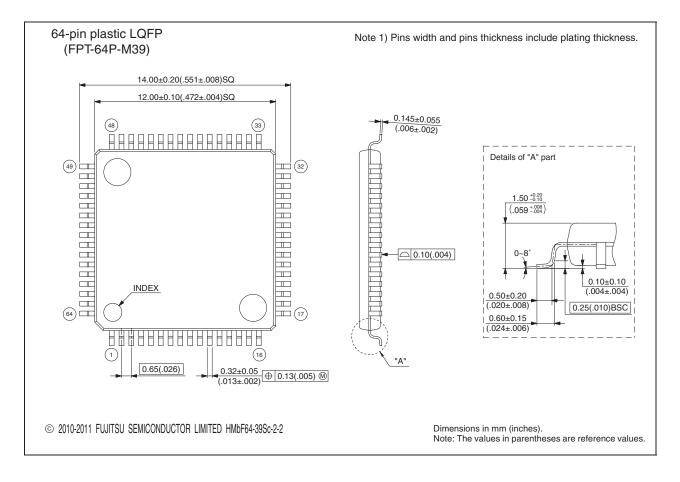

## · Output voltage characteristics

| 64-pin plastic LQFP | Lead pitch                            | 0.65 mm             |

|---------------------|---------------------------------------|---------------------|

|                     | Package width $\times$ package length | 12.00 mm × 12.00 mm |

|                     | Lead shape                            | Gullwing            |

|                     | Sealing method                        | Plastic mold        |

|                     | Mounting height                       | 1.70 mm MAX         |

|                     | Weight                                | 0.47 g              |

| (FPT-64P-M39)       |                                       |                     |

# **Document History Page**

| Document Title: MB95810K Series, New 8FX 8-bit Microcontrollers<br>Document Number: 002-04694 |         |                    |                    |                                                                                                          |  |

|-----------------------------------------------------------------------------------------------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------|--|

| Revision                                                                                      | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                    |  |

| **                                                                                            | -       | AKIH               | 05/27/2013         | Migrated to Cypress and assigned document number 002-08453.<br>No change to document contents or format. |  |

| *A                                                                                            | 5193921 | AKIH               | 03/29/2016         | Updated to Cypress template<br>Added MB95F818KPMC-G-UNE2 in "Ordering Information".                      |  |

| *В                                                                                            | 5845951 | YSAT               | 08/07/2017         | Adapted new Cypress logo                                                                                 |  |