Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 6MHz                                                         |

| Connectivity               | SCI, USB                                                     |

| Peripherals                | LED, LVD, POR, PWM                                           |

| Number of I/O              | 21                                                           |

| Program Memory Size        | 16KB (16K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 384 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                    |

| Data Converters            | -                                                            |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 32-LQFP                                                      |

| Supplier Device Package    | 32-LQFP (7x7)                                                |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908jb16fa |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

## **Section 1. General Description**

| 1.1    | Contents                                                                          |

|--------|-----------------------------------------------------------------------------------|

| 1.2    | Introduction                                                                      |

| 1.3    | Features                                                                          |

| 1.4    | MCU Block Diagram                                                                 |

| 1.5    | Pin Assignments                                                                   |

| 1.6    | Pin Functions                                                                     |

| 1.6.1  | Power Supply Pins (V <sub>DD</sub> , V <sub>SS</sub> )                            |

| 1.6.2  | Voltage Regulator Output Pin (V <sub>REG</sub> )                                  |

| 1.6.3  | Oscillator Pins (OSC1 and OSC2)                                                   |

| 1.6.4  | External Reset Pin (RST)35                                                        |

| 1.6.5  | External Interrupt Pins (IRQ, PTE4/D-)                                            |

| 1.6.6  | CGM Power Supply Pins (V <sub>DDA</sub> , V <sub>SSA0</sub> , V <sub>SSA1</sub> ) |

| 1.6.7  | CGM Voltage Regulator Out (V <sub>REGA0</sub> )                                   |

| 1.6.8  | CGM Voltage Regulator In (V <sub>REGA1</sub> )                                    |

| 1.6.9  | External Filter Capacitor Pins (CGMXFC1, CGMXFC2)36                               |

| 1.6.10 | CGM Clock Output Pins (CGMOUT1, CGMOUT2)36                                        |

| 1.6.11 | Port A Input/Output (I/O) Pins (PTA7/KBA7–PTA0/KBA0)36                            |

| 1.6.12 | Port C I/O Pins (PTC1/RxD, PTC0/TxD)37                                            |

| 1.6.13 | B Port D I/O Pins (PTD5–PTD0)                                                     |

| 1.6.14 | Port E I/O Pins (PTE4/D–, PTE3/D+, PTE2/T2CH01,                                   |

|        | PTE1/T1CH01, PTE0/TCLK)                                                           |

## Section 2. Memory Map

| 2.1 | Contents                       |

|-----|--------------------------------|

| 2.2 | Introduction                   |

| 2.3 | Unimplemented Memory Locations |

MC68HC908JB16 - Rev. 1.1

| Addr.           | Register Name                                         |                 | Bit 7                   | 6            | 5         | 4          | 3          | 2      | 1          | Bit 0  |

|-----------------|-------------------------------------------------------|-----------------|-------------------------|--------------|-----------|------------|------------|--------|------------|--------|

|                 | IRQ Status and Control                                | Read:           | 0                       | 0            | 0         | 0          | IRQF       | 0      |            | MODE   |

| \$001E          | Register                                              | Write:          |                         |              |           |            |            | ACK    | IMASK      | MODE   |

|                 | (INTSCR)                                              | Reset:          | 0                       | 0            | 0         | 0          | 0          | 0      | 0          | 0      |

| \$001F          | Configuration Register<br>(CONFIG) <sup>†</sup>       | Read:<br>Write: | LVIDR                   | LVI5OR3      | URSTD     | LVID       | SSREC      | COPRS  | STOP       | COPD   |

|                 | (0001110)                                             | Reset:          | 0*                      | 0*           | 0*        | 0*         | 0          | 0      | 0          | 0      |

| •               | e writable register after ea<br>VI5OR3, URSTD, and LV |                 |                         | R or LVI res | set only. |            |            |        |            |        |

|                 | USB Endpoint 0 Data                                   |                 | UE0R07                  | UE0R06       | UE0R05    | UE0R04     | UE0R03     | UE0R02 | UE0R01     | UE0R00 |

| \$0020          | Register 0                                            |                 | UE0T07                  | UE0T06       | UE0T05    | UE0T04     | UE0T03     | UE0T02 | UE0T01     | UE0T00 |

| (UE0D0)         | Reset:                                                |                 |                         |              | Unaffecte | d by reset |            |        |            |        |

|                 | USB Endpoint 0 Data                                   | Read:           | UE0R17                  | UE0R16       | UE0R15    | UE0R14     | UE0R13     | UE0R12 | UE0R11     | UE0R10 |

| \$0021          | D21 Register 1                                        |                 | UE0T17                  | UE0T16       | UE0T15    | UE0T14     | UE0T13     | UE0T12 | UE0T11     | UE0T10 |

|                 | (UE0D1)                                               | Reset:          |                         |              |           | Unaffecte  | d by reset |        |            |        |

|                 | USB Endpoint 0 Data                                   | Read:           | UE0R27                  | UE0R26       | UE0R25    | UE0R24     | UE0R23     | UE0R22 | UE0R21     | UE0R20 |

| \$0022 Register | Register 2                                            | Write:          | UE0T27                  | UE0T26       | UE0T25    | UE0T24     | UE0T23     | UE0T22 | UE0T21     | UE0T20 |

|                 | (UE0D2)                                               | Reset:          | et: Unaffected by reset |              |           |            |            |        |            |        |

|                 | USB Endpoint 0 Data                                   | Read:           | UE0R37                  | UE0R36       | UE0R35    | UE0R34     | UE0R33     | UE0R32 | UE0R31     | UE0R30 |

| \$0023          | Register 3                                            | Write:          | UE0T37                  | UE0T36       | UE0T35    | UE0T34     | UE0T33     | UE0T32 | UE0T31     | UE0T30 |

|                 | (UE0D3)                                               | Reset:          | t: Unaffected by reset  |              |           |            |            |        |            |        |

|                 | USB Endpoint 0 Data                                   | Read:           | UE0R47                  | UE0R46       | UE0R45    | UE0R44     | UE0R43     | UE0R42 | UE0R41     | UE0R40 |

| \$0024          | Register 4                                            | Write:          | UE0T47                  | UE0T46       | UE0T45    | UE0T44     | UE0T43     | UE0T42 | UE0T41     | UE0T40 |

|                 | (UE0D4)                                               | Reset:          | Unaffected by reset     |              |           |            |            |        |            |        |

|                 | USB Endpoint 0 Data                                   | Read:           | UE0R57                  | UE0R56       | UE0R55    | UE0R54     | UE0R53     | UE0R52 | UE0R51     | UE0R50 |

| \$0025          | Register 5                                            | Write:          | UE0T57                  | UE0T56       | UE0T55    | UE0T54     | UE0T53     | UE0T52 | UE0T51     | UE0T50 |

|                 | (UE0D5)                                               | Reset:          |                         |              |           | Unaffecte  | d by reset |        |            |        |

|                 | USB Endpoint 0 Data                                   | Read:           | UE0R67                  | UE0R66       | UE0R65    | UE0R64     | UE0R63     | UE0R62 | UE0R61     | UE0R60 |

| \$0026          | Register 6                                            | Write:          | UE0T67                  | UE0T66       | UE0T65    | UE0T64     | UE0T63     | UE0T62 | UE0T61     | UE0T60 |

|                 | (UE0D6)                                               | Reset:          |                         |              |           | Unaffecte  | d by reset |        |            |        |

|                 | USB Endpoint 0 Data                                   | Read:           | UE0R77                  | UE0R76       | UE0R75    | UE0R74     | UE0R73     | UE0R72 | UE0R71     | UE0R70 |

| \$0027          | Register 7                                            | Write:          | UE0T77                  | UE0T76       | UE0T75    | UE0T74     | UE0T73     | UE0T72 | UE0T71     | UE0T70 |

|                 | (UE0D7)                                               | Reset:          |                         |              |           | Unaffecte  | d by reset |        |            |        |

|                 | U = Unaffected                                        |                 | X = Indeter             | minate       |           | = Unimpler | nented     | R      | = Reserved | ł      |

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 12)

MC68HC908JB16 - Rev. 1.1

# NP

Memory Map

| Addr.                            | Register Name                                         |                           | Bit 7   | 6       | 5      | 4          | 3      | 2      | 1          | Bit 0  |

|----------------------------------|-------------------------------------------------------|---------------------------|---------|---------|--------|------------|--------|--------|------------|--------|

| \$0050                           | Reserved                                              | Read:<br>Write:<br>Reset: | R       | R       | R      | R          | R      | R      | R          | R      |

|                                  |                                                       |                           |         |         |        |            |        |        |            |        |

| \$0051                           | PLL Bandwidth Control                                 |                           | R       | LOCK1   | R      | PLLON1     | R      | LOCK2  | R          | PLLON2 |

|                                  |                                                       |                           |         | 0       |        | 0          | L      | 0      |            | 0      |

| \$0052                           | VCO Control Register<br>(PVCR)                        | Read:<br>Write:           | VCO_7   | VCO_6   | VCO_5  | VCO_4      | VCO_3  | VCO_2  | VCO_1      | VCO_0  |

|                                  |                                                       | Reset:                    | 0       | 0       | 1      | 1          | 0      | 0      | 0          | 0      |

| \$0053                           |                                                       |                           | VDS1_11 | VDS1_10 | VDS1_9 | VDS1_8     | 0      | 0      | RDS1_9     | RDS1_8 |

|                                  | (PNRH1)                                               | Reset:                    | 0       | 0       | 1      | 0          | 0      | 0      | 0          | 0      |

| \$0054                           | PLL1 N Divider Select<br>Register Low                 | Read:<br>Write:<br>Reset: | VDS1_7  | VDS1_6  | VDS1_5 | VDS1_4     | VDS1_3 | VDS1_2 | VDS1_1     | VDS1_0 |

|                                  | (PNSL1)                                               |                           | 0       | 1       | 1      | 1          | 1      | 1      | 0          | 1      |

| \$0055                           | PLL1 R Divider Select<br>0055 Register Low<br>(PRSL1) |                           | RDS1_7  | RDS1_6  | RDS1_5 | RDS1_4     | RDS1_3 | RDS1_2 | RDS1_1     | RDS1_0 |

|                                  |                                                       |                           | 1       | 0       | 0      | 1          | 0      | 0      | 0          | 0      |

| \$0056                           | PLL2 N & R Divider Select<br>Register High            | Read:<br>Write:           | VDS2_11 | VDS2_10 | VDS2_9 | VDS2_8     | 0      | 0      | RDS2_9     | RDS2_8 |

|                                  | (PNRH2)                                               | Reset:                    | 0       | 0       | 1      | 0          | 0      | 0      | 0          | 0      |

| \$0057                           | PLL2 N Divider Select<br>Register Low                 | Read:<br>Write:           | VDS2_7  | VDS2_6  | VDS2_5 | VDS2_4     | VDS2_3 | VDS2_2 | VDS2_1     | VDS2_0 |

|                                  | (PNSL1)                                               | Reset:                    | 0       | 1       | 1      | 1          | 1      | 1      | 0          | 1      |

| \$0058                           | PLL2 R Divider Select<br>Register Low                 | Read:<br>Write:           | RDS2_7  | RDS2_6  | RDS2_5 | RDS2_4     | RDS2_3 | RDS2_2 | RDS2_1     | RDS2_0 |

|                                  | (PRSL2)                                               | Reset:                    | 1       | 0       | 0      | 1          | 0      | 0      | 0          | 0      |

| \$0059                           | Phase Detector Control<br>Register                    |                           | PHD_7   | PHD_6   | PHD_5  | PHD_4      | PHD_3  | PHD_2  | PHD_1      | PHD_0  |

|                                  | (PDCR)                                                | Reset:                    | 1       | 0       | 0      | 1          | 0      | 0      | 0          | 0      |

| U = Unaffected X = Indeterminate |                                                       |                           |         |         |        | = Unimpler | nented | R      | = Reserved | 1      |

| Description      | Write to last address accessed + 1 |  |  |  |  |  |  |

|------------------|------------------------------------|--|--|--|--|--|--|

| Operand          | Operand Specifies single data byte |  |  |  |  |  |  |

| Data<br>Returned | None                               |  |  |  |  |  |  |

| Opcode           | \$19                               |  |  |  |  |  |  |

|                  | Command Sequence                   |  |  |  |  |  |  |

|                  | SENT TO<br>MONITOR                 |  |  |  |  |  |  |

### Table 9-7. IWRITE (Indexed Write) Command

**NOTE:** A sequence of IREAD or IWRITE commands can sequentially access a block of memory over the full 64k-byte memory map.

| Reads stack pointer                                       |  |  |  |  |  |  |

|-----------------------------------------------------------|--|--|--|--|--|--|

| None                                                      |  |  |  |  |  |  |

| Returns stack pointer in high byte:low byte order         |  |  |  |  |  |  |

| \$0C                                                      |  |  |  |  |  |  |

| Command Sequence                                          |  |  |  |  |  |  |

| SENT TO<br>MONITOR                                        |  |  |  |  |  |  |

|                                                           |  |  |  |  |  |  |

| K READSP K SP K SP K   ECHO ECHO ECHO ECHO ECHO ECHO ECHO |  |  |  |  |  |  |

|                                                           |  |  |  |  |  |  |

## 10.10 I/O Registers

**NOTE:** References to either timer 1 or timer 2 may be made in the following text by omitting the timer number. For example, TSC may generically refer to both T1SC and T2SC.

These I/O registers control and monitor operation of the TIM:

- TIM status and control register (TSC)

- TIM counter registers (TCNTH:TCNTL)

- TIM counter modulo registers (TMODH:TMODL)

- TIM channel status and control registers (TSC0, TSC1)

- TIM channel registers (TCH0H:TCH0L, TCH1H:TCH1L)

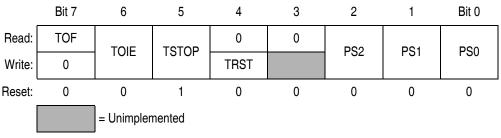

#### 10.10.1 TIM Status and Control Register

The TIM status and control register (TSC):

- Enables TIM overflow interrupts

- Flags TIM overflows

- Stops the TIM counter

- Resets the TIM counter

- Prescales the TIM counter clock

Address: T1SC, \$000A and T2SC, \$0040

Figure 10-4. TIM Status and Control Register (TSC)

#### 11.5.4 Resume After Suspend

The MCU can be activated from the suspend state by normal bus activity, a USB reset signal, or by a forced resume driven from the MCU.

#### 11.5.4.1 Host Initiated Resume

The host signals resume by initiating resume signalling (K state) for at least 20ms followed by a standard low-speed EOP signal. This 20ms ensures that all devices in the USB network are awakened.

After resuming the bus, the host must begin sending bus traffic within 3ms to prevent the device from re-entering suspend mode.

#### 11.5.4.2 USB Reset Signalling

Reset can wake a device from the suspended mode.

#### 11.5.4.3 Remote Wakeup

The MCU also supports the remote wakeup feature. The firmware has the ability to exit suspend mode by signaling a resume state to the upstream host or hub. A non-idle state (K state) on the USB data lines is accomplished by asserting the FRESUM bit in the UCR1 register.

When using the remote wakeup capability, the firmware must wait for at least 5ms after the bus is in the idle state before sending the remote wakeup resume signaling. This allows the upstream devices to get into their suspend state and prepare for propagating resume signaling. The FRESUM bit should be asserted to cause the resume state on the USB data lines for at least 10ms, but not more than 15ms. Note that the resume signalling is controlled by the FRESUM bit and meeting the timing specifications is dependent on the firmware. When FRESUM is cleared by firmware, the data lines will return to their high-impedance state.

Refer to register definitions (see **11.8.6 USB Control Register 1**) for more information about how the force resume (FRESUM) bit can be used to initiate the remote wakeup feature.

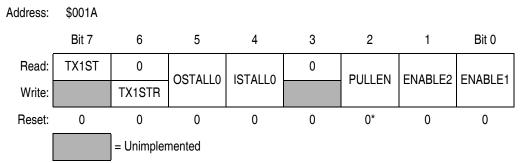

### 11.8.8 USB Control Register 3

\* PULLEN bit is reset by POR or LVI reset only.

#### Figure 11-22. USB Control Register 3 (UCR3)

TX1ST — Endpoint 0 Transmit First Flag

This read-only bit is set if the endpoint 0 data transmit flag (TXD0F) is set when the USB control logic is setting the endpoint 0 data receive flag (RXD0F). In other words, if an unserviced endpoint 0 transmit flag is still set at the end of an endpoint 0 reception, then this bit will be set. This bit lets the firmware know that the endpoint 0 transmission happened before the endpoint 0 reception.

Reset clears this bit.

1 = IN transaction occurred before SETUP/OUT

0 = IN transaction occurred after SETUP/OUT

TX1STR — Clear Endpoint 0 Transmit First Flag

Writing a logic 1 to this write-only bit will clear the TX1ST bit if it is set. Writing a logic 0 to the TX1STR has no effect. Reset clears this bit.

OSTALL0 — Endpoint 0 Force STALL Bit for OUT token

This read/write bit causes endpoint 0 to return a STALL handshake when polled by an OUT token by the USB host controller. The USB hardware clears this bit when a SETUP token is received. Reset clears this bit.

1 = Send STALL handshake

0 = Default

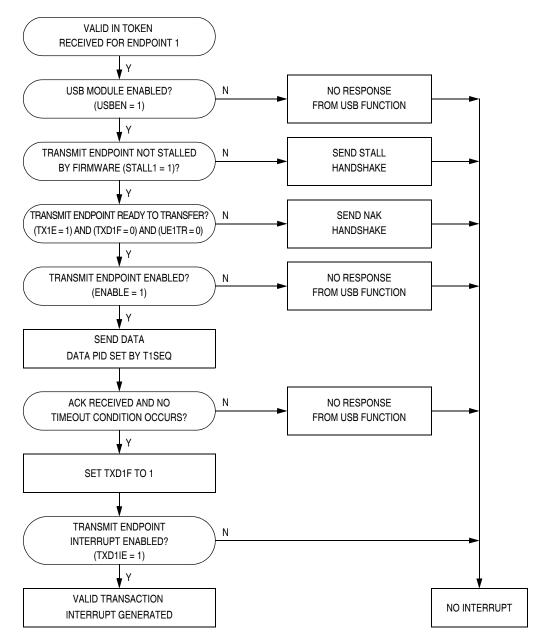

### 11.9.1.3 Transmit Endpoint 1

For an IN transaction directed at endpoint 1, the USB module will generate an interrupt by setting the TXD1F in the UIR1 register. The conditions necessary for the interrupt to occur are shown in **Figure 11-32**.

MC68HC908JB16 - Rev. 1.1

## Serial Communications Interface

Address: \$005A

|        | Bit 7 | 6     | 5     | 4 | 3    | 2    | 1   | Bit 0 |

|--------|-------|-------|-------|---|------|------|-----|-------|

| Read:  | LOOPS | ENSCI | TXINV | М | WAKE | ILTY | PEN | ΡΤΥ   |

| Write: |       |       |       |   |      |      |     |       |

| Reset: | 0     | 0     | 0     | 0 | 0    | 0    | 0   | 0     |

Figure 12-9. SCI Control Register 1 (SCC1)

LOOPS - Loop Mode Select Bit

This read/write bit enables loop mode operation. In loop mode the RxD pin is disconnected from the SCI, and the transmitter output goes into the receiver input. Both the transmitter and the receiver must be enabled to use loop mode. Reset clears the LOOPS bit.

- 1 = Loop mode enabled

- 0 = Normal operation enabled

- ENSCI Enable SCI Bit

This read/write bit enables the SCI and the SCI baud rate generator. Clearing ENSCI sets the SCTE and TC bits in SCI status register 1 and disables transmitter interrupts. Reset clears the ENSCI bit.

- 1 = SCI enabled

- 0 = SCI disabled

- TXINV Transmit Inversion Bit

This read/write bit reverses the polarity of transmitted data. Reset clears the TXINV bit.

- 1 = Transmitter output inverted

- 0 = Transmitter output not inverted

- **NOTE:** Setting the TXINV bit inverts all transmitted values, including idle, break, start, and stop bits.

**Technical Data**

MC68HC908JB16 - Rev. 1.1

### 12.9.6 SCI Data Register

The SCI data register (SCDR) is the buffer between the internal data bus and the receive and transmit shift registers.

| Address: | \$005F              |    |    |    |    |    |    |       |

|----------|---------------------|----|----|----|----|----|----|-------|

|          | Bit 7               | 6  | 5  | 4  | 3  | 2  | 1  | Bit 0 |

| Read:    | R7                  | R6 | R5 | R4 | R3 | R2 | R1 | R0    |

| Write:   | T7                  | T6 | T5 | T4 | Т3 | T2 | T1 | Т0    |

| Reset:   | Unaffected by reset |    |    |    |    |    |    |       |

Figure 12-15. SCI Data Register (SCDR)

R7/T7-R0/T0 — Receive/Transmit Data Bits

Reading the SCI data register accesses the read-only received data bits, R7:R0. Writing to the SCI data register writes the data to be transmitted, T7:T0. Reset has no effect on the SCI data register.

**NOTE:** Do not use read/modify/write instructions on the SCI data register.

Clock Generator Module (CGM)

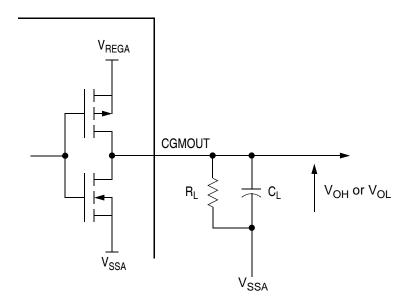

## 13.6 CGMOUT External Connections

The output of CGM clock is a standard CMOS output with push-pull configuration. The output logic high and low levels are specified with corresponding DC loading current (see **20.13 CGM Electrical Characteristics**). The transient current is mainly determined by the maximum loading capacitor value.

Figure 13-5. CGMOUT External Connections

## 13.7 Calculation of VCO Frequency

The relationship between the VCO frequency,  $f_{VCLK},$  and the crystal reference frequency,  $f_{XCLK},$  is:

$$f_{VCLK} = \frac{N}{R} \times f_{XCLK}$$

MC68HC908JB16 - Rev. 1.1

### 13.9.6 Phase Detector Control Register (PDCR)

The phase detector control register configures the phase detector for both PLLs.

| Address: | \$0059 |

|----------|--------|

| 710000   | φ0000  |

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | PHD_7 | PHD_6 | PHD_5 | PHD_4 | PHD_3 | PHD_2 | PHD_1 | PHD_0 |

| Reset:          | 1     | 0     | 0     | 1     | 0     | 0     | 0     | 0     |

Figure 13-14. Phase Detector Control Register (PDCR)

PHD\_[7:0] — Phase detector Control Bits for both PLLs

Set PHD\_[7:0] = \$70 for maximum performance.

## 13.10 Pre-Defined VCO Output Frequency Settings

The exact frequency values for the following required channels cannot be synthesized by using a reference frequency higher than 10kHz. An absolute offset frequency from +1.66kHz to +1.89kHz will be introduced for different channels and the maximum relative offset is only  $\pm$ 115Hz with 1.775kHz as the center point (see **Table 13-1** . **Predefined Programming Setting for PLL**). The absolute offset frequency can be further minimized by reducing the crystal frequency by 60 ppm (360Hz) in actual application.

| Table 13-1. | Predefined | Programming | g Setting for PLL |  |

|-------------|------------|-------------|-------------------|--|

|-------------|------------|-------------|-------------------|--|

| Channel<br>Frequency<br>(MHz) | Crystal<br>Frequency<br>(MHz) | Divider R | Reference<br>Frequency<br>(kHz) | Divider N | VCO<br>Frequency<br>(MHz) | Absolute<br>Offset<br>(kHz) |

|-------------------------------|-------------------------------|-----------|---------------------------------|-----------|---------------------------|-----------------------------|

| 26.54                         | 12                            | 288       | 41.67                           | 637       | 26.54166                  | +1.66                       |

| 26.59                         | 12                            | 338       | 35.50                           | 749       | 26.59171                  | +1.71                       |

| 26.64                         | 12                            | 268       | 44.78                           | 595       | 26.64179                  | +1.79                       |

| 26.69                         | 12                            | 370       | 32.43                           | 823       | 26.69189                  | +1.89                       |

| 26.74                         | 12                            | 302       | 39.74                           | 673       | 26.74172                  | +1.72                       |

## 14.6 Port E

Port E is a 5-bit special function port that shares three of its pins with the timer interface modules (TIMs) and two of its pins with the USB data pins D+ and D–. PTE4 and PTE3 are open-drain when configured as output.

### 14.6.1 Port E Data Register

The port E data register contains a data latch for each of the five port E pins.

| Address:                 | \$0008 |           |                     |                    |                 |                 |                 |                 |  |  |  |

|--------------------------|--------|-----------|---------------------|--------------------|-----------------|-----------------|-----------------|-----------------|--|--|--|

|                          | Bit 7  | 6         | 5                   | 4                  | 3               | 2               | 1               | Bit 0           |  |  |  |

| Read:                    | 0      | 0         | 0                   | PTE4               | PTE3            | PTE2            | PTE1            | PTE0            |  |  |  |

| Write:                   |        |           |                     | FIC4               |                 |                 |                 |                 |  |  |  |

| Reset:                   |        |           | Unaffected by reset |                    |                 |                 |                 |                 |  |  |  |

| Alternative<br>Function: |        |           |                     | D-                 | D+              | T2CH01          | T1CH01          | TCLK            |  |  |  |

| Additional<br>Function:  |        |           |                     | Optional<br>pullup | Optional pullup | Optional pullup | Optional pullup | Optional pullup |  |  |  |

| Additional<br>Function:  |        |           |                     | External interrupt |                 |                 |                 |                 |  |  |  |

|                          |        |           |                     | Open-drain         | Open-drain      |                 |                 |                 |  |  |  |

|                          |        | = Unimple | mented              |                    |                 |                 |                 |                 |  |  |  |

Figure 14-11. Port E Data Register (PTE)

PTE[4:0] — Port E Data Bits

PTE[4:0] are read/write, software-programmable bits. Data direction of each port E pin is under the control of the corresponding bit in data direction register E.

The PTE4 and PTE3 pullup enable bits, PTE4P and PTE3P, in the port option control register (POCR) enable  $5k\Omega$  pullups on PTE4 and PTE3 if the respective pin is configured as an input and the USB module is disabled. (See 14.7 Port Options.)

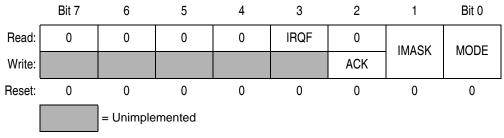

## 15.8 IRQ Status and Control Register

The IRQ status and control register (ISCR) controls and monitors operation of the IRQ module. The ISCR has the following functions:

- Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks IRQ interrupt request

- Controls triggering sensitivity of the IRQ pin.

Address: \$001E

IRQF — IRQ Flag

This read-only status bit is high when the IRQ interrupt is pending.

1 = IRQ interrupt pending

0 = IRQ interrupt not pending

ACK — IRQ Interrupt Request Acknowledge Bit

Writing a logic 1 to this write-only bit clears the IRQ latch. ACK always reads as logic 0. Reset clears ACK.

IMASK — IRQ Interrupt Mask Bit

Writing a logic 1 to this read/write bit disables IRQ interrupt requests. Reset clears IMASK.

1 = IRQ interrupt requests disabled

0 = IRQ interrupt requests enabled

MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the  $\overline{IRQ}$  pin. Reset clears MODE.

$1 = \overline{IRQ}$  pin interrupt requests on falling edges and low levels

$0 = \overline{IRQ}$  pin interrupt requests on falling edges only

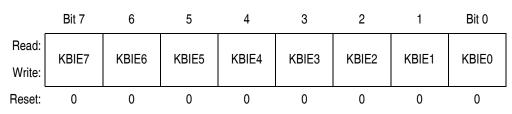

### 16.7.2 Keyboard Interrupt Enable Register

The keyboard interrupt enable register enables or disables each port A pin to operate as a keyboard interrupt pin.

Address: \$0017

Figure 16-4. Keyboard Interrupt Enable Register (KBIER)

KBIE7-KBIE0 - Keyboard Interrupt Enable Bits

Each of these read/write bits enables the corresponding keyboard interrupt pin to latch interrupt requests. Reset clears the keyboard interrupt enable register.

1 = PTAx/KBAx pin enabled as keyboard interrupt pin

0 = PTAx/KBAx not enabled as keyboard interrupt pin

## 16.8 Low-Power Modes

The WAIT and STOP instructions put the MCU in low-power consumption standby modes.

#### 16.8.1 Wait Mode

The keyboard module remains active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

### 16.8.2 Stop Mode

The keyboard module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

MC68HC908JB16 - Rev. 1.1

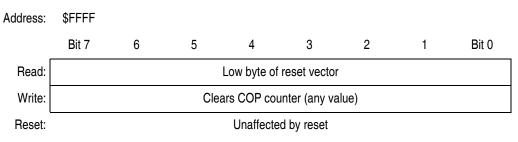

## 17.5 COP Control Register

The COP control register is located at address \$FFFF and overlaps the reset vector. Writing any value to \$FFFF clears the COP counter and starts a new timeout period. Reading location \$FFFF returns the low byte of the reset vector.

Figure 17-3. COP Control Register (COPCTL)

## 17.6 Interrupts

The COP does not generate CPU interrupt requests.

## 17.7 Monitor Mode

When monitor mode is entered with  $V_{TST}$  on the  $\overline{IRQ}$  pin, the COP is disabled as long as  $V_{TST}$  remains on the  $\overline{IRQ}$  pin or the  $\overline{RST}$  pin. When monitor mode is entered by having blank reset vectors and not having  $V_{TST}$  on the  $\overline{IRQ}$  pin, the COP is automatically disabled until a POR occurs.

## 17.8 Low-Power Modes

The WAIT and STOP instructions put the MCU in low powerconsumption standby modes.

## Section 18. Low-Voltage Inhibit (LVI)

## 18.1 Contents

| 18.2 Introduction                                                                                         |

|-----------------------------------------------------------------------------------------------------------|

| 18.3 Features                                                                                             |

| 18.4Functional Description                                                                                |

| 18.5 LVI Control and Configuration                                                                        |

| 18.6     Low-Power Modes     .306       18.6.1     Wait Mode     .306       18.6.2     Stop Mode     .306 |

## 18.2 Introduction

This section describes the low-voltage inhibit (LVI) module, which monitors the voltage on the V<sub>DD</sub> pin and V<sub>REG</sub> pin. and can force a reset when the V<sub>DD</sub> or V<sub>REG</sub> voltage falls below the LVI trip falling voltage.

## 18.3 Features

Features of the LVI module include:

- Independent voltage monitoring circuits for V<sub>DD</sub> and V<sub>REG</sub>

- Independent LVI circuit disable for V<sub>DD</sub> and V<sub>REG</sub>

- Selectable LVI trip voltage for V<sub>DD</sub>

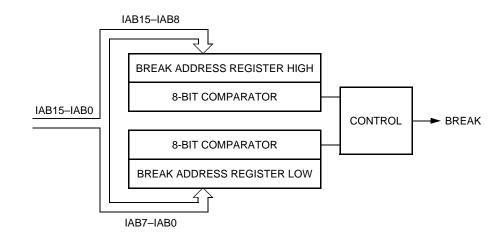

### Figure 19-1. Break Module Block Diagram

| Addr.                                      | Register Name                                 |        | Bit 7  | 6          | 5      | 4  | 3  | 2          | 1    | Bit 0 |

|--------------------------------------------|-----------------------------------------------|--------|--------|------------|--------|----|----|------------|------|-------|

|                                            |                                               | Read:  | R      | R          | R      | R  | R  | R -        | SBSW | R     |

| \$FE00 SIM Break Status Register<br>(SBSR) | SIM Break Status Register (SBSR)              | Write: | 11     |            |        |    |    |            | Note |       |

|                                            | ( , , , , , , , , , , , , , , , , , , ,       | Reset: |        |            |        |    |    |            | 0    |       |

|                                            |                                               | Read:  | BCFE   | R          | R      | R  | R  | R          | R    | R     |

| \$FE03                                     | SIM Break Flag Control<br>Register (SBFCR)    | Write: | DULE   |            |        |    |    |            |      |       |

|                                            |                                               | Reset: | 0      |            |        |    |    |            |      |       |

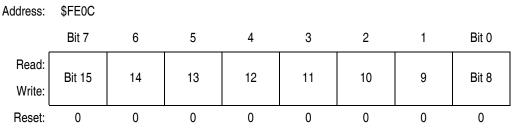

|                                            |                                               | Read:  | Bit 15 | 14         | 13     | 12 | 11 | 10         | 9    | Bit 8 |

| \$FE0C                                     | Break Address Register<br>High (BRKH)         | Write: |        |            |        |    |    |            |      |       |

|                                            |                                               | Reset: | 0      | 0          | 0      | 0  | 0  | 0          | 0    | 0     |

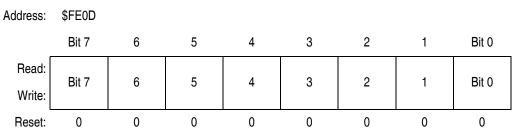

|                                            |                                               | Read:  | Bit 7  | 6          | 5      | 4  | 3  | 2          | 1    | Bit 0 |

| \$FE0D                                     | Break Address Register<br>Low (BRKL)          | Write: |        |            |        |    |    |            |      |       |

|                                            |                                               | Reset: | 0      | 0          | 0      | 0  | 0  | 0          | 0    | 0     |

| \$FE0E                                     | Break Status and Control<br>Register (BRKSCR) | Read:  | BRKE   | BRKA       | 0      | 0  | 0  | 0          | 0    | 0     |

|                                            |                                               | Write: |        |            |        |    |    |            |      |       |

|                                            |                                               | Reset: | 0      | 0          | 0      | 0  | 0  | 0          | 0    | 0     |

| Note: Writing a logic 0 clears SBSW.       |                                               |        |        | = Unimpler | nented |    | R  | = Reserved | l    |       |

Figure 19-2. Break Module I/O Register Summary

Break Module (BRK)

BRKA — Break Active Bit

This read/write status and control bit is set when a break address match occurs. Writing a logic 1 to BRKA generates a break interrupt. Clear BRKA by writing a logic 0 to it before exiting the break routine. Reset clears the BRKA bit.

1 = (When read) Break address match

0 = (When read) No break address match

### 19.6.2 Break Address Registers

The break address registers (BRKH and BRKL) contain the high and low bytes of the desired breakpoint address. Reset clears the break address registers.

Figure 19-4. Break Address Register High (BRKH)

Figure 19-5. Break Address Register Low (BRKL)

## 19.6.3 SIM Break Status Register

The SIM break status register (SBSR) contains a flag to indicate that a break caused an exit from wait mode. The flag is useful in applications requiring a return to wait mode after exiting from a break interrupt.

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Rev. 1.1 MC68HC908JB16/D August 1, 2005 RoHS-compliant and/or Pb- free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb- free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale.s Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The ARM POWERED logo is a registered trademark of ARM Limited. ARM7TDMI-S is a trademark of ARM Limited. Java and all other Java-based marks are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other countries. The Bluetooth trademarks are owned by their proprietor and used by Freescale Semiconductor, Inc. under license.

© Freescale Semiconductor, Inc. 2005. All rights reserved.