Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 8KB (2.75K x 24)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 512 x 8                                                                     |

| RAM Size                   | 1.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 9x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 20-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08ka101-e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to 20-pin and 28-pin packages. The general block the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

#### 1.1.4 EASY MIGRATION

Regardless of the memory size, all the devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also helps in migrating to the next larger device. This is true when moving between devices with the same pin count, or even jumping from 20-pin to 28-pin devices.

The PIC24F family is pin compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple, to the powerful and complex.

#### 1.2 Other Special Features

**Communications:** The PIC24F16KA102 family incorporates a range of serial communication peripherals to handle a range of application requirements. There is and module that supports both the Master and Slave modes of operation. It also comprises UARTs with built-in IrDA<sup>fi</sup> encoders/decoders and an SPI module. Real-Time Clock/Calendar: This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

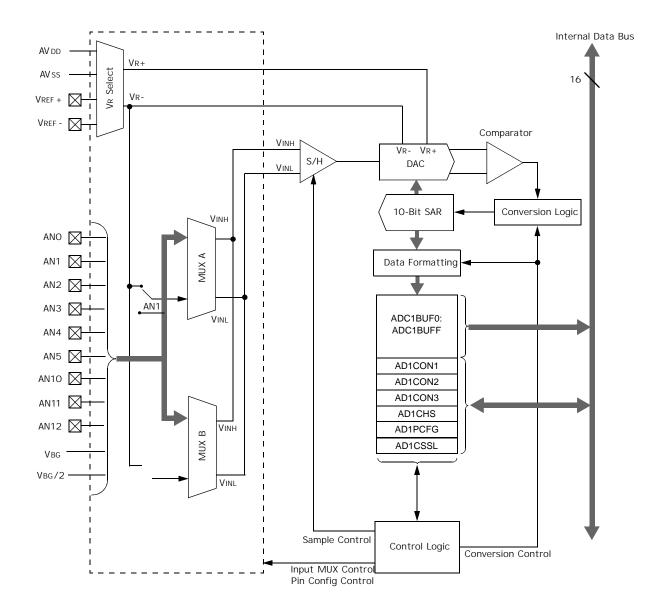

10-Bit A/D Converter: This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and faster sampling speed. The 16-deep result buffer can be used either in Sleep to reduce power, or in Active mode to improve throughput.

Charge Time Measurement Unit (CTMU) Interface: The PIC24F16KA102 family includes the new CTMU interface module, which can be used for capacitive touch sensing, proximity sensing and also for precision time measurement and pulse generation.

#### 1.3 Details on Individual Family Members

Devices in the PIC24F16KA102 family are available in diagram for all devices is displayedFigure 1-1.

The devices are different from each other in two ways:

- 1. Flash program memory (8 Kbytes for PIC24F08KA devices, 16 Kbytes for PIC24F16KA devices).

- 2 Available I/O pins and ports (18 pins on two ports for 20-pin devices and 24 pins on two ports for 28-pin devices).

- 3. Alternate SCLx and SDAx pins are available only in 28-pin devices and not in 20-pin devices.

All other features for devices in this family are identical; these are summarized inable 1-1.

A list of the pin features available on the PIC24F16KA102 family devices, sorted by function, is provided inTable 1-2

Note: Table 1-1 provides the pin location of individual peripheral features and not how they are multiplexed on the same pin. 1 his information is provided in the pinout diagrams on pages4, 5 and 6 of the dat sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

### 4.0 MEMORY ORGANIZATION

As with Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and busing. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 Program Address Space

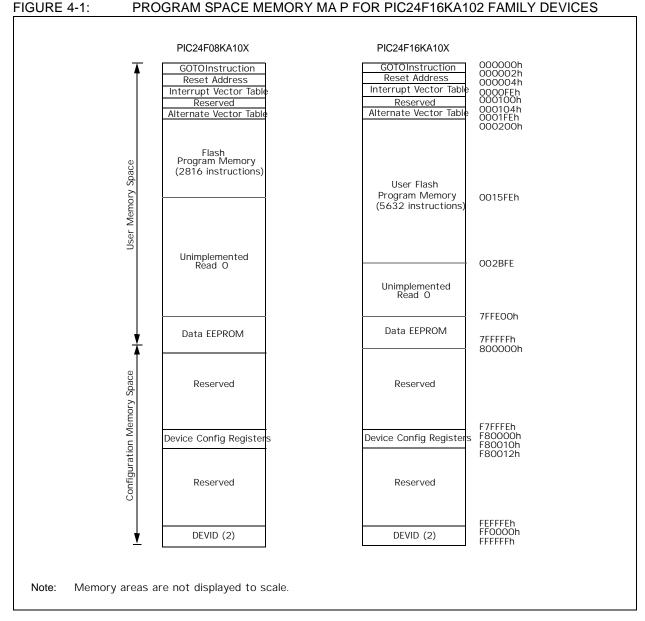

The program address memory space of the PIC24F devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program exution, or from a table operation or data space remapping, as described in Section 4.3 "Interfacing Program and Data Memory Spaces".

The user access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24F16KA102 family of devices are displayed infigure 4-1

| TABLE 4      | . 0. |        |        |        | RS MA  |        |        |       |            |             |            |            |            |           |           |        |    |       |               |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|------------|-------------|------------|------------|------------|-----------|-----------|--------|----|-------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7       | Bit 6      | Bit 5      | Bit 4      | Bit 3     | Bit 2     | Bit    | 1  | Bit 0 | All<br>Resets |

| WREGO        | 0000 |        |        |        |        |        |        |       | Working    | g Register  | 0          |            |            |           |           |        |    |       | 0000          |

| WREG1        | 0002 |        |        |        |        |        |        |       | Working    | g Register  | 1          |            |            |           |           |        |    |       | 0000          |

| WREG2        | 0004 |        |        |        |        |        |        |       | Working    | g Register  | 2          |            |            |           |           |        |    |       | 0000          |

| WREG3        | 0006 |        |        |        |        |        |        |       | Working    | g Register  | 3          |            |            |           |           |        |    |       | 0000          |

| WREG4        | 8000 |        |        |        |        |        |        |       | Working    | g Register  | 4          |            |            |           |           |        |    |       | 0000          |

| WREG5        | 000A |        |        |        |        |        |        |       | Working    | g Register  | 5          |            |            |           |           |        |    |       | 0000          |

| WREG6        | 000C |        |        |        |        |        |        |       | Working    | g Register  | 6          |            |            |           |           |        |    |       | 0000          |

| WREG7        | 000E |        |        |        |        |        |        |       | Working    | g Register  | 7          |            |            |           |           |        |    |       | 0000          |

| WREG8        | 0010 |        |        |        |        |        |        |       | Working    | g Register  | 8          |            |            |           |           |        |    |       | 0000          |

| WREG9        | 0012 |        |        |        |        |        |        |       | Working    | g Register  | 9          |            |            |           |           |        |    |       | 0000          |

| WREG10       | 0014 |        |        |        |        |        |        |       | Working    | Register    | 10         |            |            |           |           |        |    |       | 0000          |

| WREG11       | 0016 |        |        |        |        |        |        |       | Working    | Register    | 11         |            |            |           |           |        |    |       | 0000          |

| WREG12       | 0018 |        |        |        |        |        |        |       | Working    | Register    | 12         |            |            |           |           |        |    |       | 0000          |

| WREG13       | 001A |        |        |        |        |        |        |       | Working    | Register    | 13         |            |            |           |           |        |    |       | 0000          |

| WREG14       | 001C |        |        |        |        |        |        |       | Working    | Register    | 14         |            |            |           |           |        |    |       | 0000          |

| WREG15       | 001E |        |        |        |        |        |        |       | Working    | Register    | 15         |            |            |           |           |        |    |       | 0800          |

| SPLIM        | 0020 |        |        |        |        |        |        | Stac  | ck Pointer | Limit Value | e Register |            |            |           |           |        |    |       | хххх          |

| PCL          | 002E |        |        |        |        |        |        | Prog  | ram Count  | er Low By   | te Registe | r          |            |           |           |        |    |       | 0000          |

| PCH          | 0030 |        |        |        |        |        |        |       |            |             |            | Progr      | am Count   | er Regist | ter High  | Byte   |    |       | 0000          |

| TBLPAG       | 0032 |        |        |        |        |        |        |       |            |             |            | Table I    | Memory P   | age Addr  | ess Regi  | ster   |    |       | 0000          |

| PSVPAG       | 0034 |        |        |        |        |        |        |       |            |             | F          | Program S  | bace Visib | lity Page | e Address | Regist | er |       | 0000          |

| RCOUNT       | 0036 |        |        |        | -      | _      |        | RE    | PEAT Loop  | Counter F   | Register   | -          |            |           |           |        |    |       | XXXX          |

| SR           | 0042 |        |        |        |        |        |        |       | DC         | IPL2        | IPL1       | IPLO       | RA         | Ν         | 0         | /      | Ζ  | С     | 0000          |

| CORCON       | 0044 |        |        |        |        |        |        |       |            |             |            |            |            | IPL3      | B PS      | SV     |    |       | 0000          |

| DISICNT      | 0052 |        |        |        |        |        |        |       | Disabl     | e Interrup  | ts Counte  | r Register |            |           |           |        |    |       | XXXX          |

Legend: = unimplemented, read as0. Reset values are shown in hexadecimal.

#### TABLE 4-15: A/D REGISTER MAP

|              | 10.    |           |                   |           |             |           |          |        |         |             |       |       |         |         |         |        |         |        |

|--------------|--------|-----------|-------------------|-----------|-------------|-----------|----------|--------|---------|-------------|-------|-------|---------|---------|---------|--------|---------|--------|

| File<br>Name | Addr   | Bit 15    | Bit 14            | Bit 13    | Bit 12      | Bit 11    | Bit 10   | Bit 9  | Bit 8   | Bit 7       | Bit 6 | Bit 5 | Bit 4 I | Bit 3 E | Sit 2 B | it1 B  | it 0 Al | Resets |

| ADC1BUF0     | 0300   |           |                   |           |             |           |          |        | A/D Da  | ta Buffer ( | 0     |       |         |         |         |        |         | хххх   |

| ADC1BUF1     | 0302   |           |                   |           |             |           |          |        | A/D Da  | ta Buffer ' | 1     |       |         |         |         |        |         | хххх   |

| ADC1BUF2     | 0304   |           | A/D Data Buffer 2 |           |             |           |          |        |         |             |       |       |         | хххх    |         |        |         |        |

| ADC1BUF3     | 0306   |           | A/D Data Buffer 3 |           |             |           |          |        |         |             |       |       |         | хххх    |         |        |         |        |

| ADC1BUF4     | 0308   |           | A/D Data Buffer 4 |           |             |           |          |        |         |             |       |       |         | хххх    |         |        |         |        |

| ADC1BUF5     | 030A   |           |                   |           |             |           |          |        | A/D Da  | ta Buffer ! | 5     |       |         |         |         |        |         | XXXX   |

| ADC1BUF6     | 030C   |           |                   |           |             |           |          |        | A/D Da  | ta Buffer ( | 6     |       |         |         |         |        |         | XXXX   |

| ADC1BUF7     | 030E   |           |                   |           |             |           |          |        | A/D Da  | ta Buffer ' | 7     |       |         |         |         |        |         | XXXX   |

| ADC1BUF8     | 0310   |           |                   |           |             |           |          |        | A/D Da  | ta Buffer 8 | 8     |       |         |         |         |        |         | XXXX   |

| ADC1BUF9     | 0312   |           |                   |           |             |           |          |        | A/D Da  | ta Buffer ( | 9     |       |         |         |         |        |         | XXXX   |

| ADC1BUFA     | 0314   |           |                   |           |             |           |          |        | A/D Dat | a Buffer 1  | 0     |       |         |         |         |        |         | XXXX   |

| ADC1BUFB     | 0316   |           |                   |           |             |           |          |        | A/D Dat | ta Buffer 1 | 1     |       |         |         |         |        |         | XXXX   |

| ADC1BUFC     | 0318   |           |                   |           |             |           |          |        | A/D Dat | a Buffer 1  | 2     |       |         |         |         |        |         | XXXX   |

| ADC1BUFD     | 031A   |           |                   |           |             |           |          |        | A/D Dat | a Buffer 1  | 3     |       |         |         |         |        |         | XXXX   |

| ADC1BUFE     | 031C   |           |                   |           |             |           |          |        | A/D Dat | a Buffer 1  | 4     |       |         |         |         |        |         | xxxx   |

| ADC1BUFF     | 031E   |           | -                 |           |             |           | -        | _      | A/D Dat | a Buffer 1  | 5     |       |         |         |         | -      |         | хххх   |

| AD1CON1      | 0320   | ADON      |                   | ADSIDL    |             |           |          | FORM1  | FORMO   | SSRC2       | SSRC1 | SSRCO |         |         | ASAM    | SAMP   | DONE    | 0000   |

| AD1CON2      | 0322   | VCFG2     | VCFG1             | VCFGO     | OFFCAL      |           | CSCNA    |        |         | BUFS        |       | SMPI3 | SMPI2   | SMPI1   | SMPIO   | BUFM   | ALTS    | 0000   |

| AD1CON3      | 0324   | ADRC      |                   |           | SAMC4       | SAMC3     | SAMC2    | SAMC1  | SAMCO   |             |       | ADCS5 | ADCS4   | ADCS3   | ADCS2   | ADCS1  | ADCS    | 0000   |

| AD1CHS       | 0328   | CHONB     |                   |           |             | CHOSB3    | CHOSB2   | CHOSB1 | CHOSBO  | CHONA       |       |       | CHOSA4  | CHOSA3  | CHOSA2  | CHOSA1 | CHOSAC  | 0000   |

| AD1PCFG      | 032C   |           |                   |           | PCFG12      | PCFG11    | CFG10    |        |         |             |       | PCFG5 | PCFG4   | PCFG3   | PCFG2   | PCFG1  | PCFGO   | 0000   |

| AD1CSSL      | 0330   |           |                   |           | CSSL12      | CSSL11    | CSSL10   |        |         |             |       | CSSL5 | CSSL4   | CSSL3   | CSSL2   | CSSL1  | CSSLO   | 0000   |

| l agond:     | uniman | longontod | road oo O         | Depat val | luco oro ok | own in ho | امماممام |        |         |             |       |       |         |         |         |        |         |        |

Legend: = unimplemented, read as0. Reset values are shown in hexadecimal.

#### TABLE 4-16: CTMU REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11  | Bit 10     | Bit 9    | Bit 8    | Bit 7    | Bit 6      | Bit 5     | Bit 4 E   | Bit 3 E    | it 2 E    | Bit1 B      | it O | All<br>Resets |

|--------------|------|--------|--------|----------|--------|---------|------------|----------|----------|----------|------------|-----------|-----------|------------|-----------|-------------|------|---------------|

| CTMUCON      | 033C | CTMUEN |        | CTMUSIDL | TGEN   | EDGEN E | DGSEQEN ID | ISSEN CT | TRIG EDO | 2POL EDG | 2SEL1 EDG2 | SELO EDG1 | POL EDG1S | EL1 EDG1SE | LO EDG2ST | AT EDG1STAT | ſ    | 0000          |

| CTMUICON     | 033E | ITRIM5 | ITRIM4 | ITRIM3   | ITRIM2 | ITRIM1  | ITRIMO     | IRNG1    | IRNGO    |          |            |           |           |            |           |             |      | 0000          |

Legend: = unimplemented, read as0. Reset values are shown in hexadecimal.

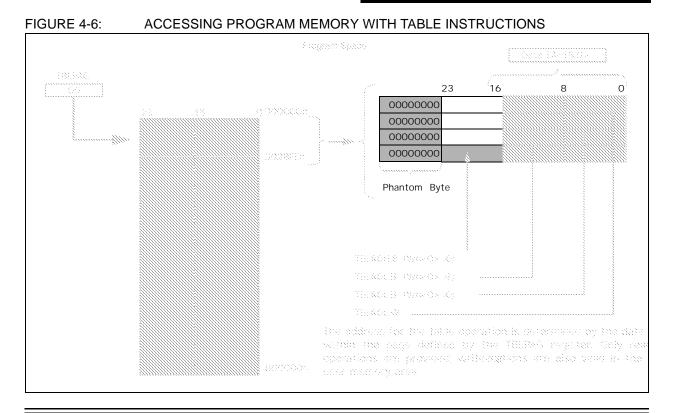

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any <sup>2</sup>. address within the program memory without going through data space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

Note: The TBLRDH and TBLWTH instructions are not used while accessing data EEPROM memory.

The PC is incremented by 2 for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit, word-wide address spaces, residing side by side, each with the same address rang BLRDL and TBLWTL access the space which contains the least significant data word, and BLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

1. TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0×t)o a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select 1s; the lower byte is selected when it **B**.

. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the phantom byte, will alway\$De

In Byte mode, it maps the upper or lower byte of the program word to D < 7:O > of the data address, as above. Note that the data will always be 0 when the upper phantom byte is selected (byte select1).

In a similar fashion, two table instruction Bb, WTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained Spection 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> =1, the page is located in configuration space.

Note: Only table read operations will execute in the configuration memory space, and only ther, in implemented areas, such as the Device D. Table write operations are not allowed.

#### 6.4.1.1 Data EEPROM Bulk Erase

To erase the entire data EEPROM (bulk erase), the address registers do not need to be configured because this operation affects the entire data EEPROM. The following sequence helps in performing bulk erase:

- 1. Configure NVMCON to Bulk Erase mode.

- 2. Clear NVMIF status bit and enable NVM interrupt (optional).

- 3. Write the key sequence to NVMKEY.

- 4. Set the WR bit to begin erase cycle.

- 5. Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

A typical bulk erase sequence is provided in Example 6-3

#### 6.4.2 SINGLE-WORD WRITE

To write a single word in the data EEPROM, the following sequence must be followed:

- Erase one data EEPROM word (as mentioned in Section 6.4.1 "Erase Data EEPROM") if the PGMONLY bit (NVMCON<12>) is set tb.

- 2. Write the data word into the data EEPROM latch.

- 3. Program the data word into the EEPROM:

- Configure the NVMCON register to program one EEPROM word (NVMCON<5:0> €001xx).

- Clear NVMIF status bit and enable NVM interrupt (optional).

- Write the key sequence to NVMKEY.

- Set the WR bit to begin erase cycle.

- Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

- To get cleared, wait until NVMIF is set.

A typical single-word write sequence is provided in Example 6-4

#### EXAMPLE 6-3: DATA EEPROM BULK ERASE

// Set up NVMCON to bulk erase the data EEPROM NVMCON = 0x4050;

// Disable Interrupts For 5 Instructions

asm volatile ("disi #5");

// Issue Unlock Sequence and Start Erase Cycle

\_\_builtin\_write\_NVM();

#### EXAMPLE 6-4: SINGLE-WORD WRITE TO DATA EEPROM

| intattribute ((space(eedata))) eeData = 0x1234;                             | // Variable located in EEPROM,declared as a global variable. |

|-----------------------------------------------------------------------------|--------------------------------------------------------------|

| int newData;<br>unsigned int offset;                                        | // New data to write to EEPROM                               |

| <pre>// Set up NVMCON to erase one word of data EEPR NVMCON = 0x4004;</pre> | OM                                                           |

| // Set up a pointer to the EEPROM location to be e                          | rased                                                        |

| TBLPAG =builtin_tblpage(&eeData);                                           | // Initialize EE Data page pointer                           |

| offset =builtin_tbloffset(&eeData);                                         | // Initizlize lower word of address                          |

| builtin_tblwtl(offset, newData);                                            | // Write EEPROM data to write latch                          |

| asm volatile ("disi #5");                                                   | // Disable Interrupts For 5 Instructions                     |

| builtin_write_NVM();                                                        | // Issue Unlock Sequence & Start Write Cycle                 |

#### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-O  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS |     |     |     |     |     |     |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-O, HS | R/W-0, H | S R/W- | o, HS | R/W-0, H\$ | S U-O |

|-------|-----|-----|-----------|----------|--------|-------|------------|-------|

|       |     |     | MATHERR   | ADDRERR  | STKERR | OSCI  | FAIL       |       |

| bit 7 |     |     |           |          |        |       |            | bit C |

| Legend:      |             | HS = Hardware Settable                                                                    | bit                    |                    |

|--------------|-------------|-------------------------------------------------------------------------------------------|------------------------|--------------------|

| R = Readab   | le bit      | W = Writable bit                                                                          | U = Unimplemented bit, | read as O          |

| -n = Value a | at POR      | 1 = Bit is set                                                                            | 0 = Bit is cleared     | x = Bit is unknown |

| bit 15       | 1 = Interro | nterrupt Nesting Disable bit<br>upt nesting is disabled<br>upt nesting is enabled         |                        |                    |

| bit 14-5     |             | ented: Read as O                                                                          |                        |                    |

| bit 4        | 1 = Overfl  | : Arithmetic Error Trap Statu<br>ow trap has occurred<br>ow trap has not occurred         | us bit                 |                    |

| bit 3        | 1 = Addres  | : Address Error Trap Status<br>ss error trap has occurred<br>ss error trap has not occurr |                        |                    |

| bit 2        | 1 = Stack   | Stack Error Trap Status bit<br>error trap has occurred<br>error trap has not occurred     |                        |                    |

|       | •                                            |

|-------|----------------------------------------------|

| bit 1 | OSCFAIL: Oscillator Failure Trap Status bit  |

|       | 1 = Oscillator failure trap has occurred     |

|       | 0 = Oscillator failure trap has not occurred |

| bit O | Unimplemented: Read as O                     |

### 9.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the fea-       |

|-------|-------------------------------------------|

|       | tures of this group of PIC24F devices. It |

|       | is not intended to be a comprehensive     |

|       | reference source. For more information    |

|       | on Oscillator Configuration, refer to the |

|       | "PIC24F Family Reference Manual",         |

|       | Section 38. "Oscillator with 500 kHz      |

|       | Low-Power FRC" (DS39726).                 |

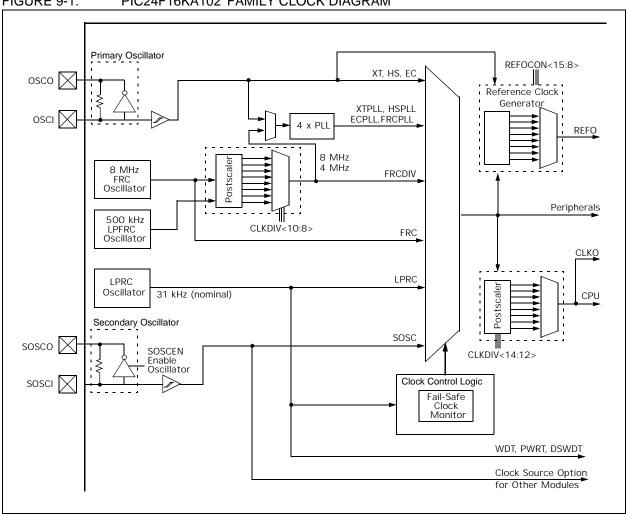

The oscillator system for the PIC24F16KA102 family of devices has the following features:

A total of five external and internal oscillator options as clock sources, providing 11 different clock modes.

On-chip 4x Phase Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources.

Software-controllable switching between various clock sources.

Software-controllable postscaler for selective clocking of CPU for system power savings.

System frequency range declaration bits for EC mode. When using an external clock source, the current consumption is reduced by setting the declaration bits to the expected frequency range. A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown.

Figure 9-1 provides a simplified diagram of the oscillator system.

#### FIGURE 9-1: PIC24F16KA102 FAMILY CLOCK DIAGRAM

#### 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

Primary Oscillator (POSC) on the OSCI and OSCO pins

Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

The PIC24F16KA102 family devices consist of two types of secondary oscillator:

- High-Power Secondary Oscillator

- Low-Power Secondary Oscillator

These can be selected by using the SOSCSEL (FOSC<5>) bit.

Fast Internal RC (FRC) Oscillator

- 8 MHz FRC Oscillator

- 500 kHz Lower Power FRC Oscillator

Low-Power Internal RC (LPRC) Oscillator

The primary oscillator and 8 MHz FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clocky. In this document, the instruction cycle clock is also denoted by Fosc/2. The internal instruction cycle clocks  $F_2$ , can be provided on the OSCO I/O pin for some operating modes of the primary oscillator.

#### 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset (POR) event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (reference 26.1 "Configuration Bits" for further details). The Primary Oscillator Configuration bits, POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a POR. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The secondary oscillator, or one of the internal oscillators, may be chosen by programming these bit locations. The EC mode frequency range Configuration bits, POSCFREQ<1:0> (FOSC<4:3>), optimize power consumption when running in EC mode. The default configuration is frequency range is greater than 8 MHz.

The Configuration bits allow users to choose between the various clock modes, shownTable 9-1.

### 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM Configuration bits (FOSC<7:6>) are used jointly to configure device clock switching and the FSCM. Clock switching is enabled only when FCKSM1 is programmed Q). The FSCM is enabled only when FCKSM<1:0> are both programmed Q).

| Oscillator Mode                                  | Oscillator Source P | OSCMD<1:0> | FNOSC<2:0> | Note |

|--------------------------------------------------|---------------------|------------|------------|------|

| 8 MHz FRC Oscillator with Postscaler (FRCDIV)    | Internal            | 11         | 111        | 1, 2 |

| 500 MHz FRC Oscillator with Postscale (LPFRCDIV) | Internal            | 11         | 110        | 1    |

| Low-Power RC Oscillator (LPRC)                   | Internal            | 11         | 101        | 1    |

| Secondary (Timer1) Oscillator (SOSC)             | Secondary           | 00         | 100        | 1    |

| Primary Oscillator (HS) with PLL Module (HSPLL)  | Primary             | 10         | 011        |      |

| Primary Oscillator (EC) with PLL Module (ECPLL)  | Primary             | 00         | 011        |      |

| Primary Oscillator (HS)                          | Primary             | 10         | 010        |      |

| Primary Oscillator (XT)                          | Primary             | 01         | 010        |      |

| Primary Oscillator (EC)                          | Primary             | 00         | 010        |      |

| 8 MHz FRC Oscillator with PLL Module (FRCPLL)    | Internal            | 11         | 001        | 1    |

| 8 MHz FRC Oscillator (FRC)                       | Internal            | 11         | 000        | 1    |

#### TABLE 9-1: CONFIGURATION BIT VA LUES FOR CLOCK SELECTION

Note 1: OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 10.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

#### 10.4 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

The Peripheral Enable bit, generically named, XXXEN, located in the module s main control SFR.

The Peripheral Module Disable (PMD) bit, generically named, XXXMD, located in one of the PMD Control registers.

Both bits have similar functions in enabling or disabling its associated module. Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect and read values will be invalid. Many peripheral modules have a corresponding PMD bit.

In contrast, disabling a module by clearing its XXXEN bit disables its functionality, but leaves its registers available to be read and written to. Power consumption is reduced, but not by as much as the PMD bits are used. Most peripheral modules have an enable bit; exceptions include capture, compare and RTCC.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, XXXIDL. By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature disables the module while in Idle mode, allowing further reduction of power consumption during Idle mode, enhancing power savings for extremely critical power applications.

### 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the I/O ports, refer to the treat of the treat of the treat of the treat ence Manual", Section 12. "I/O Ports with Peripheral Pin Select (PPS)" (DS39711). Note that the PIC24F16KA102 family devices do not support Peripheral Pin Select features.

All of the device pins (except/Vand Vss) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

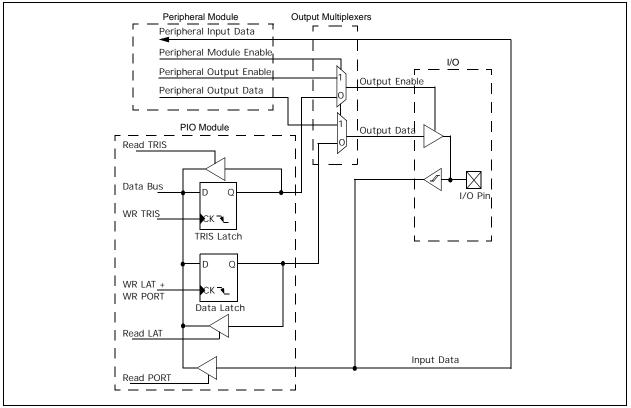

#### 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral s output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents loop through , in which a port s digital output can drive the input of a peripheral that shares the same pirigure 11-1 displays how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Data Latch register (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

Note: The I/O pins retain their state during Deep Sleep. They will retain this state at wake-up until the software restore bit (RELEASE) is cleared.

#### FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

/ 2008-2011 Microchip Technology Inc.

| R/W-O         | U-O                                                                                                                                                                                          | R/W-O                             | R/W-1 HC         | R/W-O          | R/W-                     | O R/W          | /-0        | R/W-O         |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|----------------|--------------------------|----------------|------------|---------------|--|--|

| I2CEN         |                                                                                                                                                                                              | I2CSIDL                           | SCLREL           | IPMIEN         | A10M                     | DISSLW         | SM         | EN            |  |  |

| it 15         |                                                                                                                                                                                              |                                   |                  |                |                          |                |            | bit 8         |  |  |

|               |                                                                                                                                                                                              |                                   |                  |                |                          |                |            |               |  |  |

| R/W-O         | R/W-O                                                                                                                                                                                        | R/W-O                             | R/W-0, H         | C R/W-O, H     | HC R/W-C                 | , HC R/W-      | O, HC      | R/W-0, H      |  |  |

| GCEN          | STREN                                                                                                                                                                                        | ACKDT                             | ACKEN            | RCEN           | PEN                      | RSEN           | SEN        |               |  |  |

| it 7          |                                                                                                                                                                                              |                                   |                  |                |                          |                |            | bit C         |  |  |

|               |                                                                                                                                                                                              |                                   |                  |                |                          |                |            |               |  |  |

| egend:        |                                                                                                                                                                                              |                                   | are Clearable k  |                |                          |                |            |               |  |  |

| R = Reada     |                                                                                                                                                                                              | W = Writabl                       |                  | •              |                          | t, read as 0   | <b>D!1</b> | - 1           |  |  |

| n = Value     | at POR                                                                                                                                                                                       | 1 = Bit is                        | set              | 0 = BIt        | is cleared               | X = 1          | bit is u   | nknown        |  |  |

| it 15         | 12CEN: 12C1                                                                                                                                                                                  | Enable bit                        |                  |                |                          |                |            |               |  |  |

| 11 15         |                                                                                                                                                                                              |                                   | ule and config   | ures the SDA   | 1 and SCL1 i             | oins as serial | port pi    | ns            |  |  |

|               |                                                                                                                                                                                              |                                   | lule; affCl pins |                |                          |                | 1 1        |               |  |  |

| oit 14        | Unimplemente                                                                                                                                                                                 | ed: Read as C                     | )                |                |                          |                |            |               |  |  |

| oit 13        | I2CSIDL: Sto                                                                                                                                                                                 | p in Idle Mode                    | e bit            |                |                          |                |            |               |  |  |

|               |                                                                                                                                                                                              |                                   | peration whe     |                | rs an Idle m             | ode            |            |               |  |  |

| oit 12        |                                                                                                                                                                                              | •                                 | ration in Idle r |                | C dlava)                 |                |            |               |  |  |

| nt iz         | SCLREL: SCL1 Release Control bit (when operating as slave)<br>1 = Releases SCL1 clock                                                                                                        |                                   |                  |                |                          |                |            |               |  |  |

|               | 0 = Holds SCL1 clock low (clock stretch)                                                                                                                                                     |                                   |                  |                |                          |                |            |               |  |  |

|               | If STREN = 1:                                                                                                                                                                                |                                   |                  |                |                          |                |            |               |  |  |

|               | Bit is R/W(i.e., software may wrice to initiate stretch and write release clock). Hardware is clear at the beginning of slave transmission; hardware is clear at the end of slave reception. |                                   |                  |                |                          |                |            |               |  |  |

|               | If STREN = 0:                                                                                                                                                                                |                                   |                  |                |                          |                |            |               |  |  |

|               | Bit is R/S (i.€<br>transmission.                                                                                                                                                             |                                   | nay only wflitet | o release cloo | ck). Hardwar             | e is clear at  | the beg    | ginning of s  |  |  |

| oit 11        |                                                                                                                                                                                              |                                   |                  |                |                          |                |            |               |  |  |

| <i>л</i> с 11 | IPMIEN: Intelligent Peripheral Management Interface (IPMI) Enable bit<br>1 = IPMI Support mode is enabled; all addresses are Acknowledged                                                    |                                   |                  |                |                          |                |            |               |  |  |

|               | 0 = IPMI Support mode is disabled                                                                                                                                                            |                                   |                  |                |                          |                |            |               |  |  |

| oit 10        | A10M: 10-Bit Slave Addressing bit                                                                                                                                                            |                                   |                  |                |                          |                |            |               |  |  |

|               |                                                                                                                                                                                              | is a 10-bit sl<br>is a 7-bit slav |                  |                |                          |                |            |               |  |  |

| oit 9         | DISSLW: Disa                                                                                                                                                                                 | able Slew Rate                    | e Control bit    |                |                          |                |            |               |  |  |

|               |                                                                                                                                                                                              | 1 = Slew rate control is disabled |                  |                |                          |                |            |               |  |  |

|               |                                                                                                                                                                                              | e control is e                    |                  |                |                          |                |            |               |  |  |

| bit 8         | SMEN: SMBus Input Levels bit<br>1 = Enables I/O pin thresholds compliant with the SMBus specification                                                                                        |                                   |                  |                |                          |                |            |               |  |  |

|               |                                                                                                                                                                                              |                                   | put threshold    |                | /IBus specifie           | cation         |            |               |  |  |

| it 7          | GCEN: Gener                                                                                                                                                                                  | al Call Enable                    | bit (when op     | erating 🖧 Isla | ive)                     |                |            |               |  |  |

|               | receptior                                                                                                                                                                                    | r)                                | en a general c   | all address is | s received in            | the I2C1RSR    | (modu      | lle is enable |  |  |

|               |                                                                                                                                                                                              | call address is                   |                  |                | 2                        |                |            |               |  |  |

| oit 6         |                                                                                                                                                                                              |                                   | h Enable bit (   | •              | ng <del>′</del> @sslave) |                |            |               |  |  |

|               | Used in coniu                                                                                                                                                                                | inction with t                    | the SCLREL bit   |                |                          |                |            |               |  |  |

#### FIGURE 22-1: 10-BIT HIGH-SPEED A/D CONVERTER BLOCK DIAGRAM

#### REGISTER 22-6: AD1CSSL: A/D INPUT SCAN SELECT REGISTER (LOW)

| U-0    | U-0 | U-0 | R/W-O  | R/W-0  | R/W-O  | U-0 | U-0   |

|--------|-----|-----|--------|--------|--------|-----|-------|

|        |     |     | CSSL12 | CSSL11 | CSSL10 |     |       |

| bit 15 |     |     |        |        |        |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-O | R/W-O | R/W-0 | R/W-C | ) R/W-Ø |

|-------|-----|-------|-------|-------|-------|-------|---------|

|       |     | CSSL5 | CSSL4 | CSSL3 | CSSL2 | CSSL1 | CSSLO   |

| bit 7 |     |       |       |       |       |       | bit C   |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as O           |

| -n = Value at POR | 1 = Bit is set   | 0 = Bit is cleared       | x = Bit is unknown |

bit 15-13 Unimplemented: Read as O

bit 12-10 CSSL<12:10>: A/D Input Pin Scan Selection bits 1 = Corresponding analog channel is selected for input scan 0 = Analog channel omitted from input scan

bit 9-6 Unimplemented: Read as 0

bit 5-0 CSSL<5:0>: A/D Input Pin Scan Selection bits

1 = Corresponding analog channel is selected for input scan

0 = Analog channel omitted from input scan

| R/P-1                | R/P-1                                                        | R/P-1                                  | R/P-1                   | R/P-1                      | U-O                            | R/P-1          | R/P-1           |  |  |  |

|----------------------|--------------------------------------------------------------|----------------------------------------|-------------------------|----------------------------|--------------------------------|----------------|-----------------|--|--|--|

| MCLRE <sup>(2)</sup> | BORV1 <sup>(3)</sup>                                         | BORVO <sup>(3)</sup>                   | I2C1SEL <sup>(1)</sup>  | PWRTEN                     |                                | BOREN1         | BORENO          |  |  |  |

| bit 7                |                                                              |                                        |                         |                            |                                |                | bit C           |  |  |  |

| _egend:              |                                                              |                                        |                         |                            |                                |                |                 |  |  |  |

| R = Readat           | ole bit                                                      | P = Progra                             | nmable bit              | U = Unim                   | plemented bit                  | , read as 0    |                 |  |  |  |

| -n = Value           | at POR                                                       | 1 = Bit is                             | set                     | O = Bit                    | is cleared                     | x = B          | it is unknown   |  |  |  |

| bit 7                | MCLRE: MCL                                                   | R Pin Fnable I                         | ).<br>( <del>(</del> 2) |                            |                                |                |                 |  |  |  |

|                      | 1 = MCLR pin<br>0 = RA5 input                                | is enabled; R                          | <u>A5 inp</u> ut pin is |                            |                                |                |                 |  |  |  |

| oit 6-5              | BORV<1:0>: [                                                 | BORV<1:0>: Brown-out Reset Enable bits |                         |                            |                                |                |                 |  |  |  |

|                      | 11 = Brown-c<br>10 = Brown-c<br>01 = Brown-c<br>00 = Low-Pov | out Reset<br>out Reset is s            | et to the high          | est voltage                | W                              |                |                 |  |  |  |

| bit 4                | I2C1SEL: Alte<br>0 = Alternate<br>1 = Default Ic             | location for                           | SCL1/SDA1 pir           |                            |                                |                |                 |  |  |  |

| bit 3                | PWRTEN: Pov<br>O = PWRT is o<br>1 = PWRT is o                | disabled                               | Enable bit              |                            |                                |                |                 |  |  |  |

| oit 2                | Unimplemente                                                 | d: Read as O                           |                         |                            |                                |                |                 |  |  |  |

| oit 1-0              | BOREN<1:0>: Brown-out Reset Enable bits                      |                                        |                         |                            |                                |                |                 |  |  |  |

|                      |                                                              | out Reset is er<br>out Reset is c      | ontrolled with          | ile device is a the SBOREN | ctive and disal<br>bit setting | bled in Sleep; | SBOREN bit is ( |  |  |  |

| Note 1: A            | Applies only to 2                                            | 28-pin device                          | S.                      |                            |                                |                |                 |  |  |  |

|                      | The MCLRE fuse                                               |                                        | changed where           | 0                          |                                |                | is prevents a   |  |  |  |

- user from accidentally locking out the device from the low-voltage test entry.

- 3: Refer toSection 29.0, Electrical Characteristfos the BOR voltages.

### 27.0 DEVELOPMENT SUPPORT

The PIC<sup>fi</sup> microcontrollers and dsPiCdigital signal controllers are supported with a full range of software The MPLAB IDE software brings an ease of software and hardware development tools: development previously unseen in the 8/16/32-bi

- Integrated Development Environment

- MPLAB<sup>fi</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>fi</sup> for Various Device Families

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

Simulators

- MPLAB SIM Software Simulator

Emulators

- MPLAB REAL ICE In-Circuit Emulator

In-Circuit Debuggers

- MPLAB ICD 3

- PICkit 3 Debug Express

- Device Programmers

- PICkit 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

#### 27.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Wind&ws operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- A full-featured editor with color-coded context

A multiple project manager

Customizable data windows with direct edit of contents

High-level source code debugging

Mouse over variable inspection

Drag and drop variables from source to watch windows

Extensive on-line help

Integration of select third party tools, such as  $\ensuremath{\mathsf{IAR}}$  C Compilers

The MPLAB IDE allows you to:

Edit your source files (either C or assembly) One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

| Assembly<br>Mnemonic |        | Assembly Syntax  | Description                                | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|------------------|--------------------------------------------|---------------|----------------|--------------------------|

| GOTO                 | GOTO   | Expr             | Go to Address                              | 2             | 2              | None                     |

|                      | GOTO   | Wn               | Go to Indirect                             | 1             | 2              | None                     |

| INC                  | INC    | f                | f = f + 1                                  | 1             | 1              | C, DC, N, OV,            |

|                      | INC    | f,WREG           | WREG = $f + 1$                             | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | Ws,Wd            | Wd = Ws + 1                                | 1             | 1              | C, DC, N, OV, 2          |

| INC2                 | INC2   | f                | f = f + 2                                  | 1             | 1              | C, DC, N, OV,            |

|                      | INC2   | f,WREG           | WREG = $f + 2$                             | 1             | 1              | C, DC, N, OV, 2          |

|                      | INC2   | Ws,Wd            | Wd = Ws + 2                                | 1             | 1              | C, DC, N, OV,            |

| IOR                  | IOR    | f                | f = f .IOR. WREG                           | 1             | 1              | N, Z                     |

|                      | IOR    | f,WREG           | WREG = f .IOR. WREG                        | 1             | 1              | N, Z                     |

|                      | IOR    | #lit10,Wn        | Wd = lit10 .IOR. Wd                        | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,Ws,Wd         | Wd = Wb .IOR. Ws                           | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,#lit5,Wd      | Wd = Wb .IOR. lit5                         | 1             | 1              | N, Z                     |

| LNK                  | LNK    | #lit14           | Link Frame Pointer                         | 1             | 1              | None                     |

| LSR                  | LSR    | f                | f = Logical Right Shift f                  | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | f,WREG           | WREG = Logical Right Shift f               | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Ws,Wd            | Wd = Logical Right Shift Ws                | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Wb,Wns,Wnd       | Wnd = Logical Right Shift Wb by Wns        | 1             | 1              | N, Z                     |

|                      | LSR    | Wb,#lit5,Wnd     | Wnd = Logical Right Shift Wb by lit5       | 1             | 1              | N, Z                     |

| MOV                  | MOV    | f,Wn             | Move f to Wn                               | 1             | 1              | None                     |

|                      | MOV    | [Wns+Slit10],Wnd | Move [Wns+Slit10] to Wnd                   | 1             | 1              | None                     |

|                      | MOV    | f                | Move f to f                                | 1             | 1              | N, Z                     |

|                      | MOV    | f,WREG           | Move f to WREG                             | 1             | 1              | N, Z                     |

|                      | MOV    | #lit16,Wn        | Move 16-bit Literal to Wn                  | 1             | 1              | None                     |

|                      | MOV.b  | #lit8,Wn         | Move 8-bit Literal to Wn                   | 1             | 1              | None                     |

|                      | MOV    | Wn,f             | Move Wn to f                               | 1             | 1              | None                     |

|                      | MOV    | Wns,[Wns+Slit10] | Move Wns to [Wns+Slit10]                   | 1             | 1              | None                     |

|                      | MOV    | Wso,Wdo          | Move Ws to Wd                              | 1             | 1              | None                     |

|                      | MOV    | WREG,f           | Move WREG to f                             | 1             | 1              | N, Z                     |

|                      | MOV.D  | Wns,Wd           | Move Double from W(ns):W(ns+1) to Wd       | 1             | 2              | None                     |

|                      | MOV.D  | Ws,Wnd           | Move Double from Ws to W(nd+1):W(nd)       | 1             | 2              | None                     |

| MUL                  | MUL.SS | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Signed(Wb) * Signed(Ws)     | 1             | 1              | None                     |

|                      | MUL.SU | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(Ws)   | 1             | 1              | None                     |

|                      | MUL.US | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Unsigned(Wb) * Signed(Ws)   | 1             | 1              | None                     |

|                      | MUL.UU | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(W   | s) 1          | 1              | None                     |

|                      | MUL.SU | Wb,#lit5,Wnd     | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(lit5  | ) 1           | 1              | None                     |

|                      | MUL.UU | Wb,#lit5,Wnd     | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(li  | t5) 1         | 1              | None                     |

|                      | MUL    | f                | W3:W2 = f * WREG                           | 1             | 1              | None                     |

| NEG                  | NEG    | f                | f = f+ 1                                   | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG    | f,WREG           | WREG = $\overline{f}$ + 1                  | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG    | Ws,Wd            | Wd = Ws + 1                                | 1             | 1              | C, DC, N, OV, Z          |

| NOP                  | NOP    |                  | No Operation                               | 1             | 1              | None                     |

|                      | NOPR   |                  | No Operation                               | 1             | 1              | None                     |

| POP                  | POP    | f                | Pop f from Top-of-Stack (TOS)              | 1             | 1              | None                     |

|                      | POP    | Wdo              | Pop from Top-of-Stack (TOS) to Wdo         | 1             | 1              | None                     |

|                      | POP.D  | Wnd              | Pop from Top-of-Stack (TOS) to W(nd):W(nd- |               | 2              | None                     |

|                      | POP.S  |                  | Pop Shadow Registers                       | 1             | 1              | All                      |

| PUSH                 | PUSH   | f                | Push f to Top-of-Stack (TOS)               | 1             | 1              | None                     |

|                      | PUSH   | Wso              | Push Wso to Top-of-Stack (TOS)             | 1             | 1              | None                     |

|                      | PUSH.D | Wns              | Push W(ns):W(ns+1) to Top-of-Stack (TOS)   | 1             | 2              | None                     |

|                      | PUSH.S |                  | Push Shadow Registers                      | 1             | 1              | None                     |

| TABLE 28-2: | INSTRUCTION SET OVERVIEW | ١ |

|-------------|--------------------------|---|

| TADLE 20-2. |                          | ) |