Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1.5K × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 9x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

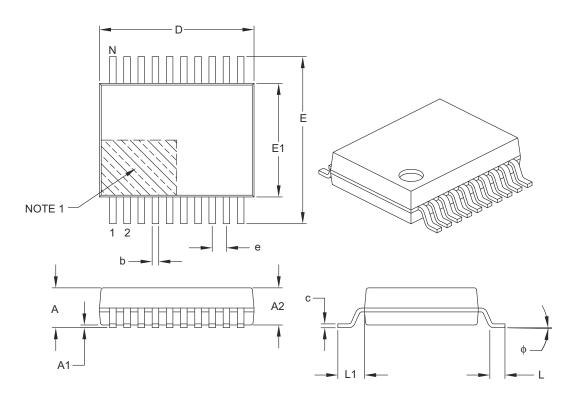

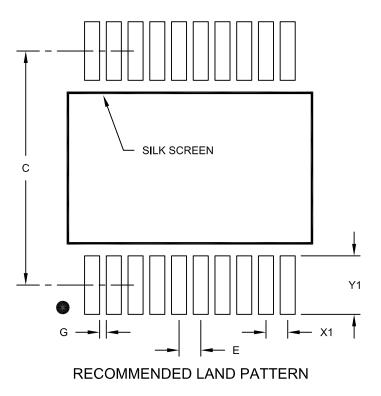

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08ka101-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

20-Pin PDIP/SSOP/SOIC/QFN 28-Pin SPDIP/SSOP/SOIC/QFN

| TABLE 1-1: DEVICE FEATURES FOR T                                        | HE PIC24F16k        | A102 FAMILY         |                                                                                   | _                 |

|-------------------------------------------------------------------------|---------------------|---------------------|-----------------------------------------------------------------------------------|-------------------|

| Features                                                                | PIC24F08KA101       | PIC24F16KA101       | PIC24F08KA102                                                                     | PIC24F16KA102     |

| Operating Frequency                                                     |                     | DC – 3              | 32 MHz                                                                            |                   |

| Program Memory (bytes)                                                  | 8K                  | 16K                 | 8K                                                                                | 16K               |

| Program Memory (instructions)                                           | 2816                | 5632                | 2816                                                                              | 5632              |

| Data Memory (bytes)                                                     |                     | 15                  | 36                                                                                |                   |

| Data EEPROM Memory (bytes)                                              |                     | 5                   | 12                                                                                |                   |

| Interrupt Sources (soft vectors/NMI traps)                              |                     | 30 (2               | 26/4)                                                                             |                   |

| I/O Ports                                                               | PORT/<br>PORTB<15:1 |                     | PORT/<br>PORTE                                                                    | 4<7:0><br>3<15:0> |

| Total I/O Pins                                                          | 1                   | 8                   | 2                                                                                 | 4                 |

| Timers: Total Number (16-bit)<br>32-Bit (from paired 16-bit timers)     |                     |                     | 3<br>1                                                                            |                   |

| Input Capture Channels                                                  |                     |                     | 1                                                                                 |                   |

| Output Compare/PWM Channels                                             |                     |                     | 1                                                                                 |                   |

| Input Change Notification Interrupt                                     | 1                   | 7                   | 2                                                                                 | 3                 |

| Serial Communications: UART<br>SPI (3-wire/4-wire)<br>I <sup>2</sup> C™ |                     |                     | 2<br>1<br>1                                                                       |                   |

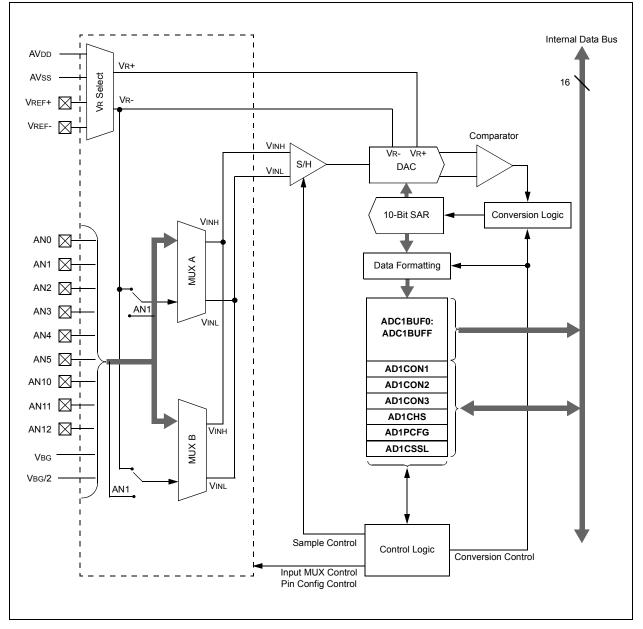

| 10-Bit Analog-to-Digital Module (input channels)                        |                     | (                   | 9                                                                                 |                   |

| Analog Comparators                                                      |                     | 2                   | 2                                                                                 |                   |

| Resets (and delays)                                                     | REPEAT Ins          | truction, Hardwa    | i, <mark>MCLR</mark> , WDT, III<br>re Traps, Configu<br>ſ, OST, PLL Lock <u>)</u> | ration Word       |

| Instruction Set                                                         | 76 Base Ins         | tructions, Multiple | e Addressing Mod                                                                  | le Variations     |

|                                                                         |                     |                     |                                                                                   |                   |

Packages

|          |                              | Pin N         | Number                        |               |     |                 |                                                |

|----------|------------------------------|---------------|-------------------------------|---------------|-----|-----------------|------------------------------------------------|

| Function | 20-Pin<br>PDIP/SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | I/O | Input<br>Buffer | Description                                    |

| AN0      | 2                            | 19            | 2                             | 27            | I   | ANA             | A/D Analog Inputs                              |

| AN1      | 3                            | 20            | 3                             | 28            | I   | ANA             |                                                |

| AN2      | 4                            | 1             | 4                             | 1             | I   | ANA             |                                                |

| AN3      | 5                            | 2             | 5                             | 2             | I   | ANA             |                                                |

| AN4      | 7                            | 4             | 6                             | 3             | I   | ANA             |                                                |

| AN5      | 8                            | 5             | 7                             | 4             | I   | ANA             |                                                |

| AN10     | 17                           | 14            | 25                            | 22            | I   | ANA             |                                                |

| AN11     | 16                           | 13            | 24                            | 21            | I   | ANA             |                                                |

| AN12     | 15                           | 12            | 23                            | 20            | I   | ANA             |                                                |

| U1BCLK   | 13                           | 10            | 18                            | 15            | 0   | _               | UART1 IrDA <sup>®</sup> Baud Clock             |

| U2BCLK   | 9                            | 6             | 11                            | 8             | 0   | _               | UART2 IrDA Baud Clock                          |

| C1INA    | 8                            | 5             | 7                             | 4             | I   | ANA             | Comparator 1 Input A (Positive Input)          |

| C1INB    | 7                            | 4             | 6                             | 3             | I   | ANA             | Comparator 1 Input B (Negative Input Option 1) |

| C1INC    | 5                            | 2             | 5                             | 2             | I   | ANA             | Comparator Input C (Negative Input Option 2)   |

| C1IND    | 4                            | 1             | 4                             | 1             | I   | ANA             | Comparator Input D (Negative Input Option 3)   |

| C1OUT    | 17                           | 14            | 25                            | 22            | 0   | _               | Comparator 1 Output                            |

| C2INA    | 5                            | 2             | 5                             | 2             | I   | ANA             | Comparator 2 Input A (Positive Input)          |

| C2INB    | 4                            | 1             | 4                             | 1             | I   | ANA             | Comparator 2 Input B (Negative Input Option 1) |

| C2INC    | 8                            | 5             | 7                             | 4             | I   | ANA             | Comparator 2 Input C (Negative Input Option 2) |

| C2IND    | 7                            | 4             | 6                             | 3             | I   | ANA             | Comparator 2 Input D (Negative Input Option 3) |

| C2OUT    | 14                           | 11            | 20                            | 17            | 0   | —               | Comparator 2 Output                            |

| CLKI     | 7                            | 4             | 9                             | 6             | Ι   | ANA             | Main Clock Input Connection                    |

| CLKO     | 8                            | 5             | 10                            | 7             | 0   | _               | System Clock Output                            |

**Legend:** ST = Schmitt Trigger input buffer, ANA = Analog level input/output,  $I^2C^{TM} = I^2C/SMBus$  input buffer

**Note 1:** Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

|          |                              | Pin I         | Number                        |               |            |                 |                                                       |

|----------|------------------------------|---------------|-------------------------------|---------------|------------|-----------------|-------------------------------------------------------|

| Function | 20-Pin<br>PDIP/SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | I/O        | Input<br>Buffer | Description                                           |

| CN0      | 10                           | 7             | 12                            | 9             | I          | ST              | Interrupt-on-Change Inputs                            |

| CN1      | 9                            | 6             | 11                            | 8             | I          | ST              |                                                       |

| CN2      | 2                            | 19            | 2                             | 27            | I          | ST              |                                                       |

| CN3      | 3                            | 20            | 3                             | 28            | I          | ST              |                                                       |

| CN4      | 4                            | 1             | 4                             | 1             | I          | ST              |                                                       |

| CN5      | 5                            | 2             | 5                             | 2             | I          | ST              |                                                       |

| CN6      | 6                            | 3             | 6                             | 3             | I          | ST              |                                                       |

| CN7      | _                            | _             | 7                             | 4             | I          | ST              |                                                       |

| CN8      | 14                           | 11            | 20                            | 17            | I          | ST              |                                                       |

| CN9      | —                            |               | 19                            | 16            | I          | ST              |                                                       |

| CN11     | 18                           | 15            | 26                            | 23            | I          | ST              |                                                       |

| CN12     | 17                           | 14            | 25                            | 22            | I          | ST              |                                                       |

| CN13     | 16                           | 13            | 24                            | 21            | I          | ST              |                                                       |

| CN14     | 15                           | 12            | 23                            | 20            | I          | ST              |                                                       |

| CN15     | —                            |               | 22                            | 19            | I          | ST              |                                                       |

| CN16     | —                            | _             | 21                            | 18            | I          | ST              |                                                       |

| CN21     | 13                           | 10            | 18                            | 15            | I          | ST              |                                                       |

| CN22     | 12                           | 9             | 17                            | 14            | I          | ST              |                                                       |

| CN23     | 11                           | 8             | 16                            | 13            | I          | ST              |                                                       |

| CN24     | _                            | _             | 15                            | 12            | I          | ST              |                                                       |

| CN27     | _                            | _             | 14                            | 11            | I          | ST              |                                                       |

| CN29     | 8                            | 5             | 10                            | 7             | I          | ST              |                                                       |

| CN30     | 7                            | 4             | 9                             | 6             | I          | ST              |                                                       |

| CVREF    | 17                           | 14            | 25                            | 22            | 0          | ANA             | Comparator Voltage Reference Output                   |

| CTED1    | 14                           | 11            | 20                            | 17            | I          | ST              | CTMU Trigger Edge Input 1                             |

| CTED2    | 15                           | 12            | 23                            | 20            | I          | ST              | CTMU Trigger Edge Input 2                             |

| CTPLS    | 16                           | 13            | 24                            | 21            | 0          | _               | CTMU Pulse Output                                     |

| IC1      | 14                           | 11            | 19                            | 16            | I          | ST              | Input Capture 1 Input                                 |

| INT0     | 11                           | 8             | 16                            | 13            | I          | ST              | External Interrupt Inputs                             |

| INT1     | 17                           | 14            | 25                            | 22            | I          | ST              | ]                                                     |

| INT2     | 14                           | 11            | 20                            | 17            | I          | ST              |                                                       |

| HLVDIN   | 15                           | 12            | 23                            | 20            | I          | ANA             | HLVD Voltage Input                                    |

| MCLR     | 1                            | 18            | 1                             | 26            | I          | ST              | Master Clear (device Reset) Input                     |

| OC1      | 14                           | 11            | 20                            | 17            | 0          | —               | Output Compare/PWM Outputs                            |

| OCFA     | 17                           | 14            | 25                            | 22            | I          | —               | Output Compare Fault A                                |

| OSCI     | 7                            | 4             | 9                             | 6             | I          | ANA             | Main Oscillator Input Connection                      |

| OSCO     | 8                            | 5             | 10                            | 7             | 0          | ANA             | Main Oscillator Output Connection                     |

| Legend:  | OT - Cohmit                  |               |                               |               | Lavral imm |                 | <sup>2</sup> C™ = I <sup>2</sup> C/SMBus input buffer |

# TABLE 1-2: PIC24F16KA102 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

**Legend:** ST = Schmitt Trigger input buffer, ANA = Analog level input/output,  $I^2C^{TM} = I^2C/SMB$ us input buffer

**Note 1:** Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

# 4.0 MEMORY ORGANIZATION

As with Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and busing. This architecture also allows the direct access of program memory from the data space during code execution.

# 4.1 **Program Address Space**

The program address memory space of the PIC24F devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or data space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

The user access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

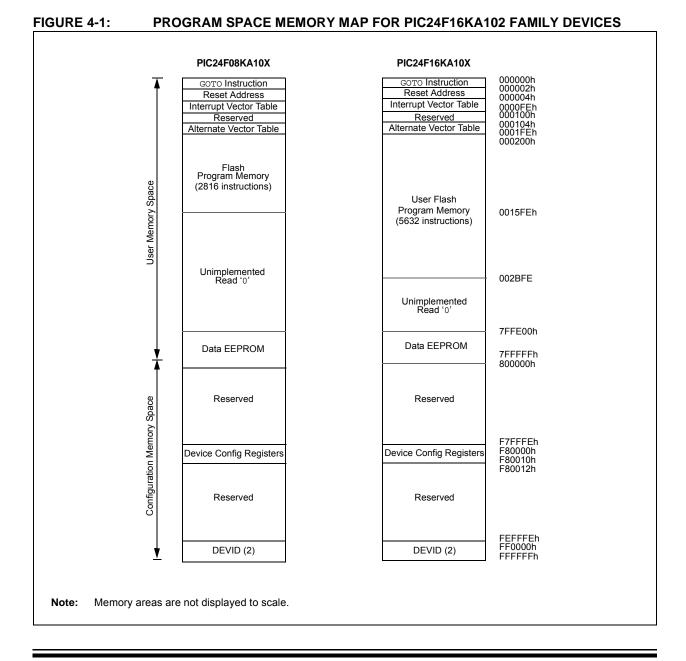

Memory maps for the PIC24F16KA102 family of devices are displayed in Figure 4-1.

# TABLE 4-17: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File<br>Name | Addr | Bit 15               | Bit 14                                                                                                      | Bit 13       | Bit 12       | Bit 11    | Bit 10 | Bit 9         | Bit 8        | Bit 7     | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|----------------------|-------------------------------------------------------------------------------------------------------------|--------------|--------------|-----------|--------|---------------|--------------|-----------|-----------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMVAL      | 0620 |                      | Alarm Value Register Window Based on ALRMPTR<15:0>                                                          |              |              |           |        |               |              |           |           |       |       |       |       |       | xxxx  |               |

| ALCFGRPT     | 0622 | ALRMEN               | LRMEN CHIME AMASK3 AMASK2 AMASK1 AMASK0 ALRMPTR1 ALRMPTR0 ARPT7 ARPT6 ARPT5 ARPT4 ARPT3 ARPT2 ARPT1 ARPT0 ( |              |              |           |        |               |              |           |           |       |       |       |       | 0000  |       |               |

| RTCVAL       | 0624 |                      |                                                                                                             |              |              |           | RTCC   | Value Registe | r Window Bas | ed on RTC | CPTR<15:0 | >     |       |       |       |       |       | xxxx          |

| RCFGCAL      | 0626 | RTCEN                | RTCEN - RTCWREN RTCSYNC HALFSEC RTCOE RTCPTR1 RTCPTR0 CAL7 CAL6 CAL5 CAL4 CAL3 CAL2 CAL1 CAL0 00            |              |              |           |        |               |              |           |           |       |       |       |       | 0000  |       |               |

| Lonondi      |      | a n l a nn a n t a d | rood oo '                                                                                                   | o' Deast val | una ara ahau | in hovodo | aimal  |               |              |           |           |       |       |       |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-18: DUAL COMPARATOR REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CMSTAT       | 0630 | CMSIDL |        | -      | _      | —      | -      | C2EVT | C1EVT | —      | —      | -     | —     |       |       | C2OUT | C10UT | 0000          |

| CVRCON       | 0632 | _      | -      | _      | _      | _      | _      | _     | _     | CVREN  | CVROE  | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| CM1CON       | 0634 | CON    | COE    | CPOL   | CLPWR  | _      | _      | CEVT  | COUT  | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

| CM2CON       | 0636 | CON    | COE    | CPOL   | CLPWR  | _      | _      | CEVT  | COUT  | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-19: CRC REGISTER MAP

| File<br>Name | Addr | Bit 15              | Bit 14                                                                                   | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8       | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|---------------------|------------------------------------------------------------------------------------------|--------|--------|--------|--------|-------|-------------|--------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| CRCCON       | 0640 | _                   | - CSIDL VWORD4 VWORD3 VWORD2 VWORD1 VWORD0 CRCFUL CRCMPT - CRCGO PLEN3 PLEN2 PLEN1 PLEN0 |        |        |        |        |       |             |              |       |       |       |       |       | 0040  |       |               |

| CRCXOR       | 0642 |                     | X<15:1> —                                                                                |        |        |        |        |       |             |              |       |       |       |       |       | 0000  |       |               |

| CRCDAT       | 0644 |                     |                                                                                          |        |        |        |        | (     | CRC Data Ir | nput Registe | er    |       |       |       |       |       |       | 0000          |

| CRCWDAT      | 0646 | CRC Result Register |                                                                                          |        |        |        |        |       |             |              |       |       |       |       | 0000  |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-20: CLOCK CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|--------|--------|--------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | SBOREN | _      | _      | DPSLP  | _      | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE   | BOR    | POR    | (Note 1)      |

| OSCCON    | 0742 | -      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | —     | CF     | _      | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _      | —      | —      | 3140          |

| OSCTUN    | 0748 | —      |        | —      |        | _      | _      |        | —      | _       | -     | TUN5   | TUN4  | TUN3   | TUN2   | TUN1   | TUN0   | 0000          |

| REFOCON   | 074E | ROEN   |        | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | _     | _      | _      | —      | _      | 0000          |

| HLVDCON   | 0756 | HLVDEN | _      | HLSIDL | _      | _      | _      | _      | _      | VDIR    | BGVST | IRVST  | _     | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on configuration fuses and by type of Reset.

#### TABLE 4-21: DEEP SLEEP REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14                                | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0   | All<br>Resets <sup>(1)</sup> |

|-----------|------|--------|---------------------------------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------|------------------------------|

| DSCON     | 0758 | DSEN   | _                                     | _      | _      | _      | —      | _     | _     | —     |       |       |       | _     | _     | DSBOR | RELEASE | 0000                         |

| DSWAKE    | 075A | _      | <u> DSINTO</u>                        |        |        |        |        |       |       |       |       |       |       |       |       | 0000  |         |                              |

| DSGPR0    | 075C |        | Deep Sleep General Purpose Register 0 |        |        |        |        |       |       |       |       |       |       |       |       | 0000  |         |                              |

| DSGPR1    | 075E |        | Deep Sleep General Purpose Register 1 |        |        |        |        |       |       |       |       |       |       |       |       |       | 0000    |                              |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Deep Sleep registers are only reset on a VDD POR event.

#### TABLE 4-22: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets   |

|-----------|------|--------|--------|--------|---------|--------|--------|-------|-------|---------|---------|---------|---------|---------|---------|---------|---------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | PGMONLY | _      | _      | _     | _     | _       | ERASE   | NVMOP5  | NVMOP4  | NVMOP3  | NVMOP2  | NVMOP1  | NVMOP0  | 0000 <b>(1)</b> |

| NVMKEY    | 0766 | —      | —      | -      | —       | _      |        | -     |       | NVMKEY7 | NVMKEY6 | NVMKEY5 | NVMKEY4 | NVMKEY3 | NVMKEY2 | NVMKEY1 | NVMKEY0 | 0000            |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

# TABLE 4-23: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|------------|

| PMD1      | 0770 | —      | _      | T3MD   | T2MD   | T1MD   | _      | _      | _     | I2C1MD | U2MD  | U1MD  |       | SPI1MD | _      | _      | ADC1MD | 0000       |

| PMD2      | 0772 | _      | -      |        | —      | —      |        | _      | IC1MD | _      |       | _     | _     | _      | _      | _      | OC1MD  | 0000       |

| PMD3      | 0774 | _      | -      |        | —      | —      | CMPMD  | RTCCMD | _     | CRCPMD |       | _     | _     | _      | _      | _      | _      | 0000       |

| PMD4      | 0776 | —      | Ι      | _      |        | _      | _      | —      | —     | _      | _     | _     | EEMD  | REFOMD | CTMUMD | HLVDMD |        | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| Cot up NTMOON for your more and an and    |                                         |

|-------------------------------------------|-----------------------------------------|

| ; Set up NVMCON for row programming opera |                                         |

| MOV #0x4004, W0                           |                                         |

| MOV W0, NVMCON                            | ; Initialize NVMCON                     |

| ; Set up a pointer to the first program m | -                                       |

| ; program memory selected, and writes ena | bled                                    |

| MOV #0x0000, W0                           | i                                       |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR       |

| MOV #0x1500, W0                           | ; An example program memory address     |

| ; Perform the TBLWT instructions to write | the latches                             |

| ; 0th_program_word                        |                                         |

| MOV #LOW_WORD_0, W2                       | ;                                       |

| MOV #HIGH_BYTE_0, W3                      | ;                                       |

| TBLWTL W2, [W0]                           | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                         | ; Write PM high byte into program latch |

| ; 1st_program_word                        |                                         |

| MOV #LOW_WORD_1, W2                       | ;                                       |

| MOV #HIGH_BYTE_1, W3                      | ;                                       |

| TBLWTL W2, [W0]                           | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                         | ; Write PM high byte into program latch |

| ; 2nd_program_word                        |                                         |

| MOV #LOW_WORD_2, W2                       | ;                                       |

| MOV #HIGH_BYTE_2, W3                      | ;                                       |

| TBLWTL W2, [W0]                           | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                         | ; Write PM high byte into program latch |

| •                                         |                                         |

| •                                         |                                         |

| •                                         |                                         |

| ; 32nd_program_word                       |                                         |

| MOV #LOW_WORD_31, W2                      | ;                                       |

| MOV #HIGH_BYTE_31, W3                     | ;                                       |

| TBLWTL W2, [W0]                           | ; Write PM low word into program latch  |

| TBLWTH W3, [W0]                           | ; Write PM high byte into program latch |

|                                           |                                         |

#### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

int __attribute__ ((space(auto_psv))) progAddr = 0x1234 // Variable located in Pgm Memory

unsigned int offset;

unsigned int i;

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW];

// Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4004;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

// Initialize lower word of address

offset = __builtin_tbloffset(&progAddr);

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

__builtin_tblwtl(offset, progData[i++]);

// Write to address low word

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

#### REGISTER 9-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| U-0 U-0 U-0 U-0 U-0 U-0 U-0<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            | J-4. KEIO                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |                |                  |                |            |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|----------------|------------|--|

| bit 15 bit 15 bit 1 U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0                                                                      | U-0                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                  | R/W-0          | R/W-0            | R/W-0          | R/W-0      |  |

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -       -       -       -         bit 7       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ROEN                                                                       |                                                                                                                                                                                                                               | ROSSLP                                                                                                                                                                                                                                                                                                   | ROSEL                                                                                                                                                                                  | RODIV3         | RODIV2           | RODIV1         | RODIV0     |  |

| Legend:       Note       Note       Note       Note         bit 7       bit 7       bit 1       bit 1         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       bit 13       ROSSLP: Reference Oscillator Output Stop in Sleep bit         1 = Reference oscillator is disabled in Sleep       0 = Reference oscillator Source Select bit         1 = Primary oscillator is used as the base clock; base clock reflects any clock switching of the device         bit 11-8       RODV<3:0>: Reference Oscillator Select bits         1110 = Base clock value divided by 32,768         1110 = Base clock value divided by 32,068         1011 = Base clock value divided by 4,096         1011 = Base clock value divided by 1,024         100 = Base clock value divided by 10,224         100 = Base clock value divided by 128         1010 = Base clock value divided by 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 15                                                                     |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |                |                  |                | bit 8      |  |

| Lagend:       Note       Note       Note         n =       n       n       n       n         bit 7       bit 1       bit 1       bit 1         Lagend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       bit 13       ROSSLP: Reference Oscillator Output Stop in Sleep bit         1 = Reference oscillator is disabled in Sleep       0 = Reference oscillator is disabled in Sleep       0 = Reference oscillator is disabled in Sleep         bit 12       ROSEL: Reference Oscillator Source Select bit       1 = Primary oscillator is used as the base clock; base clock reflects any clock switching of the device         bit 11-8       RODIV<3:0:>: Reference Oscillator Select bits       1111 = Base clock value divided by 32,768         1110 = Base clock value divided by 4,096       1011 = Base clock value divided by 4,096       1011 = Base clock value divided by 1,024         1001 = Base clock value divided by 1,024       1001 = Base clock value divided by 1,024       1001 = Base clock value divided by 128         1010 = Base clock value divided by 128       1011 = Base clock value divided by 128       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |                |                  |                |            |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       0       = Reference oscillator Output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference oscillator is uisabled in Sleep       0         bit 12       ROSEL: Reference Oscillator Source Select bit       1 = Primary oscillator is used as the base clock <sup>(1)</sup> 0 = System clock is used as the base clock to sleet bits         111 = Base clock value divided by 32,768       1110 = Base clock value divided by 4,096       1011 = Base clock value divided by 4,096         1010 = Base clock value divided by 4,096       1011 = Base clock value divided by 512       1000 = Base clock value divided by 512         1000 = Base clock value divided by 22,048       0101 = Base clock value divided by 32,006       0111 = Base clock value divided by 32,006         0111 = Base clock value divided by 22,048       0101 = Base clock value divided by 22,048       0101 = Base clock value divided by 512         0100 = Base clock value divided by 22,048       0101 = Base clock value divided by 22,048       0101 = Base clock value divided by 22,04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0-0                                                                        | 0-0                                                                                                                                                                                                                           | 0-0                                                                                                                                                                                                                                                                                                      | 0-0                                                                                                                                                                                    | 0-0            | 0-0              | 0-0            | 0-0        |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       0       = Reference oscillator Output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference oscillator is uisabled in Sleep       0         bit 12       ROSEL: Reference Oscillator Source Select bit       1 = Primary oscillator is used as the base clock <sup>(1)</sup> 0 = System clock is used as the base clock to sleet bits         111 = Base clock value divided by 32,768       1110 = Base clock value divided by 4,096       1011 = Base clock value divided by 4,096         1010 = Base clock value divided by 4,096       1011 = Base clock value divided by 512       1000 = Base clock value divided by 512         1000 = Base clock value divided by 22,048       0101 = Base clock value divided by 32,006       0111 = Base clock value divided by 32,006         0111 = Base clock value divided by 22,048       0101 = Base clock value divided by 22,048       0101 = Base clock value divided by 512         0100 = Base clock value divided by 22,048       0101 = Base clock value divided by 22,048       0101 = Base clock value divided by 22,04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <br>bit 7                                                                  | _                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                        | —              |                  | _              | hit 0      |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       isabled         bit 13       ROSSLP: Reference Oscillator Output Stop in Sleep bit       1 = Reference oscillator is disabled in Sleep         bit 12       ROSEL: Reference Oscillator Source Select bit       1 = Primary oscillator is used as the base clock <sup>(1)</sup> 0 = System clock is used as the base clock; base clock reflects any clock switching of the device         bit 11=       Base clock value divided by 16,384         110 = Base clock value divided by 10,224         100 = Base clock value divided by 1,024         100 = Base clock value divided by 10,224         101 = Base clock value divided by 12         101 = Base clock value divided by 32         101 = Base clock value divided by 12         1010 = Base clock value divi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |                |                  |                |            |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROEN: Reference Oscillator Output Enable bit       1 = Reference oscillator is enabled on REFO pin       0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'       1       ROSSLP: Reference Oscillator Output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0 = Reference oscillator is disabled in Sleep       0         bit 12       ROSEL: Reference Oscillator Source Select bit       1 = Primary oscillator is used as the base clock( <sup>11</sup> )       0 = System clock is used as the base clock base clock reflects any clock switching of the device         bit 11-8       RODIV-3:0>: Reference Oscillator Divisor Select bits       1111 = Base clock value divided by 32,768         1110 = Base clock value divided by 4,192       1000 = Base clock value divided by 4,096         1011 = Base clock value divided by 4,096       1011 = Base clock value divided by 4,096         1010 = Base clock value divided by 128       1010 = Base clock value divided by 128         1010 = Base clock value divided by 128       1010 = Base clock value divided by 226         0111 = Base clock value divided by 16       011 = Base clock value divided by 16         0111 = Base clock value divided by 16       011 = Base clock value divided by 128         0110 = Base clock value divided by 128       0100 = Base clock value divided by 128 <td>Legend:</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Legend:                                                                    |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |                |                  |                |            |  |

| bit 15 ROEN: Reference Oscillator Output Enable bit<br>1 = Reference oscillator is enabled on REFO pin<br>0 = Reference oscillator is disabled<br>bit 14 Unimplemented: Read as '0'<br>bit 13 ROSSLP: Reference Oscillator Output Stop in Sleep bit<br>1 = Reference oscillator continues to run in Sleep<br>0 = Reference oscillator source Select bit<br>1 = Primary oscillator is used as the base clock <sup>(1)</sup><br>0 = System clock is used as the base clock base clock reflects any clock switching of the device<br>bit 11-8 RODIV<3:0>: Reference Oscillator Divisor Select bits<br>1111 = Base clock value divided by 32,768<br>1110 = Base clock value divided by 8,192<br>1000 = Base clock value divided by 4,096<br>1011 = Base clock value divided by 1,024<br>1000 = Base clock value divided by 1,024<br>1000 = Base clock value divided by 1,024<br>1000 = Base clock value divided by 128<br>0111 = Base clock value divided by 128<br>0110 = Base clock value divided by 4,096<br>0111 = Base clock value divided by 128<br>0101 = Base clock value divided by 4,006<br>0111 = Base clock value divided by 128<br>0101 = Base clock value divided by 128<br>0101 = Base clock value divided by 4,096<br>0111 = Base clock value divided by 128<br>0110 = Base clock value divided by 4,096<br>0111 = Base clock value divided by 4,096<br>0111 = Base clock value divided by 128<br>0110 = Base clock value divided by 128<br>0110 = Base clock value divided by 4,096<br>0111 = Base clock value divided by 4,096              | R = Readab                                                                 | le bit                                                                                                                                                                                                                        | W = Writable I                                                                                                                                                                                                                                                                                           | oit                                                                                                                                                                                    | U = Unimplem   | nented bit, rea  | d as '0'       |            |  |

| 1 = Reference oscillator is enabled on REFO pin         0 = Reference oscillator is disabled         bit 14       Unimplemented: Read as '0'         bit 13       ROSSLP: Reference Oscillator Output Stop in Sleep bit         1 = Reference oscillator continues to run in Sleep       0         0 = Reference oscillator source Select bit       1 = Primary oscillator is used as the base clock <sup>(1)</sup> 0 = System clock is used as the base clock (sase clock reflects any clock switching of the device         bit 11-8       RODIV<3:0>: Reference Oscillator Divisor Select bits         1111 = Base clock value divided by 32,768         1110 = Base clock value divided by 4,192         1100 = Base clock value divided by 4,192         1100 = Base clock value divided by 2,048         1011 = Base clock value divided by 1,024         1010 = Base clock value divided by 1,024         1011 = Base clock value divided by 256         0111 = Base clock value divided by 128         0111 = Base clock value divided by 128         0110 = Base clock value divided by 32         0100 = Base clock value divided by 32         0101 = Base clock value divided by 4         0111 = Base clock value divided by 4         0101 = Base clock value divided by 4         0111 = Base clock value divided by 4         0111 = Base clock value divided by 4         0111 = Ba                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |                |                  |                |            |  |

| bit 13 ROSLP: Reference Oscillator Output Stop in Sleep bit<br>1 = Reference oscillator continues to run in Sleep<br>0 = Reference oscillator is disabled in Sleep<br>bit 12 ROSEL: Reference Oscillator Source Select bit<br>1 = Primary oscillator is used as the base clock <sup>(1)</sup><br>0 = System clock is used as the base clock; base clock reflects any clock switching of the device<br>bit 11-8 RODIV-3:0>: Reference Oscillator Divisor Select bits<br>1111 = Base clock value divided by 32,768<br>1110 = Base clock value divided by 4,192<br>1100 = Base clock value divided by 4,096<br>1011 = Base clock value divided by 4,096<br>1011 = Base clock value divided by 4,096<br>1011 = Base clock value divided by 512<br>1000 = Base clock value divided by 10,244<br>1011 = Base clock value divided by 128<br>0110 = Base clock value divided by 128<br>0110 = Base clock value divided by 128<br>0110 = Base clock value divided by 4,096<br>0111 = Base clock value divided by 4,096<br>0111 = Base clock value divided by 128<br>0100 = Base clock value divided by 128<br>0100 = Base clock value divided by 128<br>0100 = Base clock value divided by 16<br>0011 = Base clock value divided by 16<br>0011 = Base clock value divided by 2<br>0000 = Base clock value divided by 2<br>0000 = Base clock value divided by 2<br>0000 = Base clock value divided by 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            | 1 = Reference<br>0 = Reference                                                                                                                                                                                                | e oscillator is er<br>e oscillator is di                                                                                                                                                                                                                                                                 | nabled on REF<br>sabled                                                                                                                                                                |                |                  |                |            |  |

| 1 = Reference oscillator continues to run in Sleep         0 = Reference oscillator is disabled in Sleep         bit 12 <b>ROSEL</b> : Reference Oscillator Source Select bit         1 = Primary oscillator is used as the base clock <sup>(1)</sup> 0 = System clock is used as the base clock (shase clock reflects any clock switching of the device         bit 11-8 <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divisor Select bits         1111 = Base clock value divided by 32,768         1110 = Base clock value divided by 16,384         1101 = Base clock value divided by 4,096         1011 = Base clock value divided by 1,024         1000 = Base clock value divided by 1,024         1000 = Base clock value divided by 128         0111 = Base clock value divided by 128         0110 = Base clock value divided by 128         0110 = Base clock value divided by 16         0111 = Base clock value divided by 16         0111 = Base clock value divided by 128         0110 = Base clock value divided by 128         0110 = Base clock value divided by 16         0111 = Base clock value divided by 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            | -                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        | n in Sleen bit |                  |                |            |  |