Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 18                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1.5K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 20-VQFN (5x5)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08ka101t-i-mq |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24F08KA101

- PIC24F16KA101

- PIC24F08KA102

- PIC24F16KA102

The PIC24F16KA102 family introduces a new line of extreme low-power Microchip devices: a 16-bit microcontroller family with a broad peripheral feature set and enhanced computational performance. It also offers a new migration option for those high-performance applications, which may be outgrowing their 8-bit platforms, but do not require the numerical processing power of a digital signal processor.

#### 1.1 Core Features

#### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> digital signal controllers. The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 64 Kbytes (data)

- A 16-element working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32-bit by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as C

- Operational performance up to 16 MIPS

#### 1.1.2 POWER-SAVING TECHNOLOGY

All of the devices in the PIC24F16KA102 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- On-the-Fly Clock Switching: The device clock can be changed under software control to the Timer1 source or the internal, low-power RC oscillator during operation, allowing users to incorporate power-saving ideas into their software designs.

- Doze Mode Operation: When timing-sensitive applications, such as serial communications, require the uninterrupted operation of peripherals, the CPU clock speed can be selectively reduced, allowing incremental power savings without missing a beat.

- Instruction-Based Power-Saving Modes: There are three instruction-based power-saving modes:

- Idle Mode: The core is shut down while leaving the peripherals active.

- Sleep Mode: The core and peripherals that require the system clock are shut down, leaving the peripherals that use their own clock, or the clock from other devices, active.

- Deep Sleep Mode: The core, peripherals (except RTCC and DSWDT), Flash and SRAM are shut down.

## 1.1.3 OSCILLATOR OPTIONS AND FEATURES

The PIC24F16KA102 family offers five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes using crystals or ceramic resonators.

- Two External Clock modes offering the option of a divide-by-2 clock output.

- Two Fast Internal Oscillators (FRCs): One with a nominal 8 MHz output and the other with a nominal 500 kHz output. These outputs can also be divided under software control to provide clock speed as low as 31 kHz or 2 kHz.

- A Phase Locked Loop (PLL) frequency multiplier, available to the External Oscillator modes and the 8 MHz FRC oscillator, which allows clock speeds of up to 32 MHz.

- A separate Internal RC oscillator (LPRC) with a fixed 31 kHz output, which provides a low-power option for timing-insensitive applications.

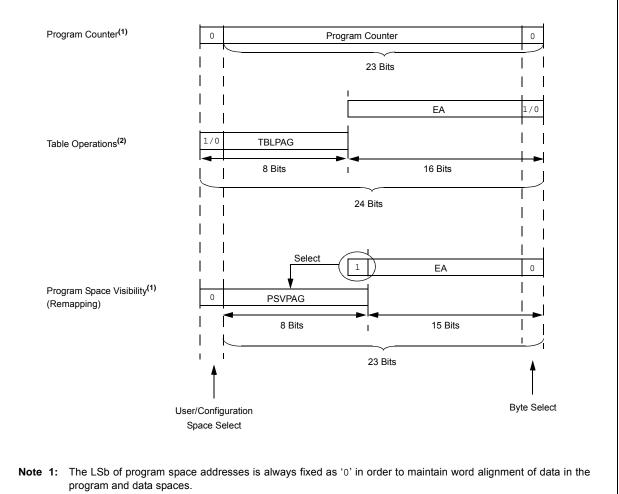

#### TABLE 4-24: PROGRAM SPACE ADDRESS CONSTRUCTION

|                                             | Access        | Program Space Address    |          |                                                  |                     |                    |  |  |

|---------------------------------------------|---------------|--------------------------|----------|--------------------------------------------------|---------------------|--------------------|--|--|

| Access Type                                 | Space         | <23>                     | <22:16>  | <15>                                             | <14:1>              | <0>                |  |  |

| Instruction Access                          | User          | 0                        |          | PC<22:1>                                         |                     | 0                  |  |  |

| (Code Execution)                            |               | 0xx xxxx xxxx xxxx xxx0  |          |                                                  |                     |                    |  |  |

| TBLRD/TBLWT                                 | User          | TBLPAG<7:0>              |          | Data EA<15:0>                                    |                     |                    |  |  |

| (Byte/Word Read/Write)                      |               | 02                       | xxx xxxx | XXX                                              | XXXX XXXX XXXX XXXX |                    |  |  |

|                                             | Configuration | TBLPAG<7:0>              |          | Data EA<15:0>                                    |                     |                    |  |  |

|                                             |               | 1xxx xxxx xxxx xxxx xxxx |          |                                                  | ***                 | xxx                |  |  |

| Program Space Visibility (Block Remap/Read) | User          | 0 PSVPAG<7:              |          | 7:0> <sup>(2)</sup> Data EA<14:0> <sup>(1)</sup> |                     | :0> <sup>(1)</sup> |  |  |

|                                             |               | 0 xxxx xx                |          | xx                                               |                     | x xxxx             |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) on the PIC24F16KA102 family.

#### FIGURE 4-5: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

2: Table operations are not required to be word-aligned. Table read operations are permitted in the configuration memory space.

#### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; | Block all interrupts<br>for next 5 instructions |

|------|-------------|---|-------------------------------------------------|

| MOV  | #0x55, W0   |   |                                                 |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                                |

| MOV  | #0xAA, W1   | ; |                                                 |

| MOV  | W1, NVMKEY  | ; | Write the AA key                                |

| BSET | NVMCON, #WR | ; | Start the erase sequence                        |

| NOP  |             | ; | 2 NOPs required after setting WR                |

| NOP  |             | ; |                                                 |

| BTSC | NVMCON, #15 | ; | Wait for the sequence to be completed           |

| BRA  | \$-2        | ; |                                                 |

|      |             |   |                                                 |

#### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| // C example using MPLAB C30 |                                                 |

|------------------------------|-------------------------------------------------|

| asm("DISI #5");              | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();         | // Perform unlock sequence and set WR           |

| REGISTER     | R 8-8: IFS4 | INTERRUPT                                                                    | FLAG STAT      | US REGISTE        | R 4              |                 |           |  |  |

|--------------|-------------|------------------------------------------------------------------------------|----------------|-------------------|------------------|-----------------|-----------|--|--|

| U-0          | U-0         | R/W-0, HS                                                                    | U-0            | U-0               | U-0              | U-0             | R/W-0, HS |  |  |

|              | —           | CTMUIF                                                                       |                | _                 | —                | —               | HLVDIF    |  |  |

| bit 15       |             |                                                                              |                |                   |                  |                 | bit 8     |  |  |

|              |             |                                                                              |                |                   |                  |                 |           |  |  |

| U-0          | U-0         | U-0                                                                          | U-0            | R/W-0, HS         | R/W-0, HS        | R/W-0, HS       | U-0       |  |  |

| —            | —           | —                                                                            |                | CRCIF             | U2ERIF           | U1ERIF          | —         |  |  |

| bit 7        |             |                                                                              |                |                   |                  |                 | bit 0     |  |  |

| Legend:      |             | HS = Hardward                                                                | e Settable bit |                   |                  |                 |           |  |  |

| R = Readat   | ole bit     | W = Writable b                                                               | oit            | U = Unimplem      | nented bit, read | d as '0'        |           |  |  |

| -n = Value a | at POR      | '1' = Bit is set                                                             |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown      |  |  |

| bit 15-14    | Unimplemer  | nted: Read as '0                                                             | 3              |                   |                  |                 |           |  |  |

| bit 13       | CTMUIF: CT  | MU Interrupt Fla                                                             | g Status bit   |                   |                  |                 |           |  |  |

|              |             | request has occur<br>request has not                                         |                |                   |                  |                 |           |  |  |

| bit 12-9     | Unimplemer  | nted: Read as '0                                                             | ,              |                   |                  |                 |           |  |  |

| bit 8        | HLVDIF: Hig | h/Low-Voltage D                                                              | etect Interrup | t Flag Status bi  | t                |                 |           |  |  |

|              |             | request has occurrequest has not                                             |                |                   |                  |                 |           |  |  |

| bit 7-4      | Unimplemer  | nted: Read as '0                                                             | 3              |                   |                  |                 |           |  |  |

| bit 3        | CRCIF: CRC  | Generator Inter                                                              | rupt Flag Stat | us bit            |                  |                 |           |  |  |

|              |             | request has occur<br>request has not                                         |                |                   |                  |                 |           |  |  |

| bit 2        | U2ERIF: UA  | RT2 Error Interru                                                            | pt Flag Status | s bit             |                  |                 |           |  |  |

|              |             | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |                |                   |                  |                 |           |  |  |

| bit 1        | U1ERIF: UA  | RT1 Error Interru                                                            | pt Flag Status | s bit             |                  |                 |           |  |  |

|              |             | request has occur<br>request has not                                         |                |                   |                  |                 |           |  |  |

| bit 0        | Unimplemer  | nted: Read as '0                                                             | 3              |                   |                  |                 |           |  |  |

|              |             |                                                                              |                |                   |                  |                 |           |  |  |

#### 8.4 Interrupt Setup Procedures

#### 8.4.1 INITIALIZATION

#### To configure an interrupt source:

- 1. Set the NSTDIS Control bit (INTCON1<15>) if nested interrupts are not desired.

- 2. Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits, for all enabled interrupt sources, may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | initialized, such that all user interrupt |  |  |  |  |  |  |  |  |

|       | sources are assigned to Priority Level 4. |  |  |  |  |  |  |  |  |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 8.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (i.e., C or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 8.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 8.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period. Level 7 interrupt sources are not disabled by the DISI instruction.

| REGISTER 10-6: PMD4: PERIPHERAL MODULE DISABLE REGISTER 4 |                            |                                       |                           |                  |                 |                  |             |  |  |

|-----------------------------------------------------------|----------------------------|---------------------------------------|---------------------------|------------------|-----------------|------------------|-------------|--|--|

| U-0                                                       | U-0                        | U-0                                   | U-0                       | U-0              | U-0             | U-0              | U-0         |  |  |

| —                                                         | —                          | —                                     |                           | —                | —               | —                | —           |  |  |

| bit 15                                                    |                            |                                       |                           |                  |                 |                  | bit 8       |  |  |

| r                                                         |                            |                                       |                           |                  |                 |                  |             |  |  |

| U-0                                                       | U-0                        | U-0                                   | R/W-0                     | R/W-0            | R/W-0           | R/W-0            | U-0         |  |  |

| —                                                         | —                          | —                                     | EEMD                      | REFOMD           | CTMUMD          | HLVDMD           | —           |  |  |

| bit 7                                                     |                            |                                       |                           |                  |                 |                  | bit 0       |  |  |

|                                                           |                            |                                       |                           |                  |                 |                  |             |  |  |

| Legend:                                                   |                            |                                       |                           |                  |                 |                  |             |  |  |

| R = Readab                                                | le bit                     | W = Writable b                        | bit                       | U = Unimpler     | nented bit, rea | d as '0'         |             |  |  |

| -n = Value at                                             | t POR                      | '1' = Bit is set                      |                           | '0' = Bit is cle | ared            | x = Bit is unkn  | iown        |  |  |

|                                                           |                            |                                       |                           |                  |                 |                  |             |  |  |

| bit 15-5                                                  | Unimplemer                 | nted: Read as '                       | כ'                        |                  |                 |                  |             |  |  |

| bit 4                                                     | EEMD: EEPI                 | ROM Memory M                          | lodule Disable b          | bit              |                 |                  |             |  |  |

|                                                           |                            | EEPROM memo<br>I memory is dis        | ory Flash panel,<br>abled | minimizing cur   | rent consumpti  | ion              |             |  |  |

| bit 3                                                     | REFOMD: R                  | eference Oscilla                      | ator Module Disa          | able bit         |                 |                  |             |  |  |

|                                                           | 1 = Reference<br>are not v |                                       | dule is disabled.         | All Reference    | Oscillator regi | sters are held i | n Reset and |  |  |

|                                                           | 0 = Referen                | ce Oscillator mo                      | odule is enabled          |                  |                 |                  |             |  |  |

| bit 2                                                     | CTMUMD: C                  | TMU Module D                          | isable bit                |                  |                 |                  |             |  |  |

|                                                           |                            | odule is disable<br>odule is enable   | d. All CTMU reg<br>d      | isters are held  | in Reset and a  | are not writable |             |  |  |

| bit 1                                                     | HLVDMD: HI                 | LVD Module Dis                        | able bit                  |                  |                 |                  |             |  |  |

|                                                           |                            | odule is disabled<br>odule is enabled | d. All HLVD regis<br>I    | sters are held i | n Reset and ar  | e not writable.  |             |  |  |

| bit 0                                                     | Unimplemer                 | nted: Read as 'o                      | כי                        |                  |                 |                  |             |  |  |

|                                                           |                            |                                       |                           |                  |                 |                  |             |  |  |

NOTES:

### 17.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C<sup>™</sup>)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Inter-Integrated Circuit, refer to the *"PIC24F Family Reference Manual"*, Section 24. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS39702).

The Inter-Integrated Circuit (I<sup>2</sup>C) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial data EEPROMs, display drivers, A/D Converters, etc.

The  $I^2C$  module supports these features:

- Independent master and slave logic

- 7-bit and 10-bit device addresses

- General call address, as defined in the I<sup>2</sup>C protocol

- Automatic clock stretching to provide delays for the processor to respond to a slave data request

- Both 100 kHz and 400 kHz bus specifications

- Configurable address masking

- Multi-Master modes to prevent loss of messages in arbitration

- Bus Repeater mode, allowing the acceptance of all messages as a slave regardless of the address

- Automatic SCL

Figure 17-1 illustrates a block diagram of the module.

#### 17.1 Pin Remapping Options

The  $l^2$ C module is tied to a fixed pin. To allow flexibility with peripheral multiplexing, the l2C1 module in 28-pin devices can be reassigned to the alternate pins, designated as SCL1 and SDA1 during device configuration.

Pin assignment is controlled by the I2C1SEL Configuration bit. Programming this bit (= 0) multiplexes the module to the SCL1 and SDA1 pins.

# 17.2 Communicating as a Master in a Single Master Environment

The details of sending a message in Master mode depends on the communications protocol for the device being communicated with. Typically, the sequence of events is as follows:

- 1. Assert a Start condition on SDA1 and SCL1.

- 2. Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- 3. Wait for and verify an Acknowledge from the slave.

- 4. Send the first data byte (sometimes known as the command) to the slave.

- 5. Wait for and verify an Acknowledge from the slave.

- 6. Send the serial memory address low byte to the slave.

- 7. Repeat Steps 4 and 5 until all data bytes are sent.

- 8. Assert a Repeated Start condition on SDA1 and SCL1.

- 9. Send the device address byte to the slave with a read indication.

- 10. Wait for and verify an Acknowledge from the slave.

- 11. Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDA1 and SCL1.

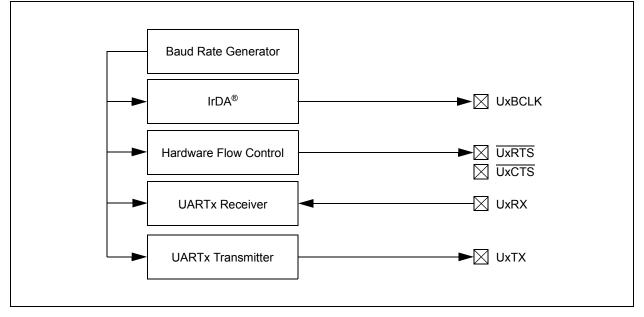

#### 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Universal Asynchronous Receiver Transmitter, refer to the *"PIC24F Family Reference Manual"*, Section 21. "UART" (DS39708).

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in this PIC24F device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. This module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator (IBRG) with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UART is displayed in Figure 18-1. The UART module consists of these important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- · Asynchronous Receiver

#### FIGURE 18-1: UART SIMPLIFIED BLOCK DIAGRAM

### 20.3 Registers

There are four registers used to control programmable CRC operation:

- CRCCON

- CRCXOR

- CRCDAT

- CRCWDAT

#### REGISTER 20-1: CRCCON: CRC CONTROL REGISTER

| U-0    | U-0 | R/W-0 | R-0, HSC |

|--------|-----|-------|----------|----------|----------|----------|----------|

| _      | —   | CSIDL | VWORD4   | VWORD3   | VWORD2   | VWORD1   | VWORD0   |

| bit 15 |     |       |          |          |          |          | bit 8    |

| R-0, HSC | R-1, HSC | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------|----------|-----|-------|-------|-------|-------|-------|

| CRCFUL   | CRCMPT   | —   | CRCGO | PLEN3 | PLEN2 | PLEN1 | PLEN0 |

| bit 7    |          |     |       |       |       |       | bit 0 |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                            |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | CSIDL: CRC Stop in Idle Mode bit                                                                                                      |

|           | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul> |

| bit 12-8  | VWORD<4:0>: Pointer Value bits                                                                                                        |

|           | Indicates the number of valid words in the FIFO. Has a maximum value of 8 when PLEN<3:0> > 7, or 16 when PLEN<3:0> $\leq$ 7.          |

| bit 7     | CRCFUL: FIFO Full bit                                                                                                                 |

|           | 1 = FIFO is full<br>0 = FIFO is not full                                                                                              |

| bit 6     | CRCMPT: FIFO Empty Bit                                                                                                                |

|           | <ul><li>1 = FIFO is empty</li><li>0 = FIFO is not empty</li></ul>                                                                     |

| bit 5     | Unimplemented: Read as '0'                                                                                                            |

| bit 4     | CRCGO: Start CRC bit                                                                                                                  |

|           | 1 = Start CRC serial shifter                                                                                                          |

|           | 0 = CRC serial shifter is turned off                                                                                                  |

| bit 3-0   | PLEN<3:0>: Polynomial Length bits                                                                                                     |

|           | Denotes the length of the polynomial to be generated minus 1.                                                                         |

REGISTER 21-1:

#### U-0 R/W-0 R/W-0 U-0 U-0 U-0 U-0 U-0 **HLVDEN** HLSIDL bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 VDIR BGVST IRVST HLVDL0 \_\_\_\_ HLVDL3 HLVDL2 HLVDL1 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 HLVDEN: High/Low-Voltage Detect Power Enable bit 1 = HLVD is enabled 0 = HLVD is disabled bit 14 Unimplemented: Read as '0' bit 13 HLSIDL: HLVD Stop in Idle Mode bit 1 = Discontinue module operation when device enters Idle mode 0 = Continue module operation in Idle mode Unimplemented: Read as '0' bit 12-8 bit 7 VDIR: Voltage Change Direction Select bit 1 = Event occurs when voltage equals or exceeds trip point (HLVDL<3:0>) 0 = Event occurs when voltage equals or falls below trip point (HLVDL<3:0>) BGVST: Band Gap Voltage Stable Flag bit bit 6 1 = Indicates that the band gap voltage is stable 0 = Indicates that the band gap voltage is unstable bit 5 **IRVST:** Internal Reference Voltage Stable Flag bit 1 = Indicates that the internal reference voltage is stable and the High-Voltage Detect logic generates the interrupt flag at the specified voltage range 0 = Indicates that the internal reference voltage is unstable and the High-Voltage Detect logic will not generate the interrupt flag at the specified voltage range, and the HLVD interrupt should not be enabled bit 4 Unimplemented: Read as '0' bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit bits 1111 = External analog input is used (input comes from the HLVDIN pin) 1110 = Trip Point 1<sup>(1)</sup> 1101 = Trip Point 2<sup>(1)</sup> 1100 = Trip Point 3<sup>(1)</sup> 0000 = Trip Point 15<sup>(1)</sup>

HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

#### REGISTER 22-5: AD1PCFG: A/D PORT CONFIGURATION REGISTER

| R/W-0   | R/W-0  | U-0   | R/W-0  | R/W-0  | R/W-0  | U-0   | U-0   |

|---------|--------|-------|--------|--------|--------|-------|-------|

| PCFG15  | PCFG14 | —     | PCFG12 | PCFG11 | PCFG10 | _     |       |

| bit 15  |        |       |        |        |        |       | bit 8 |

|         |        |       |        |        |        |       |       |

| U-0     | U-0    | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

| —       | —      | PCFG5 | PCFG4  | PCFG3  | PCFG2  | PCFG1 | PCFG0 |

| bit 7   |        |       |        |        |        |       | bit ( |

|         |        |       |        |        |        |       |       |

| Lonondi |        |       |        |        |        |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### 26.3 Deep Sleep Watchdog Timer (DSWDT)

In PIC24F16KA102 family devices, in addition to the WDT module, a DSWDT module is present which runs while the device is in Deep Sleep, if enabled. It is driven by either the SOSC or LPRC oscillator. The clock source is selected by the Configuration bit, DSWDTOSC (FDS<4>).

The DSWDT can be configured to generate a time-out at 2.1 ms to 25.7 days by selecting the respective postscaler. The postscaler can be selected by the Configuration bits, DSWDTPS<3:0> (FDS<3:0>). When the DSWDT is enabled, the clock source is also enabled.

DSWDT is one of the sources that can wake-up the device from Deep Sleep mode.

#### 26.4 Program Verification and Code Protection

For all devices in the PIC24F16KA102 family, code protection for the boot segment is controlled by the Configuration bit, BSS0, and the general segment by the Configuration bit, GSS0. These bits inhibit external reads and writes to the program memory space; this has no direct effect in normal execution mode.

Write protection is controlled by bit, BWRP, for the boot segment and bit, GWRP, for the general segment in the Configuration Word. When these bits are programmed to '0', internal write and erase operations to program memory are blocked.

#### 26.5 In-Circuit Serial Programming

PIC24F16KA102 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGCx) and data (PGDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

#### 26.6 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 2 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the EMUCx (Emulation/Debug Clock) and EMUDx (Emulation/Debug Data) pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGCx, PGDx and the EMUDx/EMUCx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

| Assembly<br>Mnemonic |       | Assembly Syntax | Description                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|-------|-----------------|------------------------------------------|---------------|----------------|--------------------------|

| ADD                  | ADD   | f               | f = f + WREG                             | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD   | f,WREG          | WREG = f + WREG                          | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD   | #lit10,Wn       | Wd = lit10 + Wd                          | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD   | Wb,Ws,Wd        | Wd = Wb + Ws                             | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD   | Wb,#lit5,Wd     | Wd = Wb + lit5                           | 1             | 1              | C, DC, N, OV, Z          |

| ADDC                 | ADDC  | f               | f = f + WREG + (C)                       | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC  | f,WREG          | WREG = f + WREG + (C)                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC  | #lit10,Wn       | Wd = lit10 + Wd + (C)                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC  | Wb,Ws,Wd        | Wd = Wb + Ws + (C)                       | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADDC  | Wb,#lit5,Wd     | Wd = Wb + Iit5 + (C)                     | 1             | 1              | C, DC, N, OV, Z          |

| AND                  | AND   | f               | f = f .AND. WREG                         | 1             | 1              | N, Z                     |

|                      | AND   | f,WREG          | WREG = f .AND. WREG                      | 1             | 1              | N, Z                     |

|                      | AND   | #lit10,Wn       | Wd = lit10 .AND. Wd                      | 1             | 1              | N, Z                     |

|                      | AND   | Wb,Ws,Wd        | Wd = Wb .AND. Ws                         | 1             | 1              | N, Z                     |

|                      | AND   | Wb,#lit5,Wd     | Wd = Wb .AND. lit5                       | 1             | 1              | N, Z                     |

| ASR                  | ASR   | f               | f = Arithmetic Right Shift f             | 1             | 1              | C, N, OV, Z              |

|                      | ASR   | f,WREG          | WREG = Arithmetic Right Shift f          | 1             | 1              | C, N, OV, Z              |

|                      | ASR   | Ws,Wd           | Wd = Arithmetic Right Shift Ws           | 1             | 1              | C, N, OV, Z              |

|                      | ASR   | Wb,Wns,Wnd      | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1              | N, Z                     |

|                      | ASR   | Wb,#lit5,Wnd    | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1              | N, Z                     |

| BCLR                 | BCLR  | f,#bit4         | Bit Clear f                              | 1             | 1              | None                     |

|                      | BCLR  | Ws,#bit4        | Bit Clear Ws                             | 1             | 1              | None                     |

| BRA                  | BRA   | C,Expr          | Branch if Carry                          | 1             | 1 (2)          | None                     |

|                      | BRA   | GE, Expr        | Branch if Greater than or Equal          | 1             | 1 (2)          | None                     |

|                      | BRA   | GEU, Expr       | Branch if Unsigned Greater than or Equal | 1             | 1 (2)          | None                     |

|                      | BRA   | GT,Expr         | Branch if Greater than                   | 1             | 1 (2)          | None                     |

|                      | BRA   | GTU, Expr       | Branch if Unsigned Greater than          | 1             | 1 (2)          | None                     |

|                      | BRA   | LE, Expr        | Branch if Less than or Equal             | 1             | 1 (2)          | None                     |

|                      | BRA   | LEU,Expr        | Branch if Unsigned Less than or Equal    | 1             | 1 (2)          | None                     |

|                      | BRA   | LT,Expr         | Branch if Less than                      | 1             | 1 (2)          | None                     |

|                      | BRA   | LTU, Expr       | Branch if Unsigned Less than             | 1             | 1 (2)          | None                     |

|                      | BRA   | N,Expr          | Branch if Negative                       | 1             | 1 (2)          | None                     |

|                      | BRA   | NC,Expr         | Branch if Not Carry                      | 1             | 1 (2)          | None                     |

|                      | BRA   | NN,Expr         | Branch if Not Negative                   | 1             | 1 (2)          | None                     |

|                      | BRA   | NOV, Expr       | Branch if Not Overflow                   | 1             | 1 (2)          | None                     |

|                      | BRA   | NZ,Expr         | Branch if Not Zero                       | 1             | 1 (2)          | None                     |

|                      | BRA   | OV,Expr         | Branch if Overflow                       | 1             | 1 (2)          | None                     |

|                      | BRA   | Expr            | Branch Unconditionally                   | 1             | 2              | None                     |

|                      | BRA   | Z,Expr          | Branch if Zero                           | 1             | 1 (2)          | None                     |

|                      | BRA   | Wn              | Computed Branch                          | 1             | 2              | None                     |

| BSET                 | BSET  | f,#bit4         | Bit Set f                                | 1             | 1              | None                     |

|                      | BSET  | Ws,#bit4        | Bit Set Ws                               | 1             | 1              | None                     |

| BSW                  | BSW.C | Ws,Wb           | Write C bit to Ws <wb></wb>              | 1             | 1              | None                     |

|                      | BSW.Z | Ws,Wb           | Write Z bit to Ws <wb></wb>              | 1             | 1              | None                     |

| BTG                  | BTG   | f,#bit4         | Bit Toggle f                             | 1             | 1              | None                     |

|                      | BTG   | Ws,#bit4        | Bit Toggle Ws                            | 1             | 1              | None                     |

| BTSC                 | BTSC  | f,#bit4         | Bit Test f, Skip if Clear                | 1             | 1<br>(2 or 3)  | None                     |

|                      | BTSC  | Ws,#bit4        | Bit Test Ws, Skip if Clear               | 1             | 1<br>(2 or 3)  | None                     |

| TABLE 28-2: | <b>INSTRUCTION SET</b> | OVERVIEW  |

|-------------|------------------------|-----------|

|             |                        | ••••••••• |

NOTES:

#### TABLE 29-11: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS |       |                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |     |            |                                               |  |

|--------------------|-------|--------------------------------------|------------------------------------------------------|--------------------|-----|------------|-----------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                       | Min                                                  | Typ <sup>(1)</sup> | Max | Conditions |                                               |  |

|                    |       | Program Flash Memory                 |                                                      |                    |     |            |                                               |  |

| D130               | Eр    | Cell Endurance                       | 10,000 <b>(2)</b>                                    | —                  | —   | E/W        |                                               |  |

| D131               | Vpr   | VDD for Read                         | VMIN                                                 | —                  | 3.6 | V          | VMIN = Minimum operating voltage              |  |

| D133A              | Tiw   | Self-Timed Write Cycle Time          | —                                                    | 2                  | —   | ms         |                                               |  |

| D134               | TRETD | Characteristic Retention             | 40                                                   | —                  | —   | Year       | Provided no other specifications are violated |  |

| D135               | IDDP  | Supply Current During<br>Programming | —                                                    | 10                 | —   | mA         |                                               |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Self-write and block erase.

#### TABLE 29-12: DC CHARACTERISTICS: DATA EEPROM MEMORY

| DC CHARACTERISTICS |        |                                                      | $\begin{array}{ll} \mbox{Standard Operating Conditions: 1.8V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |     |     |      |                                               |  |

|--------------------|--------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-----------------------------------------------|--|

| Param<br>No.       | Sym    | Characteristic                                       | Min Typ <sup>(1)</sup> Max Units                                                                                                                                                                                                                                         |     |     |      | Conditions                                    |  |

|                    |        | Data EEPROM Memory                                   |                                                                                                                                                                                                                                                                          |     |     |      |                                               |  |

| D140               | Epd    | Cell Endurance                                       | 100,000                                                                                                                                                                                                                                                                  | _   | _   | E/W  |                                               |  |

| D141               | VPRD   | VDD for Read                                         | VMIN                                                                                                                                                                                                                                                                     | _   | 3.6 | V    | VMIN = Minimum operating voltage              |  |

| D143A              | Tiwd   | Self-Timed Write Cycle<br>Time                       | —                                                                                                                                                                                                                                                                        | 4   | —   | ms   |                                               |  |

| D143B              | Tref   | Number of Total Write/Erase<br>Cycles Before Refresh | —                                                                                                                                                                                                                                                                        | 10M | —   | E/W  |                                               |  |

| D144               | TRETDD | Characteristic Retention                             | 40                                                                                                                                                                                                                                                                       | —   | _   | Year | Provided no other specifications are violated |  |

| D145               | Iddpd  | Supply Current During<br>Programming                 | —                                                                                                                                                                                                                                                                        | 7   |     | mA   |                                               |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

| AC CHARACTERISTICS |       |                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                  |    |     |                                                     |  |

|--------------------|-------|----------------------------------|------------------------------------------------------|----------------------------------|----|-----|-----------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic <sup>(1)</sup>    | Min                                                  | Min Typ <sup>(2)</sup> Max Units |    |     | Conditions                                          |  |

| OS50               | Fplli | PLL Input Frequency<br>Range     | 4                                                    | _                                | 8  | MHz | ECPLL, HSPLL modes,<br>-40°C $\leq$ TA $\leq$ +85°C |  |

| OS51               | Fsys  | PLL Output Frequency<br>Range    | 16                                                   | —                                | 32 | MHz | $-40^{\circ}C \le TA \le +85^{\circ}C$              |  |

| OS52               | TLOCK | PLL Start-up Time<br>(Lock Time) | —                                                    | 1                                | 2  | ms  |                                                     |  |

| OS53               | DCLK  | CLKO Stability (Jitter)          | -2                                                   | 1                                | 2  | %   | Measured over a 100 ms<br>period                    |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

| AC CHA       | RACTERISTICS                                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |                                        |                                  |  |  |

|--------------|----------------------------------------------|------------------------------------------------------|-----|-----|-------|----------------------------------------|----------------------------------|--|--|

| Param<br>No. | Characteristic                               | Min                                                  | Тур | Max | Units | Conditions                             |                                  |  |  |

|              | Internal FRC Accuracy @ 8 MHz <sup>(1)</sup> |                                                      |     |     |       |                                        |                                  |  |  |

| F20          | FRC                                          | -1                                                   |     | +1  | %     | +25°C                                  | 3.0V < VDD < 3.6V                |  |  |

|              |                                              | -3                                                   | _   | +3  | %     | $-40^\circ C \le T A \le +85^\circ C$  | $3.00 \leq 000 \leq 3.00$        |  |  |

|              |                                              | -5                                                   | _   | +5  | %     | $-40^\circ C \le T A \le +85^\circ C$  | 1.8V < VDD < 3.6V                |  |  |

|              |                                              | -10                                                  | _   | +10 | %     | $-40^\circ C \le TA \le +125^\circ C$  | $1.0V \leq VDD \leq 3.0V$        |  |  |

| F21          | LPRC @ 31 kHz <sup>(2)</sup>                 |                                                      |     |     |       |                                        |                                  |  |  |

|              |                                              | -15                                                  | _   | 15  | %     | +25°C                                  |                                  |  |  |

|              |                                              | -15                                                  | _   | 15  | %     | $-40^\circ C \le T A \le +85^\circ C$  | $1.8V \leq V\text{DD} \leq 3.6V$ |  |  |

|              |                                              | -30                                                  | _   | +30 | %     | $-40^\circ C \le T A \le +125^\circ C$ |                                  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. OSCTUN bits can be used to compensate for temperature drift.

2: Change of LPRC frequency as VDD changes.

### TABLE 29-28:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET TIMING REQUIREMENTS

|              |        |                                                             | Standard Operating Co<br>(unless otherwise state<br>Operating temperature |                    |      |       |                 |  |

|--------------|--------|-------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|------|-------|-----------------|--|

| Param<br>No. | Symbol | Characteristic                                              | Min.                                                                      | Typ <sup>(1)</sup> | Max. | Units | Conditions      |  |

| SY10         | TmcL   | MCLR Pulse Width (low)                                      | 2                                                                         | _                  | _    | μS    |                 |  |

| SY11         | TPWRT  | Power-up Timer Period                                       | 50                                                                        | 64                 | 90   | ms    |                 |  |

| SY12         | TPOR   | Power-on Reset Delay                                        | 1                                                                         | 5                  | 10   | μS    |                 |  |

| SY13         | Tioz   | I/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset | —                                                                         | -                  | 100  | ns    |                 |  |

| SY20         | TWDT   | Watchdog Timer Time-out Period                              | 0.85                                                                      | 1.0                | 1.15 | ms    | 1.32 prescaler  |  |

|              |        |                                                             | 3.4                                                                       | 4.0                | 4.6  | ms    | 1:128 prescaler |  |

| SY25         | TBOR   | Brown-out Reset Pulse Width                                 | 1                                                                         |                    |      | μS    |                 |  |

| SY35         | TFSCM  | Fail-Safe Clock Monitor Delay                               |                                                                           | 2                  | 2.3  | μS    |                 |  |

| SY45         | TRST   | Configuration Update Time                                   |                                                                           | 20                 |      | μS    |                 |  |

| SY55         | TLOCK  | PLL Start-up Time                                           |                                                                           | 1                  |      | ms    |                 |  |

| SY65         | Tost   | Oscillator Start-up Time                                    |                                                                           | 1024               |      | Tosc  |                 |  |

| SY75         | TFRC   | Fast RC Oscillator Start-up Time                            |                                                                           | 1                  | 1.5  | μS    |                 |  |

| SY85         | TLPRC  | Low-Power Oscillator Start-up<br>Time                       | _                                                                         | —                  | 100  | μS    |                 |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

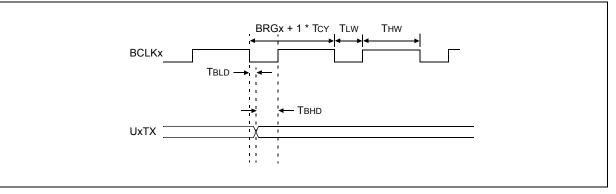

#### FIGURE 29-8: BAUD RATE GENERATOR OUTPUT TIMING

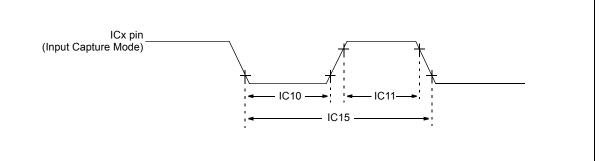

#### FIGURE 29-14: INPUT CAPTURE TIMINGS

#### TABLE 29-33: INPUT CAPTURE

| Param.<br>No.     | Symbol                        | Characteristic                       |              | Min                      | Max | Units          | Conditions                       |

|-------------------|-------------------------------|--------------------------------------|--------------|--------------------------|-----|----------------|----------------------------------|

| IC10              | TccL                          | ICx Input Low Time –                 | No Prescaler | Tcy + 20                 | _   | ns             | Must also meet                   |

|                   | Synchronous Timer             | With Prescaler                       | 20           | _                        | ns  | Parameter IC15 |                                  |

| IC11              | C11 TccH ICx Input Low Time – |                                      | No Prescaler | Tcy + 20                 | _   | ns             | Must also meet                   |

| Synchronous Timer |                               | With Prescaler                       | 20           | _                        | ns  | Parameter IC15 |                                  |

| IC15              | TccP                          | ICx Input Period – Synchronous Timer |              | <u>2 * Tcy + 40</u><br>N | —   | ns             | N = prescale<br>value (1, 4, 16) |

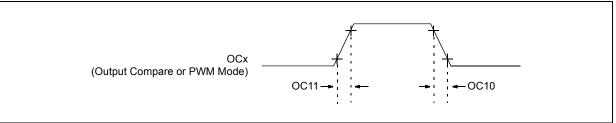

#### TABLE 29-34: OUTPUT CAPTURE

| Param.<br>No. | Symbol | Characteristic       | Min | Мах | Units | Conditions |

|---------------|--------|----------------------|-----|-----|-------|------------|

| OC11          | TCCR   | OC1 Output Rise Time | —   | 10  | ns    |            |

|               |        |                      | —   | —   | ns    |            |

| OC10          | TCCF   | OC1 Output Fall Time | —   | 10  | ns    |            |

|               |        |                      | —   | —   | ns    |            |

#### FIGURE 29-15: OUTPUT COMPARE TIMINGS

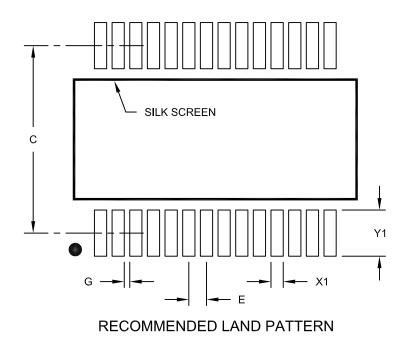

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension                | MIN         | NOM      | MAX  |      |

| Contact Pitch            | E           | 0.65 BSC |      |      |

| Contact Pad Spacing      | С           |          | 7.20 |      |

| Contact Pad Width (X28)  | X1          |          |      | 0.45 |

| Contact Pad Length (X28) | Y1          |          |      | 1.75 |

| Distance Between Pads    | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A