Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 18                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1.5K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 20-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08ka101t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0  | Device Overview                                             | 9   |

|------|-------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with 16-Bit Microcontrollers | 17  |

| 3.0  | CPU                                                         |     |

| 4.0  | Memory Organization                                         |     |

| 5.0  | Flash Program Memory                                        |     |

| 6.0  | Data EEPROM Memory                                          | 51  |

| 7.0  | Resets                                                      | 57  |

| 8.0  | Interrupt Controller                                        |     |

| 9.0  | Oscillator Configuration                                    |     |

| 10.0 | Power-Saving Features                                       | 101 |

| 11.0 | I/O Ports                                                   | 113 |

| 12.0 | Timer1                                                      | 115 |

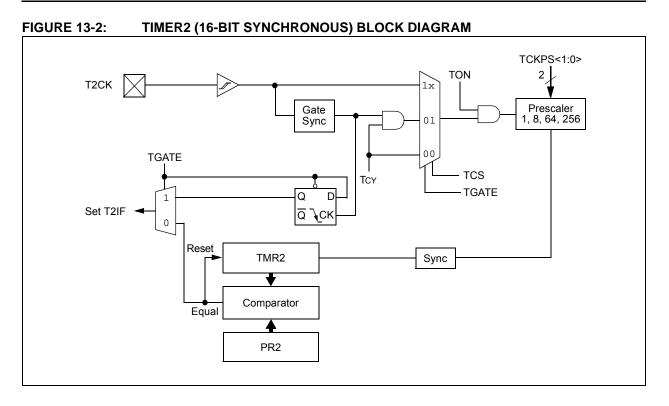

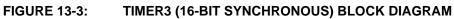

| 13.0 | Timer2/3                                                    | 117 |

| 14.0 | Input Capture                                               | 123 |

| 15.0 | Output Compare                                              | 125 |

| 16.0 | Serial Peripheral Interface (SPI)                           |     |

| 17.0 |                                                             |     |

| 18.0 |                                                             |     |

| 19.0 |                                                             |     |

| 20.0 |                                                             |     |

| 21.0 | High/Low-Voltage Detect (HLVD)                              |     |

| 22.0 |                                                             |     |

| 23.0 |                                                             |     |

| 24.0 | · · · · · · · · · · · · · · · · · · ·                       |     |

| 25.0 |                                                             |     |

| 26.0 |                                                             |     |

| 27.0 | F F F                                                       |     |

| 28.0 |                                                             |     |

| 29.0 |                                                             |     |

|      | Packaging Information                                       |     |

|      | endix A: Revision History                                   |     |

|      | (                                                           |     |

|      | Microchip Web Site                                          |     |

|      | omer Change Notification Service                            |     |

|      | omer Support                                                |     |

|      | ler Response                                                |     |

| Prod | uct Identification System                                   |     |

# TABLE 4-4: ICN REGISTER MAP

| File<br>Name | Addr | Bit 15                 | Bit 14  | Bit 13  | Bit 12  | Bit 11                 | Bit 10 | Bit 9  | Bit 8                  | Bit 7                 | Bit 6   | Bit 5   | Bit 4  | Bit 3         | Bit 2  | Bit 1  | Bit 0                  | All<br>Resets |

|--------------|------|------------------------|---------|---------|---------|------------------------|--------|--------|------------------------|-----------------------|---------|---------|--------|---------------|--------|--------|------------------------|---------------|

| CNEN1        | 0060 | CN15IE <sup>(1)</sup>  | CN14IE  | CN13IE  | CN12IE  | CN11IE <sup>(1)</sup>  |        | CN9IE  | CN8IE                  | CN7IE <sup>(1)</sup>  | CN6IE   | CN5IE   | CN4IE  | CN3IE         | CN2IE  | CN1IE  | CN0IE                  | 0000          |

| CNEN2        | 0062 | _                      | CN30IE  | CN29IE  | _       | CN27IE <sup>(1)</sup>  | _      | _      | CN24IE <sup>(1)</sup>  | CN23IE                | CN22IE  | CN21IE  | _      | _             | _      | _      | CN16IE <sup>(1)</sup>  | 0000          |

| CNPU1        | 0068 | CN15PUE <sup>(1)</sup> | CN14PUE | CN13PUE | CN12PUE | CN11PUE <sup>(1)</sup> | _      | CN9PUE | CN8PUE                 | CN7PUE <sup>(1)</sup> | CN6PUE  | CN5PUE  | CN4PUE | <b>CN3PUE</b> | CN2PUE | CN1PUE | CN0PUE                 | 0000          |

| CNPU2        | 006A | _                      | CN30PUE | CN29PUE |         | CN27PUE <sup>(1)</sup> | _      | _      | CN24PUE <sup>(1)</sup> | CN23PUE               | CN22PUE | CN21PUE |        | _             | _      |        | CN16PUE <sup>(1)</sup> | 0000          |

| CNPD1        | 0070 | CN15PDE <sup>(1)</sup> | CN14PDE | CN13PDE | CN12PDE | CN11PDE <sup>(1)</sup> | _      | CN9PDE | CN8PDE                 | CN7PDE <sup>(1)</sup> | CN6PDE  | CN5PDE  | CN4PDE | CN3PDE        | CN2PDE | CN1PDE | CN0PDE                 | 0000          |

| CNPD2        | 0072 | —                      | CN30PDE | CN29PDE | _       | CN27PDE <sup>(1)</sup> | _      | _      | CN24PDE <sup>(1)</sup> | CN23PDE               | CN22PDE | CN21PDE | _      | _             | _      | _      | CN16PDE <sup>(1)</sup> | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are not implemented in 20-pin devices.

# TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------|------|--------|---------|---------|---------|--------|---------|---------|---------|-------|---------|---------|---------|---------|---------|---------|---------|---------------|

| INTCON1      | 0080 | NSTDIS | _       | _       | _       | _      | _       | _       | _       | _     | _       | _       | MATHERR | ADDRERR | STKERR  | OSCFAIL | —       | 0000          |

| INTCON2      | 0082 | ALTIVT | DISI    | -       | _       |        | _       | _       | _       | _     | _       | _       | _       | _       | INT2EP  | INT1EP  | INT0EP  | 0000          |

| IFS0         | 0084 | NVMIF  | -       | AD1IF   | U1TXIF  | U1RXIF | SPI1IF  | SPF1IF  | T3IF    | T2IF  | _       | _       | _       | T1IF    | OC1IF   | IC1IF   | INT0IF  | 0000          |

| IFS1         | 0086 | U2TXIF | U2RXIF  | INT2IF  | —       | _      |         |         | —       | —     |         |         | INT1IF  | CNIF    | CMIF    | MI2C1IF | SI2C1IF | 0000          |

| IFS3         | 008A | —      | RTCIF   | _       | —       | _      |         |         | —       | —     |         |         |         |         | —       | _       | —       | 0000          |

| IFS4         | 008C | —      | _       | CTMUIF  | —       | _      |         |         | HLVDIF  | —     |         |         |         | CRCIF   | U2ERIF  | U1ERIF  | —       | 0000          |

| IEC0         | 0094 | NVMIE  | _       | AD1IE   | U1TXIE  | U1RXIE | SPI1IE  | SPF1IE  | T3IE    | T2IE  |         |         |         | T1IE    | OC1IE   | IC1IE   | INT0IE  | 0000          |

| IEC1         | 0096 | U2TXIE | U2RXIE  | INT2IE  | _       | _      |         |         | —       | —     |         |         | INT1IE  | CNIE    | CMIE    | MI2C1IE | SI2C1IE | 0000          |

| IEC3         | 009A | —      | RTCIE   | -       | _       |        | _       | _       | _       | -     | _       | _       | _       | _       | _       | _       | _       | 0000          |

| IEC4         | 009C | _      | -       | CTMUIE  | _       |        | _       | _       | HLVDIE  | -     | _       | _       | _       | CRCIE   | U2ERIE  | U1ERIE  | _       | 0000          |

| IPC0         | 00A4 | —      | T1IP2   | T1IP1   | T1IP0   | _      | OC1IP2  | OC1IP1  | OC1IP0  | —     | IC1IP2  | IC1IP1  | IC1IP0  |         | INT0IP2 | INT0IP1 | INT0IP0 | 4444          |

| IPC1         | 00A6 | —      | T2IP2   | T2IP1   | T2IP0   | _      |         |         | —       | —     |         |         |         |         | —       | _       | —       | 4444          |

| IPC2         | 00A8 | —      | U1RXIP2 | U1RXIP1 | U1RXIP0 | _      | SPI1IP2 | SPI1IP1 | SPI1IP0 | —     | SPF1IP2 | SPF1IP1 | SPF1IP0 |         | T3IP2   | T3IP1   | T3IP0   | 4444          |

| IPC3         | 00AA | —      | NVMIP2  | NVMIP1  | NVMIP0  | _      |         |         | —       | —     | AD1IP2  | AD1IP1  | AD1IP0  |         | U1TXIP2 | U1TXIP1 | U1TXIP0 | 4044          |

| IPC4         | 00AC | —      | CNIP2   | CNIP1   | CNIP0   | _      | CMIP2   | CMIP1   | CMIP0   | —     | MI2C1P2 | MI2C1P1 | MI2C1P0 |         | SI2C1P2 | SI2C1P1 | SI2C1P0 | 4444          |

| IPC5         | 00AE | —      | _       | _       | —       | _      |         |         | —       | —     |         |         |         |         | INT1IP2 | INT1IP1 | INT1IP0 | 0004          |

| IPC7         | 00B2 | —      | U2TXIP2 | U2TXIP1 | U2TXIP0 | _      | U2RXIP2 | U2RXIP1 | U2RXIP0 | —     | INT2IP2 | INT2IP1 | INT2IP0 |         | —       | _       | —       | 4440          |

| IPC15        | 00C2 | —      | _       | _       | —       | _      | RTCIP2  | RTCIP1  | RTCIP0  | —     |         |         |         |         | —       | _       | —       | 0400          |

| IPC16        | 00C4 | —      | CRCIP2  | CRCIP1  | CRCIP0  |        | U2ERIP2 | U2ERIP1 | U2ERIP0 | _     | U1ERIP2 | U1ERIP1 | U1ERIP0 | -       | —       | —       | —       | 4440          |

| IPC18        | 00C8 | _      | _       | _       | _       | _      | —       | —       | _       | _     | _       | _       | _       | —       | HLVDIP2 | HLVDIP1 | HLVDIP0 | 0004          |

| IPC19        | 00CA | _      | _       | _       | —       | _      | —       | —       | _       | _     | CTMUIP2 | CTMUIP1 | CTMUIP0 | —       | _       | _       | _       | 0040          |

| INTTREG      | 00E0 | CPUIRQ | _       | VHOLD   | —       | ILR3   | ILR2    | ILR1    | ILR0    | _     | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-17: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File<br>Name | Addr | Bit 15               | Bit 14    | Bit 13       | Bit 12       | Bit 11    | Bit 10  | Bit 9         | Bit 8        | Bit 7     | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|----------------------|-----------|--------------|--------------|-----------|---------|---------------|--------------|-----------|-----------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMVAL      | 0620 |                      |           |              |              |           | Alarm V | alue Register | Window Base  | d on ALR  | MPTR<15:0 | )>    |       |       |       |       |       | xxxx          |

| ALCFGRPT     | 0622 | ALRMEN               | CHIME     | AMASK3       | AMASK2       | AMASK1    | AMASK0  | ALRMPTR1      | ALRMPTR0     | ARPT7     | ARPT6     | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | 0000          |

| RTCVAL       | 0624 |                      |           |              |              |           | RTCC    | Value Registe | r Window Bas | ed on RTC | CPTR<15:0 | >     |       |       |       |       |       | xxxx          |

| RCFGCAL      | 0626 | RTCEN                | —         | RTCWREN      | RTCSYNC      | HALFSEC   | RTCOE   | RTCPTR1       | RTCPTR0      | CAL7      | CAL6      | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000          |

| Lonondi      |      | a n l a nn a n t a d | rood oo ' | o' Deast val | una ara ahau | in hovodo | aimal   |               |              |           |           |       |       |       |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-18: DUAL COMPARATOR REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CMSTAT       | 0630 | CMSIDL |        | -      | _      | —      | -      | C2EVT | C1EVT | —      | —      | -     | —     |       |       | C2OUT | C10UT | 0000          |

| CVRCON       | 0632 | _      | -      | _      | _      | _      | _      | _     | _     | CVREN  | CVROE  | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| CM1CON       | 0634 | CON    | COE    | CPOL   | CLPWR  | _      | _      | CEVT  | COUT  | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

| CM2CON       | 0636 | CON    | COE    | CPOL   | CLPWR  | _      | _      | CEVT  | COUT  | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-19: CRC REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7        | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|-------------|--------------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CRCCON       | 0640 | _      | _      | CSIDL  | VWORD4 | VWORD3 | VWORD2 | VWORD1 | VWORD0      | CRCFUL       | CRCMPT | _     | CRCGO | PLEN3 | PLEN2 | PLEN1 | PLEN0 | 0040          |

| CRCXOR       | 0642 |        |        |        |        |        |        |        | X<15:1>     |              |        |       |       |       |       |       | _     | 0000          |

| CRCDAT       | 0644 |        |        |        |        |        |        | (      | CRC Data Ir | nput Registe | er     |       |       |       |       |       |       | 0000          |

| CRCWDAT      | 0646 |        |        |        |        |        |        |        | CRC Resu    | ult Register |        |       |       |       |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '000100' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as displayed in Example 5-5.

# EXAMPLE 5-1: ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE

| : Sot up NUMCON for row orago operation |                                       |

|-----------------------------------------|---------------------------------------|

| ; Set up NVMCON for row erase operation |                                       |

| MOV #0x4058, W0                         | ;                                     |

| MOV W0, NVMCON                          | ; Initialize NVMCON                   |

| ; Init pointer to row to be ERASED      |                                       |

| MOV #tblpage(PROG_ADDR), W0             | i                                     |

| MOV W0, TBLPAG                          | ; Initialize PM Page Boundary SFR     |

| MOV #tbloffset(PROG_ADDR), W0           | ; Initialize in-page EA[15:0] pointer |

| TBLWTL W0, [W0]                         | ; Set base address of erase block     |

| DISI #5                                 | ; Block all interrupts                |

|                                         | for next 5 instructions               |

| MOV #0x55, W0                           |                                       |

| MOV W0, NVMKEY                          | ; Write the 55 key                    |

| MOV #0xAA, W1                           | ;                                     |

| MOV W1, NVMKEY                          | ; Write the AA key                    |

| BSET NVMCON, #WR                        | ; Start the erase sequence            |

| NOP                                     | ; Insert two NOPs after the erase     |

| NOP                                     | ; command is asserted                 |

|                                         |                                       |

# EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

| // C example using MPLAB C30                                   |                                                                        |

|----------------------------------------------------------------|------------------------------------------------------------------------|

| <pre>intattribute ((space(auto_psv))) progAddr = 0x1234;</pre> | // Variable located in Pgm Memory, declared as a<br>// global variable |

| unsigned int offset;                                           | ,, giobal variable                                                     |

| //Set up pointer to the first memory location to be written    |                                                                        |

| <pre>TBLPAG =builtin_tblpage(&amp;progAddr);</pre>             | // Initialize PM Page Boundary SFR                                     |

| <pre>offset =builtin_tbloffset(&amp;progAddr);</pre>           | // Initialize lower word of address                                    |

| <pre>builtin_tblwtl(offset, 0x0000);</pre>                     | // Set base address of erase block                                     |

|                                                                | // with dummy latch write                                              |

| NVMCON = $0 \times 4058;$                                      | // Initialize NVMCON                                                   |

| asm("DISI #5");                                                | // Block all interrupts for next 5 instructions                        |

| builtin_write_NVM();                                           | <pre>// C30 function to perform unlock // sequence and set WR</pre>    |

| REGISTER           | 8-4: INICC                                                                          | JNZ: INTERR                                                                                                                                        | UPI CONTI                                     | ROL REGIST       | EKZ              |                 |        |

|--------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|------------------|-----------------|--------|

| R/W-0              | R-0, HSC                                                                            | U-0                                                                                                                                                | U-0                                           | U-0              | U-0              | U-0             | U-0    |

| ALTIVT             | DISI                                                                                | —                                                                                                                                                  | _                                             | —                | —                | —               | _      |

| bit 15             |                                                                                     |                                                                                                                                                    |                                               |                  |                  |                 | bit    |

|                    |                                                                                     |                                                                                                                                                    |                                               |                  |                  |                 |        |

| U-0                | U-0                                                                                 | U-0                                                                                                                                                | U-0                                           | U-0              | R/W-0            | R/W-0           | R/W-0  |

| —                  | —                                                                                   | _                                                                                                                                                  |                                               | —                | INT2EP           | INT1EP          | INT0EP |

| bit 7              |                                                                                     |                                                                                                                                                    |                                               |                  |                  |                 | bit    |

|                    |                                                                                     |                                                                                                                                                    |                                               |                  |                  |                 |        |

| Legend:            |                                                                                     | HSC = Hardw                                                                                                                                        | are Settable/C                                |                  |                  |                 |        |

| R = Readabl        | le bit                                                                              | W = Writable                                                                                                                                       | bit                                           | U = Unimple      | mented bit, read | d as '0'        |        |

| -n = Value at      | t POR                                                                               | '1' = Bit is set                                                                                                                                   |                                               | '0' = Bit is cle | eared            | x = Bit is unkr | nown   |

| bit 14<br>bit 13-3 | 1 = Use Alterr<br>0 = Use stand<br>DISI: DISI In:<br>1 = DISI inst<br>0 = DISI inst | Ne Alternate Internate Internate Interrupt V<br>lard (default) ve<br>struction Status<br>ruction is active<br>ruction is not ac<br>ted: Read as '0 | ector Table<br>ector table<br>s bit<br>ective |                  |                  |                 |        |

| bit 2              | •                                                                                   | rnal Interrupt 2                                                                                                                                   |                                               | Dolority Soloot  | hit              |                 |        |

| Dit 2              | 1 = Interrupt c                                                                     | on negative edge                                                                                                                                   | je                                            |                  | Dit              |                 |        |

| bit 1              | 1 = Interrupt c                                                                     | rnal Interrupt 1<br>on negative edg<br>on positive edge                                                                                            | je                                            | Polarity Select  | bit              |                 |        |

| bit 0              | 1 = Interrupt c                                                                     | rnal Interrupt 0<br>on negative edg<br>on positive edge                                                                                            | je                                            | Polarity Select  | bit              |                 |        |

|                    |                                                                                     |                                                                                                                                                    |                                               |                  |                  |                 |        |

# REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER2

## 10.2.4.5 Deep Sleep WDT

To enable the DSWDT in Deep Sleep mode, program the Configuration bit, DSWDTEN (FDS<7>). The device Watchdog Timer (WDT) need not be enabled for the DSWDT to function. Entry into Deep Sleep mode automatically resets the DSWDT.

The DSWDT clock source is selected by the DSWDTOSC Configuration bit (FDS<4>). The postscaler options are programmed by the DSWDTPS<3:0> Configuration bits (FDS<3:0>). The minimum time-out period that can be achieved is 2.1 ms and the maximum is 25.7 days. For more details on the FDS Configuration register and DSWDT configuration options, refer to **Section 26.0 "Special Features"**.

### 10.2.4.6 Switching Clocks in Deep Sleep Mode

Both the RTCC and the DSWDT may run from either SOSC or the LPRC clock source. This allows both the RTCC and DSWDT to run without requiring both the LPRC and SOSC to be enabled together, reducing power consumption.

Running the RTCC from LPRC will result in a loss of accuracy in the RTCC of approximately 5 to 10%. If a more accurate RTCC is required, it must be run from the SOSC clock source. The RTCC clock source is selected with the RTCOSC Configuration bit (FDS<5>).

Under certain circumstances, it is possible for the DSWDT clock source to be off when entering Deep Sleep mode. In this case, the clock source is turned on automatically (if DSWDT is enabled), without the need for software intervention. However, this can cause a delay in the start of the DSWDT counters. In order to avoid this delay when using SOSC as a clock source, the application can activate SOSC prior to entering Deep Sleep mode.

#### 10.2.4.7 Checking and Clearing the Status of Deep Sleep

Upon entry into Deep Sleep mode, the status bit DPSLP (RCON<10>), becomes set and must be cleared by software.

On power-up, the software should read this status bit to determine if the Reset was due to an exit from Deep Sleep mode and clear the bit if it is set. Of the four possible combinations of DPSLP and POR bit states, three cases can be considered:

- Both the DPSLP and POR bits are cleared. In this case, the Reset was due to some event other than a Deep Sleep mode exit.

- The DPSLP bit is clear, but the POR bit is set. This is a normal POR.

- Both the DPSLP and POR bits are set. This means that Deep Sleep mode was entered, the device was powered down and Deep Sleep mode was exited.

# 10.2.4.8 Power-on Resets (PORs)

VDD voltage is monitored to produce PORs. Since exiting from Deep Sleep functionally looks like a POR, the technique described in **Section 10.2.4.7** "**Checking and Clearing the Status of Deep Sleep**" should be used to distinguish between Deep Sleep and a true POR event.

When a true POR occurs, the entire device, including all Deep Sleep logic (Deep Sleep registers, RTCC, DSWDT, etc.) is reset.

#### 10.2.4.9 Summary of Deep Sleep Sequence

To review, these are the necessary steps involved in invoking and exiting Deep Sleep mode:

- 1. Device exits Reset and begins to execute its application code.

- 2. If DSWDT functionality is required, program the appropriate Configuration bit.

- 3. Select the appropriate clock(s) for the DSWDT and RTCC (optional).

- 4. Enable and configure the DSWDT (optional).

- 5. Enable and configure the RTCC (optional).

- 6. Write context data to the DSGPRx registers (optional).

- 7. Enable the INT0 interrupt (optional).

- 8. Set the DSEN bit in the DSCON register.

- 9. Enter Deep Sleep by issuing a PWRSV #SLEEP\_MODE command.

- 10. Device exits Deep Sleep when a wake-up event occurs.

- 11. The DSEN bit is automatically cleared.

- 12. Read and clear the DPSLP status bit in RCON, and the DSWAKE status bits.

- 13. Read the DSGPRx registers (optional).

- 14. Once all state related configurations are complete, clear the RELEASE bit.

- 15. Application resumes normal operation.

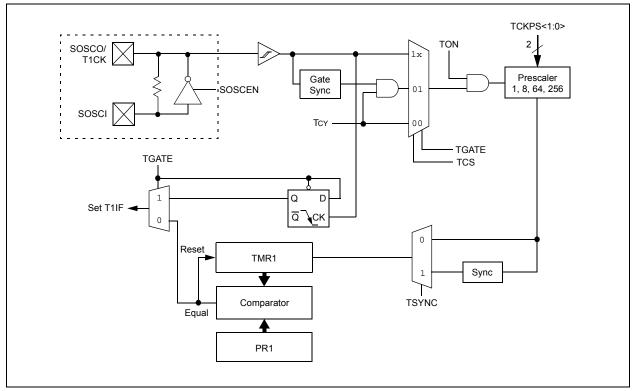

# 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "PIC24F Family Reference Manual", Section 14. "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC), or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 presents a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

# FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

# EXAMPLE 15-1: PWM PERIOD AND DUTY CYCLE CALCULATIONS<sup>(1)</sup>

1. Find the Timer Period register value for a desired PWM frequency of 52.08 kHz, where Fosc = 8 MHz with PLL (32 MHz device clock rate) and a Timer2 prescaler setting of 1:1.

Tcy = 2 \* Tosc = 62.5 ns

PWM Period = 1/PWM Frequency = 1/52.08 kHz =  $19.2 \mu$ s

PWM Period = (PR2 + 1) • Tcy • (Timer 2 Prescale Value)

19.2 µs = (PR2 + 1) • 62.5 ns • 1

PR2 = 306

2. Find the maximum resolution of the duty cycle that can be used with a 52.08 kHz frequency and a 32 MHz device clock rate:

PWM Resolution =  $log_{10}(FCY/FPWM)/log_{10}2)$  bits

= (log<sub>10</sub>(16 MHz/52.08 kHz)/log<sub>10</sub>2) bits

= 8.3 bits

**Note 1:** Based on Tcy = 2 \* Tosc; Doze mode and PLL are disabled.

# TABLE 15-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (Fcy = 4 MHz)<sup>(1)</sup>

| PWM Frequency         | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-----------------------|--------|-------|--------|--------|---------|----------|---------|

| Timer Prescaler Ratio | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Register Value | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits)     | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

# TABLE 15-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz)<sup>(1)</sup>

| PWM Frequency         | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-----------------------|---------|--------|--------|---------|----------|---------|---------|

| Timer Prescaler Ratio | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Register Value | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits)     | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

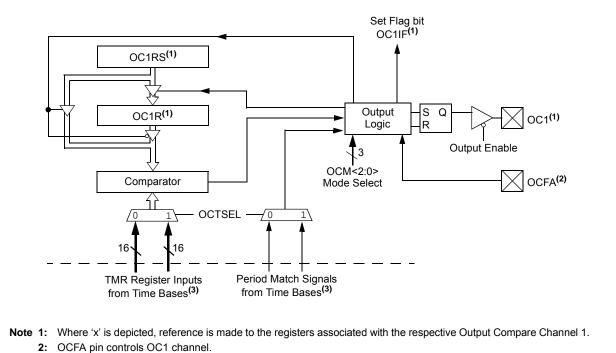

Control princontrols our channel.

Each output compare channel can use one of two selectable time bases. Refer to the device data sheet for the time bases associated with the module.

# REGISTER 15-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0     | U-0 | U-0 | U-0                     | U-0                    | U-0                        | U-0                        | U-0   |

|---------|-----|-----|-------------------------|------------------------|----------------------------|----------------------------|-------|

| _       | —   | —   | —                       | —                      | —                          | -                          | —     |

| bit 15  |     |     |                         |                        |                            |                            | bit 8 |

|         |     |     |                         |                        |                            |                            |       |

| U-0     | U-0 | U-0 | R/W-0                   | R/W-0                  | R/W-0                      | R/W-0                      | R/W-0 |

| _       | —   | —   | SMBUSDEL <sup>(3)</sup> | OC1TRIS <sup>(2)</sup> | RTSECSEL1 <sup>(1,4)</sup> | RTSECSEL0 <sup>(1,4)</sup> | _     |

| bit 7   |     |     |                         |                        |                            |                            | bit 0 |

|         |     |     |                         |                        |                            |                            |       |

| Logondy |     |     |                         |                        |                            |                            |       |

#### Legend:

| Legena.           |                  |                               |                    |

|-------------------|------------------|-------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | as 'O'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |

#### bit 15-5 Unimplemented: Read as '0'

- bit 3 OC1TRIS: OC1 Output Tri-State Select bit<sup>(2)</sup>

- 1 = OC1 output will not be active on the pin; OCPWM1 can still be used for internal triggers

- 0 = OC1 output will be active on the pin based on the OCPWM1 module settings

### bit 0 Unimplemented: Read as '0'

### Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL) bit needs to be set.

- 2: To enable the actual OC1 output, the OCPWM1 module has to be enabled.

- 3: Bit 4 is described in Section 17.0 "Inter-Integrated Circuit (I2C<sup>™</sup>)".

- 4: Bits 2 and 1 are described in Section 19.0 Real-Time Clock and Calendar (RTCC).

# 18.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UART:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt two cycles after being set).

- 4. Write data byte to lower byte of UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0, and then, the user may set UTXEN. This will cause the serial bit stream to begin immediately because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

# 18.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UART (as described in **Section 18.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt two cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

# 18.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UART for the desired mode.

- 2. Set UTXEN and UTXBRK sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

# 18.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UART (as described in Section 18.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UART.

- 3. A receive interrupt will be generated when one or more data characters have been received, as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

# 18.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear to Send (UxCTS) and Request to Send (UxRTS) are the two hardware-controlled pins that are associated with the UART module. These two pins allow the UART to operate in Simplex and Flow Control modes. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

# 18.7 Infrared Support

The UART module provides two types of infrared UART support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

As the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 18.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the UxBCLK pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the UxBCLK pin will output the 16x baud clock if the UART module is enabled; it can be used to support the IrDA codec chip.

# 18.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UART has full implementation of the IrDA encoder and decoder as part of the UART module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

# 26.0 SPECIAL FEATURES

- **Note:** This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Watchdog Timer, High-Level Device integration and Programming Diagnostics, refer to the individual sections of the *"PIC24F Family Reference Manual"* provided below:

- Section 9. "Watchdog Timer (WDT)" (DS39697)

- Section 36. "High-Level Integration with Programmable High/ Low-Voltage Detect (HLVD)" (DS39725)

- Section 33. "Programming and Diagnostics" (DS39716)

PIC24F16KA102 family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

# 26.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped, starting at program memory location, F80000h. A complete list is provided in Table 26-1. A detailed explanation of the various bit functions is provided in Register 26-1 through Register 26-8.

The address, F80000h, is beyond the user program memory space. In fact, it belongs to the configuration memory space (800000h-FFFFFFh), which can only be accessed using table reads and table writes.

#### TABLE 26-1: CONFIGURATION REGISTERS LOCATIONS

| Configuration<br>Register | Address |

|---------------------------|---------|

| FBS                       | F80000  |

| FGS                       | F80004  |

| FOSCSEL                   | F80006  |

| FOSC                      | F80008  |

| FWDT                      | F8000A  |

| FPOR                      | F8000C  |

| FICD                      | F8000E  |

| FDS                       | F80010  |

# REGISTER 26-1: FBS: BOOT SEGMENT CONFIGURATION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | BSS2  | BSS1  | BSS0  | BWRP  |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-4 Unimplemented: Read as '0'

- bit 3-1 BSS<2:0>: Boot Segment Program Flash Code Protection bits

- 111 = No boot program Flash segment

- 011 = Reserved

- 110 = Standard security, boot program Flash segment starts at 200h, ends at 000AFEh

- 010 = High-security boot program Flash segment starts at 200h, ends at 000AFEh

- 101 = Standard security, boot program Flash segment starts at 200h, ends at 0015FEh<sup>(1)</sup>

- 001 = High-security, boot program Flash segment starts at 200h, ends at 0015FEh<sup>(1)</sup>

- 100 = Reserved

- 000 = Reserved

# bit 0 BWRP: Boot Segment Program Flash Write Protection bit

- 1 = Boot segment may be written

- 0 = Boot segment is write-protected

Note 1: This selection should not be used in PIC24F08KA1XX devices.

| R/P-1         | R/P-1                                                                                                                                                              | R/P-1                                                                                                                     | R/P-1              | R/P-1             | R/P-1           | R/P-1           | R/P-1                                |  |  |  |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|-----------------|-----------------|--------------------------------------|--|--|--|--|--|--|--|--|--|

| FCKSM1        | FCKSM0                                                                                                                                                             | SOSCSEL                                                                                                                   | POSCFREQ1          | POSCFREQ0         | OSCIOFNC        | POSCMD1         | POSCMD0                              |  |  |  |  |  |  |  |  |  |

| bit 7         |                                                                                                                                                                    |                                                                                                                           |                    |                   |                 |                 | bit C                                |  |  |  |  |  |  |  |  |  |

|               |                                                                                                                                                                    |                                                                                                                           |                    |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

| Legend:       |                                                                                                                                                                    |                                                                                                                           |                    |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

| R = Readabl   | le bit                                                                                                                                                             | P = Progran                                                                                                               | nmable bit         | U = Unimplem      | ented bit, read | l as '0'        |                                      |  |  |  |  |  |  |  |  |  |

| -n = Value at | t POR                                                                                                                                                              | '1' = Bit is s                                                                                                            | et                 | '0' = Bit is clea | red             | x = Bit is unkr | iown                                 |  |  |  |  |  |  |  |  |  |

|               |                                                                                                                                                                    |                                                                                                                           |                    |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

| bit 7-6       | FCKSM<1:0>:                                                                                                                                                        | Clock Switch                                                                                                              | ning and Monitor   | Selection Confi   | iguration bits  |                 |                                      |  |  |  |  |  |  |  |  |  |

|               |                                                                                                                                                                    |                                                                                                                           |                    | Clock Monitor is  |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               |                                                                                                                                                                    |                                                                                                                           |                    | Clock Monitor is  |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               | 00 = Clock swi                                                                                                                                                     | itching is ena                                                                                                            | bled, Fail-Safe (  | Clock Monitor is  | enabled         |                 |                                      |  |  |  |  |  |  |  |  |  |

| bit 5         |                                                                                                                                                                    |                                                                                                                           | illator Select bit |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               | ,                                                                                                                                                                  | Secondary oscillator is configured for high-power operation<br>Secondary oscillator is configured for low-power operation |                    |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               |                                                                                                                                                                    |                                                                                                                           | 0                  | • •               |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

| bit 4-3       |                                                                                                                                                                    |                                                                                                                           | •                  | uency Range Co    | •               |                 |                                      |  |  |  |  |  |  |  |  |  |

|               |                                                                                                                                                                    |                                                                                                                           |                    | frequency is gre  |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               | 10 = Primary oscillator/external clock input frequency is between 100 kHz and 8 MHz<br>01 = Primary oscillator/external clock input frequency is less than 100 kHz |                                                                                                                           |                    |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               | 00 = Reserved                                                                                                                                                      |                                                                                                                           |                    |                   |                 | -               |                                      |  |  |  |  |  |  |  |  |  |

| bit 2         | <b>OSCIOFNC:</b> C                                                                                                                                                 | LKO Enable                                                                                                                | Configuration bi   | t                 |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               | 1 = CLKO output signal active on the OSCO pin; primary oscillator must be disabled or configured for                                                               |                                                                                                                           |                    |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               | the External Clock mode (EC) for the CLKO to be active (POSCMD<1:0> = 11 or 00)                                                                                    |                                                                                                                           |                    |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               | 0 = CLKO outp                                                                                                                                                      | out is disabled                                                                                                           | ł                  |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

| bit 1-0       | POSCMD<1:0                                                                                                                                                         | >: Primary O                                                                                                              | scillator Configu  | ration bits       |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               | 11 = Primary C                                                                                                                                                     |                                                                                                                           |                    |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               | 10 = HS Oscill                                                                                                                                                     |                                                                                                                           |                    |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               | 01 = XT Oscilla                                                                                                                                                    |                                                                                                                           |                    |                   |                 |                 |                                      |  |  |  |  |  |  |  |  |  |

|               | 00 = External 0                                                                                                                                                    | CIOCK MODE IS                                                                                                             | selected           |                   |                 |                 | 00 = External Clock mode is selected |  |  |  |  |  |  |  |  |  |

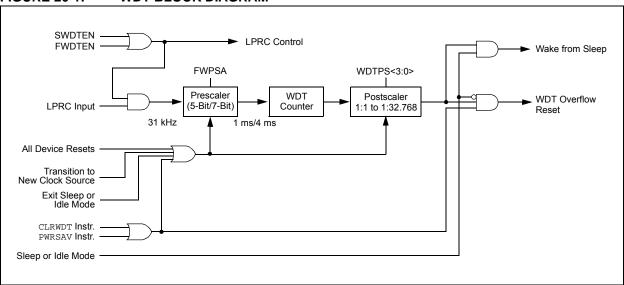

# 26.2 Watchdog Timer (WDT)

For the PIC24F16KA102 family of devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 31 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the FWPSA Configuration bit. With a 31 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the Configuration bits, WDTPS<3:0> (FWDT<3:0>), which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler time-out periods, ranging from 1 ms to 131 seconds, can be achieved.

The WDT, prescaler and postscaler are reset:

- On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction During normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3:2>) will need to be cleared in software after the device wakes up.

The WDT Flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

### 26.2.1 WINDOWED OPERATION

The Watchdog Timer has an optional Fixed Window mode of operation. In this Windowed mode, CLRWDT instructions can only reset the WDT during the last 1/4 of the programmed WDT period. A CLRWDT instruction executed before that window causes a WDT Reset, similar to a WDT time-out.

Windowed WDT mode is enabled by programming the Configuration bit, WINDIS (FWDT<6>), to '0'.

### 26.2.2 CONTROL REGISTER

The WDT is enabled or disabled by the FWDTEN Configuration bit. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

FIGURE 26-1: WDT BLOCK DIAGRAM

# 26.3 Deep Sleep Watchdog Timer (DSWDT)

In PIC24F16KA102 family devices, in addition to the WDT module, a DSWDT module is present which runs while the device is in Deep Sleep, if enabled. It is driven by either the SOSC or LPRC oscillator. The clock source is selected by the Configuration bit, DSWDTOSC (FDS<4>).

The DSWDT can be configured to generate a time-out at 2.1 ms to 25.7 days by selecting the respective postscaler. The postscaler can be selected by the Configuration bits, DSWDTPS<3:0> (FDS<3:0>). When the DSWDT is enabled, the clock source is also enabled.

DSWDT is one of the sources that can wake-up the device from Deep Sleep mode.

# 26.4 Program Verification and Code Protection

For all devices in the PIC24F16KA102 family, code protection for the boot segment is controlled by the Configuration bit, BSS0, and the general segment by the Configuration bit, GSS0. These bits inhibit external reads and writes to the program memory space; this has no direct effect in normal execution mode.

Write protection is controlled by bit, BWRP, for the boot segment and bit, GWRP, for the general segment in the Configuration Word. When these bits are programmed to '0', internal write and erase operations to program memory are blocked.

# 26.5 In-Circuit Serial Programming

PIC24F16KA102 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGCx) and data (PGDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

# 26.6 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 2 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the EMUCx (Emulation/Debug Clock) and EMUDx (Emulation/Debug Data) pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGCx, PGDx and the EMUDx/EMUCx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

# TABLE 29-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD) (CONTINUED)

| DC CHARACTER               | RISTICS                |     |       | Standard Operating Conditions: 1.8V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |            |               |  |  |  |  |  |

|----------------------------|------------------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|--|--|--|--|--|

| Parameter No.              | Typical <sup>(1)</sup> | Max | Units |                                                                                                                                                                                                       | Conditions |               |  |  |  |  |  |

| IDD Current <sup>(2)</sup> |                        |     |       |                                                                                                                                                                                                       |            |               |  |  |  |  |  |

| DC31                       |                        | 28  |       | -40°C                                                                                                                                                                                                 |            |               |  |  |  |  |  |

| DC31a                      |                        | 28  | μΑ    | +25°C                                                                                                                                                                                                 | 1.8V       |               |  |  |  |  |  |

| DC31b                      | 8                      | 28  |       | +60°C                                                                                                                                                                                                 |            |               |  |  |  |  |  |

| DC31c                      |                        | 28  |       | +85°C                                                                                                                                                                                                 |            |               |  |  |  |  |  |

| DC31d                      |                        | 55  |       | -40°C                                                                                                                                                                                                 |            | LPRC (31 kHz) |  |  |  |  |  |

| DC31e                      |                        | 55  |       | +25°C                                                                                                                                                                                                 |            |               |  |  |  |  |  |

| DC31f                      | 15                     | 55  | μA    | +60°C                                                                                                                                                                                                 | 3.3V       | 1             |  |  |  |  |  |

| DC31g                      |                        | 55  |       | +85°C                                                                                                                                                                                                 |            |               |  |  |  |  |  |

| DC31h                      |                        | 250 |       | +125°C                                                                                                                                                                                                |            |               |  |  |  |  |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** Operating Parameters:

• EC mode with clock input driven with a square wave rail-to-rail

• I/Os are configured as outputs, driven low

• MCLR - VDD

• WDT FSCM is disabled

• SRAM, program and data memory are active

• All PMD bits are set except for modules being measured

### TABLE 29-11: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS |                                 |                                      | $\begin{array}{ll} \mbox{Standard Operating Conditions: 1.8V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |                 |      |                                               |  |

|--------------------|---------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|------|-----------------------------------------------|--|

| Param<br>No.       | <sup>1</sup> Sym Characteristic |                                      | Min                                                                                                                                                                                                                                                                      | Typ <sup>(1)</sup> | Max Units Condi |      | Conditions                                    |  |

|                    |                                 | Program Flash Memory                 |                                                                                                                                                                                                                                                                          |                    |                 |      |                                               |  |

| D130               | Eр                              | Cell Endurance                       | 10,000 <b>(2)</b>                                                                                                                                                                                                                                                        | —                  | —               | E/W  |                                               |  |

| D131               | Vpr                             | VDD for Read                         | VMIN                                                                                                                                                                                                                                                                     | —                  | 3.6             | V    | VміN = Minimum operating voltage              |  |

| D133A              | Tiw                             | Self-Timed Write Cycle Time          | —                                                                                                                                                                                                                                                                        | 2                  | —               | ms   |                                               |  |

| D134               | TRETD                           | Characteristic Retention             | 40                                                                                                                                                                                                                                                                       | —                  | —               | Year | Provided no other specifications are violated |  |

| D135               | IDDP                            | Supply Current During<br>Programming | —                                                                                                                                                                                                                                                                        | 10                 | —               | mA   |                                               |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Self-write and block erase.

# TABLE 29-12: DC CHARACTERISTICS: DATA EEPROM MEMORY

| DC CHARACTERISTICS |        |                                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |     |       |                                               |  |

|--------------------|--------|------------------------------------------------------|------------------------------------------------------|--------------------|-----|-------|-----------------------------------------------|--|

| Param<br>No.       | Sym    | Sym Characteristic                                   |                                                      | Typ <sup>(1)</sup> | Мах | Units | Conditions                                    |  |

|                    |        | Data EEPROM Memory                                   |                                                      |                    |     |       |                                               |  |

| D140               | Epd    | Cell Endurance                                       | 100,000                                              | _                  | —   | E/W   |                                               |  |

| D141               | VPRD   | VDD for Read                                         | VMIN                                                 | _                  | 3.6 | V     | VMIN = Minimum operating voltage              |  |

| D143A              | Tiwd   | Self-Timed Write Cycle<br>Time                       | —                                                    | 4                  | —   | ms    |                                               |  |

| D143B              | Tref   | Number of Total Write/Erase<br>Cycles Before Refresh | —                                                    | 10M                | —   | E/W   |                                               |  |

| D144               | TRETDD | Characteristic Retention                             | 40                                                   | —                  | _   | Year  | Provided no other specifications are violated |  |

| D145               | Iddpd  | Supply Current During<br>Programming                 | —                                                    | 7                  |     | mA    |                                               |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

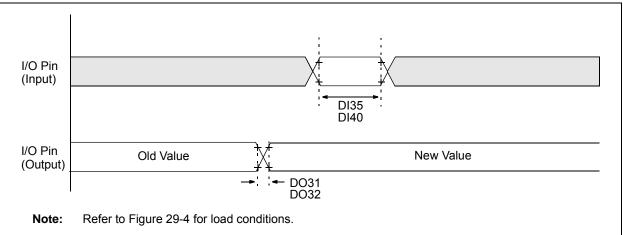

# TABLE 29-25: CLKO AND I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |      |                                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |    |    |     |  |  |

|--------------------|------|---------------------------------------|------------------------------------------------------|----|----|-----|--|--|